Der U61000 ist ein im Zentrum für Mikroelektronik entwickelter 1MBit DRAM, der nie in die Großserienproduktion überführt wurde. Der sogenannte Megabit-Chip hat eine gewisse Berühmtheit erlangt, da er eines der letzten Prestigeprojekte der DDR-Halbleiterindustrie war. Viele der folgenden Informationen stammen von Personen, die damals an der Entwicklung des Bausteins beteiligt waren, darunter der Projektleiter Prof. Dr. Bernd Junghans, der Systemarchitekt Andreas Scade, der Chefentwickler Dr. Jens Knobloch, der Leiter der Technologieentwicklung Dr. Michael Raab, der Direktor für Forschung und Entwicklung Prof. Dr. Dieter Landgraf-Dietz, der Bereichsleiter Jörg Ludewig und Dr. Hans Becker, der im Bereich des U61000 promoviert hat.

Beim Gehäuse fällt sofort der ungewöhnlich große Deckel auf. Er erstreckt sich fast über die komplette Fläche. Die Zeichen A2 zeigen, dass der Baustein im Februar 1990 produziert wurde. Die 12 auf der linken Seite kennzeichnet die langsamste Sortierung mit einer Zugriffszeit von 120ns. Parallel dazu war laut Datenblatt noch eine schnellere Sortierung vorgesehen.

Dieses Diagramm stammt aus der Studie "Der Osten Deutschlands - ein Standort europäischer Elektronik-Industrie" von Prof. Dr. Wolfgang Marschall. Es zeigt den technologischen Rückstand der DDR Halbleiterindustrie im internationalen Vergleich.

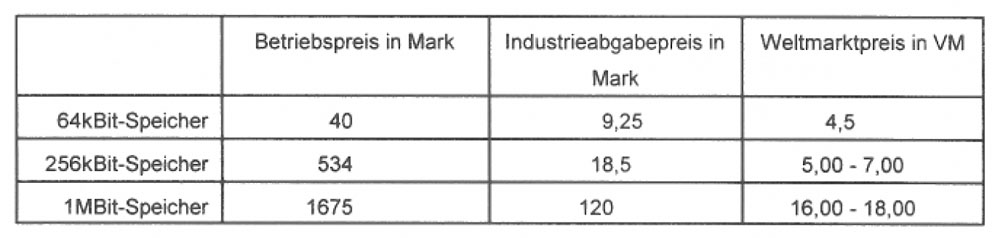

Noch etwas deutlicher ist obige Tabelle, entnommen aus dem Artikel "Die "technologische Lücke" - zum Rückstand der mikroelektronischen Industrie der DDR" 1998 erschienen im Heft 25 der "Dresdener Beiträge zur Geschichte der Technikwissenschaften". In der DDR hätte demnach die Serienproduktion des 1-Megabit Chips erst 5 Jahre nach der internationalen Markteinführung begonnen. Neben dem technologischen Rückstand, sorgten außerdem die hohen Entwicklungskosten und die vergleichsweise geringen Stückzahlen dafür, dass elektronische Bauteile aus eigener Entwicklung und Produktion sehr hohe Kosten verursachten. Für die DDR waren die Eigenentwicklungen trotzdem notwendig und sinnvoll, da integrierte Schaltkreise oft auf Embargolisten standen und man außerdem wertvolle Devisen dafür opfern musste. Gleichzeitig benötigte man dringend viele unterschiedliche ICs unter anderem für Konsumgüter, für die Industrie und natürlich auch für den militärischen Bereich.

Entwickelt man in der Halbleiterindustrie neue Prozesse, die kleinere Strukturbreiten ermöglichen, so fertigt man damit üblicherweise zuerst Speicherbausteine. Speicherbausteine besitzen verhältnismäßig einfache, sich ständig wiederholende Strukturen. Es war folglich für die DDR nur logisch die Speichertechnologie weiter zu entwickeln. Der beim U61000 verwendete Prozess trägt die Bezeichnung CSGT5d: Complementary Silicon Gate Technology, Technologieniveau 5. Der Buchstabe d kennzeichnet wahrscheinlich eine Variante dieses Prozesses. In der Veröffentlichung "Looking back: Artwork and Mask Making in Dresden for the East German Megabit Chip Project" von Hans W. Becker findet sich eine Angabe, dass "about 16" Masken zum Einsatz kamen. Michael Raab, Leiter der Technologieentwicklung spricht auf der 19. Leibnizkonferenz im Vortrag „Technologie der Mikroelektronik der Schlüssel für die digitale Revolution“ ebenfalls von 16 Masken (und 6 Implantationsschritten). In der Zeitschrift "Mikroprozessortechnik" findet sich 1989 ein großer von Dr. Jens Knobloch verfasster Artikel mit etwas mehr Details. Demnach kamen zur Verbindung der 2,3 Millionen Bauelemente drei Polysiliziumlagen und eine Metalllage zum Einsatz. Insgesamt waren 430 Teilschritte notwendig, um den U61000 herzustellen. In diesem Artikel ist von 18 fotolithografischen Strukturierungen die Rede.

Zur Entwicklung des U61000 wurden natürlich auch Fremdmuster analysiert. Wichtig war in diesem Zusammenhang vor allem der TC511000 von Toshiba. Siemens produzierte ähnliche Chips und hatte dafür eine Lizenz von Toshiba erworben. Der Auslandsgeheimdienst der DDR hatte sogar Unterlagen zu diesem Megabit-Chip beschafft. Den U61000 konnte man allerdings nicht auf dieser Grundlage aufbauen, da man mit den Technologien und Materialien arbeiten musste, die man zur Verfügung hatte. Bei Grundlagen der Architektur und den Funktionsblöcken hat man sich vielleicht inspirieren lassen, ein einfaches Kopieren des westlichen Produkts war allerdings nicht möglich.

Die Sowjetunion konnte vor der DDR 256kBit-Speicher produzieren. Als die DDR der Sowjetunion allerdings einen 1MBit-Speicher überreichen konnte, waren dort erst Unikate der eigenen Megabit-Speicher verfügbar. Diese basierten außerdem noch nicht auf der moderneren CMOS-Technik. Allerdings nutzte die DDR teilweise technische Spezialausrüstung aus westlicher Produktion, während die Sowjetunion nur auf eigene Produktionsanlagen setzte (Quelle: Wafer-Stepper und Megabit-Chip von Otto Bernd Kirchner).

Der U61000 war laut Wikipedia unter anderem für den Einsatz in den Robotron Rechnern K1820, K1840 und EC1835 eingeplant. Hier ist die Workstation K1822 zu sehen. Dabei handelt es sich um einen Nachbau des MicroVAX II von DEC. Im rechten Bild ist das zugehörige Speichermodul MSC20 abgebildet. Mit 72 U61000 bietet die Steckkarte 8MB Speicherplatz.

Hier ist ein mit U61000 bestücktes SIMM-Modul zu sehen.

Die obige Tabelle zeigt die verschiedenen Revisionen des U61000, einige Kernspezifikationen und von welchen Personen die Informationen stammen. Vor den bekannteren Versionen gab es den U61000T, der später zu U61000-0 umbenannt wurde. Das war der erste Entwurf des Megabitspeichers, der im Dezember 1987 fertiggestellt wurde. Im April 1988 waren erste Chips verfügbar, die allerdings noch Bitfehler enthielten.

Mit dem Erkenntnisgewinn aus dem U61000-0 wurde im Mai 1988 der Entwurf des U61000-1 fertiggestellt. Damit war es möglich im August 1988 erste bitfehlerfreie Chips zu produzieren. Im September 1988 konnte man erste Muster des Megabitchips der Öffentlichkeit präsentieren. Aus dieser Variante wurden daraufhin die Untervarianten U61000-1.1 und U61000-1.2 erzeugt. Die Pilotproduktion mit dem U61000-1.1 erfolgte im März 1989. Der U61000-1.2 wurde vom September 1989 bis zum März 1990 produziert. Insgesamt hat man dabei 6.700 Bauteile hergestellt.

Die Abmessungen des U61000-1 betrugen 12,8mm x 5,1mm. Für den Einsatz in Expoxidgehäusen war es notwendig das Die noch etwas zu verkleinern. Aus diesem Grund wurde im Januar 1989 der Entwurf der Version U61000-2 fertig gestellt. Für diese und die zwei Untervarianten 2.1 und 2.2 werden Abmessungen zwischen 12,5mm x 4,4mm und 12,6mm x 4,5mm angegeben. Wichtig war vor allem eine Reduktion der Breite. Bei den vorherigen Tests hatte man festgestellt, dass man die Abmessungen der Speicherkondensatoren von 3,89µm x 9,00µm auf 3,24µm x 9,00µm reduzieren konnte. Das war in diesem Zusammenhang sicherlich sehr hilfreich.

Dr. Hans Becker gibt für die letzten beiden Versionen 2.1 und 2.2 eine Ausbeute von 10% bzw. 20% an. Die Gesamtzahl aller produzierten U61000 muss den verschiedenen Quellen nach zu urteilen ungefähr 30.000 Stück betragen haben.

Im Rahmen der 19. Leibnizkonferenz findet sich der Vortrag "Entwicklung des Megabitspeichers U61000 1986 bis 1990" von Dr. Jens Knobloch. Darin ist die obige Tabelle enthalten, die die Kennwerte der Pilotproduktion aufzeigt. Die anvisierten Spezifikationen wurden erreicht und teilweise deutlich übertroffen. Die Ausbeute lag bei 9,5% und auch die notwendige Zuverlässigkeit konnte nachgewiesen werden.

Im Gehäuse zeigt sich wie grenzwertig groß das Die des U61000 ist. Außerdem fällt auf, das sich auf dem Silizium keine dicke Schutzschicht befindet, wie man sie beispielweise beim U2164 findet. Solche Schichten nutzt man bei Speichern gerne, um Alphastrahlung abzuschirmen. Die Gehäusematerialien sind nie ganz frei von radioaktiven Elementen, deren Strahlung zu Bitkippern führen kann. Eine gewisse Robustheit gegenüber ionisierender Strahlung erreicht man durch den Aufbau und die Anordnung der Speicherzellen. Dr. Jens Knobloch beschreibt im Artikel "Der Megabitspeicher U61000" in der Zeitschrift Mikroprozessortechnik (Heft 10, 1989) außerdem, dass beim U61000 unter den Speicherkondensatoren und unter den Bitleitungen Potentialbarrieren eingearbeitet wurden, die die Auswirkungen ionisierender Strahlung reduzieren sollen.

Ebenfalls im Rahmen der 19. Leibnizkonferenz findet sich der Vortrag "Speicherchip-Packaging - die Technologielokomotive für das Back-end" von Jörg Ludewig. Darin ist eine technische Zeichnung des Gehäuses abgebildet. Das Gehäuse musste importiert werden und war entsprechen teuer. Eine Umstellung auf ein Epoxidgehäuse sollte entsprechend möglichst schnell erfolgen.

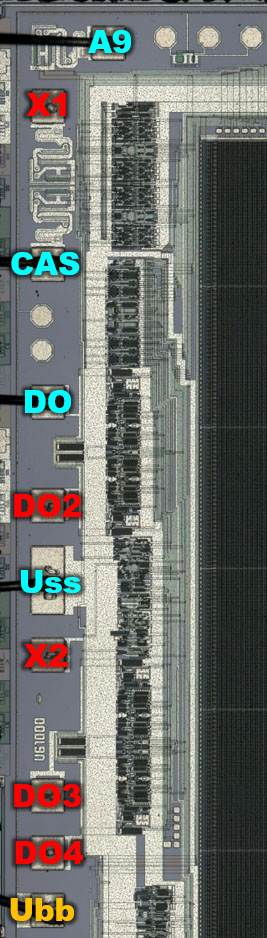

Die Beschriftung zeigt, dass das Potential Ubb an beiden Kanten kontaktiert wird. Ubb ist das Substratpotential, das nicht nach außen geführt wird, sondern nur mit der Metallfläche verbunden ist, auf der sich das Die befindet.

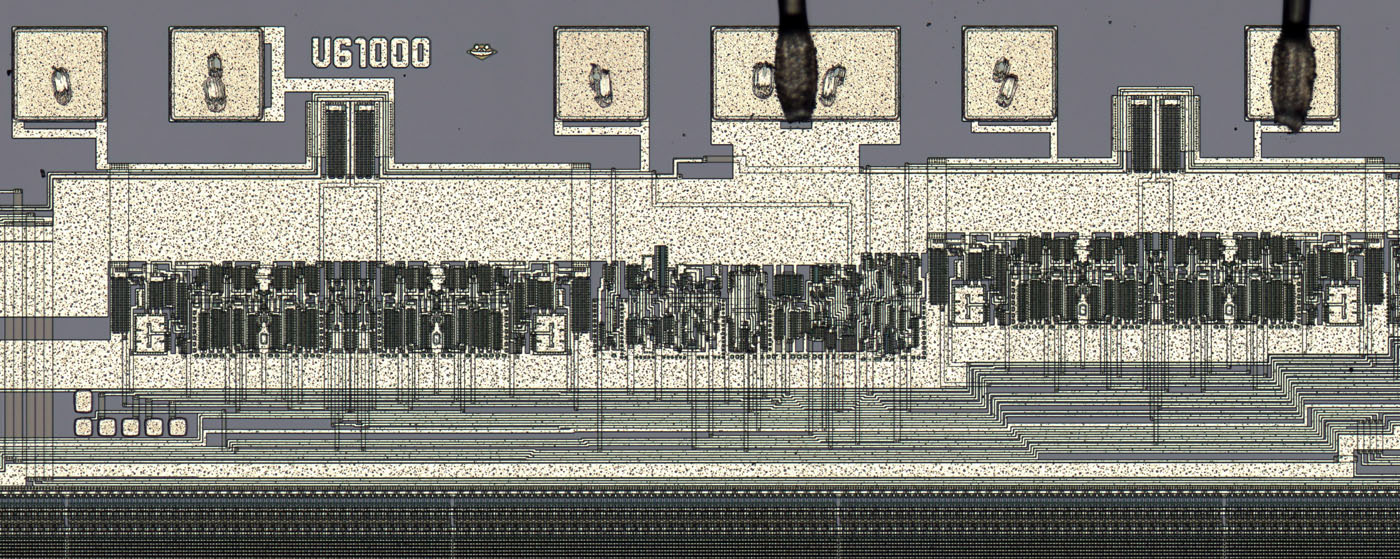

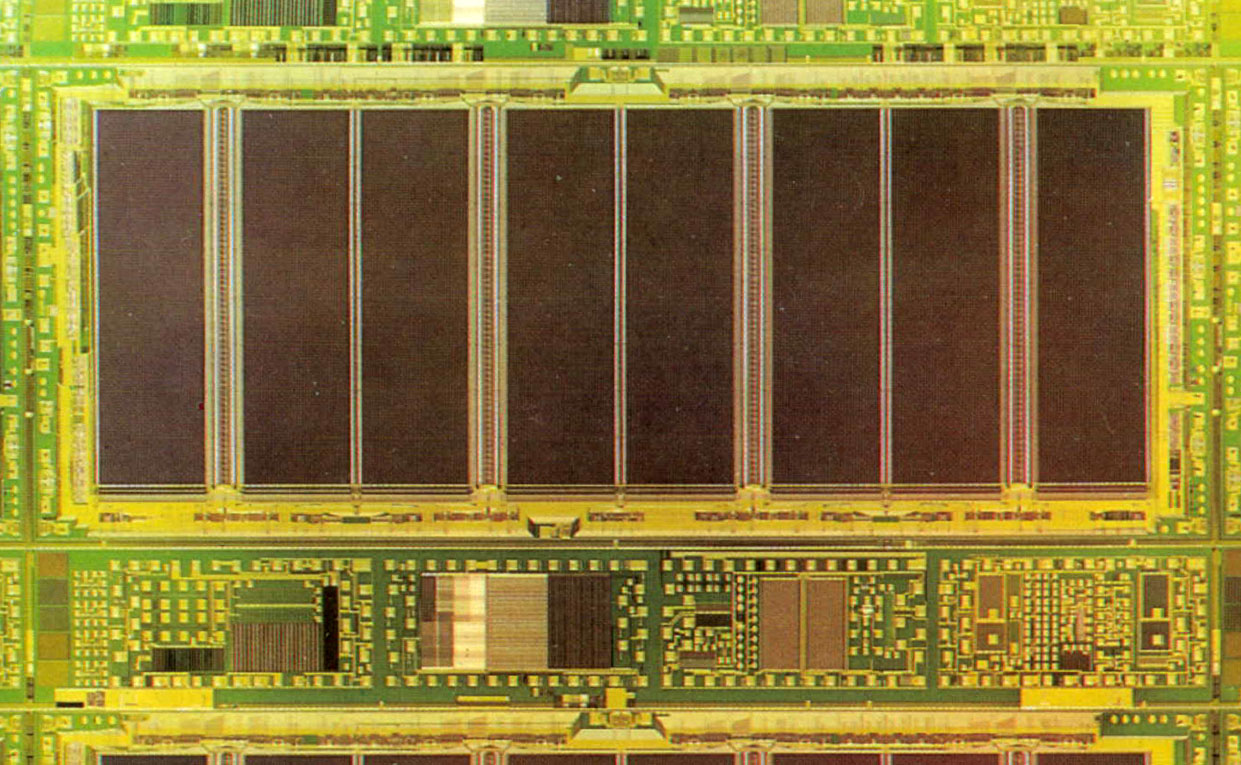

Die Abmessungen des Dies betragen 12,8mm x 5,1mm. Das entspricht den Abmessungen, die man in der Literatur für den U61000-1 findet.

Das Bild des Dies ist auch in einer höheren Auflösung verfügbar: 28MB

Neben der Bezeichnung U61000 ist ein stilisierter Frosch abgebildet. Mit diesem Zeichen hat sich der damalige Chefentwickler Dr. Jens Knobloch auf seinen Designs verewigt.

Das Datenblatt des U61000 zeigt die Schnittstellen des Speichers. Über die zehn Adressleitungen wird zuerst die Zeile und dann die Spalte des Speichers ausgewählt.

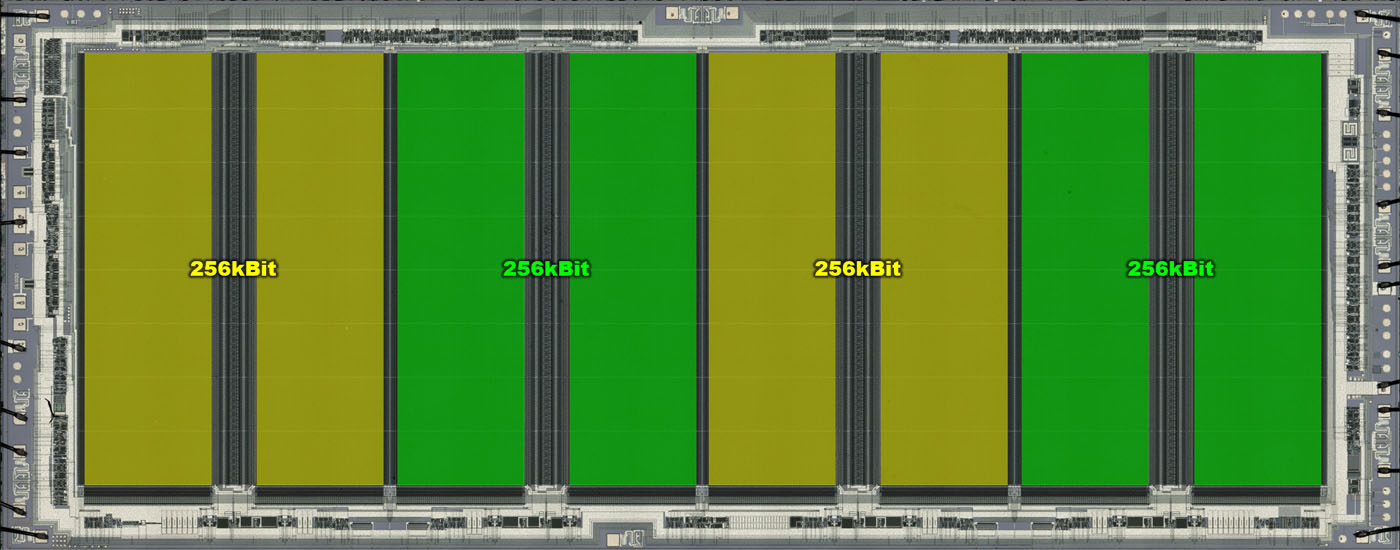

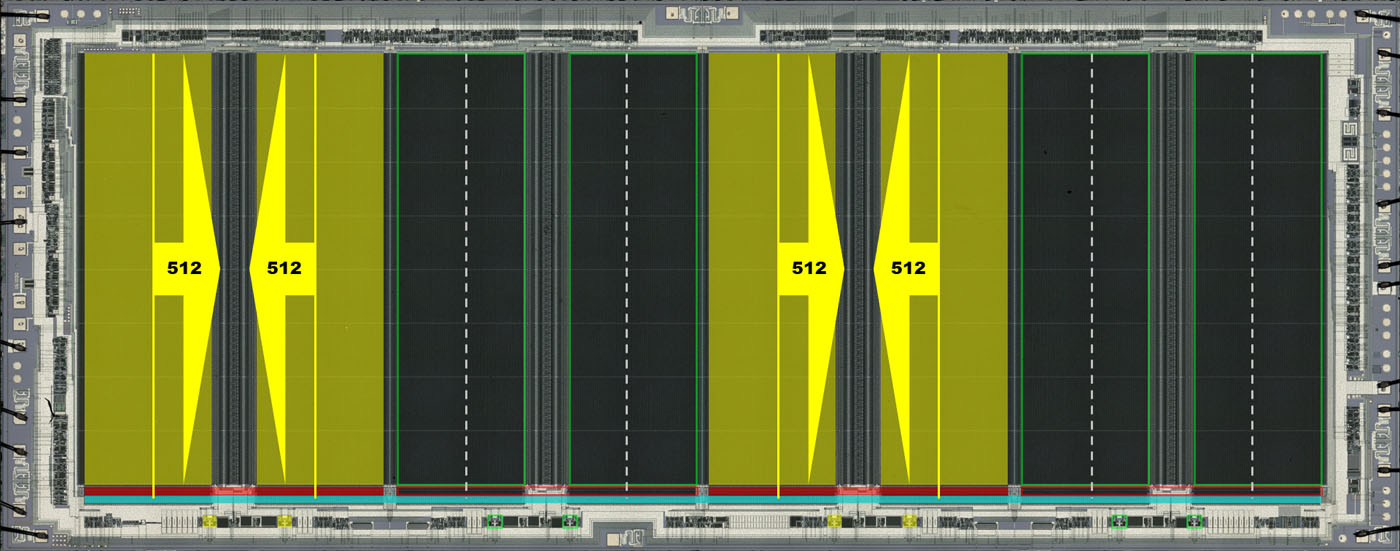

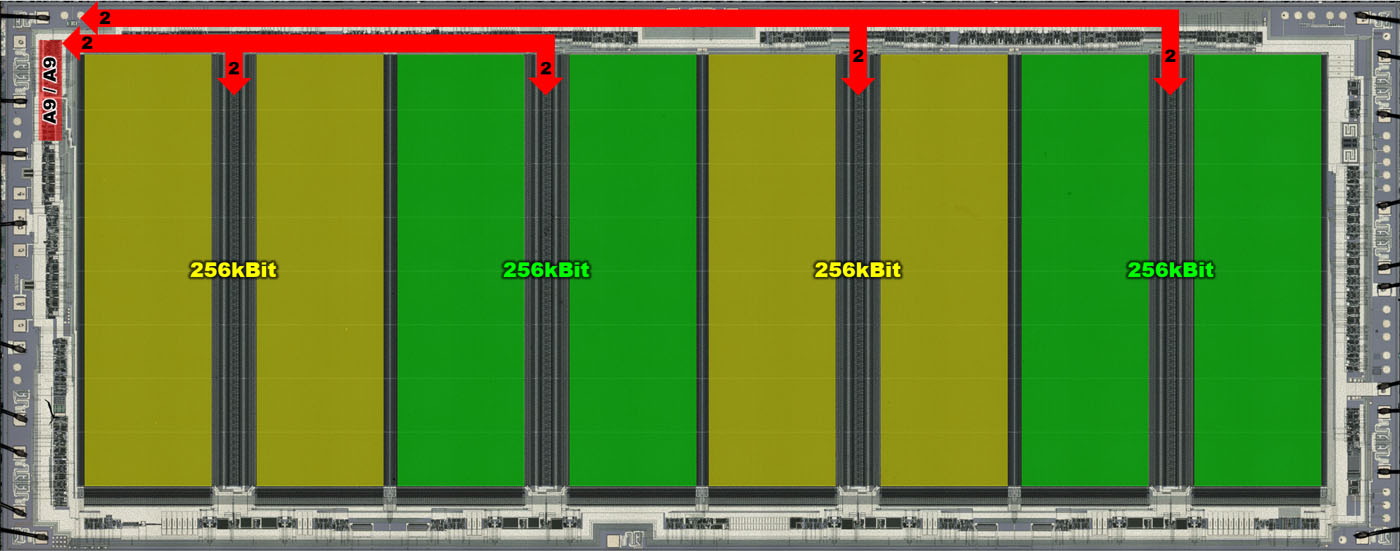

Im bereits erwähnten Artikel "Der Megabitspeicher U61000" findet sich das obige Blockschaltbild. Den Kern des Speichers bilden vier 256kB-Blöcke. Jeder Block besitzt 512 Zeilen. Die Zeilendekoder aktivieren jeweils eine Zeile. Viermal 512 Sensorverstärker werten die viermal 512 Spalten aus und schreiben die Daten danach auch wieder zurück. Der Spaltendekoder wählt aus jedem Block eine Zelle aus. Aus den vier Zellen wird letztlich dann eine für die Ausgabe ausgewertet. Wie sich noch zeigen wird entspricht diese Darstellung nicht ganz der Realität.

Zur Adressierung werden die zehn Adressbits einmal im Zeilenadresspuffer und einmal im Spaltenadresspuffer abgelegt. Der U61000 enthält zusätzlich eine Refreshsteuerung mit einem Adresszähler. Dieser Funktionsblock erleichtert es alle Daten im Speicher immer wieder rechtzeitig zu aktualisieren.

Die Potentiale der Pins finden sich problemlos auf dem Die wieder (türkis). Wie es in der Zeichnung des Gehäuses zu sehen war, befindet sich links und rechts je ein Bondpad, das das Substratpotential führt (orange). An der oberen Kante befinden sich zwei ungenutzte Bondpads. An der unteren Kante ist ein weiteres ungenutztes Bondpad platziert (weiß). Die Signale aller drei Bondpads enden in Stichleitungen. Die Strukturen enthalten aber Vorhalte die Bondpads mit den Adresspotentialen A0, A8 und A9 zu verbinden. Vermutlich wollte man sich damit die Option offen halten andere Gehäusetypen mit anders platzierten Kontaktflächen zu nutzen.

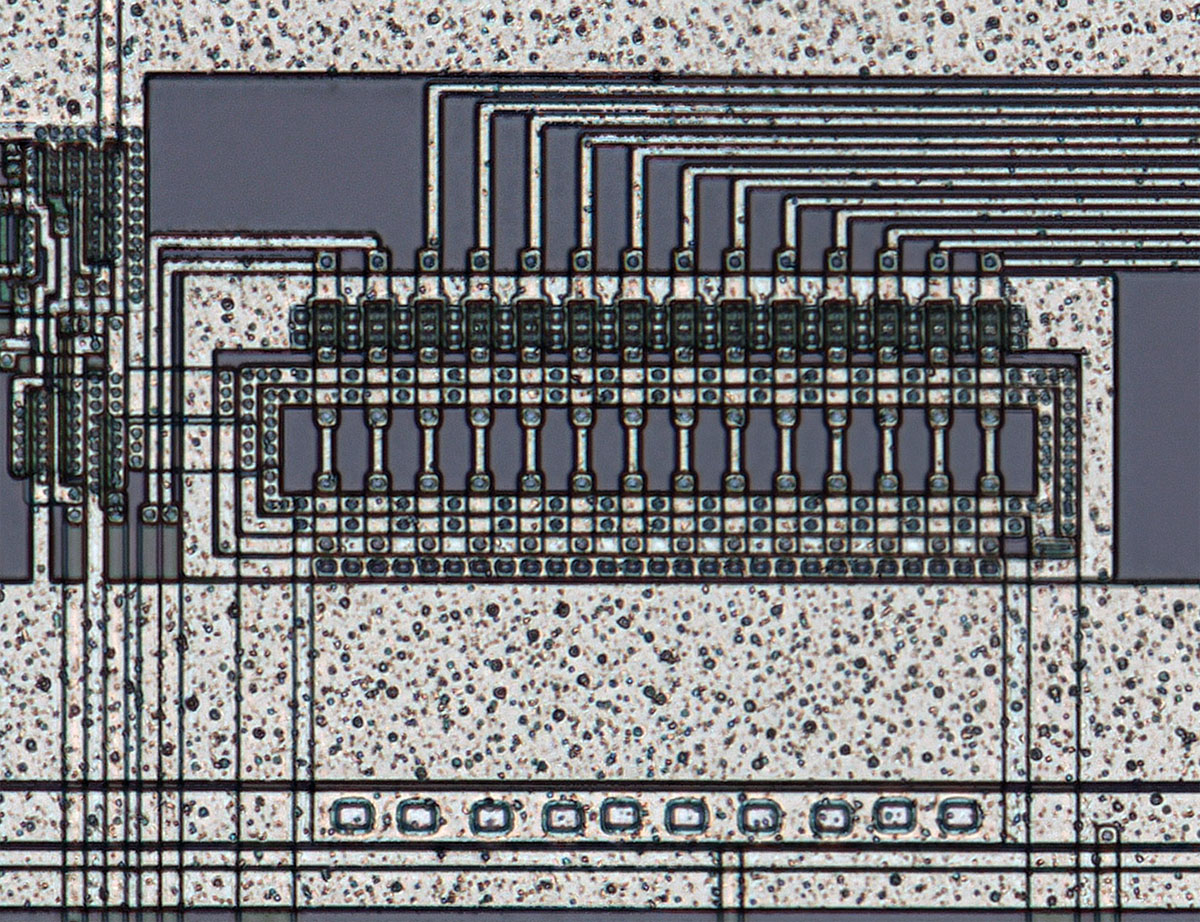

Die Eingangsschutzbeschaltung erscheint beinahe wie ein Kunstwerk. Zu einem Großteil entspricht sie der Schutzbeschaltung, die im Rahmen des U2164 genauer beschrieben ist. Hier hat man zusätzlich nahe am Bondpad einen Transistor integriert, der einen Metallstreifen als Gateelektrode nutzt. Dieser Transistor wird erst bei außergewöhnlich hohen Spannungen leitend und schafft dann eine niederohmige Verbindung zum Bezugspotential.

Das Die besitzt sehr viele Testpads. Darunter sind 27 große Testpads (rot), die man auch automatisiert kontaktieren könnte. 82 deutlich kleinere Testpads (gelb) erlauben es bei tiefergehenden Tests interne Signal zu kontaktieren, ohne dass man die Strukturen des Chips bearbeiten muss.

Die großen Testpads kontaktieren oft, aber nicht ausschließlich Teststrukturen. Die kleinen Testpads dienen hauptsächlich als Abgriffe interner Signale.

Die Strukturbreiten und die vielen Lagen erschweren eine genaue Analyse der Schaltungsteile. Die erkennbaren Strukturen und die Verbindungen erlauben es aber an vielen Stellen die Funktionsweise der Schaltung zu verstehen.

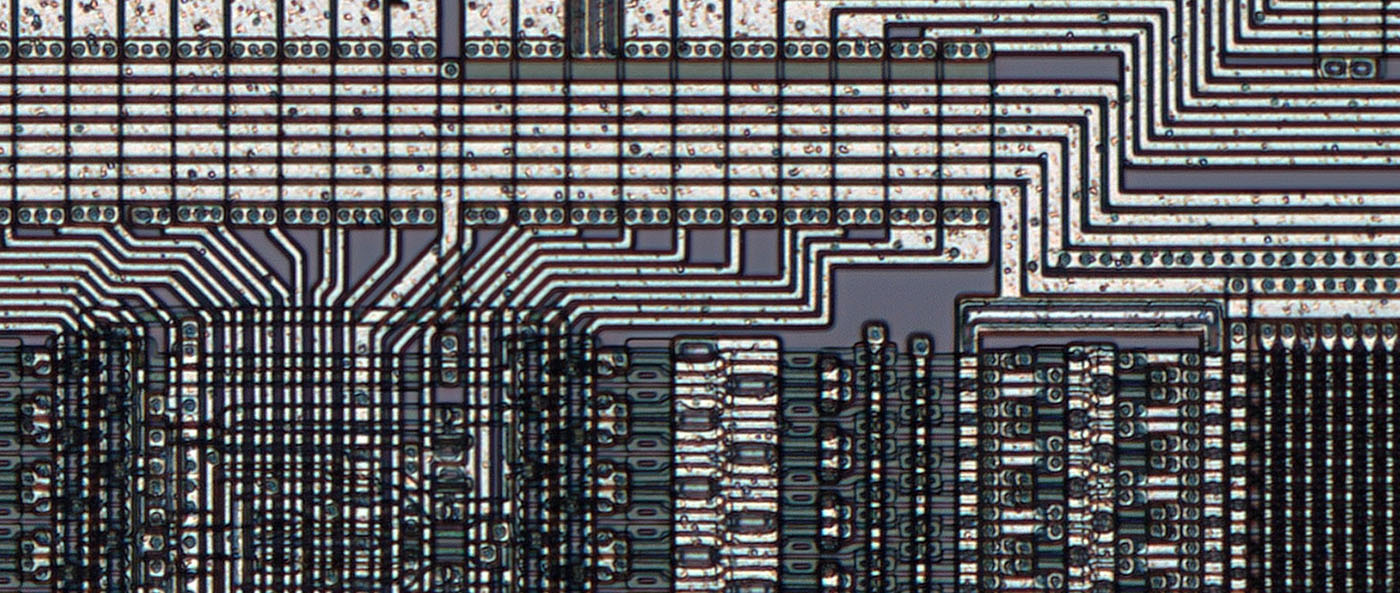

Im rechten oberen Bereich des Dies finden sich die großen Strukturen der Ladungspumpe, die für ein negatives Substratpotential sorgt. Man könnte meinen, dass der obere Bereich den zugehörigen Taktgenerator darstellt. Tatsächlich scheint sich der Taktgenerator aber im unteren Bereich des Dies zu befinden. Damit bleibt offen welche Funktion die obere Schaltung erfüllt. Vielleicht handelt es sich um eine Anpassung des Taktsignals.

Hier ist die Schaltung im unteren rechten Bereich des Dies zu sehen, die höchstwahrscheinlich den Taktgenerator enthält. Der größere, obere Teil des Bilds enthält große Strukturen, die Widerstände und Kapazitäten darstellen könnten, wie man sie für einen Taktgenerator benötigt. Die kleinen, sich wiederholenden Strukturen könnten die zugehörigen Transistoren sein. Am oberen Ende des Bilds führen vier breitere Leitungen nach rechts, die Taktleitungen zu sein scheinen.

Die Taktleitungen führen unter anderem zur Ladungspumpe. Der U61000 benötigt allerdings auch in anderen Bereichen ein Taktsignal. Offensichtlich ist dabei der Adresszähler zur regelmäßigen Aktualisierung der Daten. Der Takt wird aber ebenfalls zu den Speicherblöcken geführt. Dazu befindet sich in den beiden rechten Ecken des Dies jeweils eine Schaltung, die wie ein Treiber aussieht. Hier ist eine der beiden Schaltungen im unteren Bereich des Bilds zu sehen.

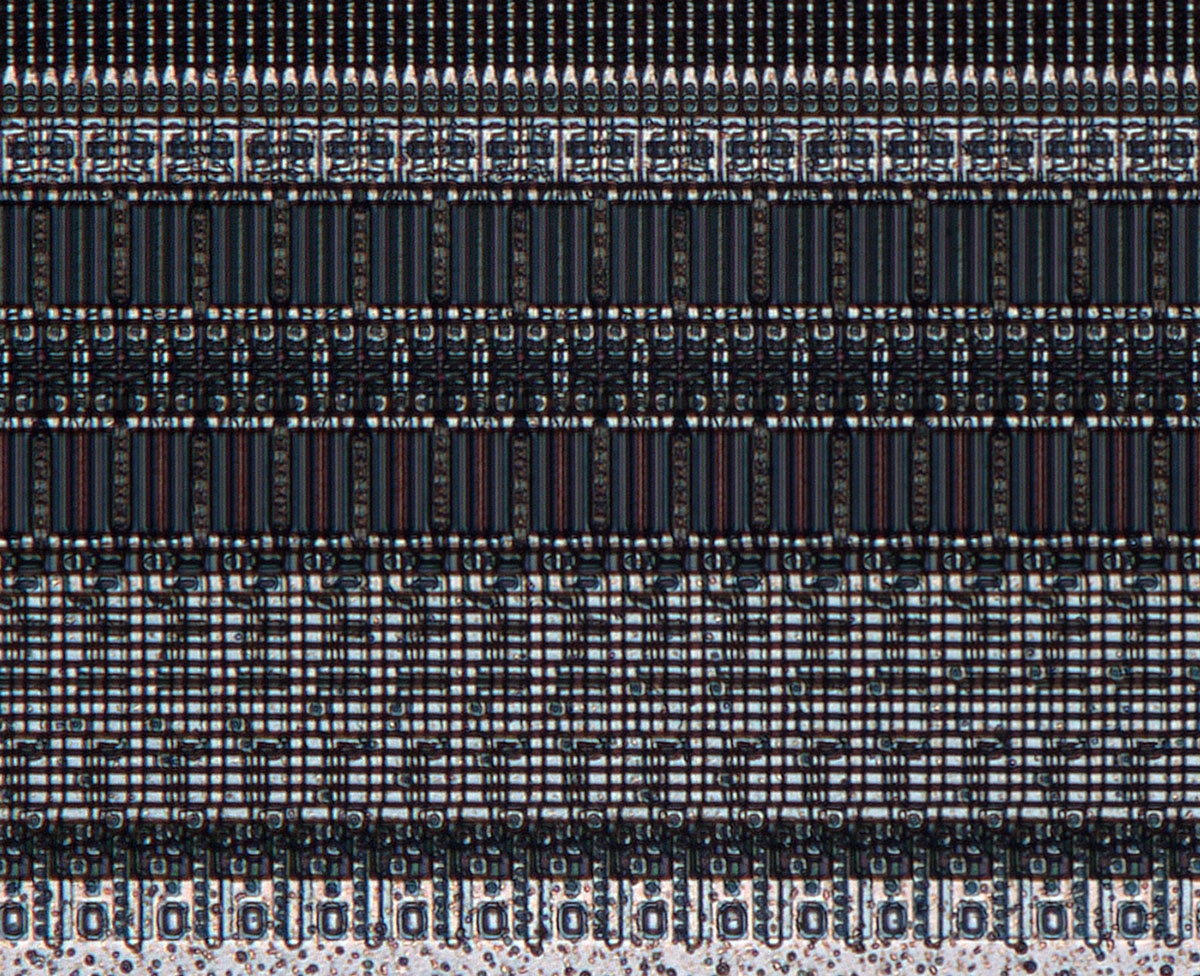

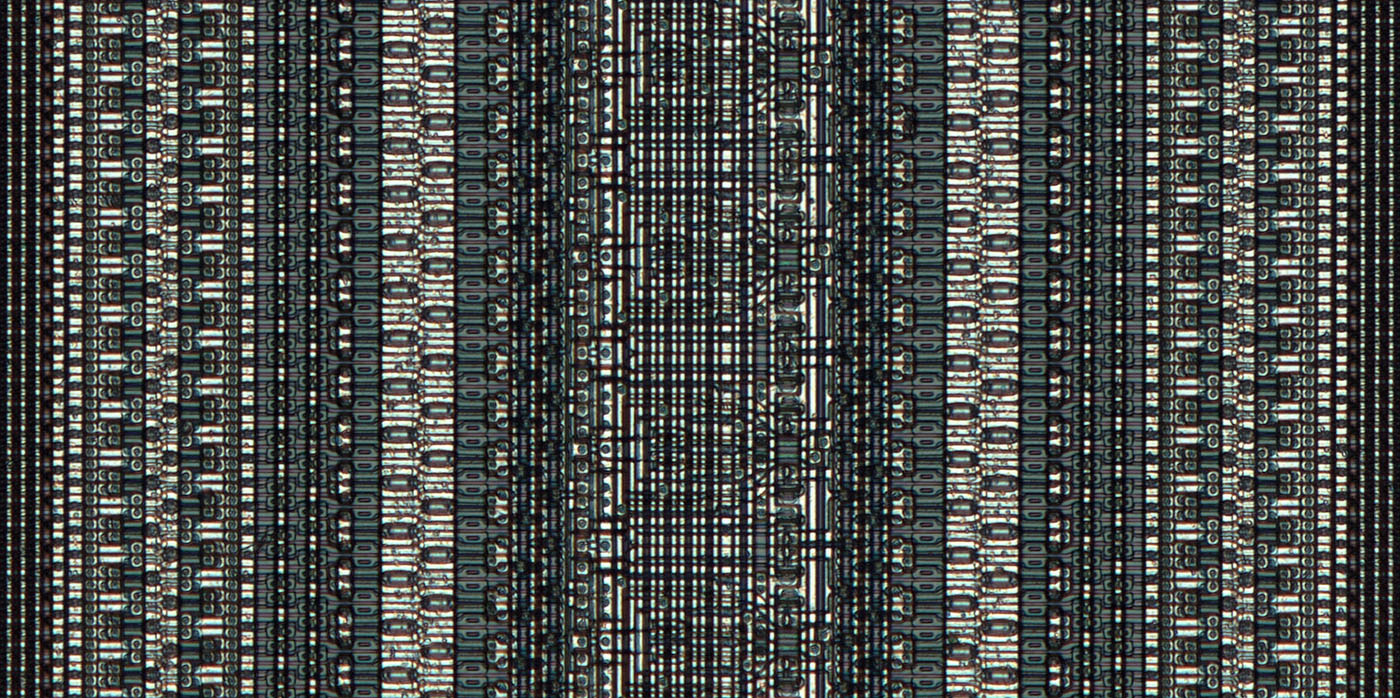

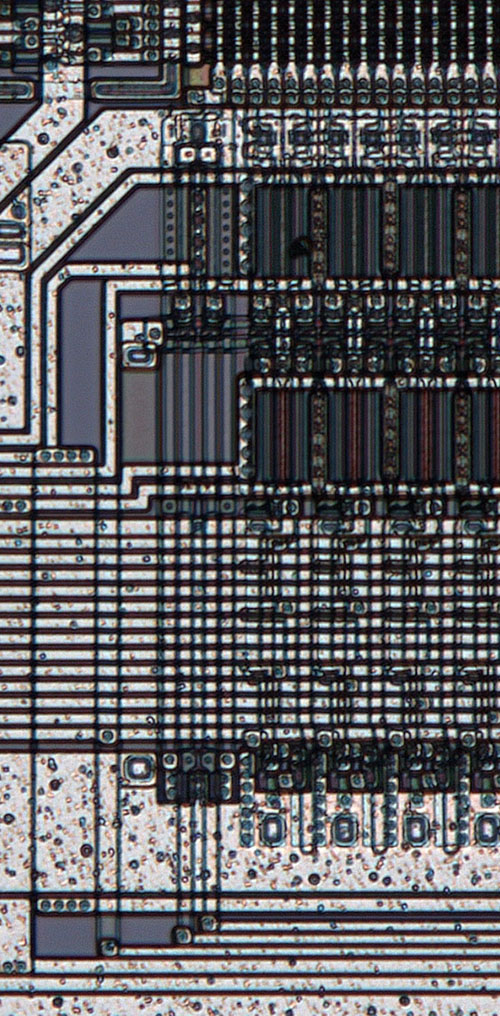

Der Aufbau des Speicherbereichs ist nicht zu erkennen. Die Strukturen wären noch groß genug, um sie optisch auflösen zu können. Die vielen Lagen, die in diesem Bereich viele Leitungen führen, erzeugen aber eine Unebenheit in der Oberfläche, die das Bild sehr unübersichtlich macht.

Die Wortleitung (Zeilenauswahl, vertikal) wurde in der Aluminiumlage abgebildet. Das verhältnismäßig niederohmige Metall erlaubt lange Leitungen. Die Bitleitungen (Spaltenauswertung, horizontal) konnten in der Folge kürzer ausgeführt werden. Das ist von Vorteil, da sich damit geringere parasitäre Kapazitäten ergeben, was die Auswertung der Spannungen erleichtert, die nur etwas über 100mV liegen.

Das obige Bild stammt aus dem Artikel "Der Megabitspeicher U61000" von Dr. Jens Knobloch. Die vier Verdrahtungslagen sorgen dafür, dass die Draufsicht auch in der stilisierten Darstellung unübersichtlich bleibt. Der Querschnitt ist etwas einfacher zu verstehen. Die erste und unterste Polysiliziumlage bildet mit den n-dotierten Flächen im Substrat die Speicherkapazitäten. Die Potentiale der Wortleitungen, die über die Metalllage verteilt werden, erreichen die Gateelektroden der Auswahltransistoren über Kontaktfenster, die im Querschnitt nicht zu sehen sind. Die Gateelektroden werden mit der zweiten Polysiliziumlage strukturiert. Das ist auf den ersten Blick verwunderlich. Üblicherweise stellt man die höchsten Anforderungen an das Gateoxid der Transistoren. Man würde daher erwarten, dass die Gateelektroden zuerst gefertigt werden. Bei einem DRAM ist die Speicherkapazität allerdings kritischer, was wahrscheinlich der Grund dafür war diese mit der ersten Polysiliziumlage darzustellen. Die Bitleitungen befinden sich in der dritten, der obersten Polysiliziumlage. Sie kontaktiert wie beim U2164 einen Punkt zwischen zwei Speicherzellen.

Prof. Dr. Bernd Junghans und Dr. Michael Raab haben in der Zeitschrift Jenaer Rundschau im Jahr 1989 den Artikel "CSGT5 - eine moderne Basistechnologie fuer Hoechstintegration" veröffentlicht. Darin findet sich der obige stilisierte Aufbau und das darunter liegende REM-Bild eines Schliffs. Man kann sofort die unregelmäßige Oberfläche erkennen, die es erschwert die Strukturen optisch aufzulösen.

Vor allem das obere Bild zeigt noch einmal deutlicher, wo sich welche Bereiche befinden und wie diese aufgebaut sind. Das Substrat ist ganz unten dunkelgrün eingefärbt. In der orangen Schicht befindet sich die Dotierung, durch die sich leitfähigen Strukturen im Substrat ergeben und zwischen denen mit einer Gateelektrode MOS-Transistoren entstehen. Das schwarz schraffierte Material ist das Siliziumoxid, dass zur Isolation der leitenden Bereiche dient. Die erste Polisilizumlage ist dunkelbraun dargestellt. Wie oben bereits beschrieben, stellt sie die Speicherkapazität dar. Die zweite Polsiliziumlage bildet in dunkelblau rechts die Gateelektrode des Auswahltransistors. Der linke Streifen hat in diesem Bild keine Funktion. Er führt lediglich zur nächsten, versetzt angeordneten Speicherzelle und bildet dort die Gatelektrode des Auswahltransistors. Die dritte Polysiliziumlage ist hier detaillierter dargestellt. Die Bildbeschreibung erklärt, dass es sich um Molybdänsilicid handelt, das sich auf einer Polysiliziumunterlage befindet. Die Metalllage ist gelb eingefärbt.

Mit der Reduktion der Strukturbreiten werden die Widerstände der Leiterbahnen und Kontakte zwischen den Lagen immer kritischer. Aus diesem Grund setzten die westlichen Megabitspeicher Titan ein. Titan reagiert mit Silizium zu Titansilicid, das einen deutlich reduzierten Widerstand bietet. Die DDR besaß kein Titan mit einer ausreichend hohen Reinheit (99,9999%). Eine Produktion von derart reinem Titan hätte mindestens 5 Jahre in Anspruch genommen. Als Alternative konnte man auf hochreines Molybdän zurückgreifen, das sich ebenfalls gut eignet, um den Widerstand von Silizium zu reduzieren. Die damit produzierten Strukturen verhielten sich allerdings anders. Das war ein Grund, warum die bekannten Strukturen der westlichen Megabitspeicher nicht einfach übernommen werden konnten.

Das obige Bild stammt aus dem Vortrag "Entwicklung des Megabitspeichers U61000 1986 bis 1990" von Dr. Jens Knobloch. Es zeigt das Ergebnis einer Elementanalyse an einem Schliff des U61000. Das Substrat und die Polysiliziumleitungen bestehen hauptsächlich aus Silizium, das blau dargestellt wird. Das isolierende Siliziumoxid wird rot abgebildet. Die Metallleitungen sind grün. In der horizontal verlaufenden Bitleitung ist deutlich das gelb eingefärbte Molybdän zu sehen.

In der Jenaer Rundschau von 1989 findet sich ein weiterer sehr interessanter Artikel: "Entwurf des Megabitspeichers" von Dr. Jens Knobloch, Prof. Dr. Wolf-Joachim Fischer, Stephan Dobritz und Andreas Scade. Darin ist unter anderem mit dem obigen Bild die Reduktion der Strukturgrößen im Bereich der DRAMs dokumentiert. Für die Veröffentlichung auf dieser Seite wurden lediglich die die Anordnung der Bausteine etwas modifiziert und die Bezeichnungen ergänzt. Teilweise sind es lediglich die funktionalen Bereiche einer Struktur, die eingefärbt wurden. Das muss man beachten, um die Darstellungen verstehen zu können. Die roten Flächen stellen die Speicherkapazitäten dar. Der Auswahltransistor befindet sich im blau markierten Bereich. Kontaktfenster sind grün eingefärbt. Die Metalllage ist grau. Für die Trench-Struktur beim 4MBit-DRAM hat man ein etwas dunkleres Blau gewählt.

Der U256, ein 16kBit-DRAM hat eine gänzlich andere Struktur als alle darauf folgenden Speichertechnologien. Der Aufbau der Speicherzellen im 64kBit-DRAM U2164 wurde bereits ausführlich dokumentiert. Die farbige Abbildung der U61000-Zelle ist mit den obigen Grundlagen gut zu verstehen. Beim U61256 scheint die Darstellung nicht ganz richtig zu sein. Demnach wären Bit- und Wortleitung in der Metalllage abgebildet und würden sich kreuzen. Nachdem der U61256 nur eine Metalllage besitzt, ist das aber nicht möglich. Den Bildern des U61256 nach zu urteilen ist die Bitleitung in der Polysiliziumlage ausgeführt. Das würde auch dazu passen, dass der U61256 öfter als wichtiger Schritt zum U61000 genannt wird. Auch der Auswahltransistor ist beim U61256 zu groß dargestellt.

Der U61000 sollte der letzte DRAM mit flächigen Speicherkondensatoren sein. Die international bereits verfügbaren 4MBit-DRAMs hatte man schon auf dreidimensionale Kondensatoren umgestellt. Eine konstante Verkleinerung der Speicherzellen reduziert im ersten Zug die Speicherkapazitäten. Man kann dem ein Stück weit entgegenwirken, indem man die Kapazitätsdichte erhöht. So ist zum Beispiel das Dielektrikum im U61000 nur noch 10nm dick. Nichtsdestotrotz ist die Entwicklung problematisch. Der Leckstrom sinkt nicht im gleichen Verhältnis wie die Kapazität, so dass sich die Haltezeit der Informationen immer weiter reduziert. Auch die parasitären Kapazitäten im Pfad der Auswertung werden bei kleineren Speicherkapazitäten immer kritischer. Beim U2164 beträgt die Speicherkapazität noch 50fF. Für den U61000 finden sich keine Informationen, aber beim 4MBit-Speicher wollte man versuchen 40fF zu erreichen. Dafür hat man wie oben zu sehen eine Trench-Kapazität eingeplant, also eine Vertiefung, die die Kapazität der Kondensatorfläche erhöht.

Das hier zu sehende Diagramm stammt ebenfalls aus dem Artikel: "Entwurf des Megabitspeichers". Dort sieht man wie sich die Fläche einer Speicherzelle über die Generationen reduziert hat. Die zwei Revisionen des 64kBit-DRAM U2164 und des 256kBit-DRAM U61256 wurden bereits dokumentiert. Auch beim U61000 konnte man die Speicherzellen von der Version 1 zur Version 2 merklich verkleinern. Zum 4MBit-Speicher sollte sich wieder eine sehr deutliche Reduktion des Flächenbedarfs ergeben.

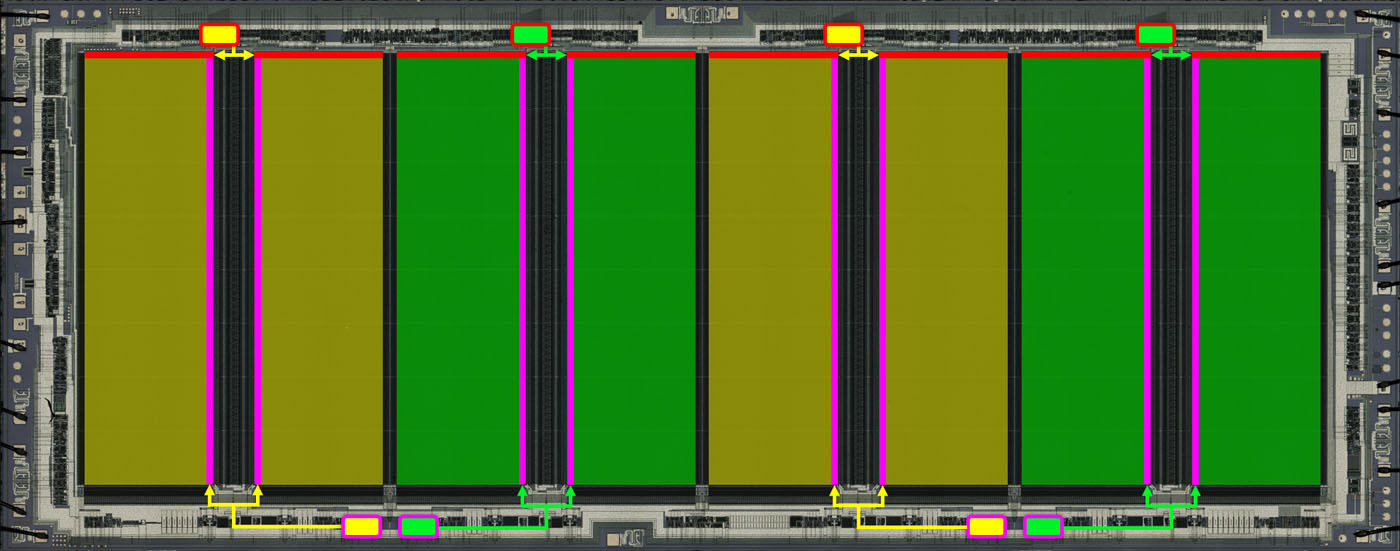

Wie im Blockschaltbild dargestellt, ist der Speicher in vier 256kBit-Blöcke aufgeteilt. Die Aufteilung ist nicht selbstverständlich und kann auch nicht beliebig gewählt werden. Man muss unter den vielen physikalischen Rahmenbedingungen eine möglichst sinnvolle Architektur finden.

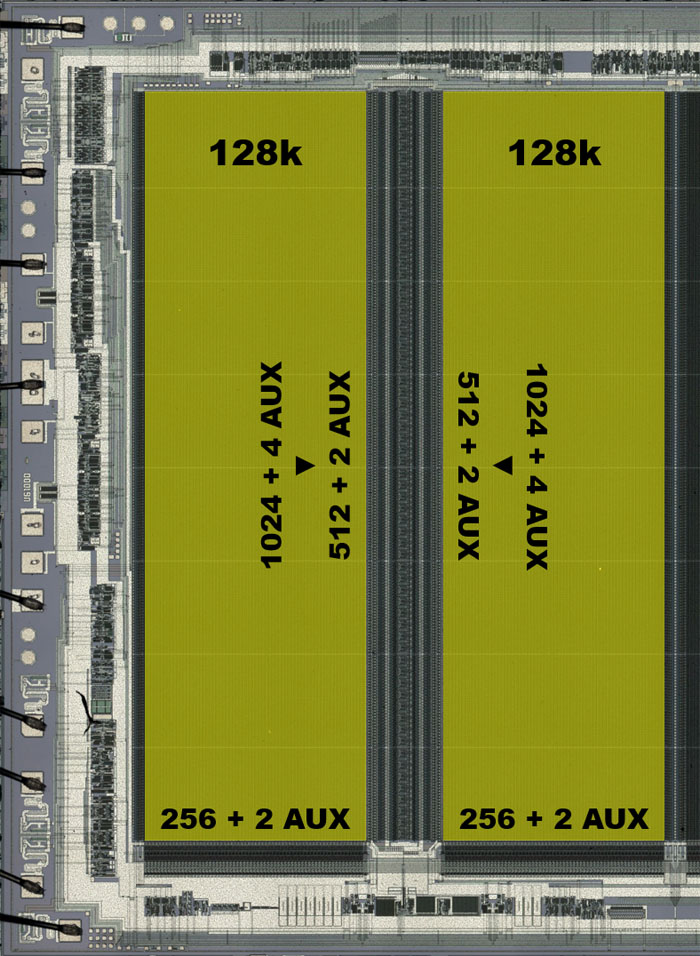

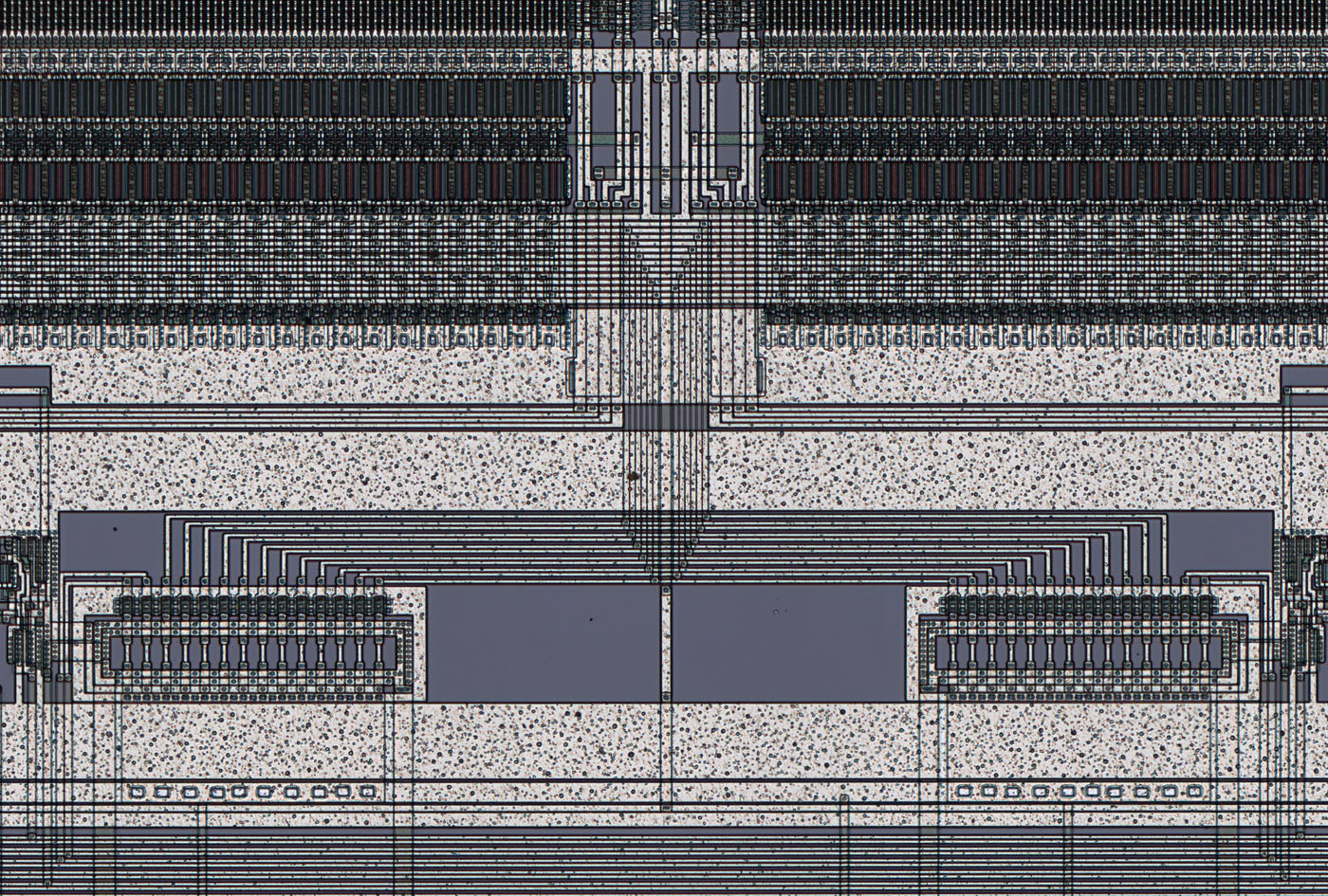

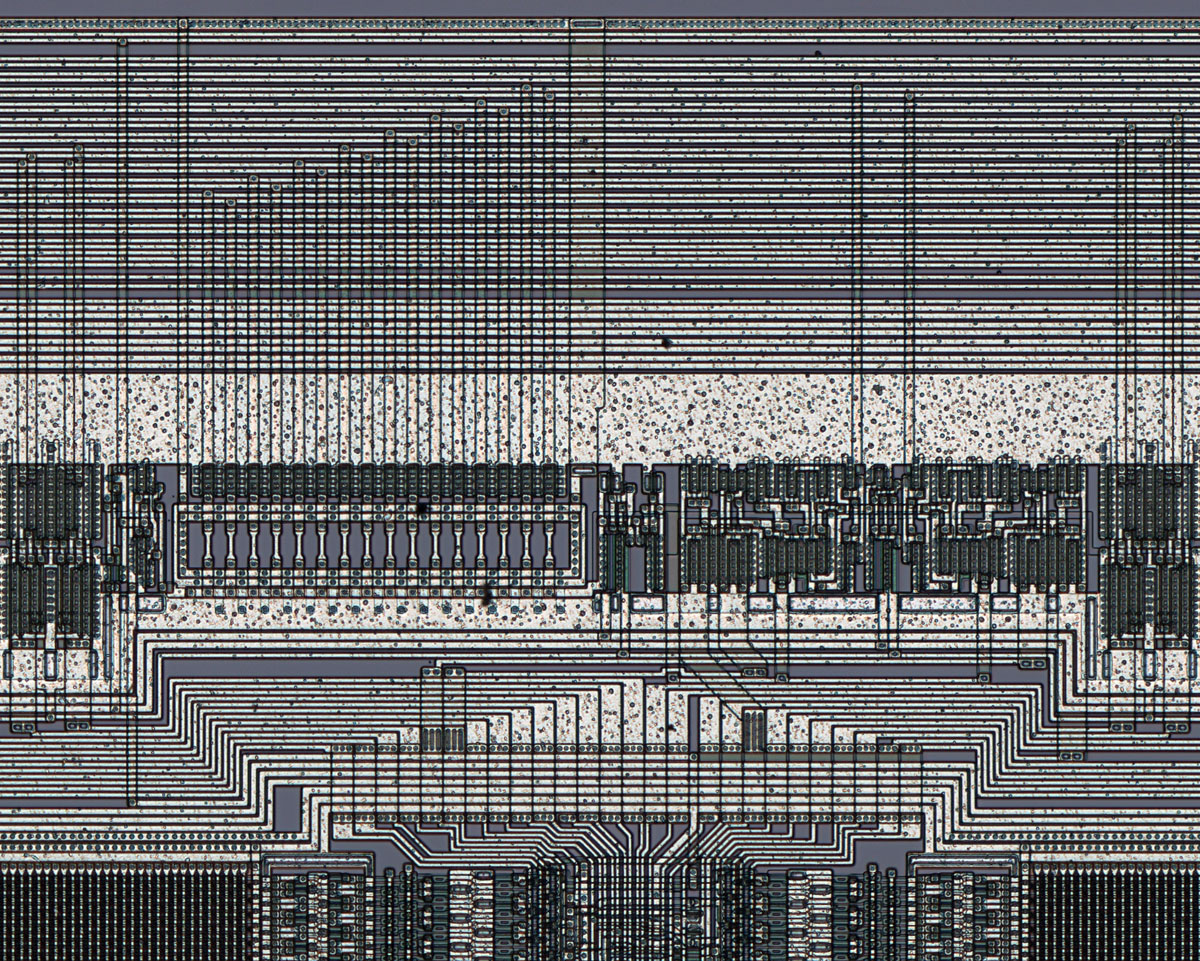

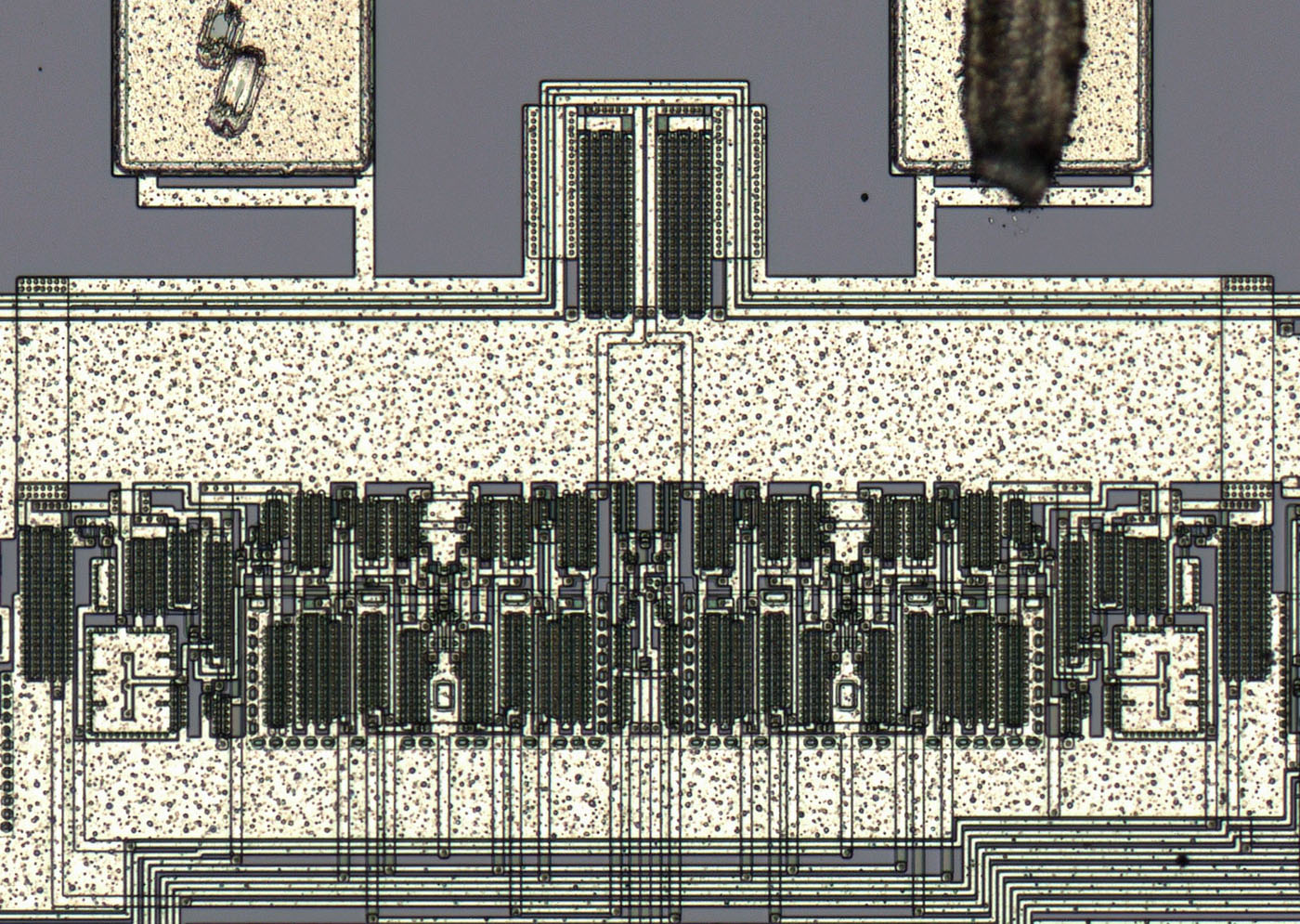

Die vier 256kB-Blöcke sind jeweils in zwei Hälften mit 128kB aufgeteilt. Es erscheint am sinnvollsten das Die weiterhin in der hier zu sehenden Orientierung darzustellen. Man muss sich allerdings damit abfinden, dass dadurch die Zeilen vertikal und die Spalten horizontal verlaufen. Man kann 256(+2) Zeilen und 1024(+4) Spalten erkennen. Wie beim U2164 sind auch hier die Speicherzellen zueinander versetzt angeordnet, so dass es sich effektiv um 512(+2) Spalten handelt.

Der U61000 besitzt neben den 1MBit Speicherzellen zusätzlich 1,2% Reservezellen. Jede Hälfte der 256kB-Blöcke besitzt zwei zusätzliche Zeilen und zwei zusätzlichen Spalten. Treten fehlerhafte Zellen auf, so kann man in gewissen Grenzen deren Adressen auf die Reservezellen umleiten.

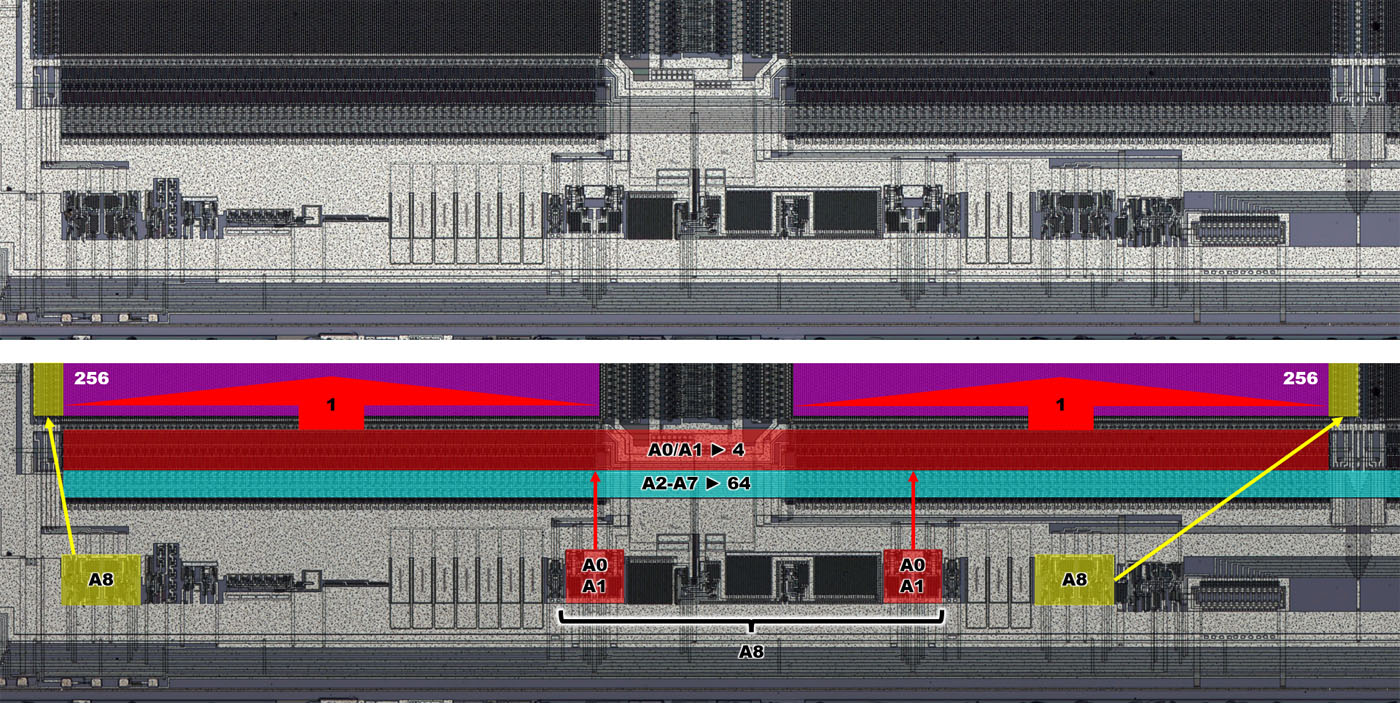

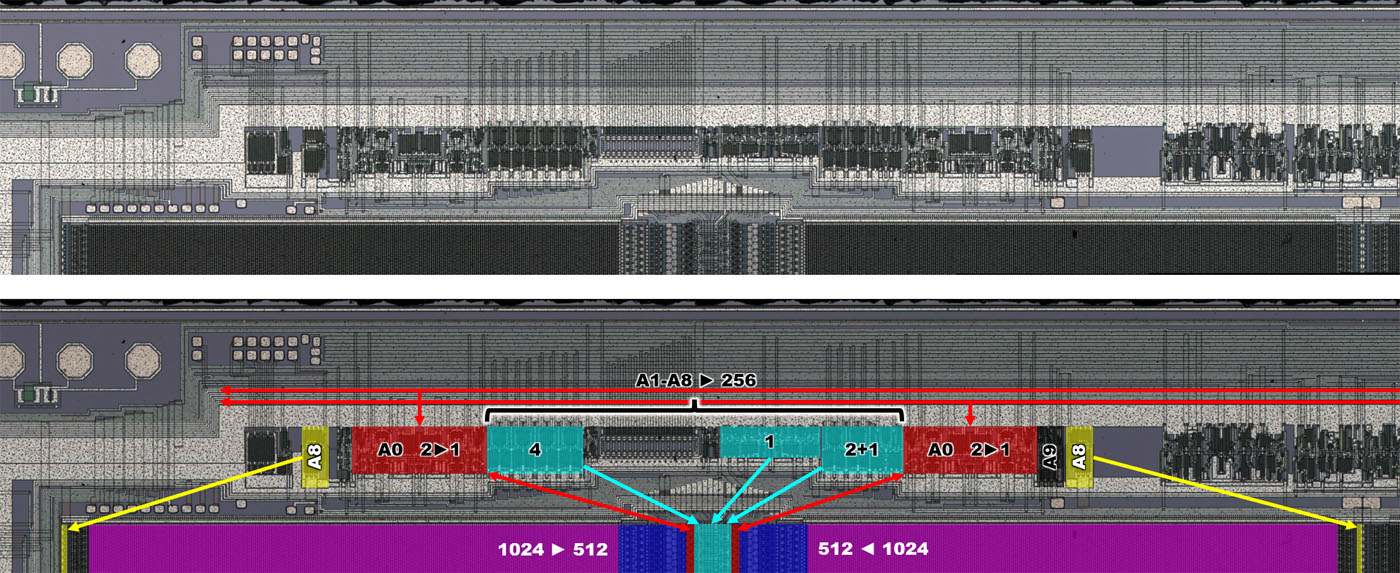

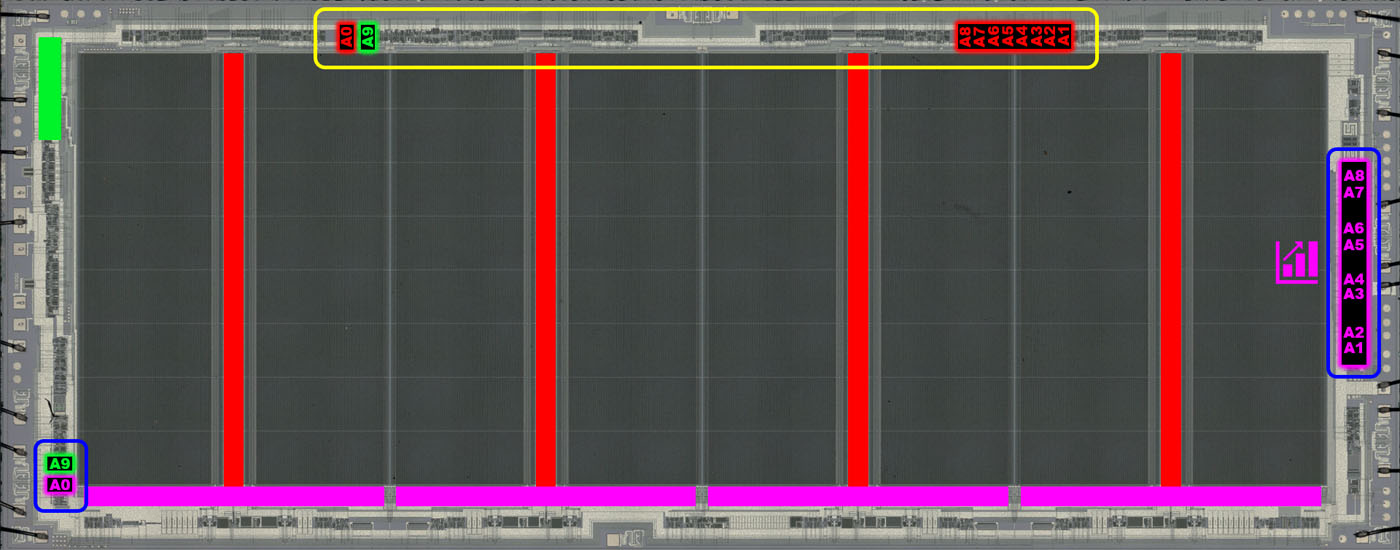

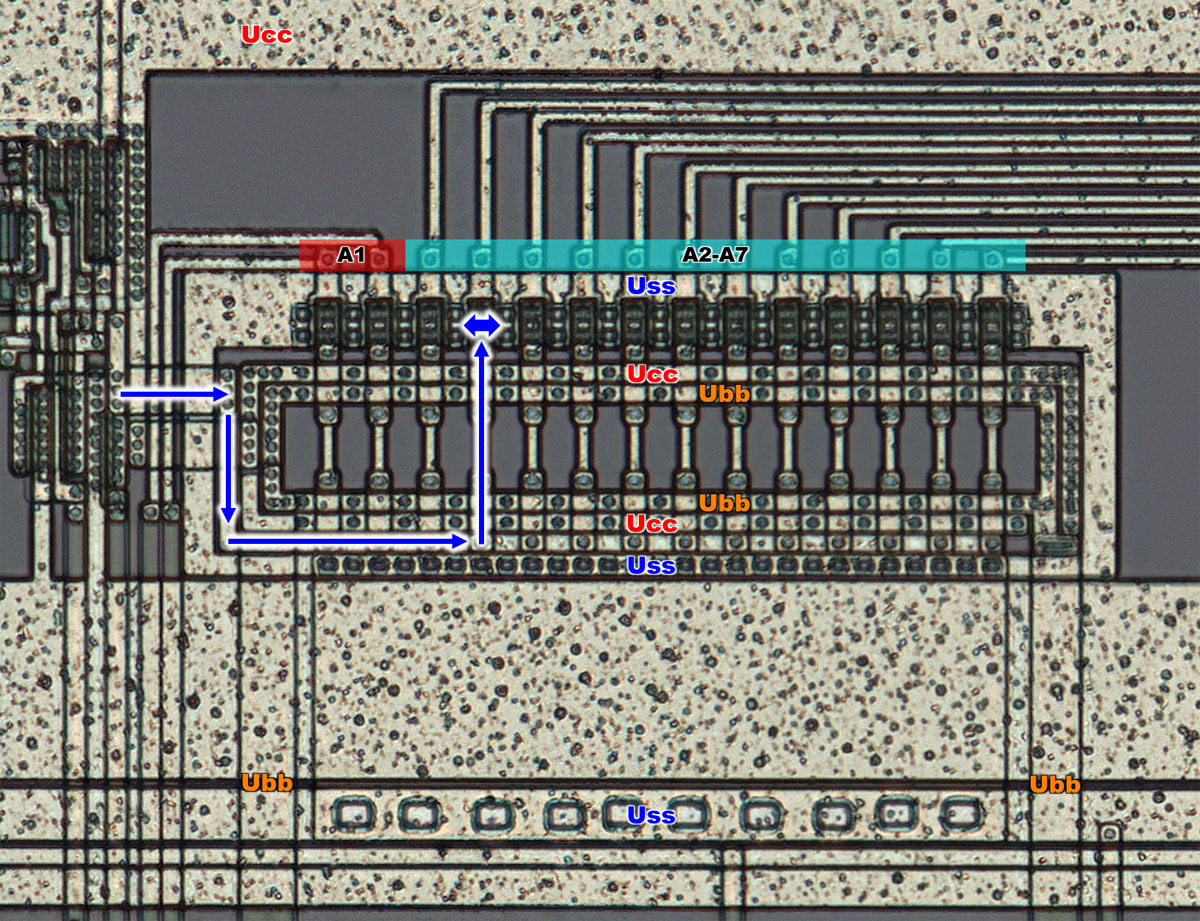

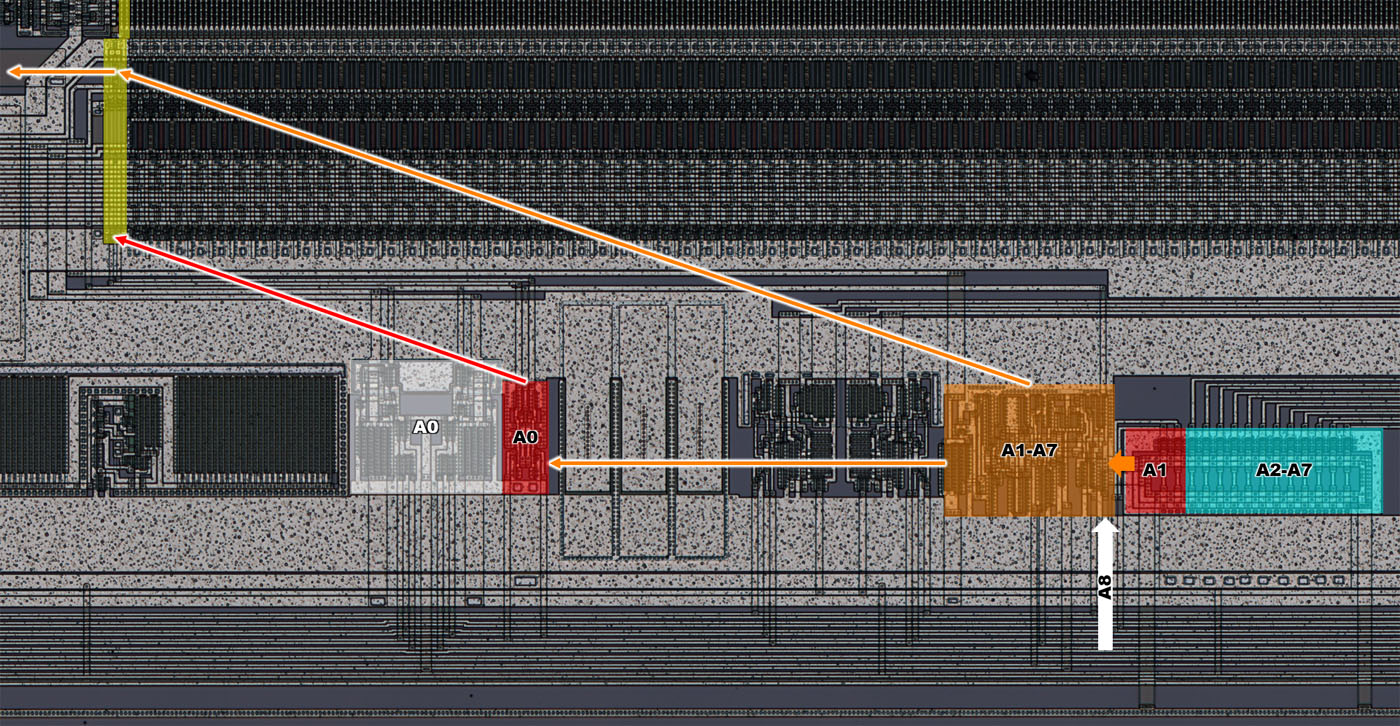

Die Zeilenauswahl erfolgt zweistufig. Sechs differentielle Signalleitungen verlaufen entlang der unteren Kanten aller vier Speicherblöcke (türkis). Gesteuert werden die Signalleitungen von den Zeilenadressregistern der Adressleitungen A2 bis A7. Zusätzlich werden die Adressleitungen A0 und A1 von kleinen Schaltungsblöcken ausgewertet, die lokal vier weitere Steuersignale für jeden Speicherblock erzeugen (rot). Ein Wert im Adressraums A0-A7 aktiviert so in jeder Hälfte des Speicherblocks eine der 256 Zeilen. Der Wert der Adressleitung A8 definiert außerdem, ob der 256kB-Speicherblock überhaupt aktiv ist oder nicht.

Man kann die unterschiedliche Kontaktierung der Adressleitungen im unteren Bereich erkennen. Wie man es erwarten würde, sind die Zeilentreiber im oberen Bereich verhältnismäßig groß.

Hier ist noch einmal deutlicher dargestellt, dass abhängig vom Zustand der Adressleitung A8 immer nur zwei der vier Speicherblöcke aktiv sind. Bei der Darstellung im Blockschaltbild könnte man meinen, dass immer alle vier Speicherblöcke ein Signal ausgeben.

Die vier Hälften der zwei aktiven Speicherblöcke geben jeweils den Zustand von 512 Speicherzellen aus. In der Mitte der Speicherblöcke erfolgt die parallele Auswertung aller Speicherzellen. Von dort aus müssen die destruktiv ausgelesenen 2048 binären Informationen dann auch wieder in die Zeilen zurückgeschrieben werden.

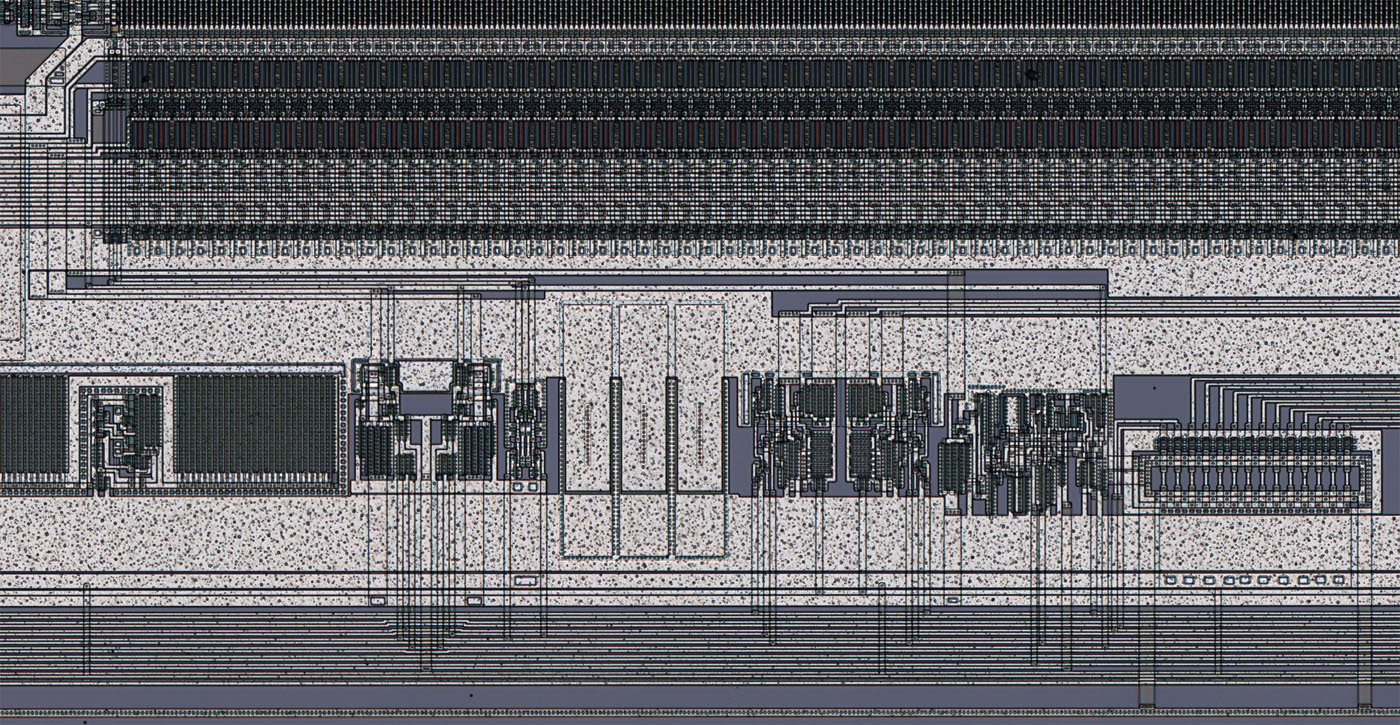

Die Spaltenauswahl erfolgt zwischen den Speicherblöcken. Die Steuerung der zugehörigen Adressierung übernehmen Schaltungsteile oberhalb der Speicherblöcke. Dort werden die Adressleitungen A1 bis A8 ausgewertet und differentiell der Spaltenauswahl zugeführt (türkis). Es fällt auf, dass die Treiberstufen von sechs Adressleitungen gleiche aufgebaut sind, während die anderen drei Treiberstufen optisch etwas aus der Reihe fallen. Wahrscheinlich steuern die Treiber unterschiedliche Auswahlmechanismen. Durch die Vorauswahl über die Adressen A1 bis A8 liefert jede Hälfte des Speicherblocks die Zustände von zwei Speicherzellen. Basierend auf der Adressleitung A0 erfolgt eine weitere Auswahl, so dass jeder Speicherblock letztlich zwei Datensignale ausgibt (rot). Das Beschreiben erfolgt über den selben Pfad.

Sowohl in der Zeilenauswahl an der unteren Kante des Dies, als auch in der Spaltenauswahl an der oberen Kante sind Schaltungsteile integriert, die nur mit der Adressleitung A8 verbunden sind (gelb). In beiden Fällen handelt es sich um das Signal A8 der Zeilenauswahl. Von diesen Schaltungsteilen führen Leitungen zu den Außenkanten der Speicherblöcke. Offensichtlich werden die Speicherblöcke auch an diesen Stellen inaktiv gehalten, wenn sie gerade nicht zu den zwei Speicherblöcken zählen, die ausgelesen oder beschrieben werden sollen. An der oberen Kante wird zusätzlich die Adressleitung A9 eingelesen. Sie scheint einen Einfluss auf die gesamte Spaltenauswahl zu haben.

Die Schaltung zur Spaltenauswahl und für die Datenverarbeitung ist eher unübersichtlich. Man kann allerdings die Adressierung in der Mitte erahnen. Zu den Speicherbereichen hin wird die paarweise Auswertung der Spalten deutlich.

Jeder der vier 256kB-Speicherblöcke liefert letztlich zwei Werte. Die Ausgänge von jeweils zwei benachbarten Speicherblöcken werden zusammengefasst. Das ist möglich, da gesteuert über die Adressleitung A8 immer nur zwei Speicherblöcke aktiv sind. In der linken oberen Ecke des Dies befindet sich der Schaltungsteil, der schließlich eine der vier Datenleitungen auswählt. Die Steuerung erfolgt über die zwei Werte, die man mit der Adressleitung A9 in die Spalten- und in die Zeilenauswahlregister schreibt.

Die Register für die Spaltenauswahl sind an der oberen Kante des Dies integriert (gelb). Das Register für die Zeilenauswahl befindet sich zum Großteil an der rechten Kante des Dies (blau). Die Register für A0 und A9 sind in der linken unteren Ecke zu finden. Bei der Zeilenauswahl ist die Zählerfunktion integriert, die für das Auffrischen der Speicherzellen genutzt wird.

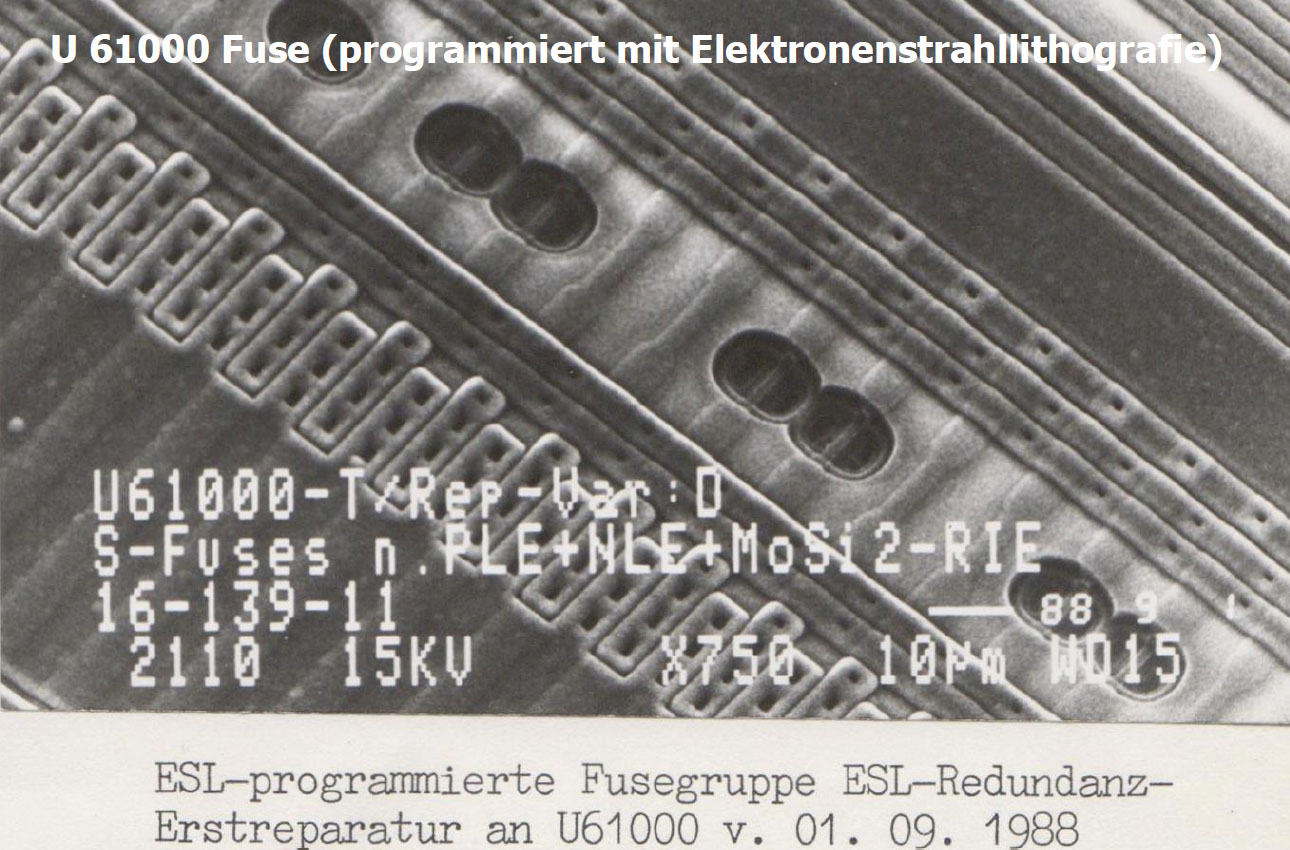

Beim 256kBit-Speicher U61256 kamen noch klassische Fuses zum Einsatz. Die dünnen Polysiliziumleitungen wurden mit einem verhältnismäßig hohen Strom durchtrennt. Derartige Fuses und die zugehörige Auslöseschaltung belegen allerdings viel Fläche. Bei einem 1MBit-Chip benötigt man mehr Konfigurationsmöglichkeiten, um eine ausreichende Ausbeute darstellen zu können. Mit klassischen Fuses lässt sich das nicht mehr sinnvoll realisieren. Toshiba setzte beim Wafertest einen Laser ein, um die Fuses seiner Megabitspeicher zu durchtrennen. In der DDR hatte man keinen geeigneten Laser zur Verfügung. Carl Zeiss Jena wollte einen derartigen Laser nicht entwickeln, da nur sehr kleine Stückzahlen benötigt worden wären.

Man musste folglich eine Alternative zur Konfiguration des U61000 finden. Letztlich hat man sich dafür entschieden nach dem Wafertest den Schaltkreis noch einmal einem Ätzprozess zu unterziehen. Die individuelle Bearbeitung erreichte man mit Elektronenstrahllithografie. Dazu wurde ein Photolack aufgetragen und selektiv mit einem Elektronenstrahl belichtet. Der darauffolgende Ätzprozess beseitigte dann nur die vorher ausgewählten Fuses. Das obige Bild stammt aus dem Vortrag "Entwicklung des Megabitspeichers U61000 1986 bis 1990" von Dr. Jens Knobloch. Es zeigt, wie ein so konfigurierter Sicherungsstreifen ausgesehen hat. Im zweiten U61000, der im August 1989 produziert wurde, sind durchtrennte Sicherungselemente zu sehen.

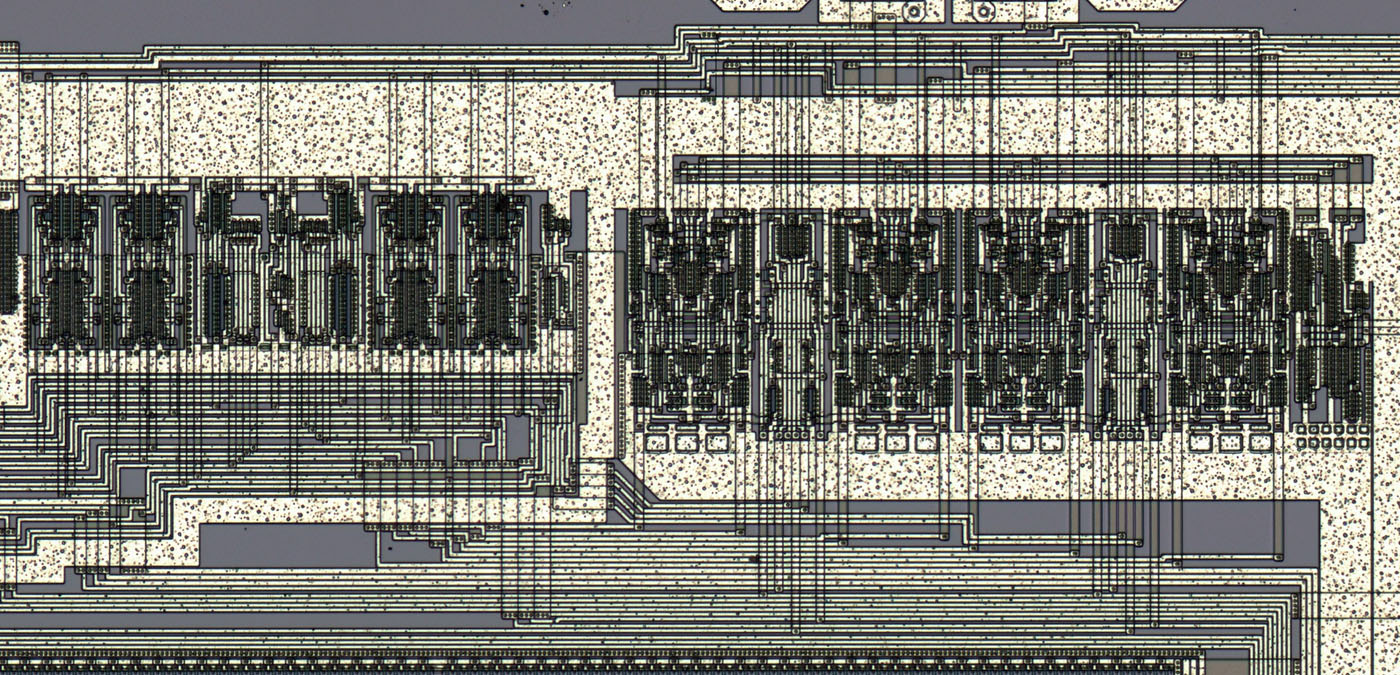

An der unteren und an der oberen Kante des Dies befinden sich jeweils vier Sicherungsstreifen. Jedem Speicherblock ist ein Streifen der oberen Kante und ein Streifen der unteren Kante zugeordnet. Der obere Streifen ermöglicht die Konfiguration der Reservespalten. Der untere Streifen konfiguriert die Reservezeilen.

Dr. Jens Knobloch berichtet, dass ohne die Reservezellen zum Jahreswechsel 1989 / 1990 eine Ausbeute von 3% erreicht werden konnte. Die Nutzung der Redundanz erhöhte den Wert auf 10%. Der hier dokumentierte U61000 scheint einer der sehr guten Speicher zu sein, da keine der Fuses unterbrochen wurde.

Die Sicherungsstreifen der Zeilenauswahl befinden sich paarweise dort, wo zwei Speicherblöcke aneinanderstoßen. Sie sind mit den differentiellen Steuersignalen A2-A7 der Zeilenauswahl verbunden.

Aus dem unteren Bereich werden den Sicherungsstreifen zusätzlich die differentiellen Steuersignale der Adressleitung A1 zugeführt. Die Sicherungselemente sind von mehreren Rahmen umgeben, die unterschiedliche Potentiale tragen. Direkt bei den Sicherungselementen ist das Substratpotential Ubb platziert. Darauf folgt das positive Versorgungspotential Ucc. Unterhalb des Ucc-Rahmens befindet sich eine Steuerleitung und schließlich das Uss-Potential. Beim Öffnen der Passivierungsschicht besteht die Gefahr, dass Verschmutzungen in das System eingebracht werden. Es könnte sein, dass die Rahmen mit ihren elektrischen Felder ein Wandern dieser Verschmutzungen verhindern sollen.

Die von oben eintreffenden differentiellen Steuerleitungen sind mit Transistoren unter dem äußersten, breiten Uss-Rahmen verbunden. Liegt dort ein Signal an, so wird eine gemeinsame Steuerleitung (blau) mit dem Uss-Potential verbunden. Da es sich um differentielle Signale handelt, ist die Steuerleitung in der hier vorliegenden Konfiguration immer mit dem Uss-Potential verbunden. Trennt man Sicherungen auf, so kann man dafür sorgen, dass bei gewissen Adressen die Steuerleitung offen bleibt. Die Schaltung links des Sicherungsstreifens wertet das Potential der Steuerleitung aus.

Während der Sicherungsstreifen die Signale der Adressleitungen A1 bis A7 auswertet, wird die darauffolgende Schaltung (orange) zusätzlich über die Adressleitung A8 gesteuert. So sind auch die Reservezeilen nur dann aktiv, wenn der zugehörige Speicherblock aktiv ist. Letztlich wird ein Steuersignal generiert, dass die zwei Reservezeilen aktiviert (gelb). Ein weiteres Steuersignal aktiviert eine Schaltung, die die Adressleitung A0 auswertet (rot). Sie sorgt für die Umschaltung zwischen den beiden Reservezeilen. Gleichzeitig wird die A0-Auswertung der normalen Zeilenauswahl deaktiviert (weiß). Damit ist sichergestellt, dass bei den Adressen, bei denen die Reservezeilen aktiv werden, die normale Zeilenauswahl deaktiviert bleibt.

Im Detail sind die unterschiedlichen Schaltungen zur Zeilenauswahl gut erkennbar. Die zwei Steuerleitungen, die aus der Adressleitung A0 erzeugt werden, führen direkt von unten nach oben. Die Steuerleitung zur Aktivierung der Reservezeilen führt über die linke Seite in den obersten Bereich der Zeilenauswahl.

Die Steuerleitung zur Aktivierung der Reservezeilen führt auch zum linken Bereich des Speicherblocks. Das bedeutet, dass die Reservezeilen in beiden Hälften des Speicherblocks immer gleich weit in den nutzbaren Adressbereich geschoben werden. Gleichzeitig sorgt die Umschaltung der Zeilenpaare über die Adressleitung A0 dafür, dass die Paare nur gemeinsam verschoben werden können. Beides schränkt die Einsatzmöglichkeiten der Reservezeilen stark ein. Eine variablere Steuerung würde allerdings eine sehr viel komplexere Auswahl und Steuerung notwendig machen. Hier musste man einen Kompromiss finden.

An der oberen Kante werden zur Verschiebung der Reservespalten die differentiellen Signale der Adressleitungen A1 bis A8 herangezogen. Während man die Reservezeilen in den Speicherhälften nur innerhalb von 128 Adressen konfigurierbar machen musste, waren bei der Spaltenauswahl 256 Adressen zu bedienen. Daher befindet sich hier auch die Adressleitung A8 unter den Sicherungselementen. Ansonsten funktioniert die Schaltung ähnlich wie die Schaltung zur Zuordnung der Reservezeilen.

Die Reservespalten befinden sich an der oberen Kante des Speicherbereichs. Man kann die unterschiedliche Ansteuerung über die dünne, unter der Metalllage nach oben führende Leitung gerade noch erkennen.

In der linken oberen Ecke des Dies befinden sich mehrere Schaltungsteile, bei denen erkennbar ist, dass es sich um Gruppen von vier gleichen Blöcken handelt. Dieses und die folgenden Bilder sind um 90° gedreht. Die Details der Schaltungen lassen sich nicht erkennen. Elektrisch ist der Bereich eingebunden zwischen den vier Datenleitungen der vier Speicherblöcke und den Endstufen für die Datenausgabe. Auch das Signal am Dateneingang wird hier her geführt. Man kann davon ausgehen, dass in diesem Bereich das notwendige Multiplexing und Demultiplexing erfolgt.

Bei genauerer Betrachtung der Schaltung zur Datenausgabe zeigt sich, dass dort vier gleiche Schaltungsblöcke in zwei symmetrischen Paaren integriert wurden. Offensichtlich handelt es sich um vier vollständige Datenausgänge. In seinem Artikel "Der Megabitspeicher U61000" erwähnt Dr. Jens Knobloch einen 4fach-Testmodus. Anscheinend konnte man die vier Blöcke parallel testen. Das ist für sich noch nichts Außergewöhnliches. Es überraschend allerdings, dass man tatsächlich vier Endstufen inklusive der notwendigen Ansteuerung integriert hat.

Überträgt man die drei zusätzlichen Ausgänge auf die Bondpads, so bleiben nur noch zwei Bondpads, deren Funktionen unklar bleiben (X1, X2). Es ist gut möglich, dass zumindest eines der Bondpads einen Testmodus aktiviert oder steuert.

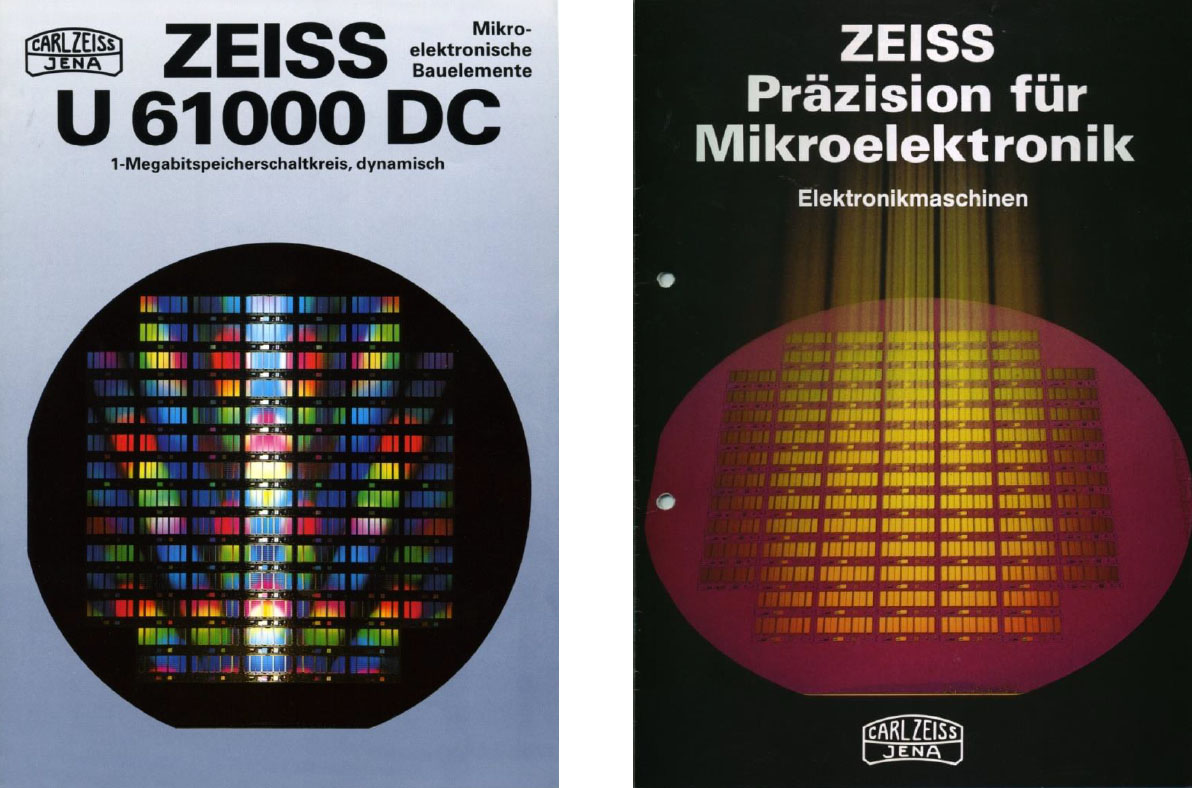

Auf diesem Bild von Dr. Jens Knobloch ist ein Wafer zu sehen, der die Strukturen des U61000 trägt. Es handelte sich um 5" große Wafer, auf denen 90 der U61000 Bausteine integriert werden konnten. Bei diesem Entwicklungsstand ist jedem U61000 noch eine große Teststruktur zur Seite gestellt. In der Serienproduktion wäre diese entfallen und man hätte entsprechend merklich mehr Bausteine auf einen Wafer integrieren können. Weltweit hatte man 1990 schon die Serienfertigungen auf 8" Wafern gestartet.

Hier sind zwei weitere Bilder von U61000-Wafern zu sehen, die Carl Zeiss Jena zu Werbezwecken genutzt hat.

In der Zeitschrift Mikroprozessortechnik (Heft 10, 1989) findet sich das obige Bild des U61000. Dort sieht man auch die großen Teststrukturen.

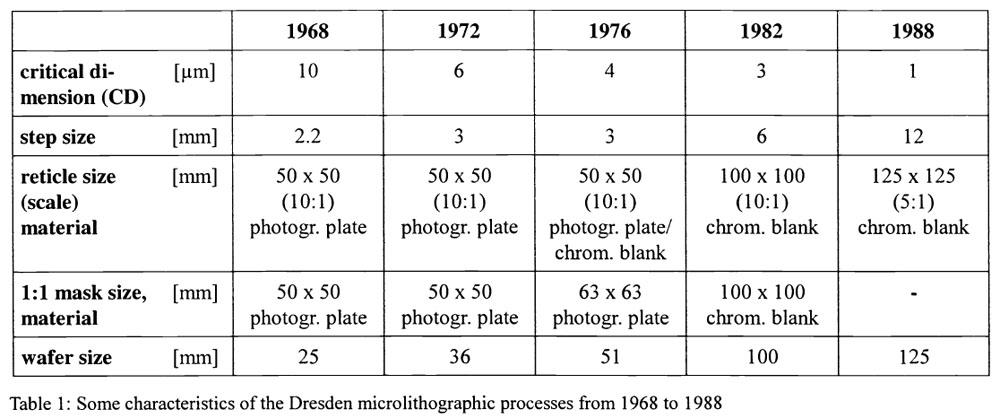

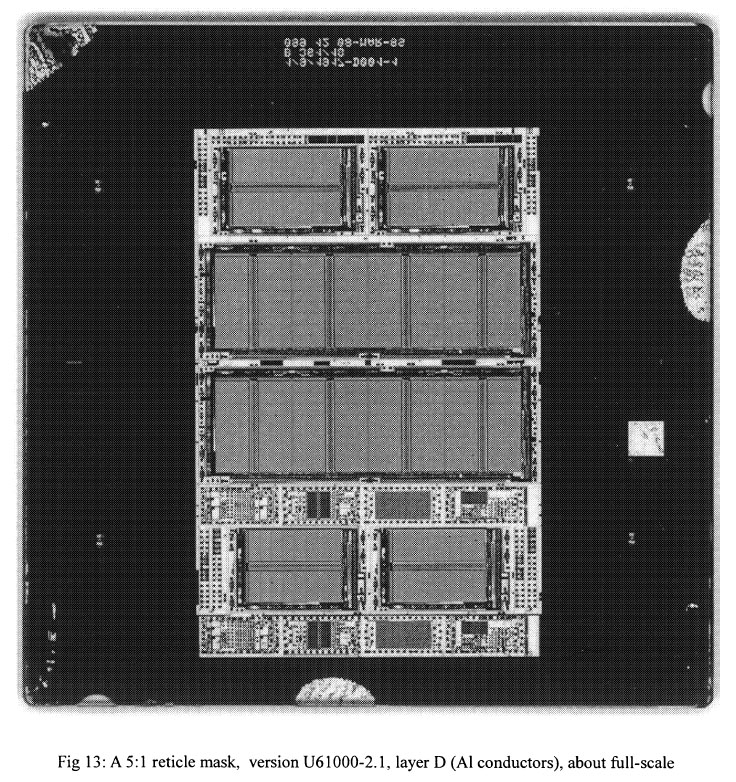

Die Veröffentlichung "Looking back: Artwork and Mask Making in Dresden for the East German Megabit Chip Project" von Hans W. Becker liefert tiefe Einblicke in die damals verwendete Technik zur Belichtung der Wafer. Die obige Tabelle und die folgenden Bilder wurden aus dieser Veröffentlichung übernommen.

Carl Zeiss Jena lieferte bei der Entwicklung des Belichtungsprozesses einen großen Beitrag. Für den U61000 ging man über auf 125mm x 125mm große Masken. Die Masken bestanden aus mit Chrom beschichtetem Glas. Die Strukturen wurden mit der Elektronenstrahlbelichtungsanlage ZBA21 aufgebracht. Die Belichtung der Wafer erfolgte direkt mit dieser Maske und dem Wafer-Stepper AÜR. Der AÜR nutzte Licht mit einer Wellenlänge von 436nm und konnte 25 Wafer pro Stunde belichten.

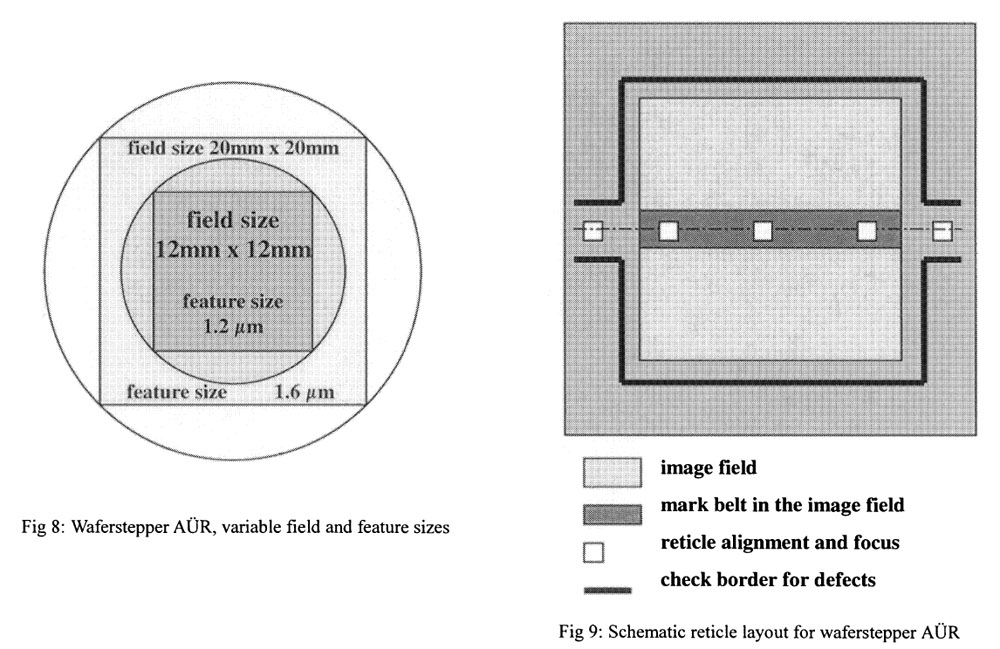

Der Waferstepper AÜR bot die Option zwei verschieden große Flächen zu belichten. Auf eine Fläche von 20mm x 20mm ließen sich minimale Strukturbreiten von 1,6µm abbilden. Die Abbildungsleistung auf eine Fläche von 12mm x 12mm wird teilweise mit 1,2µm und teilweise mit 1,0µm angegeben. Später hat man noch eine zweite Generation des AÜR entwickelt, der auf einem Bildfeld von 12mm x 12mm Strukturbreiten von 1,0µm darstellen konnte. Auf einer Fläche von 10mm x 10mm waren 0,8µm möglich.

Das rechte Bild zeigt, dass die Fläche von 12mm x 12mm beim AÜR nicht uneingeschränkt verwendet werden konnte. In der Mitte befindet sich ein Streifen, der unter anderem Strukturen enthält, die zum Ausrichten und Fokussieren benötigt wurden. Die Zweiteilung reduzierte die Nutzfläche, war aber gleichzeitig gewollt. Die doppelte Platzierung des Designs hat man genutzt, um Fehler auf der Maske mit Hilfe eines Vergleichs der beiden Hälften zu erkennen. Fehler konnten man teilweise mit einem Laser korrigieren.

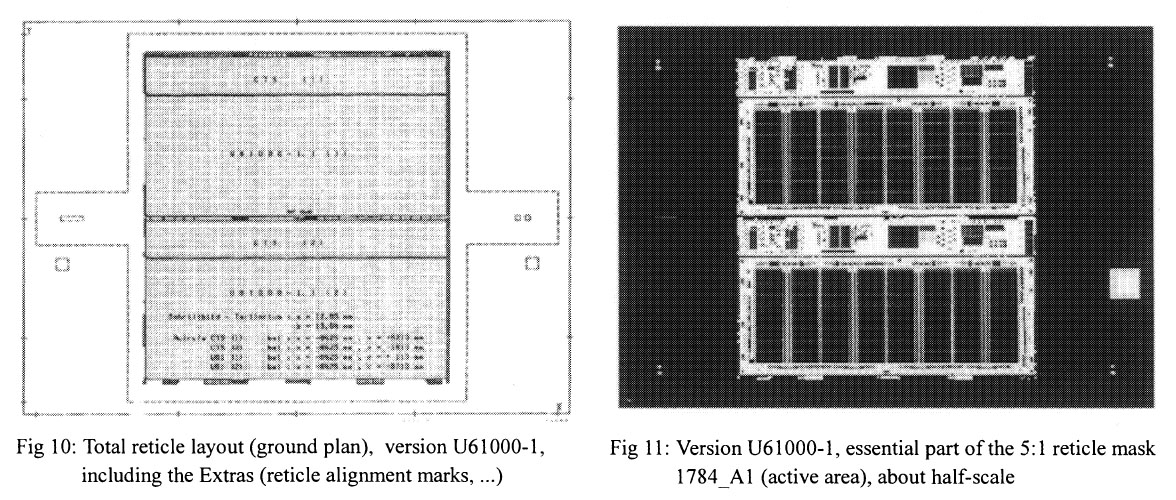

Hier ist links die Aufteilung der Masken beim U61000-1 zu sehen. Sie wurden im Mai 1988 produziert. Durch den Abbildungsmaßstab von 5:1 sind die Masken deutlich größer als der Speicher. Die zwei großen grauen Flächen sind die beiden Speicherbausteine. Über jedem Speicher befindet sich der Testchip CT5 mit seinen vielen Teststrukturen. Dr. Jens Knobloch spricht vom Technologietestfeld PTF5. Im rechten Bild ist die Maske für die aktiven Flächen dargestellt. Dort sind deutlich die Strukturen der Speicher und der Testbereiche zu erkennen.

Die Gesamtfläche der Abbildung beträgt 12,95mm x 13,86mm und ist somit merklich größer als die spezifizierten 12mm x 12mm des AÜR Wafersteppers. Es gelang dennoch funktionsfähige Chips damit zu produzieren.

Hier ist die Maske für die Aluminiumlage des U61000-2.1 zu sehen, die im Februar 1989 produziert wurde. Darauf sind noch mehr Teststrukturen platziert. Die Gesamtfläche der Abbildung beträgt 12,70mm x 18,00mm, allerdings wird nicht die komplette Fläche zur Belichtung genutzt. Die unteren Teststrukturen dienen lediglich der Fehlersuche auf der Maske.

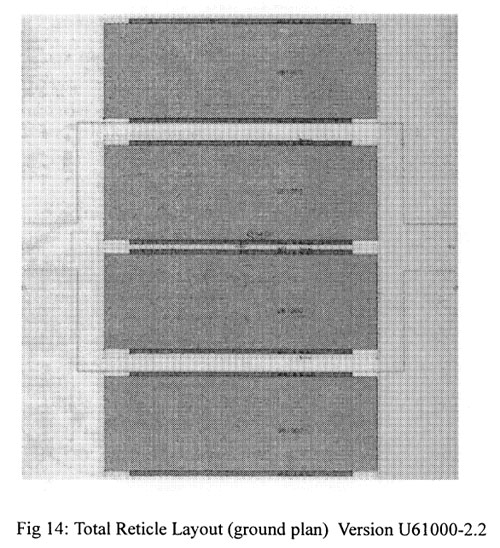

Das obige Bild zeigt die Aufteilung der Masken für den U61000-2.2. Dieser Maskensatz wurde im Oktober 1989 produziert. Die mittleren beiden Blöcke stellen die zu belichtenden U61000 dar und werden auf einer Fläche von 12,70mm x 10,30mm abgebildet. Die äußeren Blöcke dienen wieder nur der Fehlersuche.

Da bei der finalen Varianten die großen Testbereiche fehlten, konnte man mehr Speicherbausteine auf den 5"-Wafern platzieren. Geht man davon aus, dass im Durchschnitt über die verschiedenen Varianten 120 Elemente auf einem Wafer Platz fanden und geht man von einer mittleren Ausbeute von 10% aus, so kann man abschätzen, dass ungefähr 2.500 Wafer des U61000 produziert wurden. Da es sich um technologisches Neuland handelte, kann man davon ausgehen, dass parallel dazu einige Testwafer hergestellt und verworfen wurden.

Der U61000 wurde nie in Serie produziert. Die Pilotproduktion erfolgte im Zentrum für Mikroelektronik Dresden. Für die Serienproduktion war das ZMD aber nicht ausgerüstet. Dafür hätte eine eigene Produktion in Erfurt aufgebaut werden sollen. Bevor es dazu kam, erfolgte die Wiedervereinigung Deutschlands. Der U61000 war auf dem internationalen Markt nicht ansatzweise konkurrenzfähig. Das zeigt die obige Tabelle recht deutlich. Sie ist aus der Dissertation "Wafer-Stepper und Megabit-Chip" von Dr. Otto Bernd Kirchner entnommen. Die Tabelle dokumentierten die Kosten und Preise der DDR-DRAM-Bausteine im Jahr 1989. Der Weltmarktpreis eines 1MBit-DRAMs war um einen Faktor 100 niedriger als die Herstellungskosten des U61000.

Der U61000 hatte nach der Wiedervereinigung keine Zukunft. Aus dem generierten Know-How entstand aber dennoch ein Produkt. Wie bei Speichern üblich, hat man auch beim U61000 versucht die Schaltung möglichst unempfindlich gegen radioaktive Strahlung zu machen. Nach der Wiedervereinigung tat man nun genau das Gegenteil und entwickelte aus dem Speicher einen Strahlungssensor. Daraus ging die Firma Megarad hervor. Später entstand daraus die Firma SARAD.

Neben dem U61000 gab es einen U60998. Zum U60998 finden sich keine offiziellen Dokumente. Angeblich handelt es sich um U61000 mit nicht korrigierbaren Fehlern. Dabei muss es sich nicht um vollständig defekte Zellen handeln. Es kann sein, dass lediglich teileweise gewisse Spezifikationen nicht ganz eingehalten werden. Die U60998 könnte man in Anwendungen einsetzen, bei denen einzelne fehlerhafte Zellen weniger kritisch sind, zum Beispiel als Seitenspeicher in einem Drucker. Angeblich wurden schon U60998 getestet, bei denen die vollen 1MBit beschrieben und fehlerfrei gelesen werden konnten.