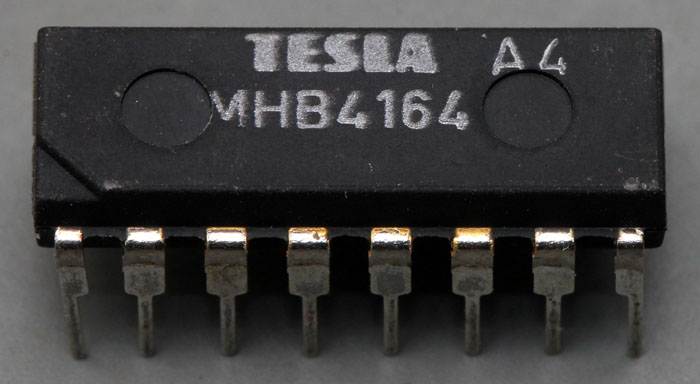

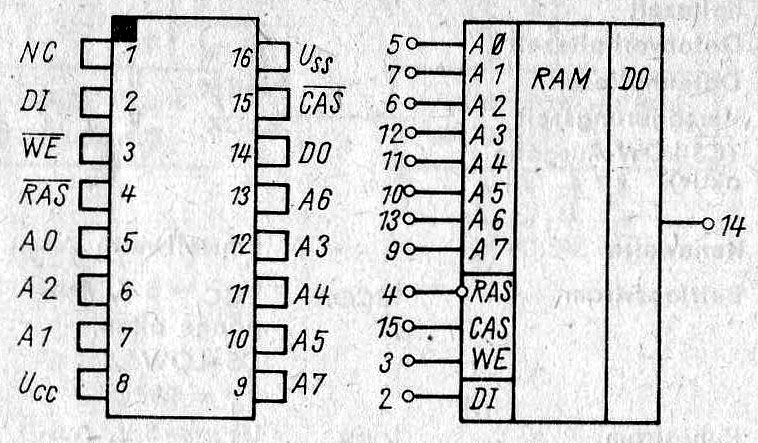

Der Tesla MHB4164 ist ein DRAM mit einer Speichertiefe von 64kBit. A4 steht für eine Produktion im April 1990.

Wie sich gleich zeigen wird, handelt es sich tatsächlich um einen im Zentrum für Mikroelektronik Dresden entwickelten U2164, wie er hier dokumentiert ist. Das Gehäuse und die dreieckige Kennzeichnung des Pin 1 lassen den Schluss zu, dass der Baustein im Halbleiterwerk Erfurt für Tesla hergestellt und spezifisch bedruckt wurde.

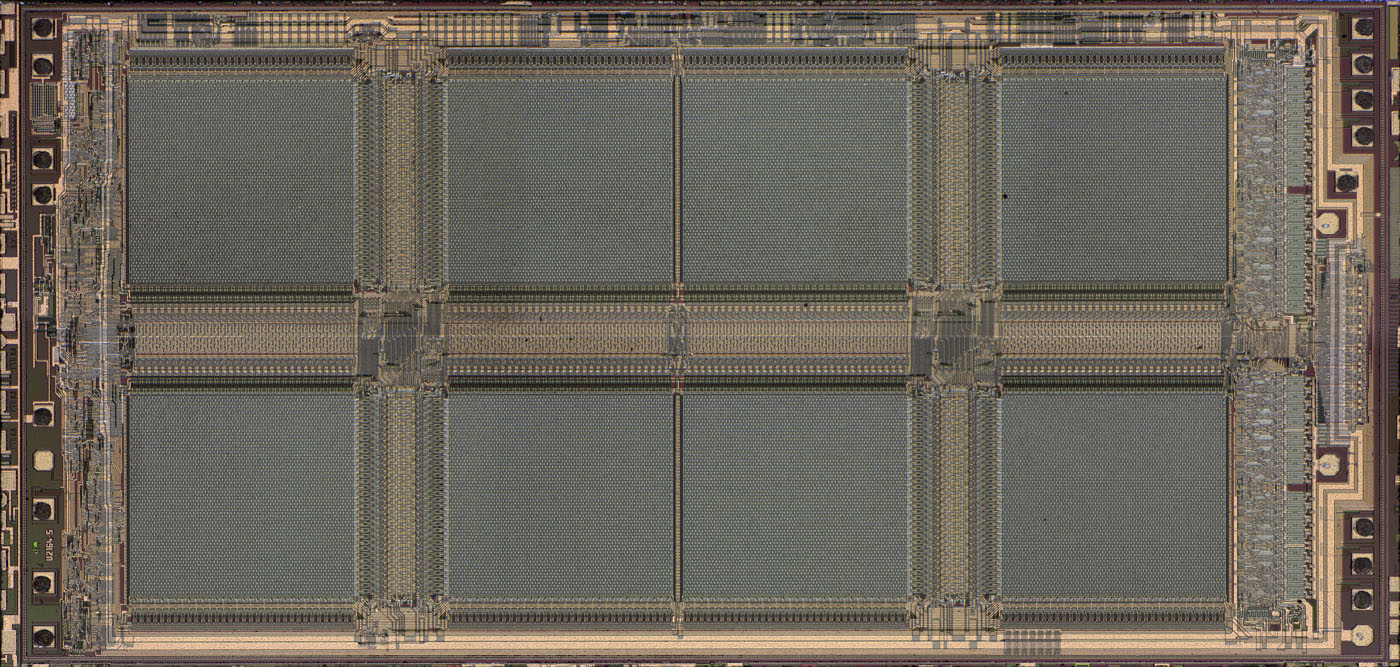

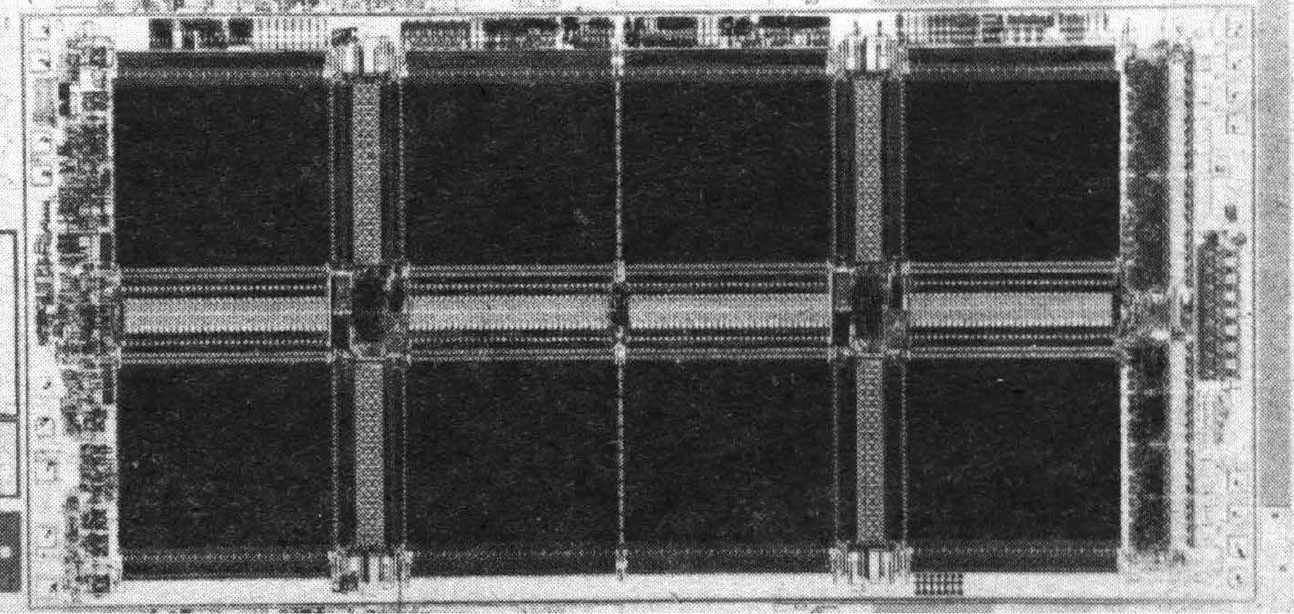

Die Abmessungen des Dies betragen 7,1mm x 3,4mm.

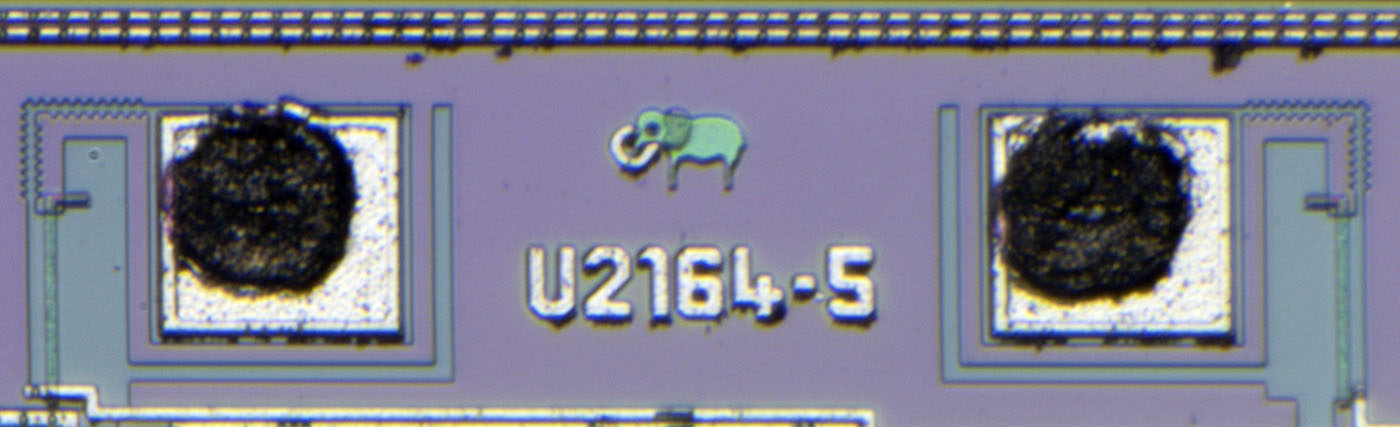

Die Beschriftung an der linken Kante des Dies zeigt, dass es sich um einen U2164 handelt. Die Zahl 5 am Ende kennzeichnet die fünfte Revision. Über der Bezeichnung ist eine Art Elefant oder Mammut abgebildet. Das erinnert stark an den Elefanten auf dem 16kBit-DRAM ITT 4116 der sich im CM8116 (SM8116) von Mikroelektronika Botevgrad befindet. Eventuell handelt es ich um eine Anspielung auf das gute Gedächtnis eines Elefanten.

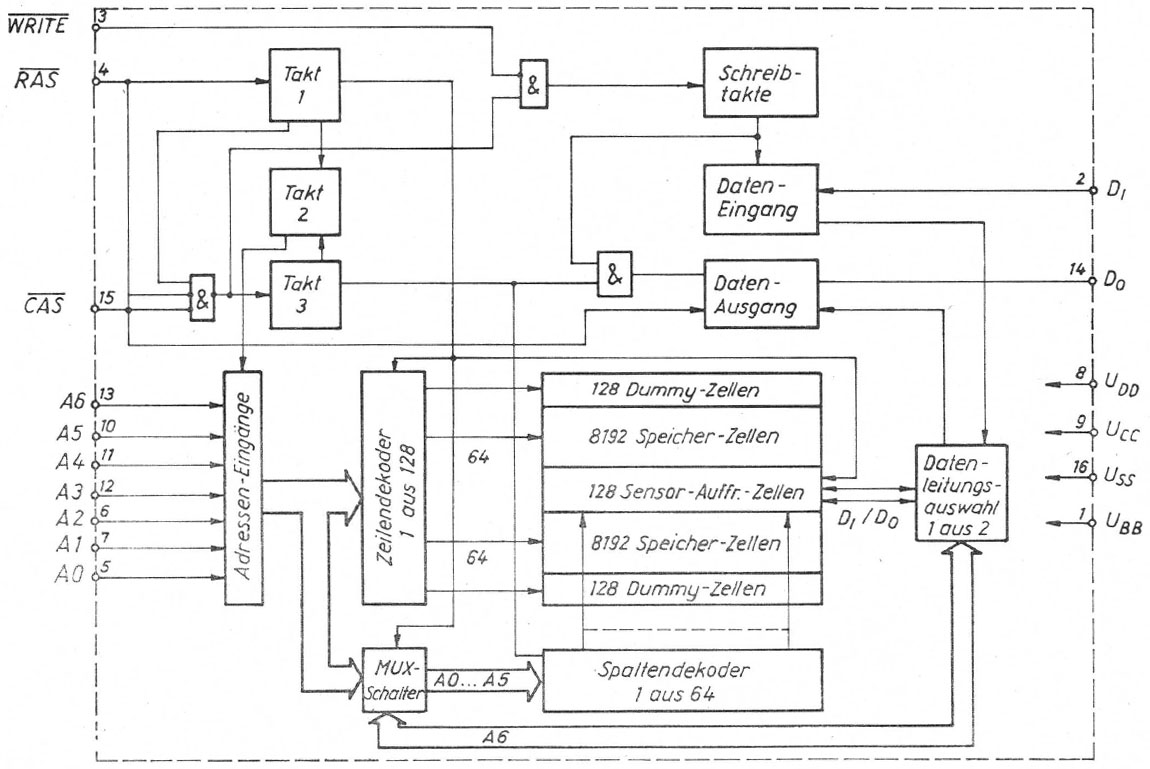

Um die Funktionsweise des U2164 zu verstehen, ist es hilfreich zuerst einen Blick auf das Blockschaltbild des U256 zu werfen. Der U2164 basiert auf diesem 16kBit-Baustein.

Die Signale RAS, CAS und WRITE steuern drei Taktgeneratoren, die derart verknüpft sind, dass die notwendigen Funktionen zur richtigen Zeit abgearbeitet werden. Die 7 Adressleitungen werden über einen Multiplexer zur Zeilen- oder zur Spaltenauswahl geführt. Der Zeilendekoder generiert aus 7 Adressleitungen 128 Steuersignale, die es ermöglichen eine Zeile des Speicherbereichs auszuwählen.

Der Speicher besteht aus zwei 8kBit-Bereichen. Jeder 8kBit-Bereich enthält 64 Zeilen und 128 Spalten. Neben den 128 Zeilen, die dem Speichern von Daten dienen, besitzt jeder 8kBit-Bereich eine Zeile mit 128-Dummy-Zellen. Die Dummy-Zellen liefern die Referenzwerte für die Ausleseverstärker.

In der Mitte des Speicherbereichs ist laut Datenblatt neben den Ausleseverstärkern auch die Refresh-Schaltung integriert. Nach dem Auslesen einer Zeile sind deren Informationen nicht mehr im Speicher vorhanden und müssen erneut in die Speicherzellen geschrieben werden. Diese Aufgabe übernimmt die Refresh-Schaltung. Die Ladung, die in den integrierten Kondensatoren abgespeichert ist, altert aber auch durch Leckströme sehr schnell. Aus diesem Grund muss spätestens alle 2ms der komplette Inhalt des Speichers einmal aufgefrischt werden.

Obwohl man nur eine einzelne Speicherzelle des DRAM adressiert, wird immer eine vollständige Zeile ausgelesen. Der Spaltendekoder nutzt lediglich 6 Bits, so dass immer 2 der 128 Spalten gleichzeitig aktiv sind. Die Auswahl welche Daten der zwei aktiven Zellen ausgegeben werden sollen erfolgt außerhalb des Speicherbereichs über das siebte Bit. Das Schreiben von Daten erfolgt nach dem gleichen Muster.

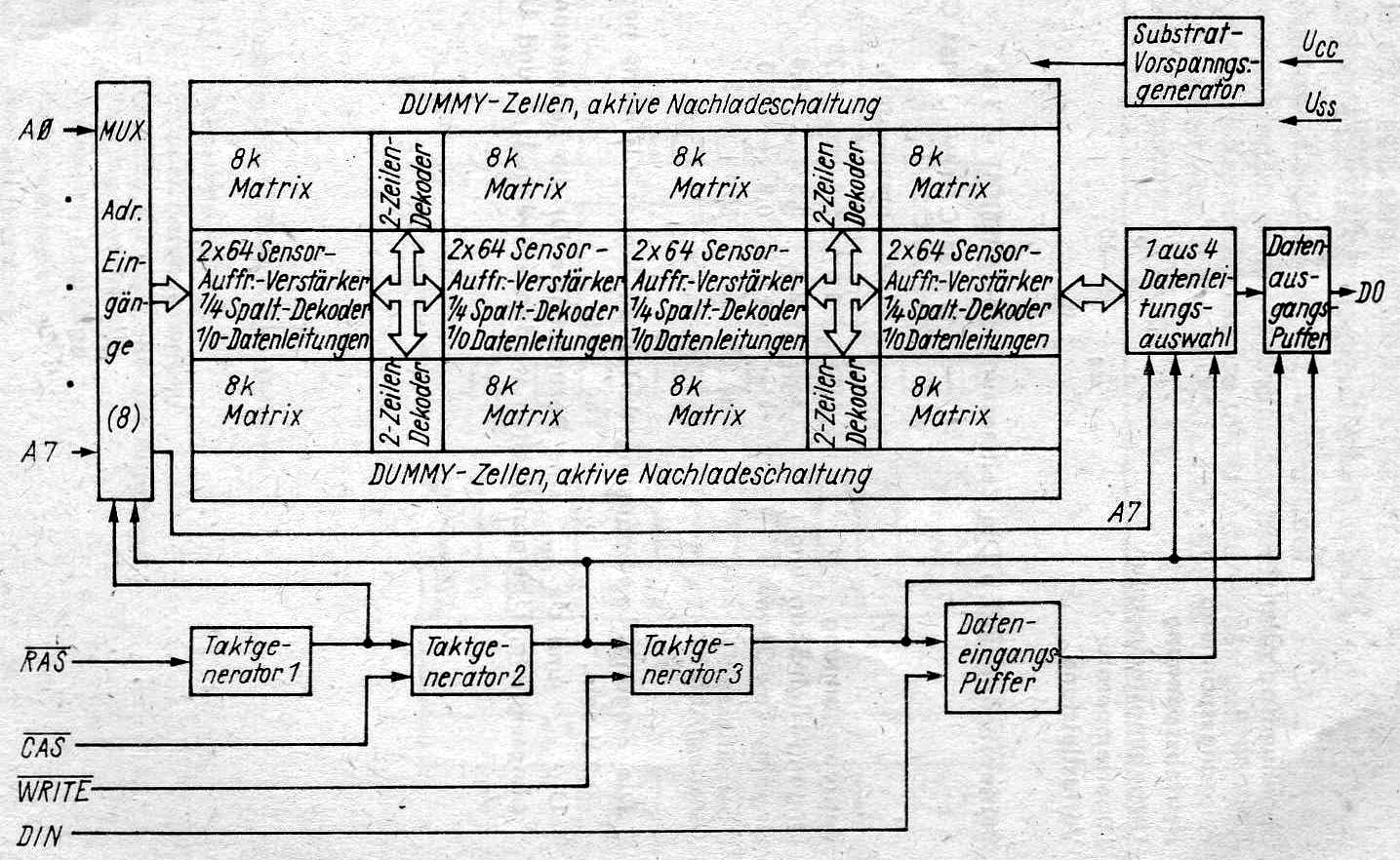

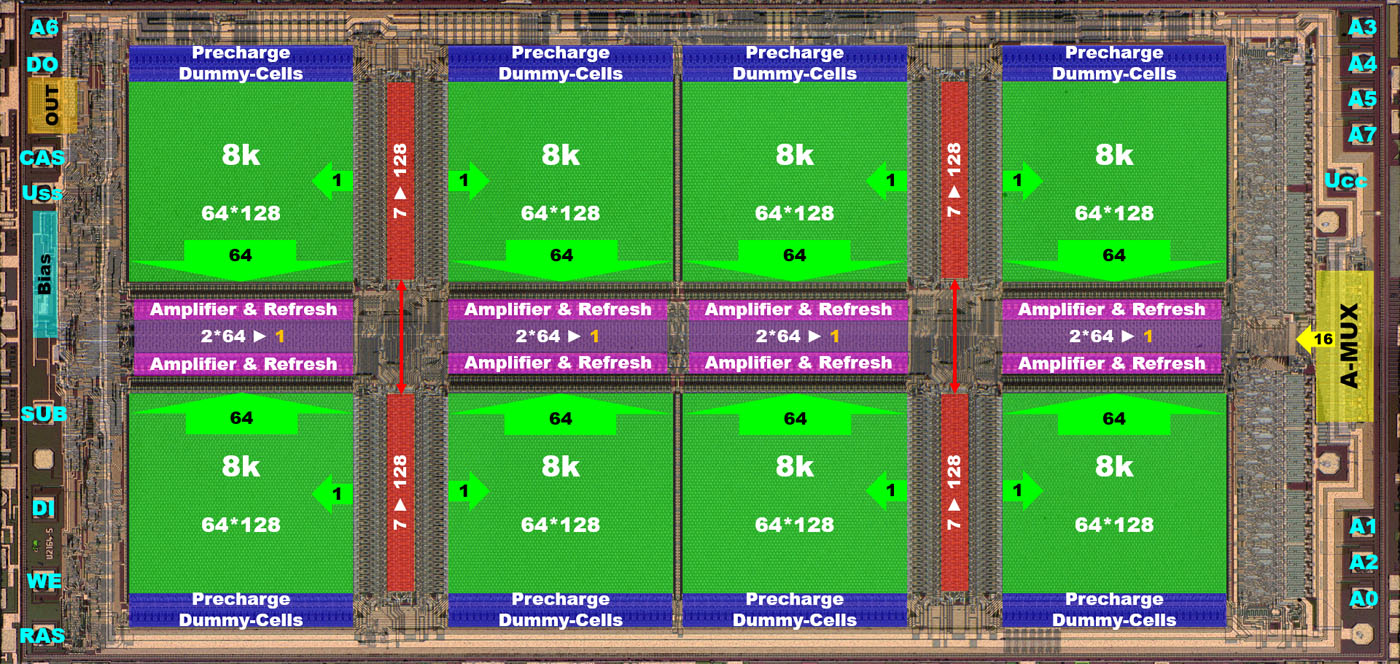

Das Blockschaltbild im Datenblatt des U2164 zeigt, dass dort die Strukturen des U256 viermal abgebildet wurden. Mittig befinden sich für jede 8kBit-Matrix 64 Leseverstärker. Die Dekoder in den Spalten zwischen den 8kBit-Matrizen aktivieren in jeder Matrix eine Zeile. So liefert der Speicherbereich insgesamt vier Datenleitungen, von denen eine über das Adressbit 7 ausgewählt wird. Ein Bit ist hier ausreichend, weil es über die Zeilen- und die Spaltenauswahl doppelt genutzt werden kann.

Der U256 benötigt eine +12V, eine +5V und eine -5V Versorgungsspannung. Beim U2164 ist eine +5V-Versorgung ausreichend. Der Baustein erzeugt selbst eine negative Spannung für das Substrat.

In der "Radio Fernsehen Elektronik" von 08/1989 findet sich ein ausführlicher Artikel über den U2164. Dort ist auch das Die abgebildet, das dem Die im MHB4164 zu entsprechen scheint. Die Abmessungen wären demnach 7,07mm x 3,4mm und es kamen mehr als 140.000 Transistoren zum Einsatz.

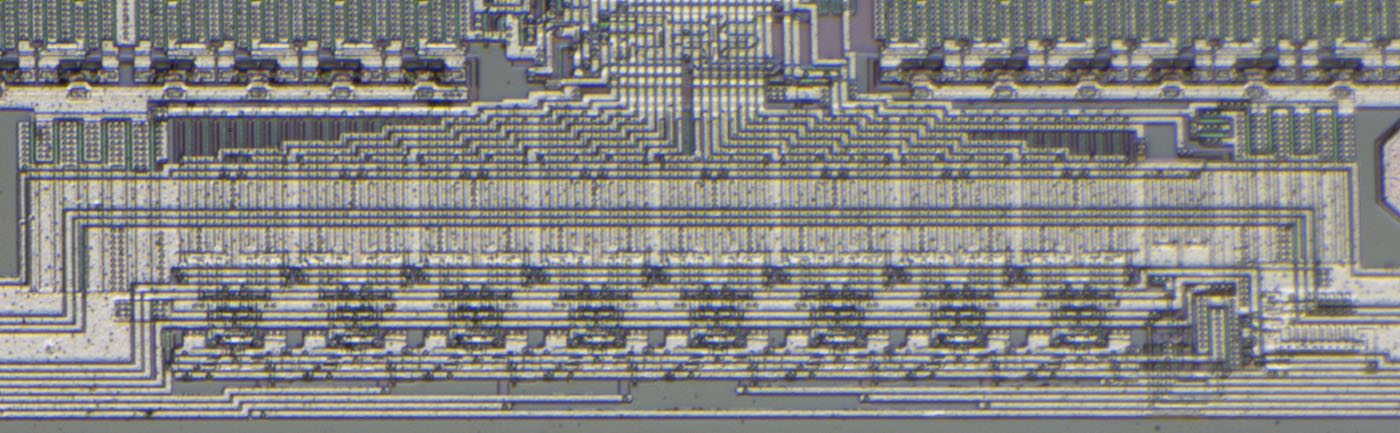

Viele Funktionsblöcke lassen sich auf dem Die identifizieren. Die 8k-Speicherbereiche (grün) bieten effektiv 64 Spalten und 128 Zeilen. Die Radio Fernsehen Elektronik gibt an, dass insgesamt 2kBit als Reservezellen integriert wurden, auf die umgeschaltet werden kann, wenn sich in den Speicherbereichen Produktionsfehler befinden. Wie die Umschaltung auf die Reservezellen erfolgt, ist im Rahmen des U2164 beschrieben. An der oberen und der unteren Außenkante befinden sich die Dummy-Zellen, die notwendig sind, um die Speicherzellen richtig auslesen zu können (blau). Noch etwas weiter außen sind die Schaltungsteile integriert, die die Bit-Leitungen und die Dummy-Zellen mit einem Referenzpegel vorladen (blau).

Zwischen den Speicherblöcken befindet sich die Zeilenauswahl (rot), die mit sieben Adressleitungen in jedem Block eine der 128 Zeilen aktiviert. Die Speicherbereiche geben jeweils 64 Signale aus, die von 64 Leseverstärkern (rosa) aufbereitet werden. Die Leseverstärker schreiben die aktive Zeile auch wieder vollständig zurück. Diese Zeile muss dann erst wieder nach 2ms aufgefrischt werden. Der Spaltendekoder (lila) wählt eine der Spalten aus. So ergeben sich insgesamt vier aktive Zellen. Die Schaltung zur Selektion einer Zelle ist nicht direkt erkennbar.

An der linken Kante findet sich die Push-Pull-Endstufe des Ausgangs (orange) und die Schaltung zur Erzeugung der negativen Substrat-Spannung (türkis). An der rechten Kante ist der Adressmultiplexer zu erkennen, der die Adressleitungen zwischen der Zeilen- und der Spaltenauswahl hin und her schaltet (gelb).

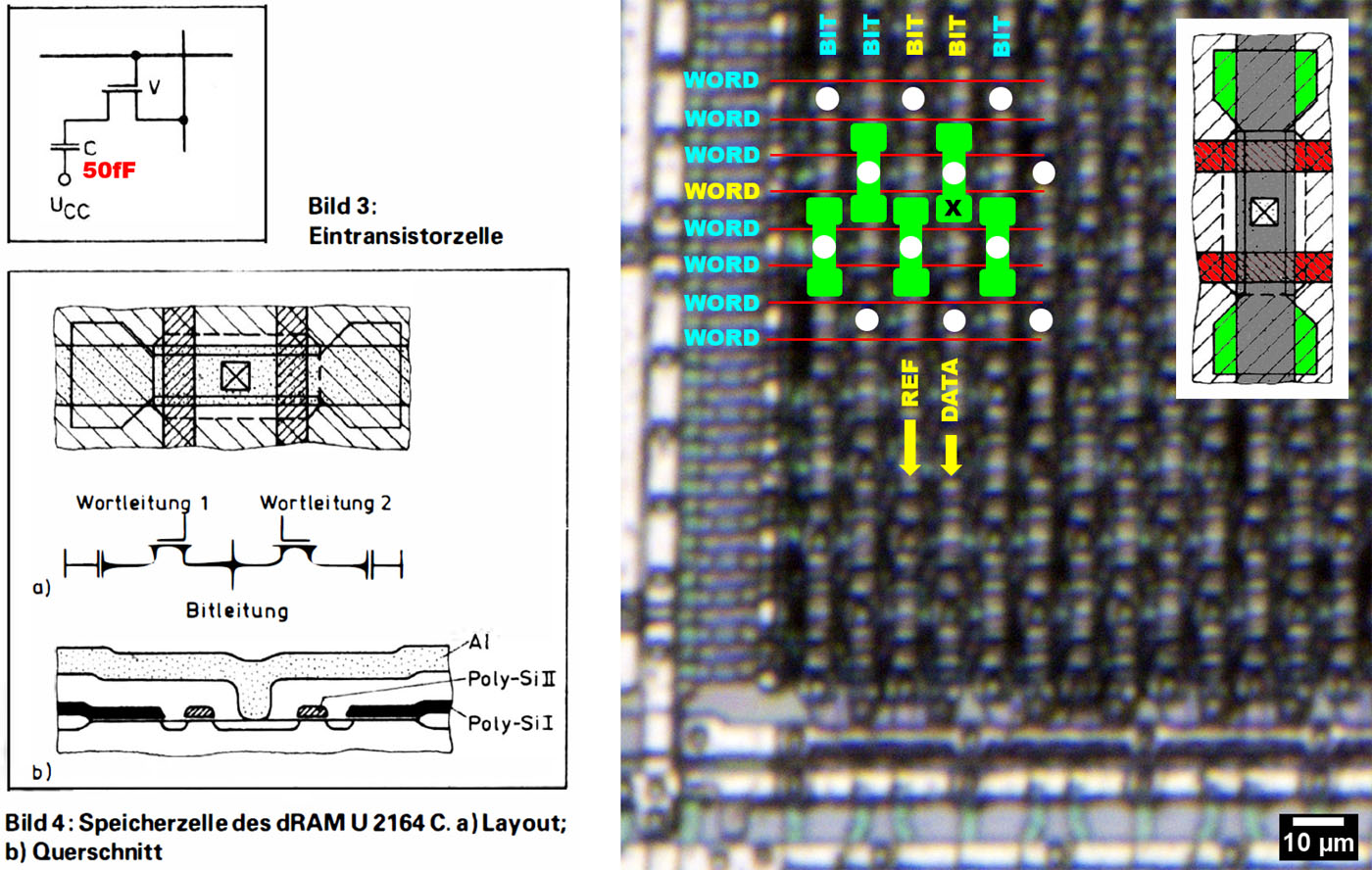

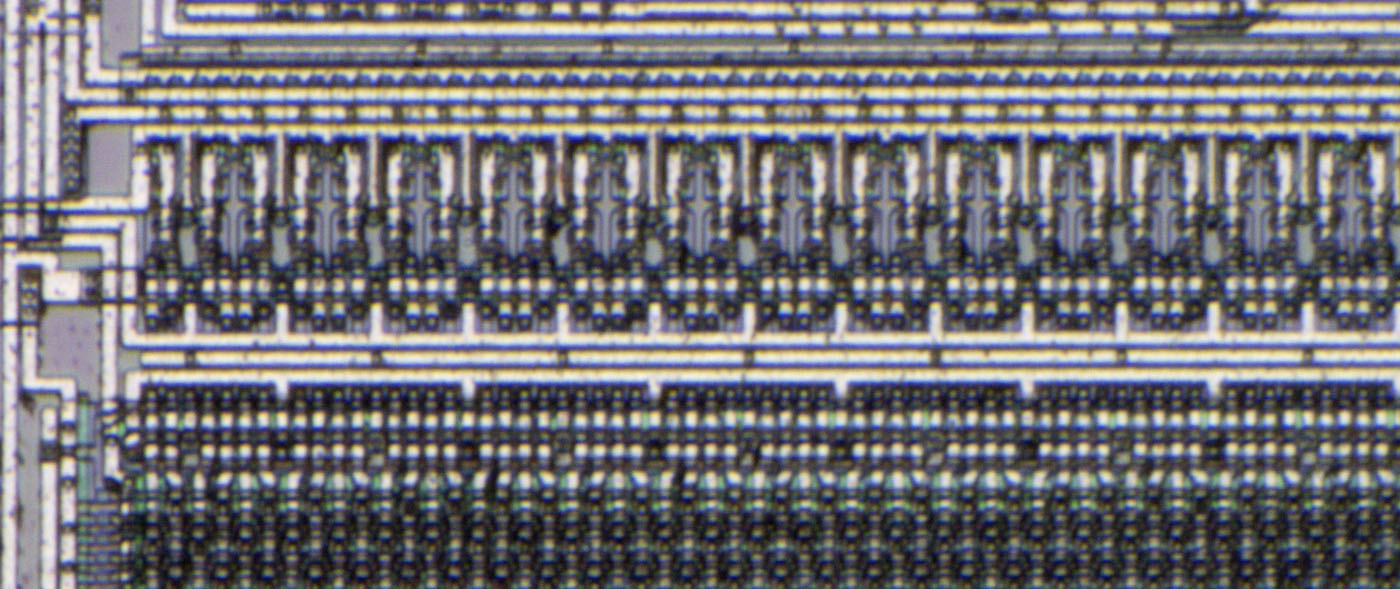

In der Radio Fernsehen Elektronik ist der Aufbau der Speicherzellen ausführlich beschrieben. Eine Speicherzelle besitzt demnach eine Speicherkapazität von 50fF. Es handelt sich um den klassischen DRAM-Aufbau mit einem Kondensator und einem Auswahltransistor. Der Artikel zeigt auch den tatsächlichen Aufbau der Speicherzellen. Eine Bit-Leitung, dargestellt durch die Metalllage, bedient immer zwei Speicherzellen. Die Polysiliziumlage 2 bildet gleichzeitig die Wortleitungen und die Gateelektroden der Auswahltransistoren ab. Die Polysiliziumlage 1 formt eine verhältnismäßig große Fläche, die als Kondensator dient.

Der Speicherbereich enthält tatsächlich nicht 64 sondern 128 Spalten. Jeder Leseverstärker ist an zwei benachbarte Spalten angeschlossen und wertet die Differenz der Spalten aus. Die Anordnung der Speicherzellen sorgt dafür, dass bei den zwei Spalten eine Spalte die gewünschte Information enthält, während die andere Spalte nur den Referenz-Wert der zugehörigen Dummy-Zelle liefert. Diese Art der differentiellen Auswertung mit dem Referenzwert einer Dummyzelle ist üblich in solchen Speichern. Die Aufteilung der Spalten in der Art, dass die zwei aktiven Spalten direkt nebeneinander liegen, reduziert zusätzlich die sogenannte Soft Error Rate. Damit wird die Anzahl von sporadischen Datenfehlern beschrieben, die nicht auf Hardwarefehler zurückzuführen sind. Ursachen sind hauptsächlich Alpha-Strahler im Package-Material, kosmische Strahlung und Neutronenstrahlung. Bereits kleine Mengen ionisierender Strahlung können einen Stromfluss erzeugen, der zum Verlust von Informationen führt. Die parallel geführten Leitungen von Daten- und Referenzsignal erhöhen die Wahrscheinlichkeit, dass eine Ionisierung beide Leitungen gleich beeinflusst und die Information erhalten bleibt.

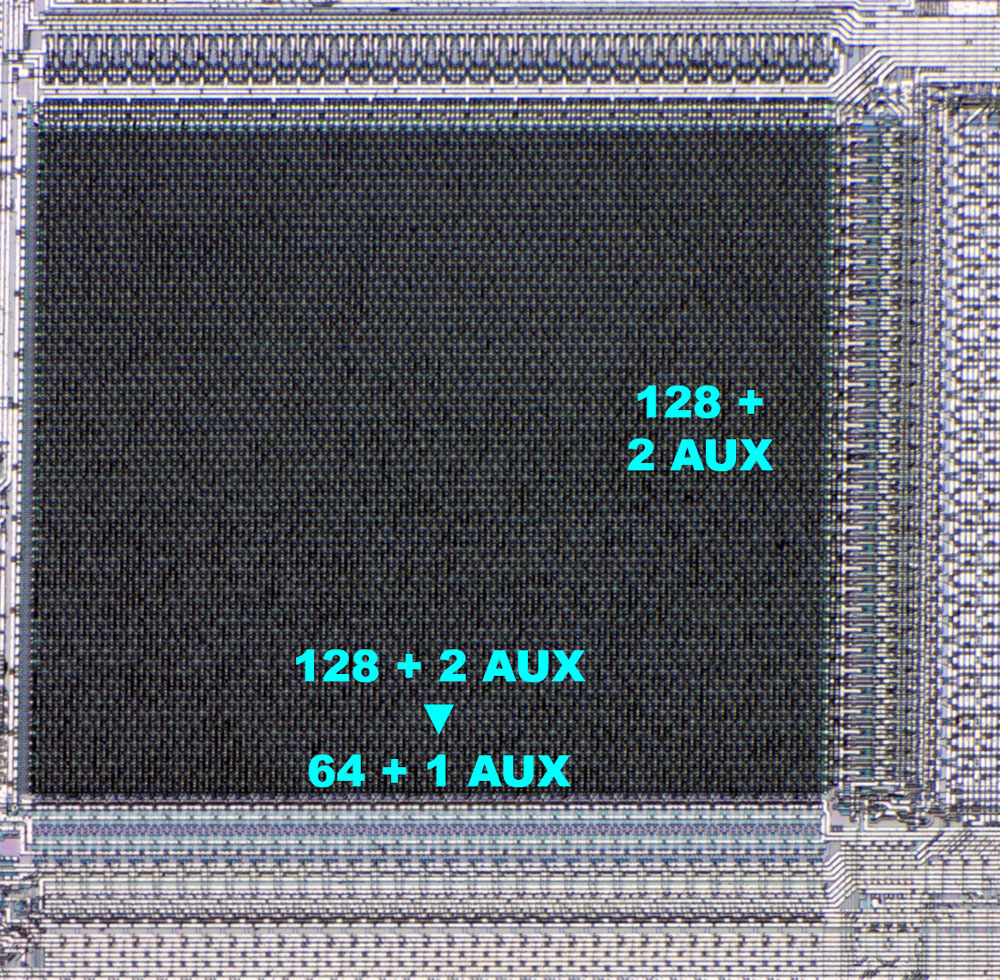

Die Analyse der Revision 4 des U2164 zeigt, dass diese Darstellung des Aufbaus in einem Detail etwas vereinfacht wurde.

In der Literatur heißt es, dass der U2164 jeweils zwei Reservezeilen und zwei Reservespalten besitzt. Diese Zeilen und Spalten finden sich auch auf dem Die. Die beschriebene Zusammenfassung von Spaltenpaaren führt allerdings dazu, dass effektiv nur ein solches Spaltenpaar als Reserve zur Verfügung steht.

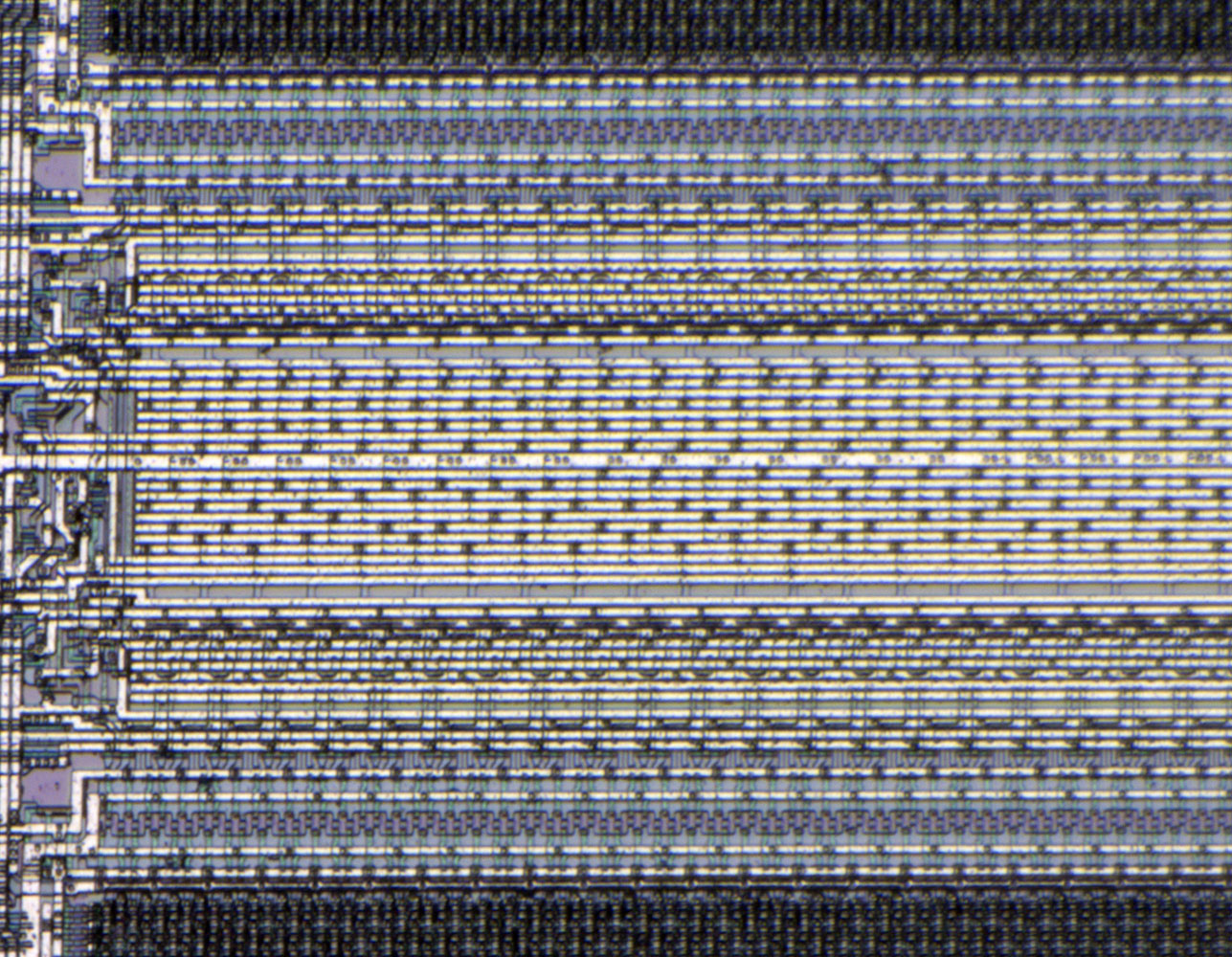

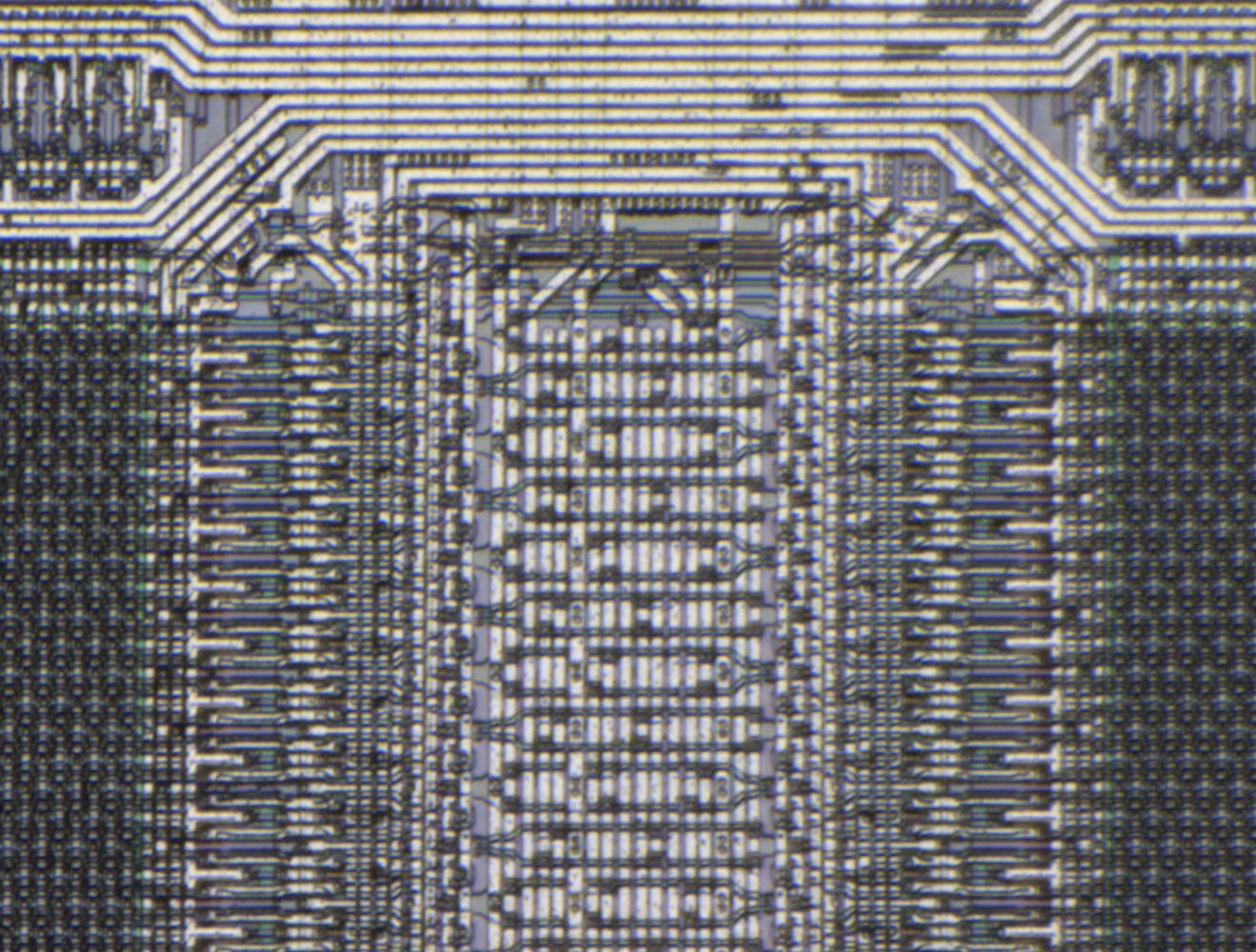

In der Spaltenauswahl ist gut die unterschiedliche Kontaktierung der horizontal verlaufenden Adressleitungen zu erkennen.

In der Schaltung zur Einspeisung des Referenzpegels sind keine speziellen Strukturen zu erkennen. In den besseren Bildern des U2164 kann man aber knapp oberhalb des Speicherbereichs die Dummyzellen identifizieren.

Wie beim Spaltendekoder sind auch die Schaltungsteile zur Zeilenauswahl mit unterschiedlichen Kontaktierungen an einem breiten Adressbus angebunden.

Der Adressmultiplexer (hier um 90° gedreht) erhält von unten 8 Eingangssignale und gibt nach oben 16 Steuersignale aus. Die 16 Steuerleitungen führen zwischen die Speicherbereiche.

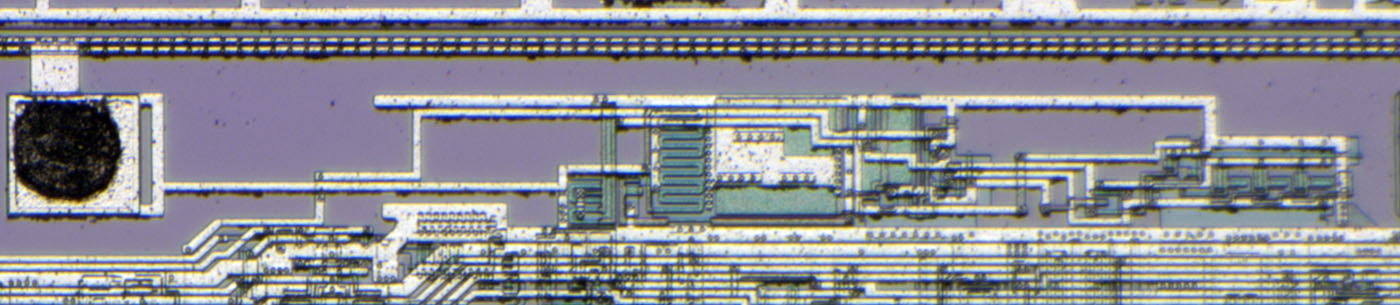

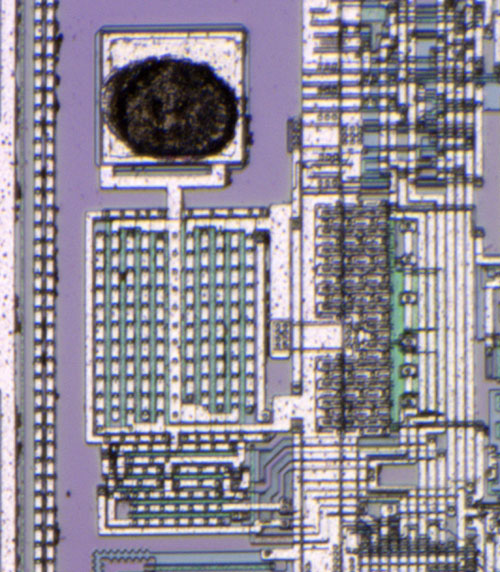

Die Schaltung zur Erzeugung des negativen Substratpotentials zeigt die dafür typischen Strukturen. Der Bereich ganz rechts könnte der Oszillator für die Ladungspumpe sein. Mittig sind verhältnismäßig große Elemente, Kondensatoren und Transistoren zu erkennen, die wahrscheinlich die eigentliche Ladungspumpe darstellen.

Man könnte meinen, dass das Bondpad links mit dem Pin 1 des Packages verbunden wäre. Dort ist beim U256 die -5V Versorgung anzulegen. Hier ist das Bondpad aber höchstwahrscheinlich wie auch beim D82720 mit dem Substratträger verbunden. Passend dazu kann man am Pin 1 eines U2164 keinen relevanten Widerstand, keine Diode und keine Spannung messen. Interessant ist der doppelte Metallrahmen, der das ganz Die umfasst, vielfach kontaktiert und so das negative Potential effektiv verteilt.

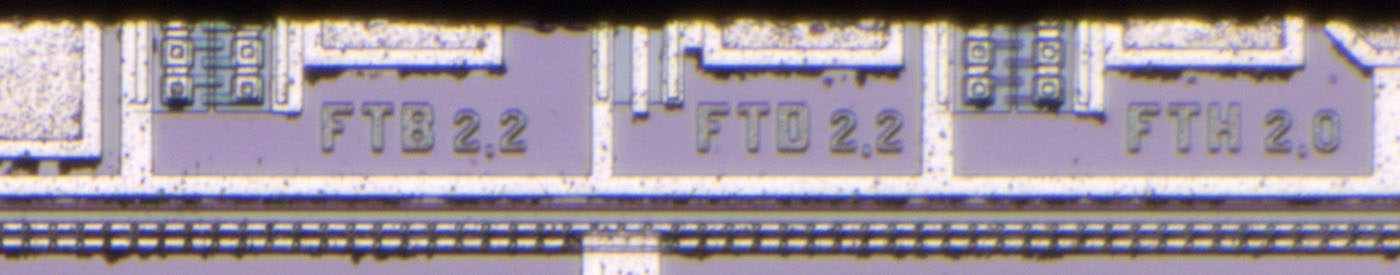

An den Kanten sind teilweise Überreste von Teststrukturen und Revisionskennzeichnungen zu erkennen. Die Platzierung in den Frässtraßen reduziert den Flächenverbrauch. Im hier abgebildeten Ausschnitt scheinen drei verschiedene Transistorarrays abgebildet zu sein.

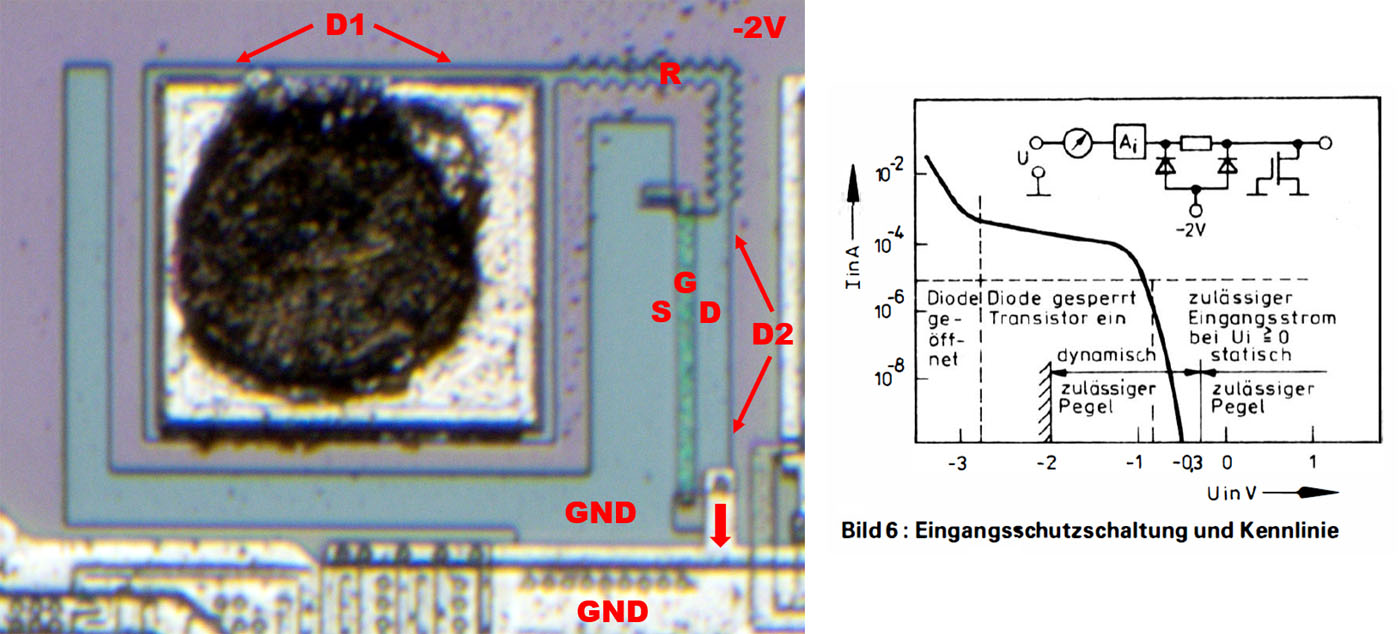

Die Schutzstrukturen an den Eingängen sind ebenfalls im Artikel der Radio Fernsehen Elektronik beschrieben. Ein sogenannter Grounded Gate NMOS wird bei zu niedrigen Spannungen aktiv und stellt einen leitfähigen Pfad zum GND-Potential her. Der Längswiderstand begrenzt den Stromfluss. Spannungen bis -2V dürfen trotzdem nicht länger als 40ns anliegen. Es handelt sich lediglich um einen Schutz vor Unterschwingungen, die bei steilen Schaltflanken auf den Leitungen entstehen können. Liegen noch niedrigere Spannungen an, dann werden die parasitären Dioden leitend. Da dieser Pfad keine Strombegrenzung besitzt, sind derart niedrige Spannungen nicht zulässig. Bei sehr hohen Spannungen (die Radio Fernsehen Elektronik gibt 12V an) wird der Grounded Gate NMOS ebenfalls leitend und schützt die Schaltung.

Die verhältnismäßig große Push-Pull-Endstufe des Datenausgangs ist gut zu erkennen. Darunter befindet sich die Treiberstufe.