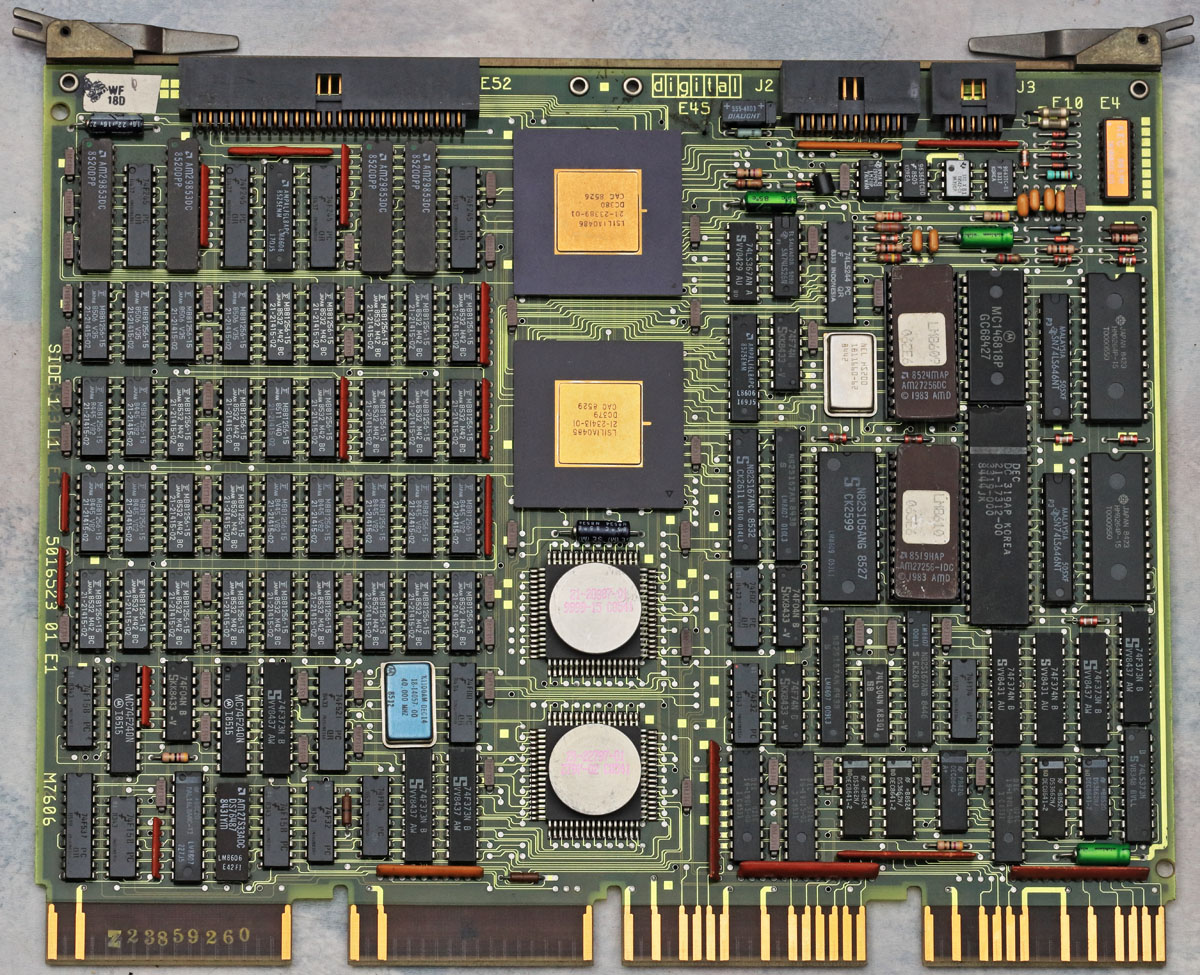

Die hier zu sehende Platine mit der Bezeichnung KA630 ist ein CPU-Modul der MicroVAX II. Die MicroVAX Computersysteme wurden von DEC (Digital Equipment Corporation) entwickelt und sind Nachfolger der VAX-11 Modellreihe. Die MicroVAX I war die erste Generation, gefolgt von der MicroVAX II.

Das von DEC aufgelegte "Digital Technical Journal" vom März 1986 erklärt viele Details der MicroVAX II. Demnach lag bei der Entwicklung der Fokus darauf möglichst viele CPU-Funktionen, die bisher auf viele integrierte Schaltkreise verteilt waren, in einen Mikroprozessor zu integrieren. Diese Entwicklung war notwendig, um konkurrenzfähig zu bleiben.

Der erste Maskensatz des 78032 wurde laut Digital Technical Journal in 20 Monaten entwickelt. 6 Monate lang wurden die Anforderungen und das grundlegende Design festgelegt. Die Entwicklung der eigentlichen Schaltung erforderte 14 Monate. Ziel war es den IC nach spätestens zweieinhalb Jahren in Serie zu produzieren.

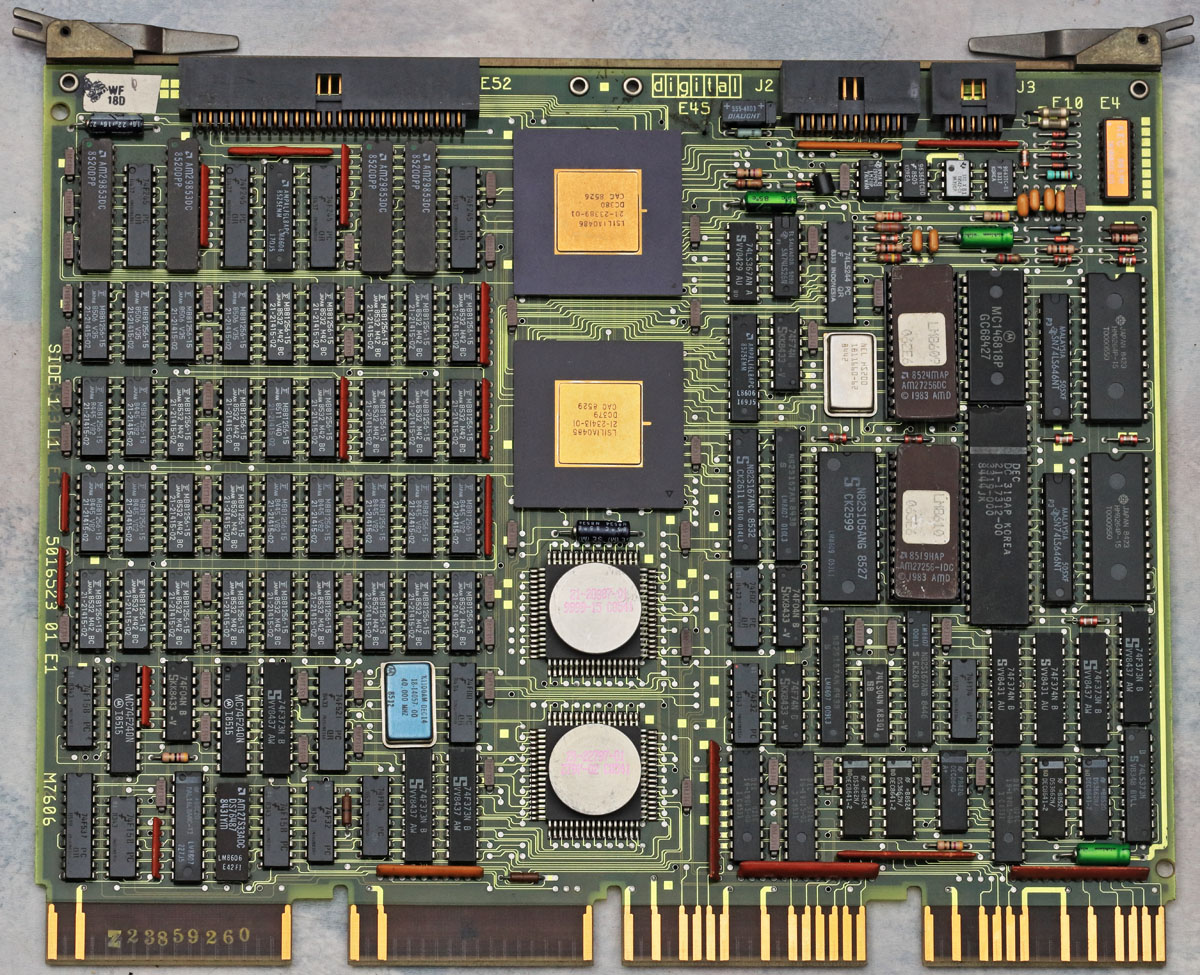

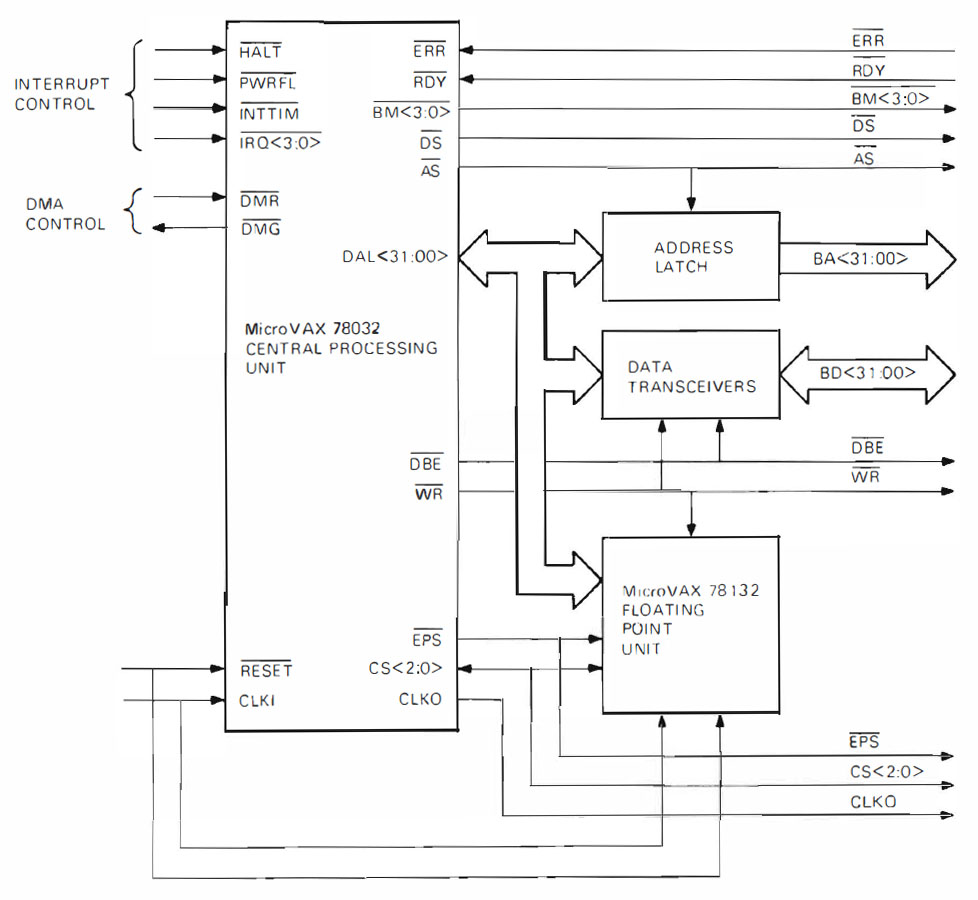

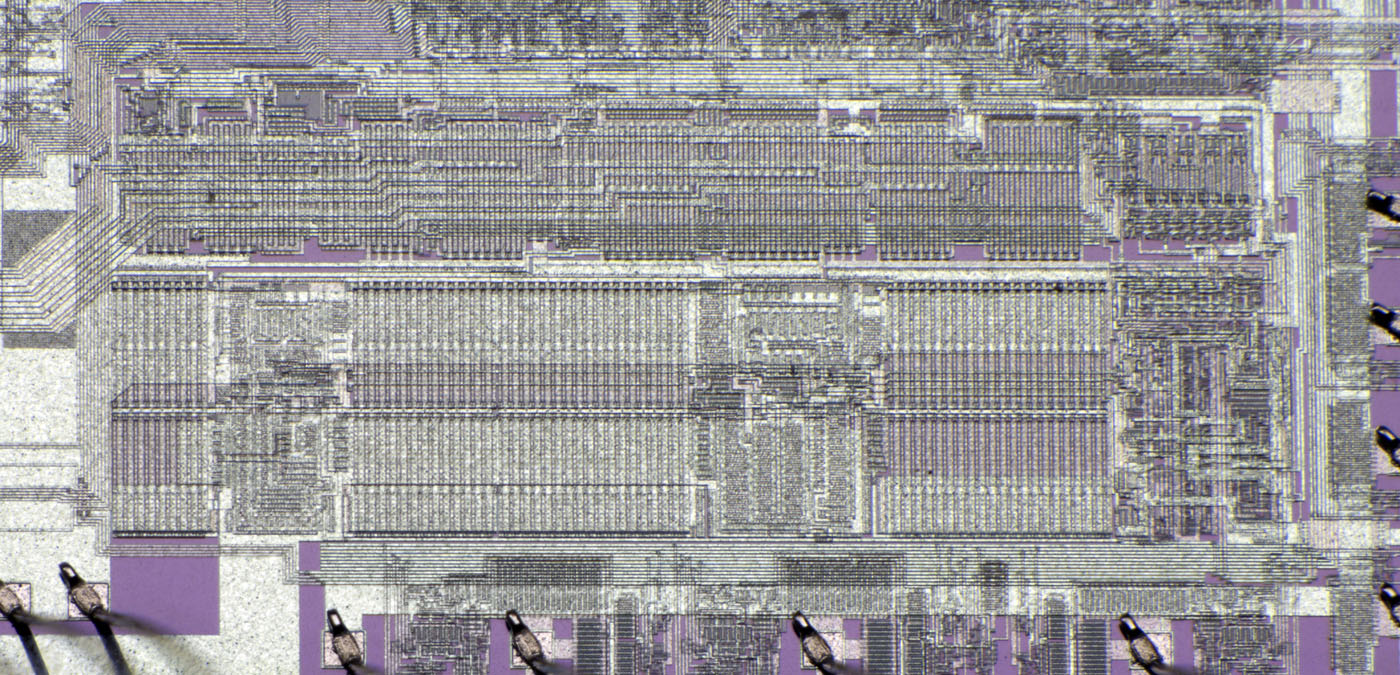

Das Digital Technical Journal enthält die obige Darstellung der KA630-Platine. Kern der Platine sind die CPU 78032 und die FPU 78132. Darüber befinden sich zwei Gatarrays. Das untere Gatearray ist eng mit der CPU verknüpft. Das obere Gatearray stellt die Schnittstelle zum Q22-Bus dar, der die CPU-Karte mit den anderen Modulen verbindet. Für eine vollständige Integration der VAX-Architektur wären 1,25 Million Transistoren notwendig gewesen. Die damalige Technik ermöglichte allerdings nur ein Zehntel davon in den Mikroprozessor zu integrieren. Daher musste man beim Integrationsgrad Kompromisse eingehen.

Links sind 36 256kBit-DRAM-Bausteine bestückt und bieten so insgesamt 1MB RAM. Das Digital Technical Journal berichtet von einer Knappheit der 256kBit-Bausteine zum Zeitpunkt der Entwicklung, so dass man alternativ eine Bestückung mit 64kBit-Speichern vorsah. Über Erweiterungskarten kann man den Arbeitsspeicher auf bis zu 16MB erweitern.

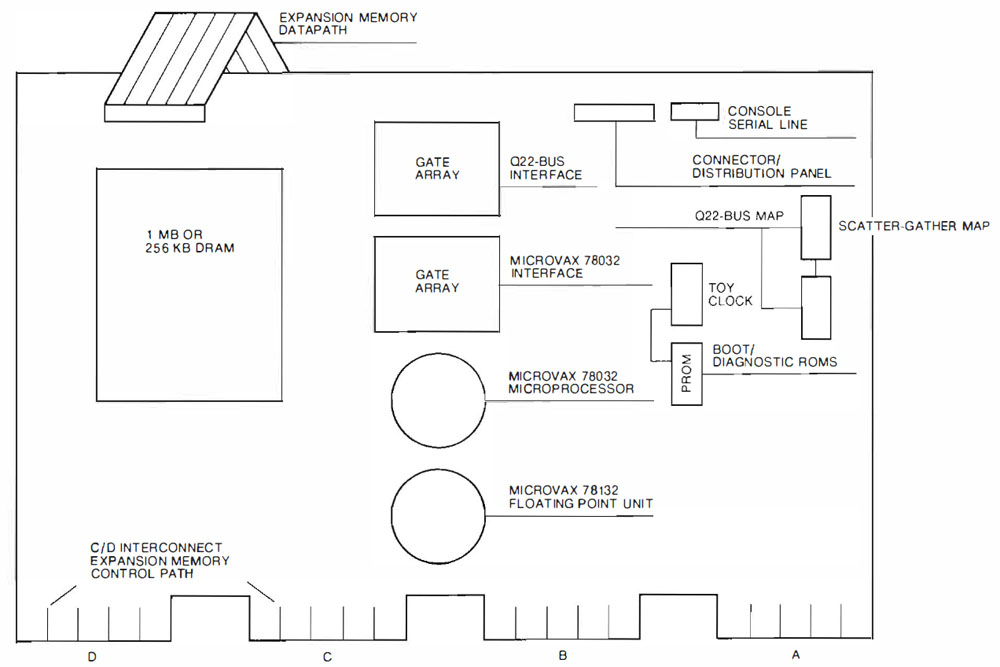

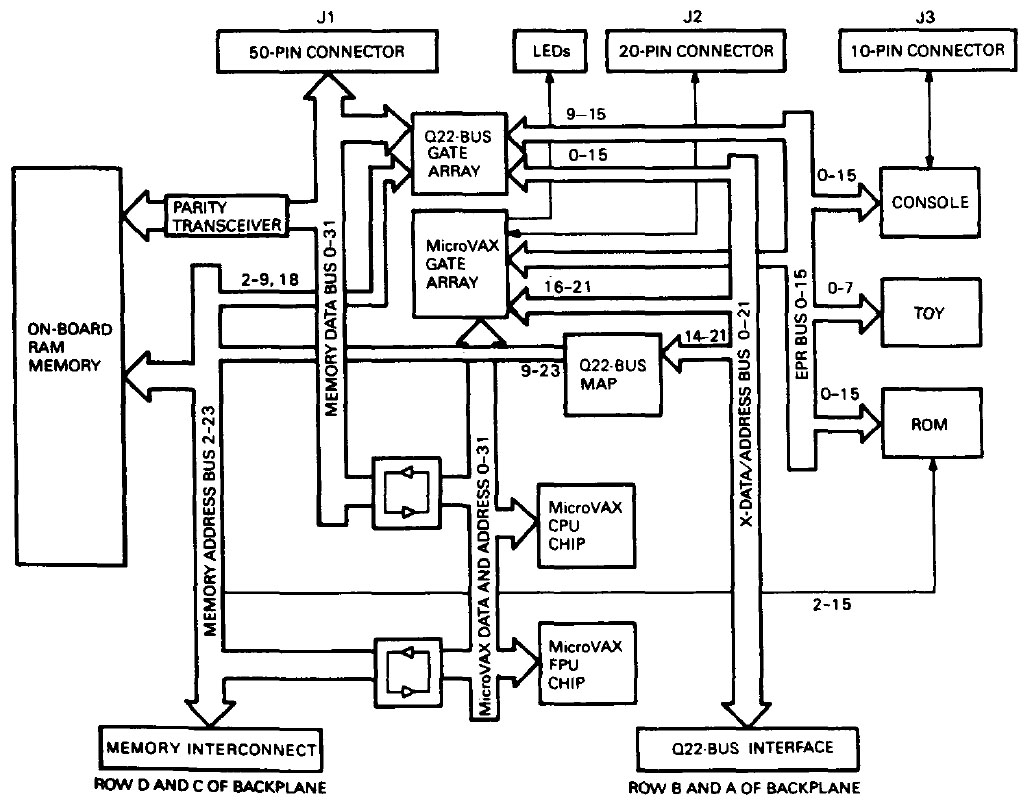

Das "KA630-AA CPU Module User´s Guide" enthält ein Blockdiagramm, dass die Architektur des CPU-Boards etwas detaillierter zeigt.

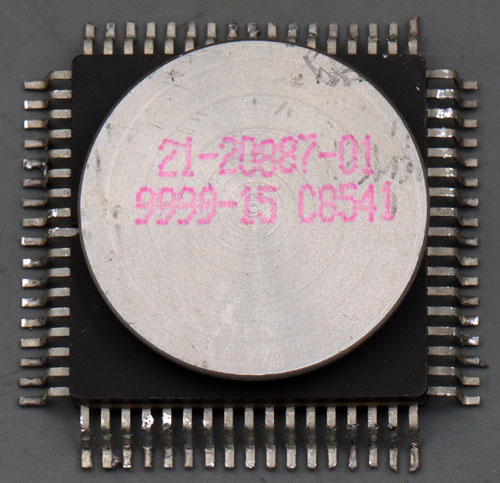

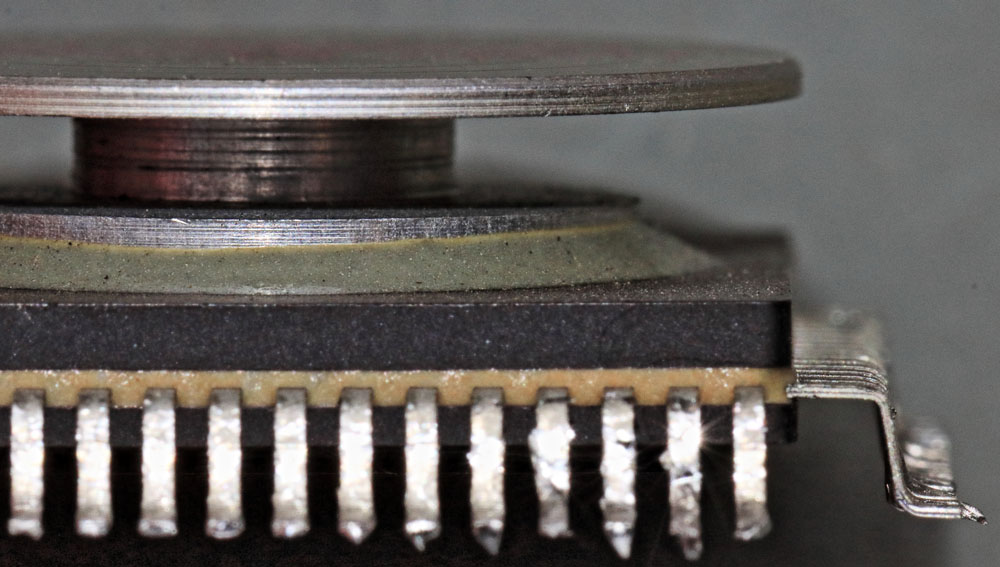

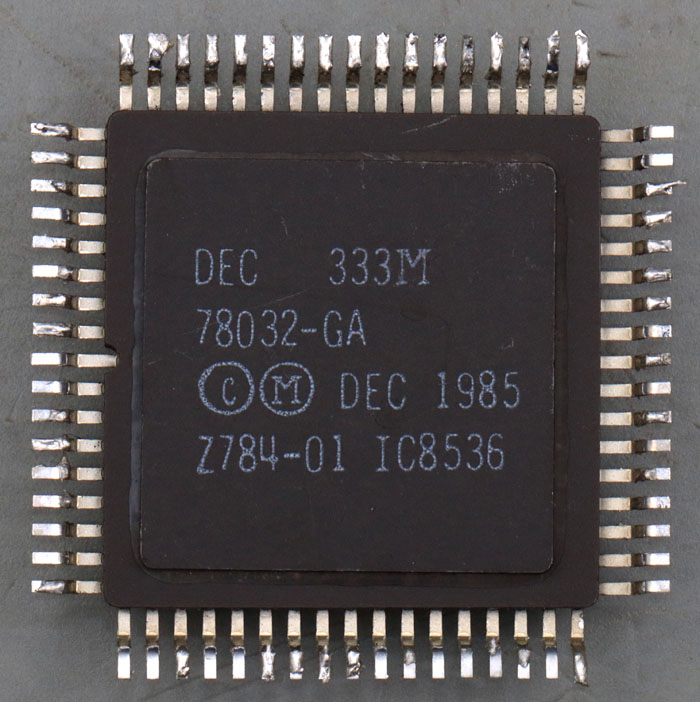

Die CPU 78032 und die FPU 78132 befinden sich in einem TQFP-68 Gehäuse mit einem runden Kühlkörper.

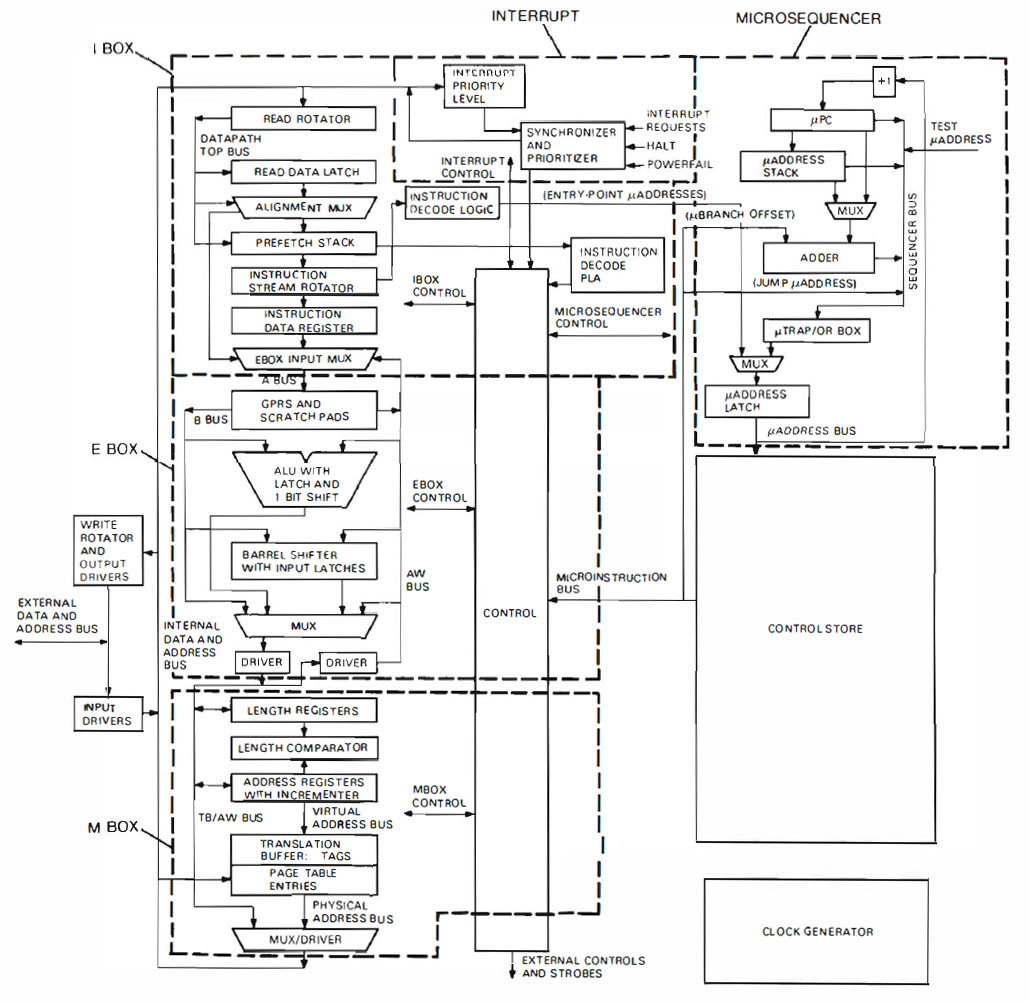

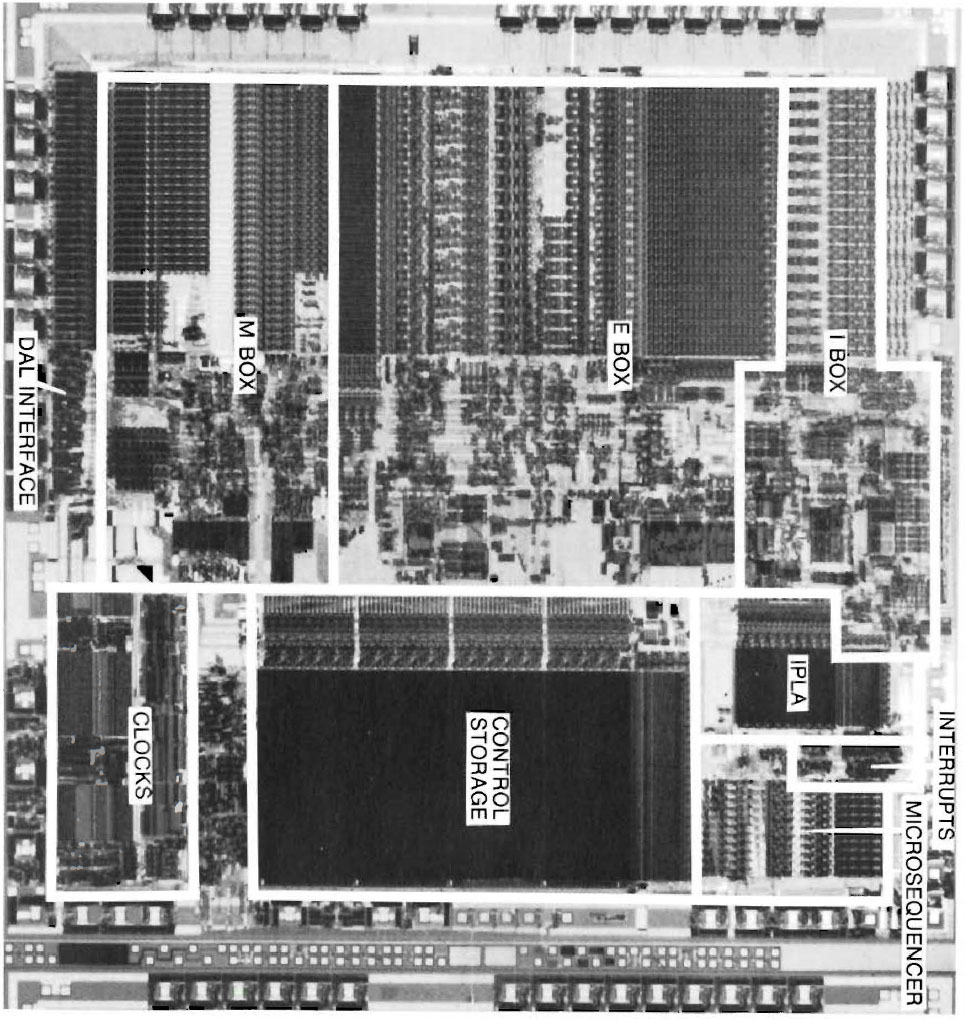

Der 78032 wurde nur von DEC selbst verwendet. Daher ist es nicht verwunderlich, dass dafür kein Datenblatt existiert. Das obige Blockschaltbild aus dem Digital Technical Journal ist die detaillierteste Darstellung, die sich finden lässt.

Die integrierten Funktionsblöcke werden im Digital Technical Journal sehr genau dargestellt.

Der Kühlkörper ist auf das Keramikgehäuse aufgeklebt. Die CPU arbeitet mit 5V und einer Taktfrequenz von 20MHz. Dabei fallen typischerweise 3W Verlustleistung an.

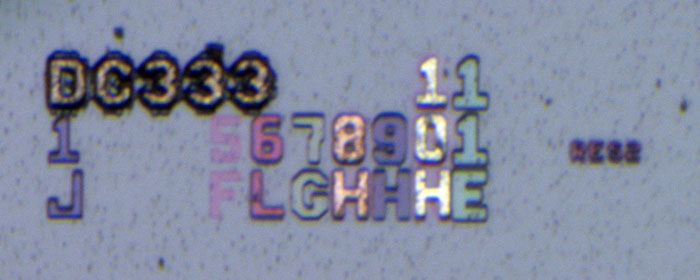

Auf der Unterseite des Gehäuses findet sich die Beschriftung. Die Zahlen 8536 in der unteren rechten Ecke stellen wahrscheinlich den Datecode dar. Die Zeichenfolge 333M verweist auf die interne Bezeichnung DC333.

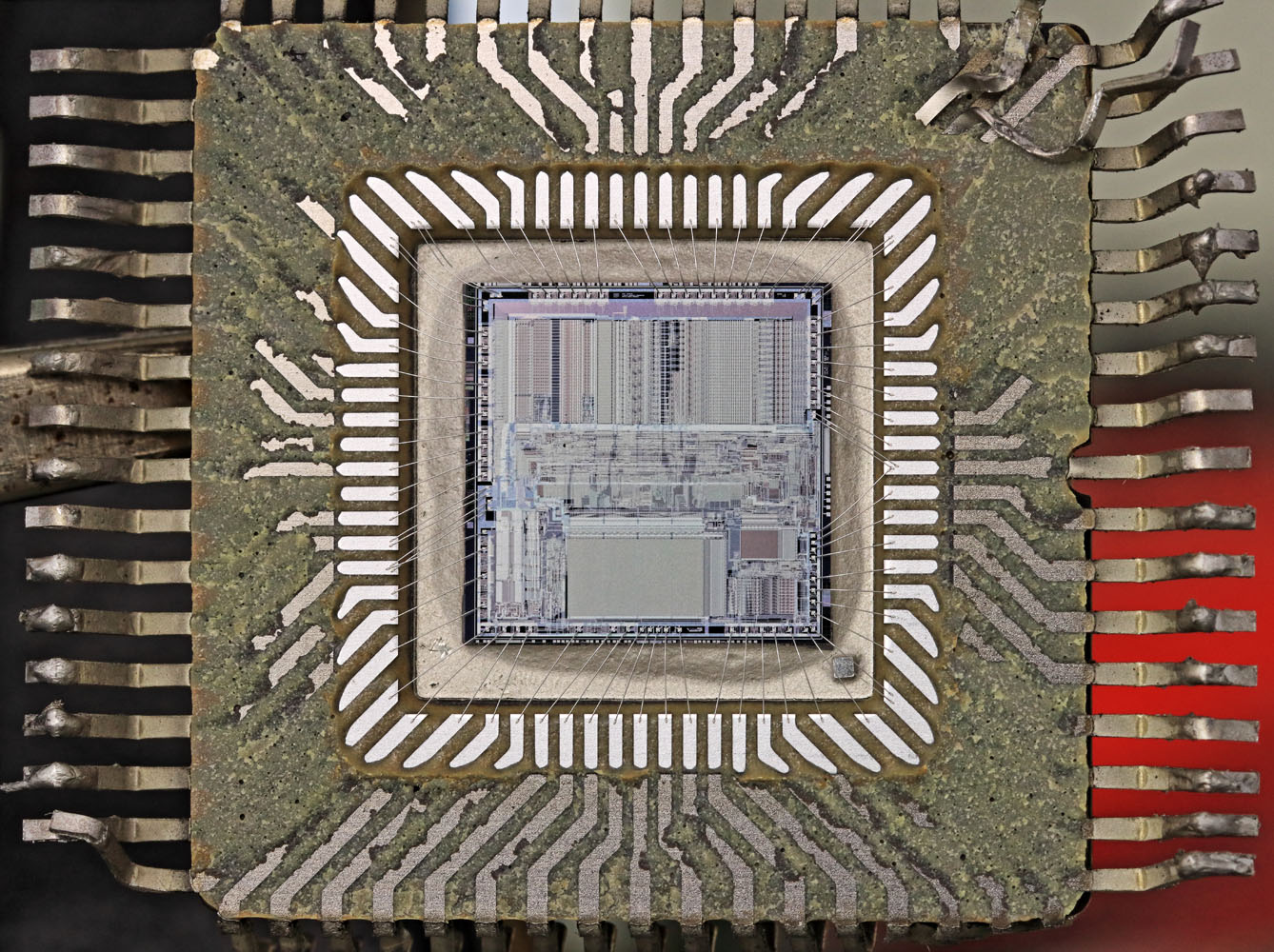

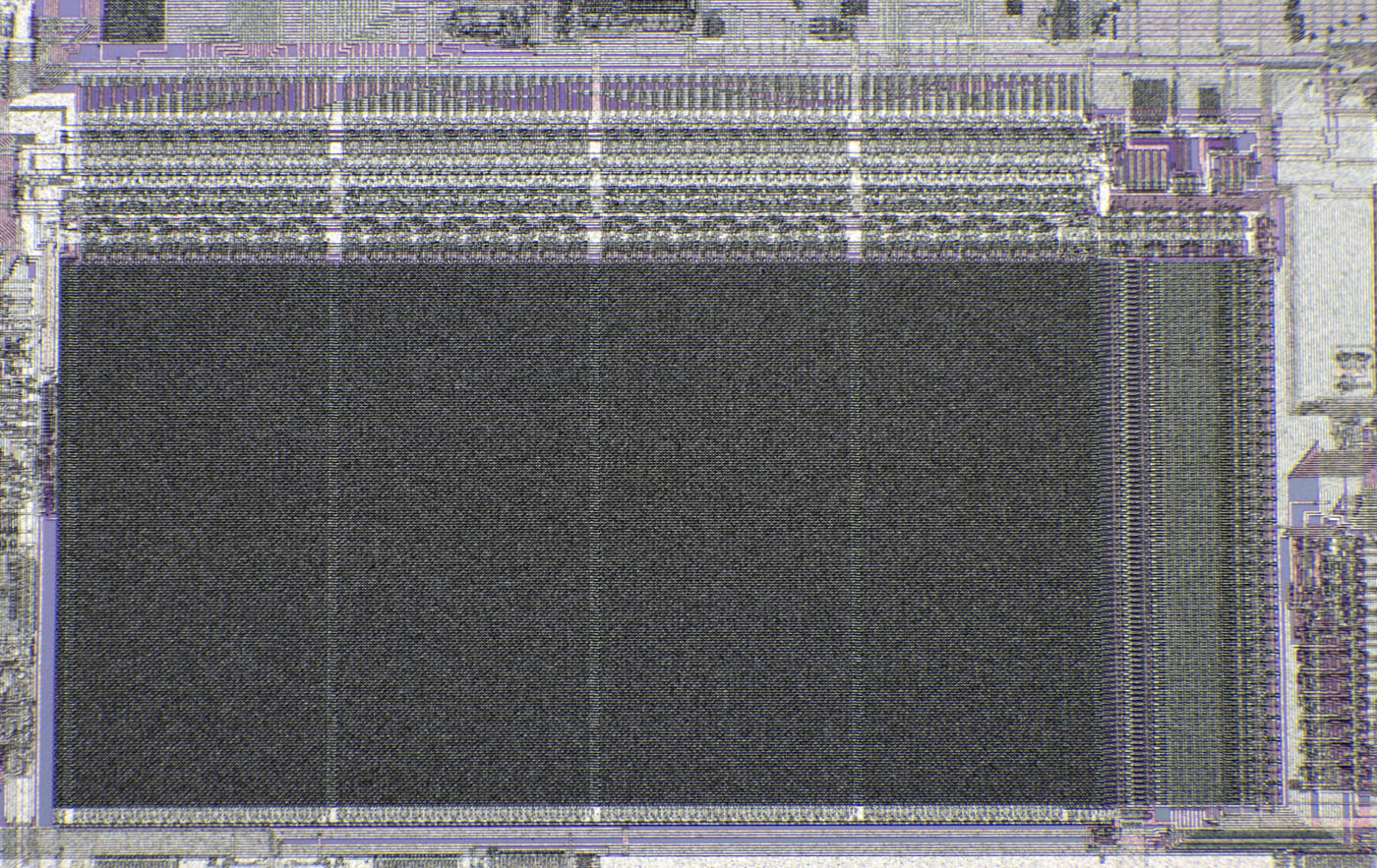

Das Die ist in der oberen Hälfte des Gehäuses befestigt. So kann die Verlustleistung effizient über die Oberseite abgeführt werden.

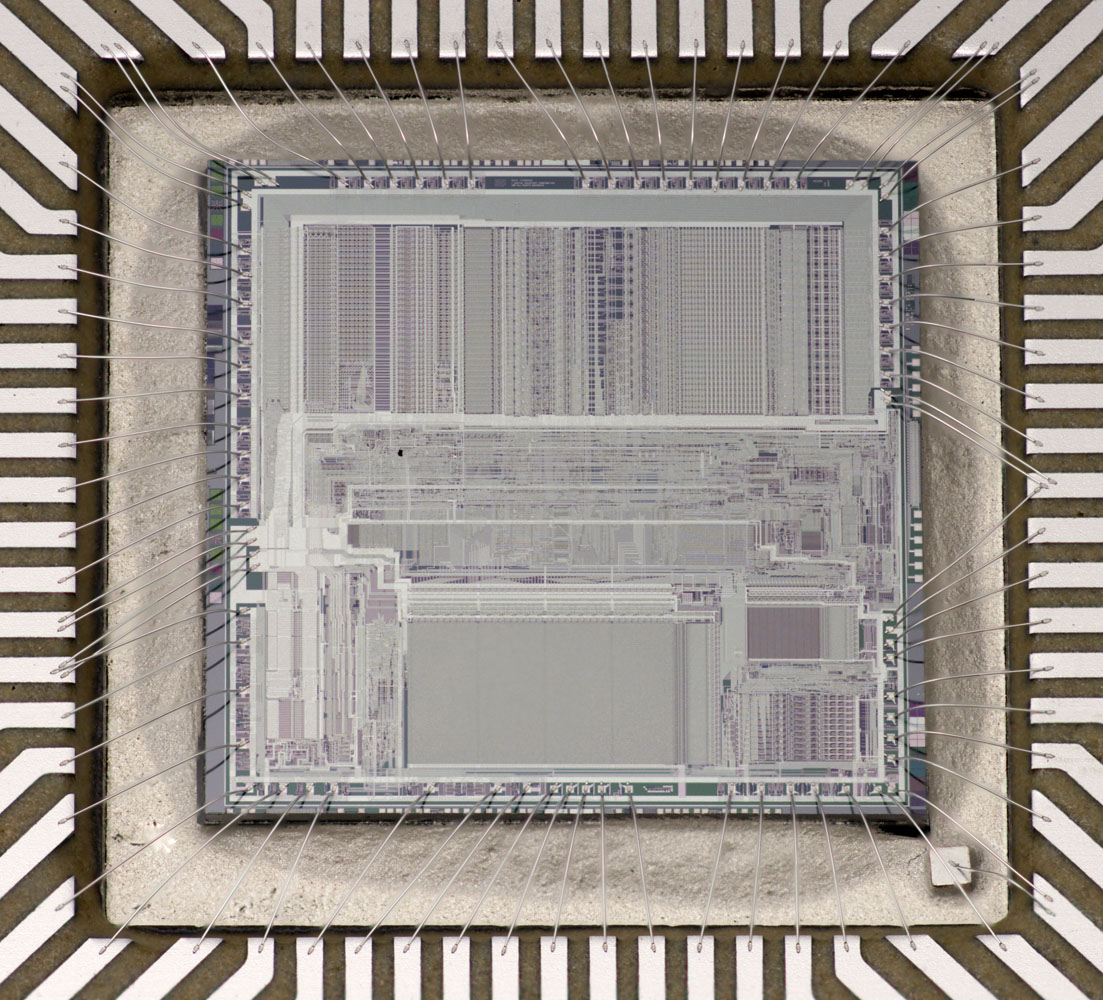

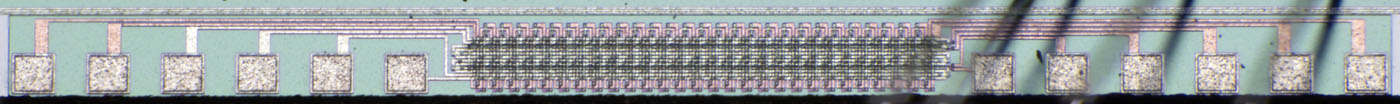

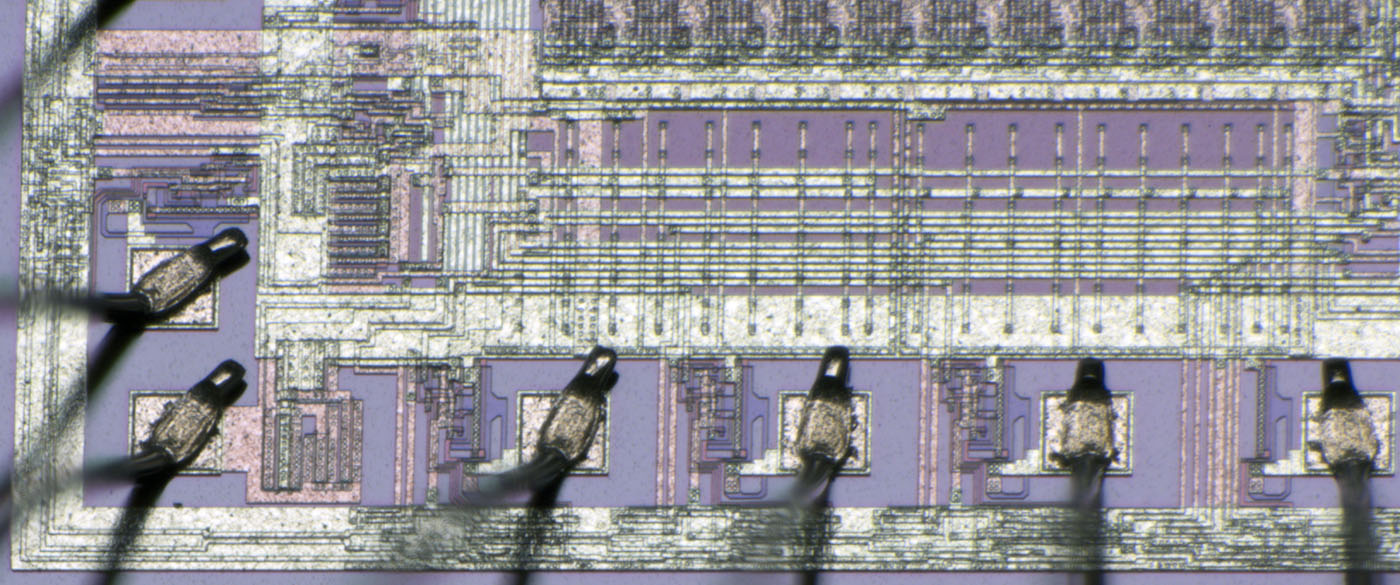

In der Übersicht fällt auf, dass ein besonderes Augenmerk auf eine störungsfreie Versorgung der einzelnen Funktionsblöcke gelegt wurde. Die obere Hälfte des Die beinhaltet in den Außenbereichen die breite Daten- und Adressschnittstelle. Diese Treiber besitzen eigene breite Versorgungsleitungen, die in den beiden Ecken mit jeweils zwei Bonddrähten auf vier Pins geführt werden. Die Versorgungspins in der Mitte der linken und rechten Seite versorgen über jeweils zwei Bonddrähte die eigentliche CPU. Die Schnittstellen in der unteren Hälfte besitzen teilweise nochmal eigene Bonddrähte, sind aber nicht so exklusiv angebunden wie die oberen Schnittstellen.

Ein kleiner Quader in der rechten unteren Ecke legt das Potential des Trägers und damit auch des Substrats auf einen Pin, der wiederum mit einem Bondpad verbunden ist.

Das Die ist 9,1mm x 9,0mm groß. Das Digital Technical Journal gibt eine Größe von 8,7mm x 8,6mm an, was der Größe ohne die Überreste der Rahmenstruktur entspricht. Das Digital Technical Journal beschreibt weiter, dass hier 125.000 Transistoren integriert wurden. Zum Einsatz kam ein 3µm NMOS-Prozess mit zwei Metalllagen, der bei DEC die Bezeichnung ZMOS trägt.

Das hier gezeigte Bild ist auch in höherer Auflösung verfügbar (102MB).

Das Digital Technical Journal zeigt die Verteilung der Funktionsblöcke auf dem Die. Offensichtlich ist das sehr große ROM im unteren Bereich, dass die Befehle in die notwendigen Steuersignale umwandelt. Der Kern der CPU, hier I-Box, E-Box und M-Box genannt, ist auf Grund der 32Bit breiten Strukturen sehr groß und nimmt inklusive der Steuerung mehr als die Hälfte der Fläche ein.

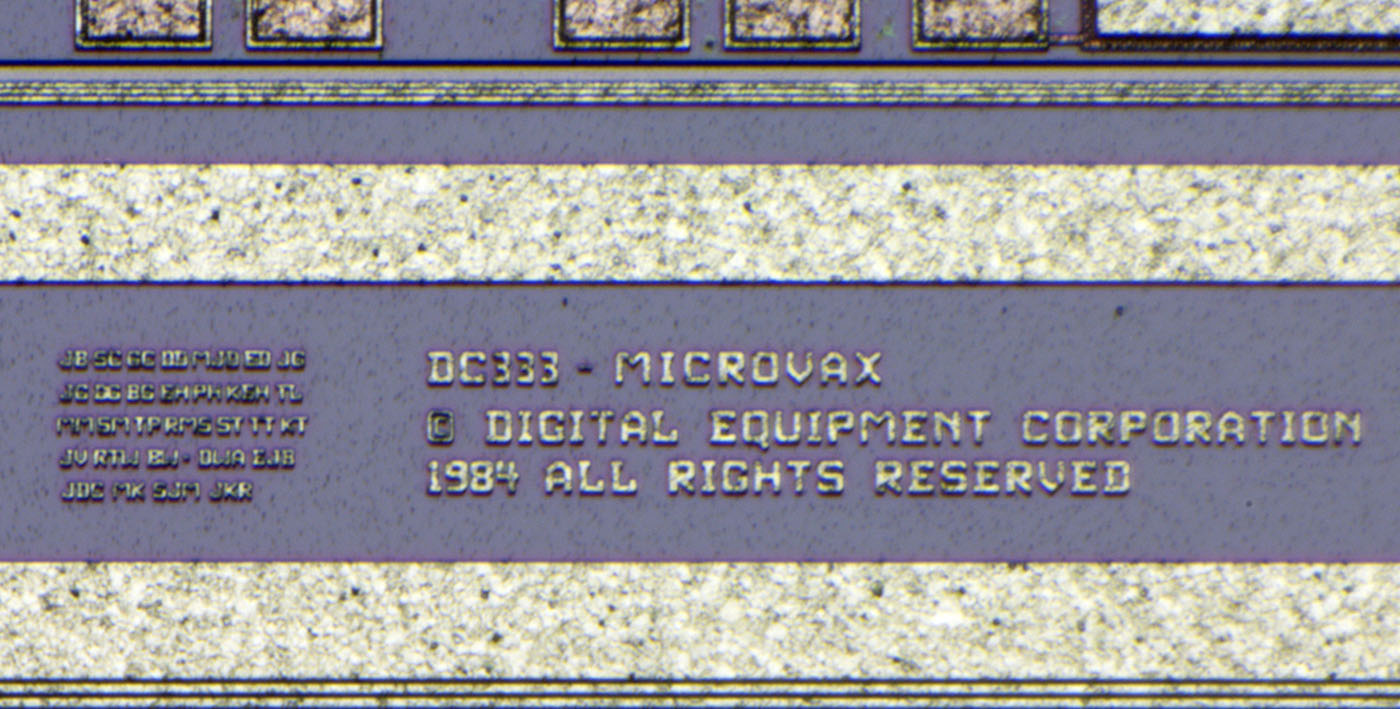

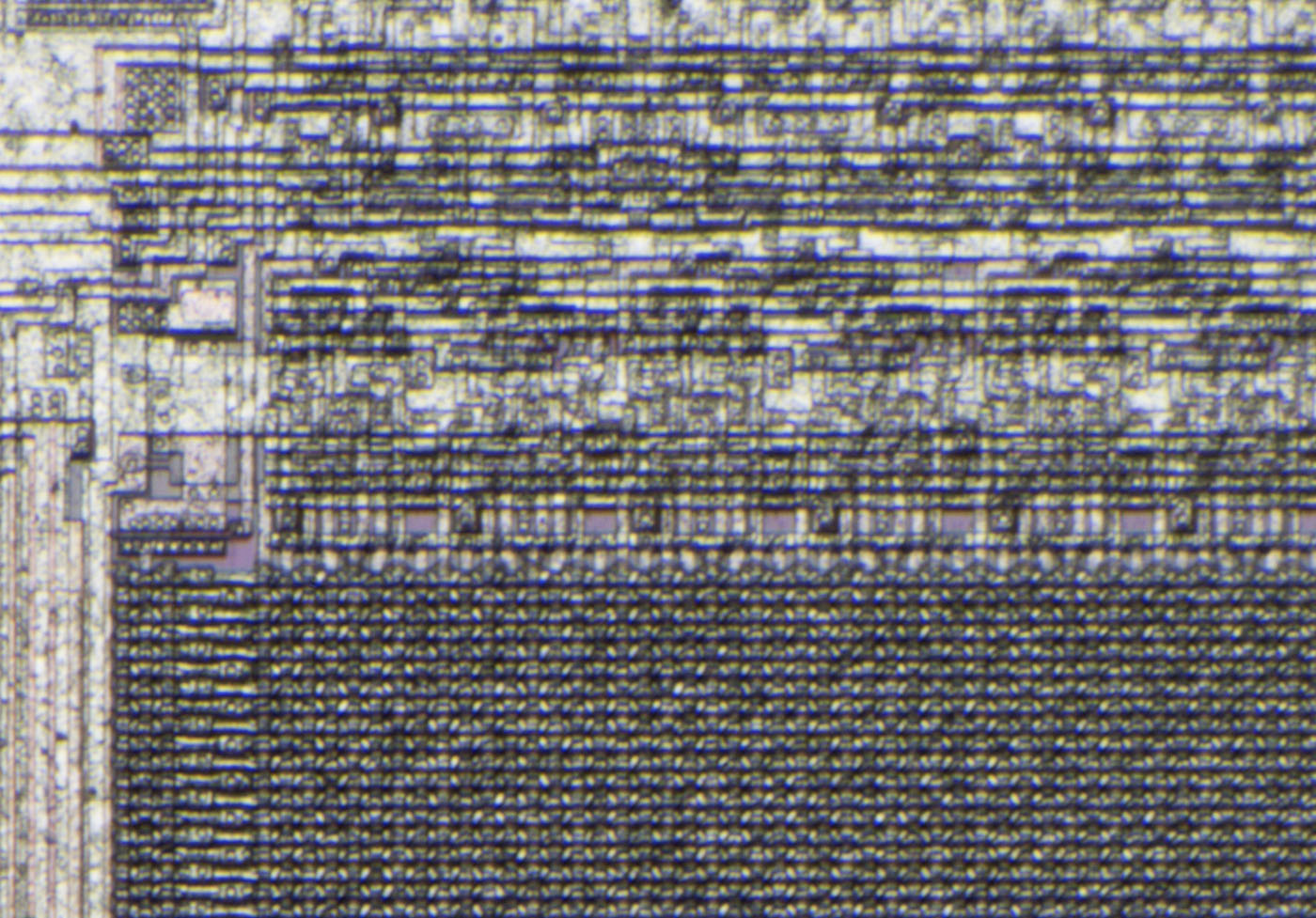

An der oberen Kante findet sich ein Copyright aus dem Jahr 1984 und die interne Bezeichnung DC333. Die Buchstaben im linken Bereich sind mit Sicherheit Kürzel der Entwickler. Das Digital Technical Journal berichtet von 18 Entwicklern, die am 78032 gearbeitet haben.

Unterhalb des Copyrights verlaufen sehr viele Leiterbahnen. An einer Stelle ist darunter eine Figur abgebildet, die anscheinend einen Hund darstellen soll. Die Form ist bei schlechteren Aufnahmen etwas besser zu erkennen.

Direkt sichtbar sind acht Masken. Sofern die Buchstaben Revisionen kennzeichnen, wurde das Design elfmal überarbeitet. Im Kontrast dazu lobt das Digital Technical Journal "sehr sehr wenige Bugs", im Detail wären es "weniger als 20 Bugs" gewesen bis es möglich war das Betriebssystem zu booten.

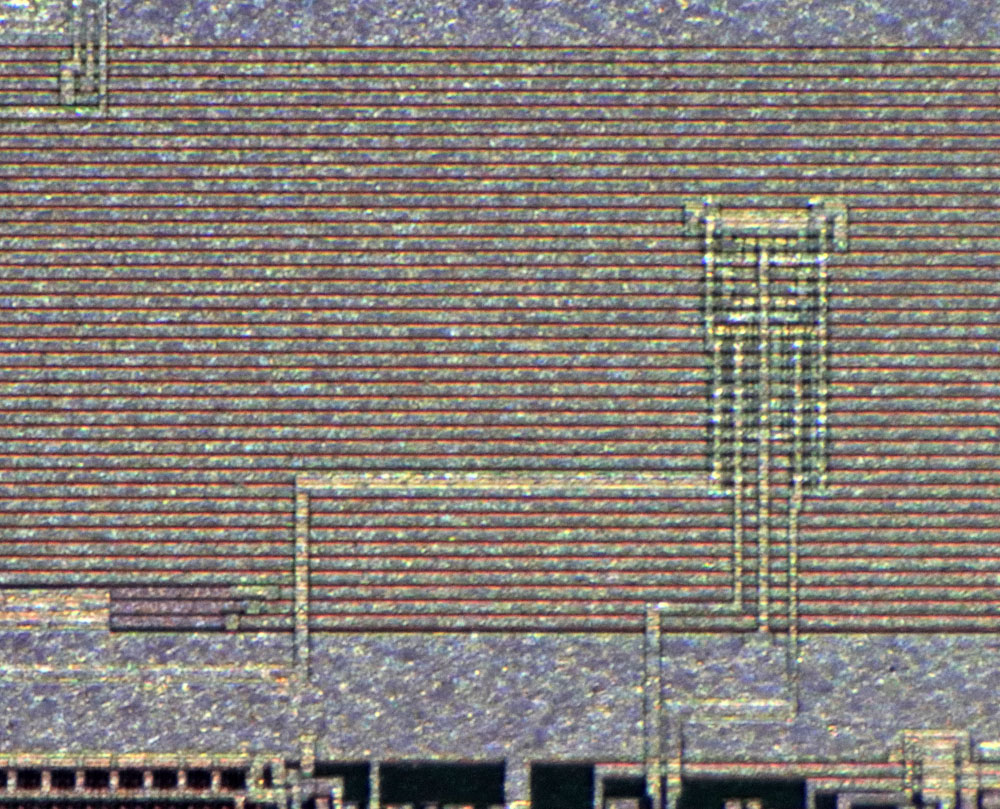

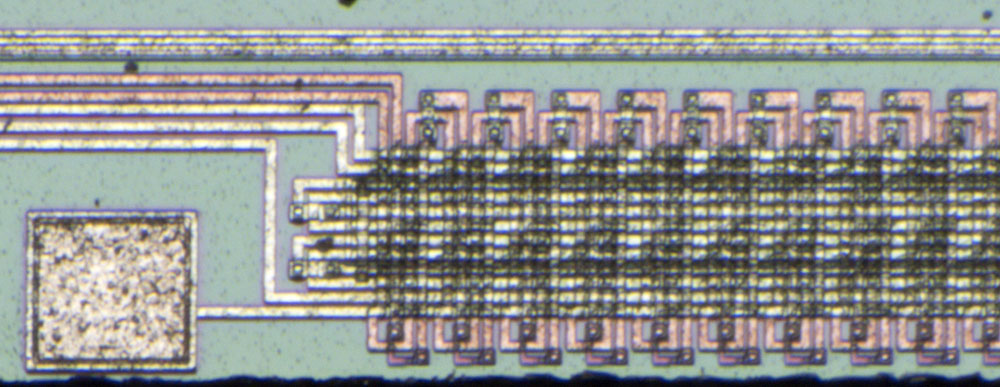

Hier sind schön die beiden Metalllagen 8 und 10 erkennbar. Die Maske 7 schafft Kontakte zum Silizium. Die obere Metalllage kann nur die untere Metalllage kontaktieren, wofür die Maske 9 genutzt wird. Die Maske 11 schafft dann Öffnungen in der Passivierungsschicht, wo sich die Bondflächen befinden.

Neben den Masken der Metalllagen bleiben dann nur noch drei sichtbare Masken. Man kann davon ausgehen, dass zwischen 1 und 5 noch weitere Masken zum Einsatz kamen. Das Digital Technical Journal beschreibt vier Transistortypen, die in diesem Prozess genutzt werden konnten: N, E (light enhancement), L (light depletion) und D.

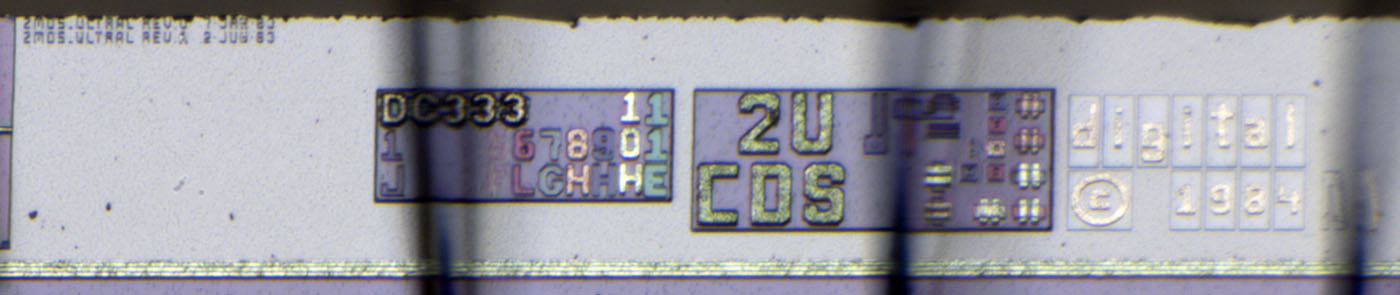

In der Rahmenstruktur sind die Bezeichnung und die Revisionen des Maskensatzes ein weiteres Mal abgebildet. 2U CDS könnte eine Prozessbezeichnung sein.

In der linken oberen Ecke ist gerade noch eine Beschriftung zu erkennen, die anscheinend auf den Technologieknoten verweist. Die Zeilen beginnen mit ZMOS.ULTRAL und enden mit einem Datum aus dem Jahr 1983.

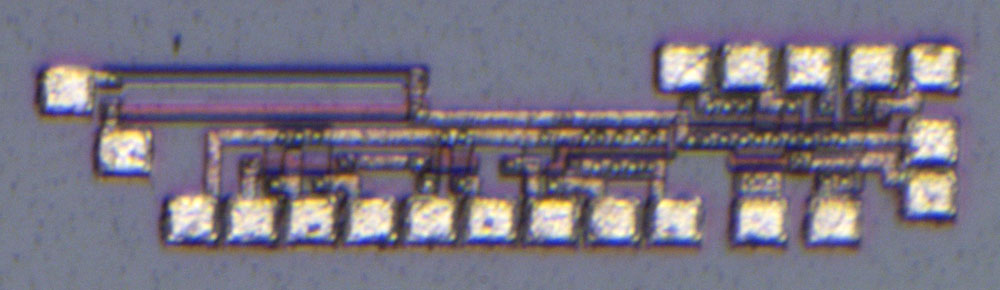

Eine Teststruktur an der unteren Kante enthält mehrere Elemente. Bei den langen Streifen links scheint es sich um Widerstände zu handeln. Die restlichen Strukturen stellen unterschiedliche Transistoren dar.

An der rechten Kante ist eine sehr breite Teststruktur integriert. Welche Funktion hier abgebildet ist bleibt unklar, es scheint sich aber auf jeden Fall um eine Verkettung mehrerer gleicher Elemente zu handeln. Vielleicht wurden hier mehrere Gatter hintereinander geschaltet, um deren Qualität mit einem Testsignal überprüfen zu können.

In der rechten unteren Ecke (hier gedreht) befindet sich ein Bias-Generator, wie man ihn auch im µPD7220 und im D82720 findet. Es handelt sich dabei um eine Ladungspumpe, die ein negatives Potential erzeugt. Direkt erkennbar ist der verhältnismäßig große Kondensator, den viele vertikale Leitungen kontaktieren. Das negative Potential wird über den Quader neben dem Die auf den Träger und so zum Substrat übertragen. Das negative Body-Potential verbessert das Schaltverhalten der Transistoren.

In der linken unteren Ecke des Dies befindet sich die Taktaufbereitung, die relativ viel Fläche einnimmt (hier gedreht). Von außen muss ein 40MHz-Takt zugeführt werden. Das Digital Technical Journal beschreibt, dass aus diesem Takt acht phasenverschobene Takte erzeugt werden. Die Treiber müssen teilweise sehr leistungsfähig sein, da sie bis zu 250pF treiben müssen.

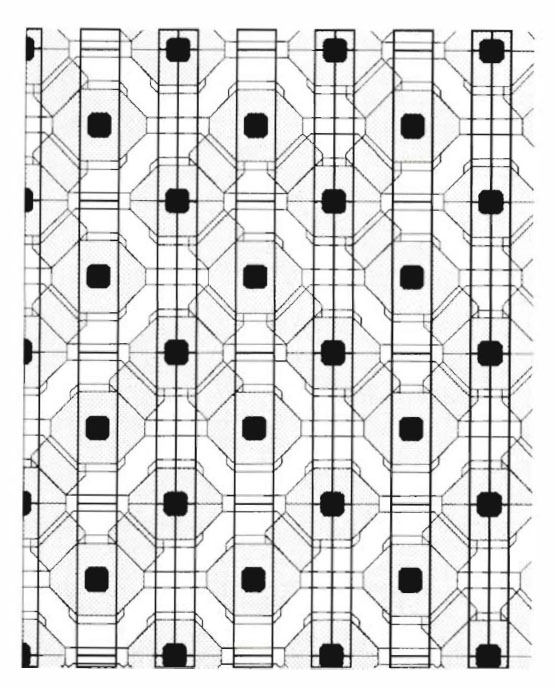

Das Layout des großen ROMs gibt das Digital Technical Journal mit 1600 x 39Bit an.

Wie bereits beschrieben war die Reduktion des Transistor- und Flächenverbrauchs eine kritische Vorgabe. Eine Erleichterung brachte die optimierte Anordnung der Steuerbefehle im Control-ROM. Das Digital Technical Journal hebt zusätzlich die X-förmigen Speicherzellen mit ihrem geringeren Platzbedarf hervor.

Auflösen lassen sich die verhältnismäßig komplexen Strukturen des Speichers nicht mehr ohne Weiteres.