Der µPD7720 war 1982 der weltweit erste Grafikprozessor. Es gibt Display-Controller, die älter sind. Display-Controller verarbeiten aber nur pixelweise die Daten, die angezeigt werden sollen. Grafikprozessoren können dagegen auch grafische Operationen ausführen. Sie können zum Beispiel Kreise zeichnen und Flächen füllen. Der µPD7720 verwaltet Grafikspeicher mit bis zu 4MBit Volumen. Das ermöglicht zum Beispiel bei einer Auflösung von 1024 x 1024 Pixel bis zu 16 Farben darzustellen. Teilweise wurden mehrere µPD7220 eingesetzt, um noch leistungsfähigere Systeme aufzubauen.

Der µPD7220 wurde von NEC entwickelt. Es kam aber bereits zu Beginn der Entwicklung einen intensiven Austausch mit Intel. Intel brachte kurze Zeit nach dem µPD7720 den vergleichbaren D82720 auf den Markt. Der µPD7220 war in drei Varianten mit den Taktfrequenzen 4MHz, 5Mhz und 5,5MHz verfügbar. Höchstwahrscheinlich handelt es sich bei den Varianten um Sortierungen, die je nach Fertigungsqualität unterschiedlich schnell betrieben werden konnten. 1983 hat NEC mit einem aktualisierten Fertigungsprozess den Nachfolger µPD7220A auf den Markt gebracht. In der DDR wurde der µPD7220 unter der Bezeichnung U82720 nachgebaut.

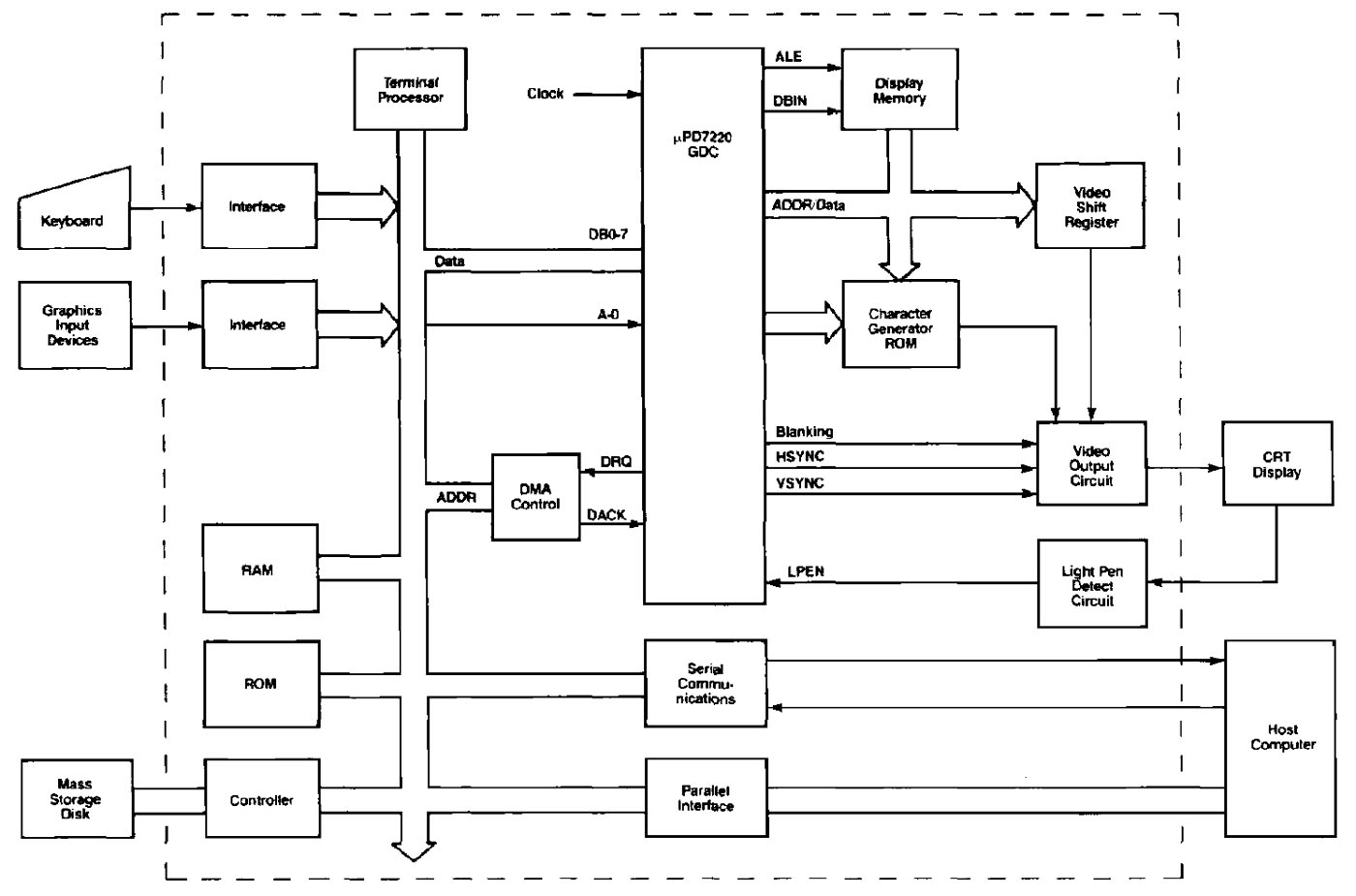

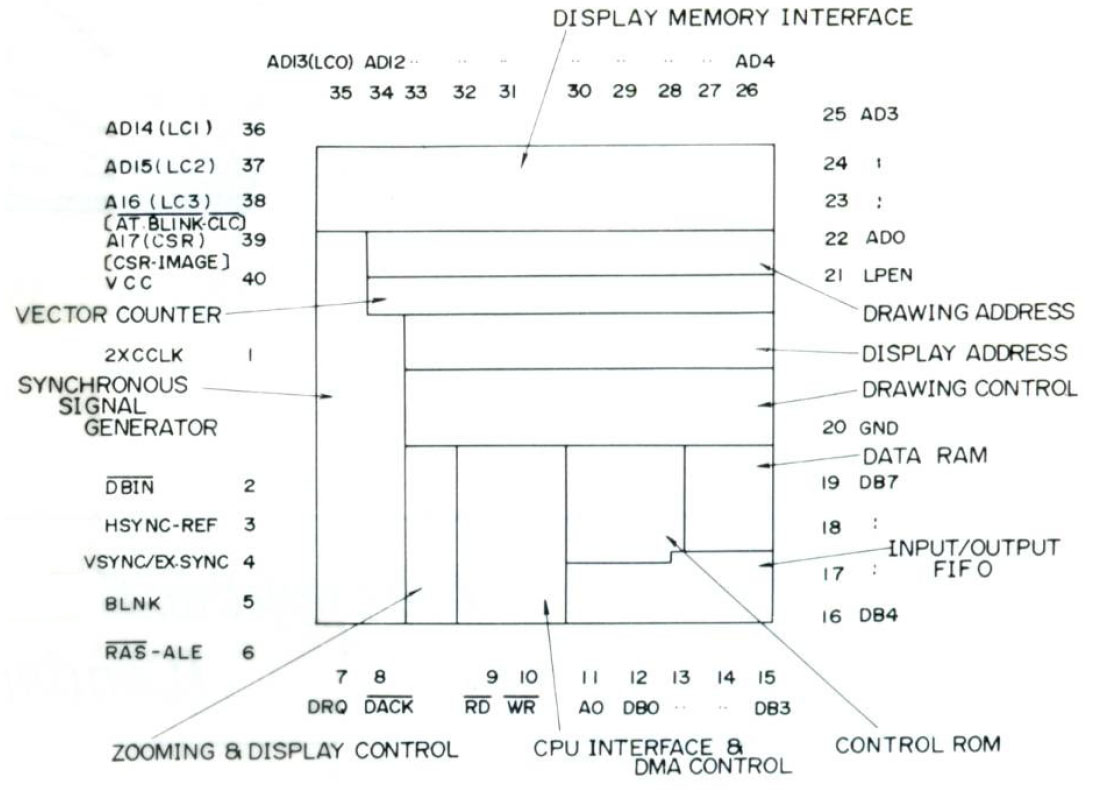

Das Datenblatt zeigt die Computerarchitektur, in die der µPD7220 üblicherweise eingebettet ist.

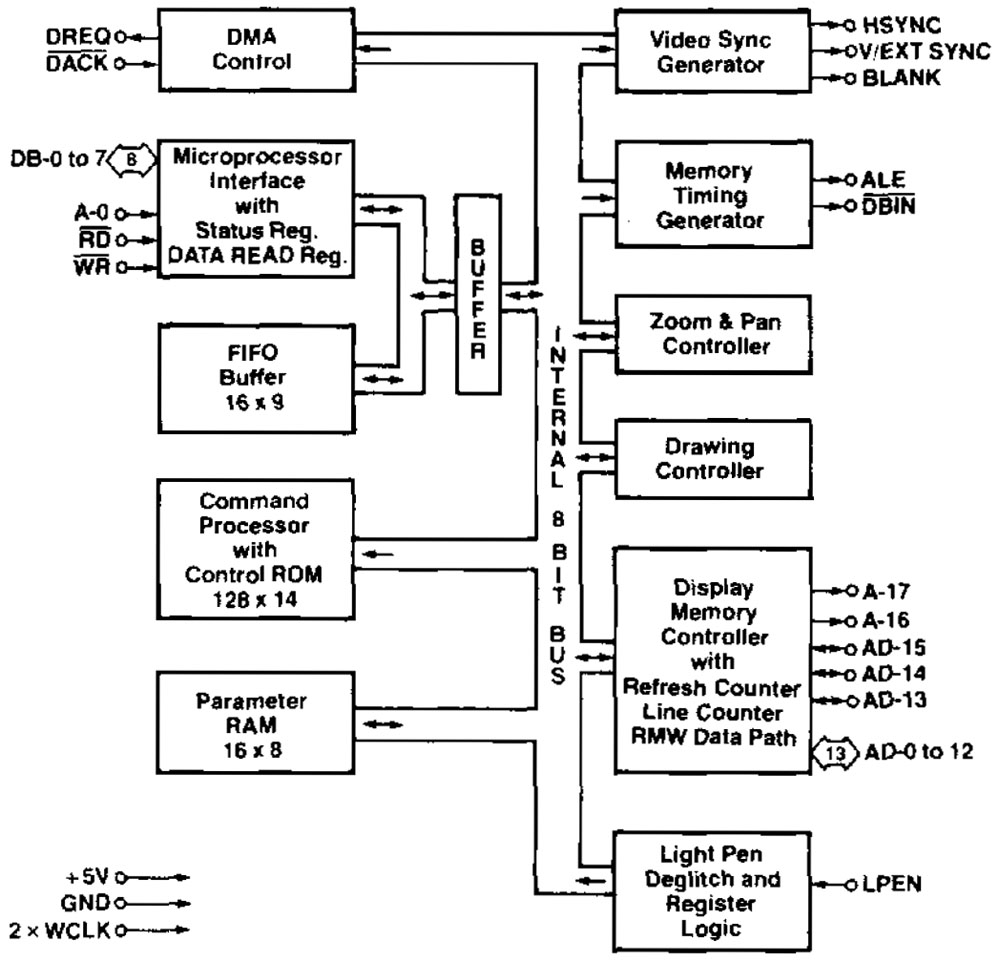

Das Datenblatt enthält außerdem ein Blockschaltbild des µPD7220. Neben den zu erwartenden Funktionsblöcken wurde auch die Auswertung eines sogenannten Light-Pens integriert. Dabei handelt es sich um einen Stift mit einem integrierten Fototransistor, der auf einen Röhrenbildschirm aufgelegt wird. Passiert der vom Grafikprozessor gesteuerte Elektronenstrahl diesen Punkt, so wird der Fototransistor leitend und der Grafikprozessor kann an das Computersystem zurückmelden, wo der Anwender den Stift platziert hat.

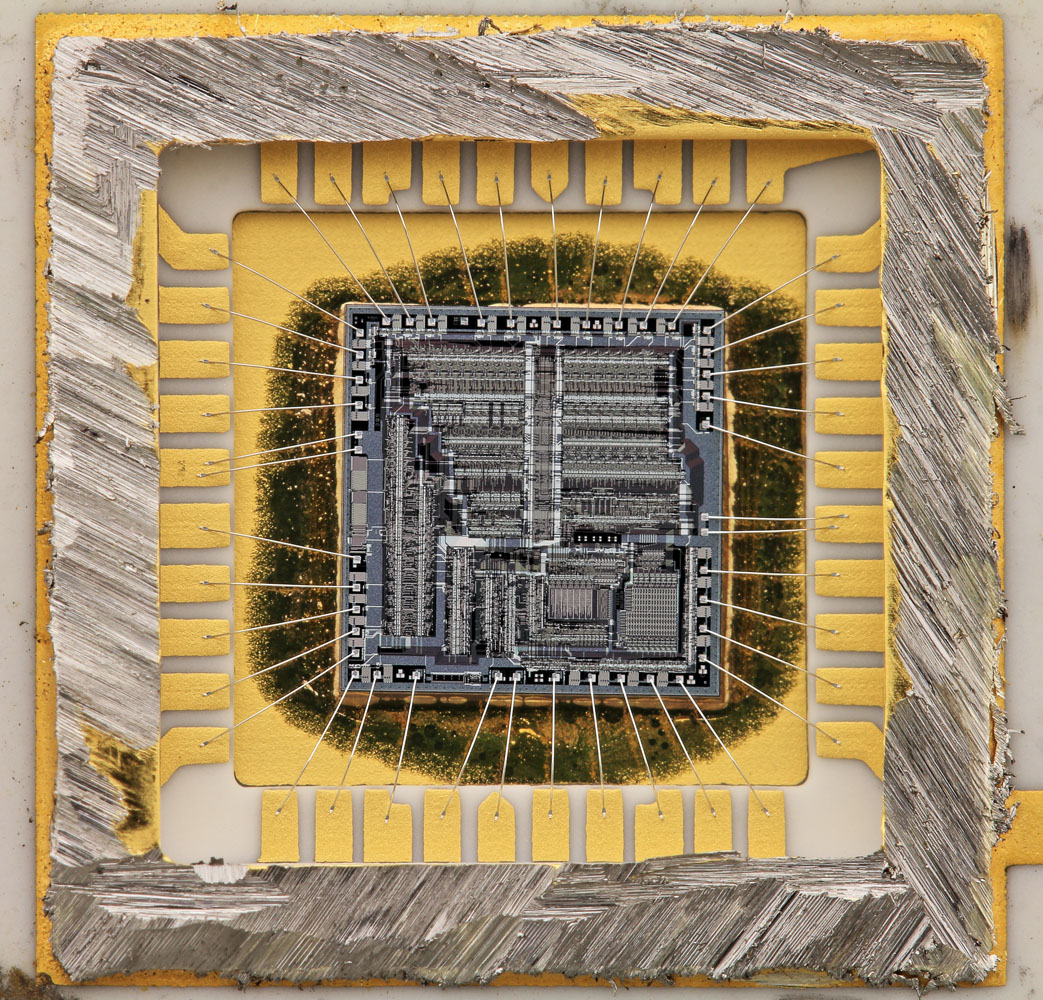

Der Deckel scheint auf dem Keramikgehäuse aufgeschweißt worden zu sein, da es sich auch mit hohen Temperaturen nicht entfernen lässt.

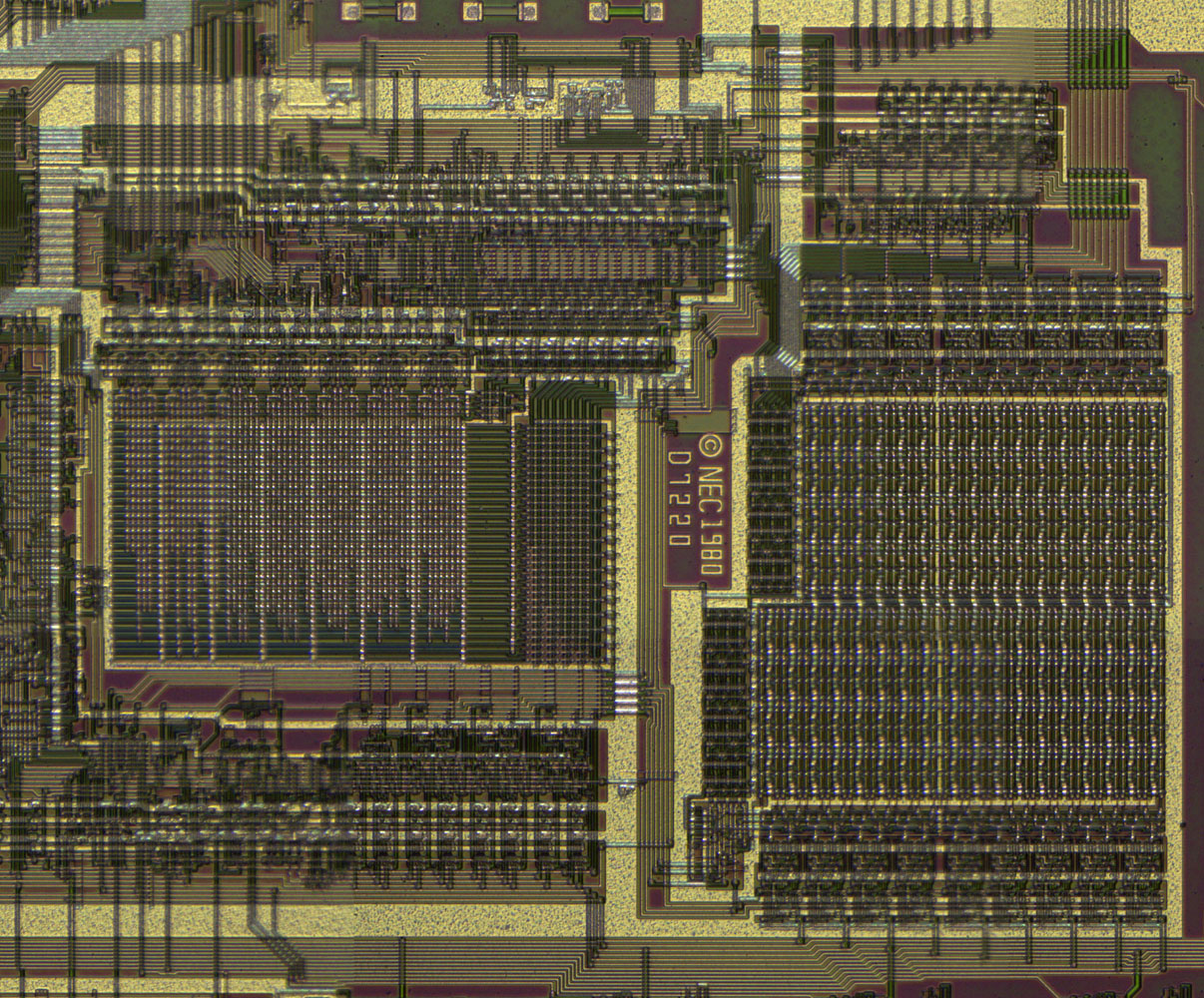

Die Abmessungen des Dies betragen 5,3mm x 5,2mm. Laut Datenblatt wurde der µPD7220 mit einem NMOS-Prozess gefertigt.

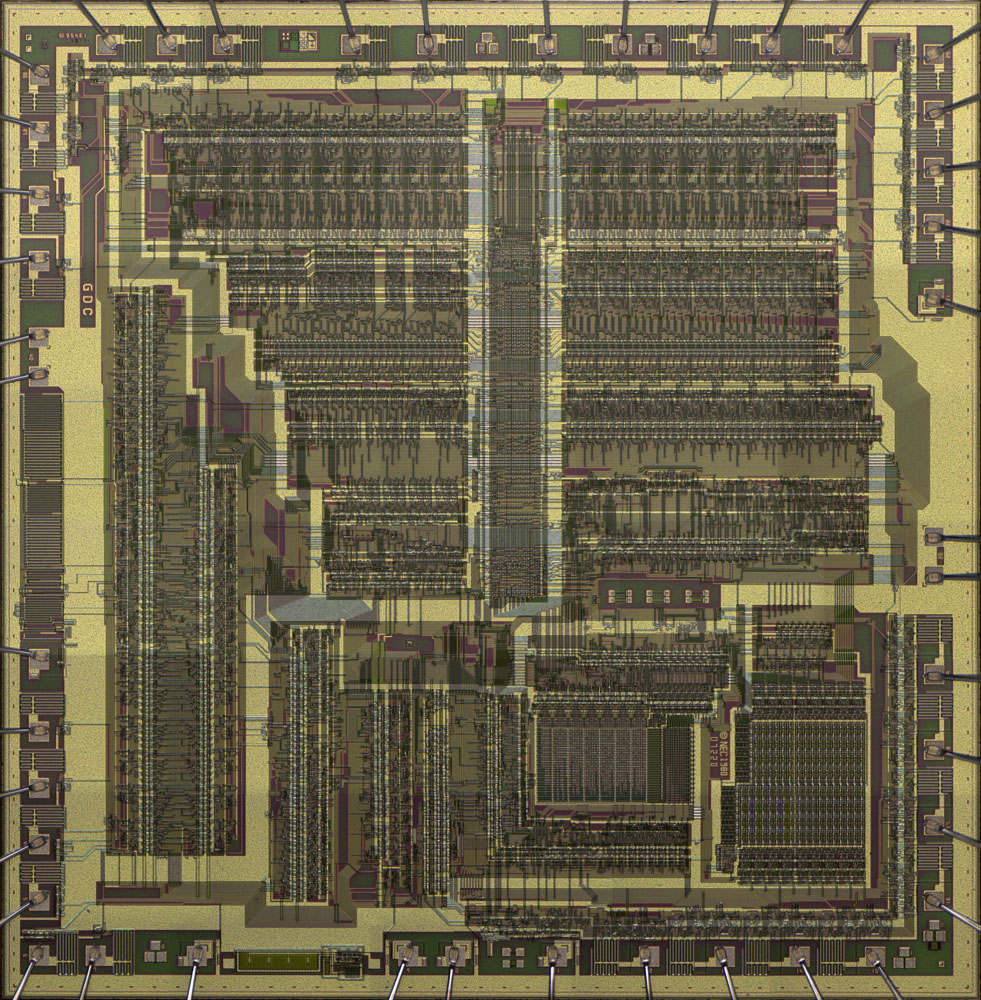

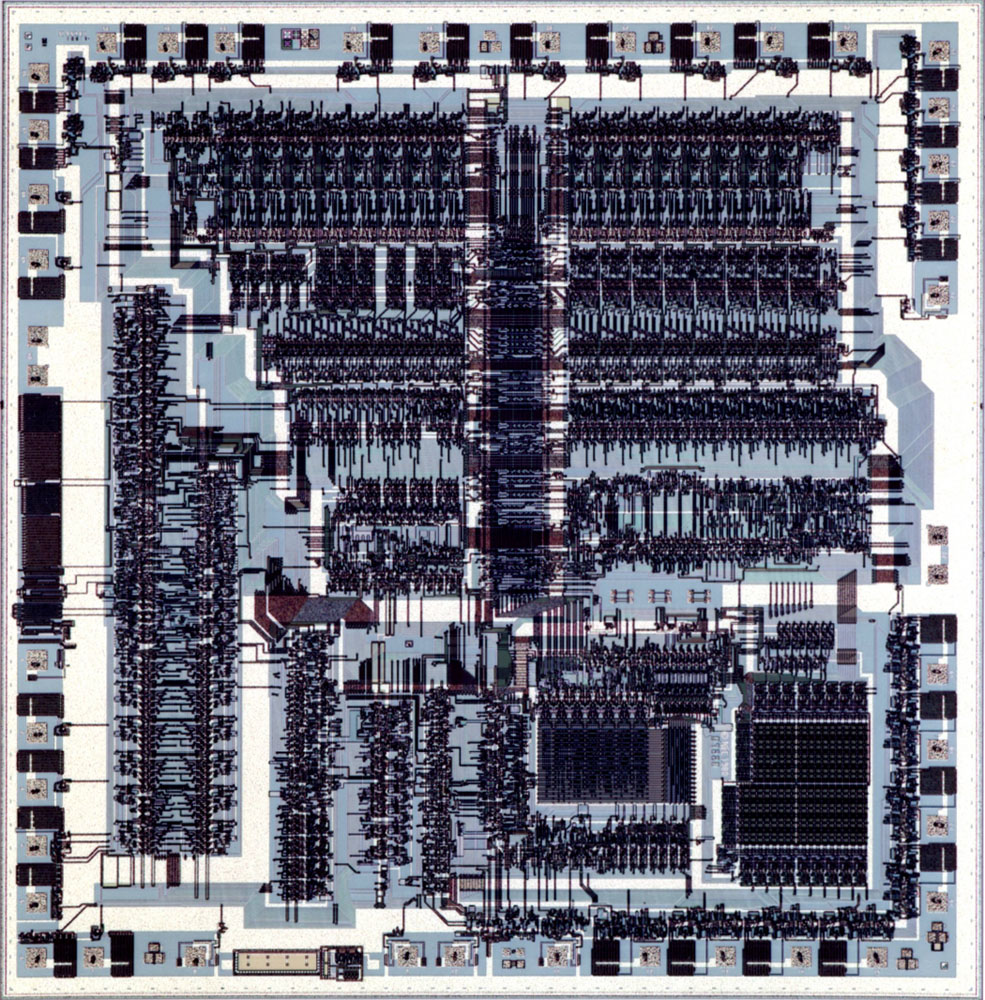

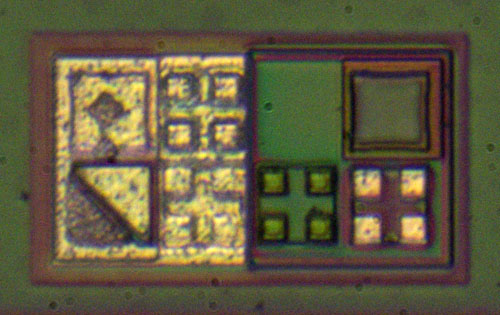

Im Rahmen der IEEE International Solid-State Circuits Conference 1981 wurde der µPD7220 unter dem Titel "A Single-Chip Graphic Display Controller" vorgestellt. In den zugehörigen Unterlagen findet sich das obige Abbild des µPD7220. Es stimmt oberflächlich betrachtet exakt mit dem Die des µPD7220 überein. In den Konferenzunterlagen wird die Größe des Dies mit 7mm x 7mm angegeben. Der vorliegende µPD7220 ist allerdings nur 5,2mm x 5,3mm groß. Die Seite www.oguchi-rd.com erklärt, dass die ersten Entwicklungsvarianten des Grafikprozessors mit einem 4µm-Prozess gefertigt wurden, während die Serienproduktion mit einem 3µm-Prozess erfolgte (Ablauf der Entwicklung). Das Verhältnis der beiden Prozesse stimmt mit dem Verhältnis der Abmessungen überein. Anscheinend beziehen sich die 7mm x 7mm auf die Entwicklungsvarianten.

Laut den IEEE-Konferenzunterlagen befinden sich mehr als 13.000 Transistoren auf dem Die.

In den IEEE-Konferenzunterlagen ist auch eine Grafik abgebildet, die zeigt an welcher Stelle des Dies welche Funktionsblöcke integriert sind.

Das Design stammt aus dem Jahr 1980. Das stimmt mit dem Zeitplan von www.oguchi-rd.com überein.

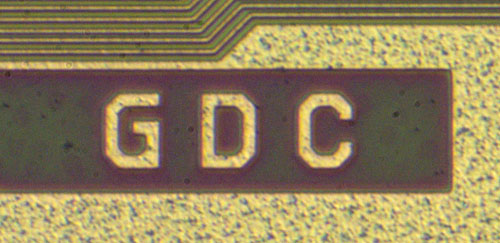

Die Buchstaben GDC stehen vermutlich für "Graphics Display Controller". Auf dem Abbild in den IEEE-Konferenzunterlagen sind diese Buchstaben noch nicht vorhanden.

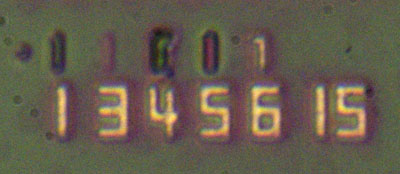

Hier scheinen die verwendeten Masken dargestellt zu sein. Demnach kamen vermutlich sechs Masken zum Einsatz.

Neben dem Maskensatz sind die Zahlen 052 abgebildet, was sich nicht weiter zuordnen lässt.

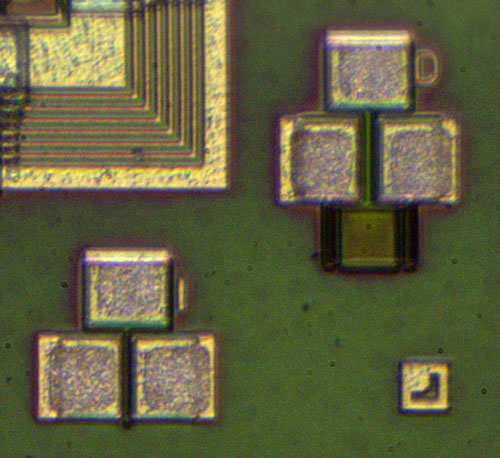

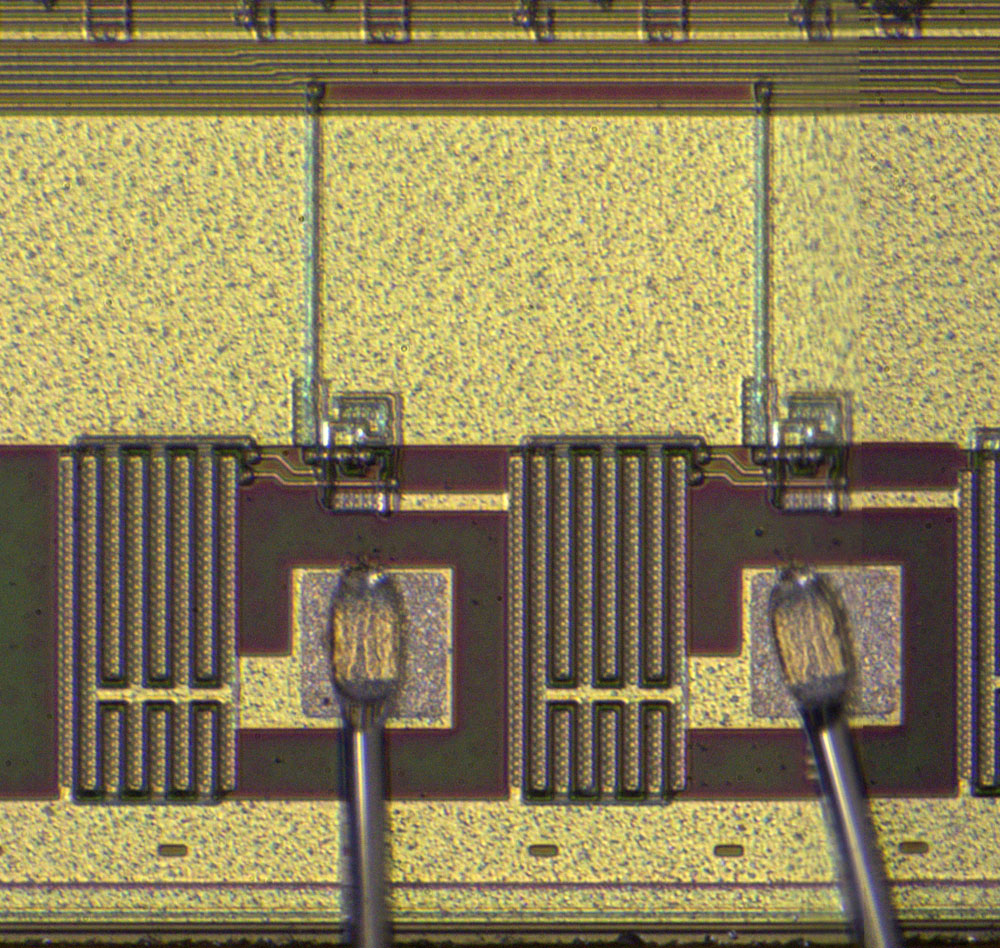

An der oberen Kante des Dies finden sich einige Strukturen, über die sich die einzelnen Herstellungsprozesse überwachen lassen.

Es wurden auch einige Teststrukturen integriert.

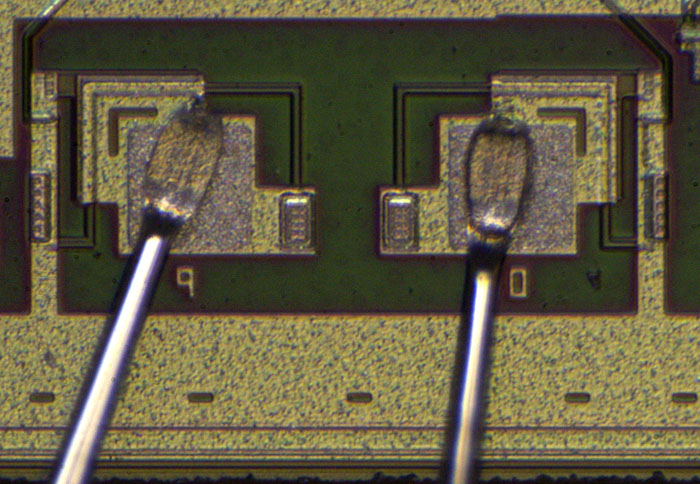

An der unteren Kante des Dies ist eine Schaltung integriert, die abgesehen von den Versorgungsleitungen mit keinem anderen Schaltungsteil verbunden ist. Rechts und links der Schaltung befinden sich Flächen, die an Testpads erinnern. Einen Großteil der Fläche nimmt ein Kondensator ein. Höchstwahrscheinlich handelt es sich um einen Bias-Generator, eine Ladungspumpe, die dafür sorgt, dass das Substrat ein negatives Potential annimmt. Dieses negative Potential verbessert die Eigenschaften der integrierten Transistoren. Die kleineren Strukturen im rechten Bereich stellen dann einen Ringoszillator und mehrere Dioden dar. Die Metallfläche, auf der sich das Die befindet sollte das gleiche negative Potential annehmen wie das Substrat. Dort lässt sich allerdings keine Spannung bestimmen. Die Fläche ist niederohmig mit dem Massepotential verbunden.

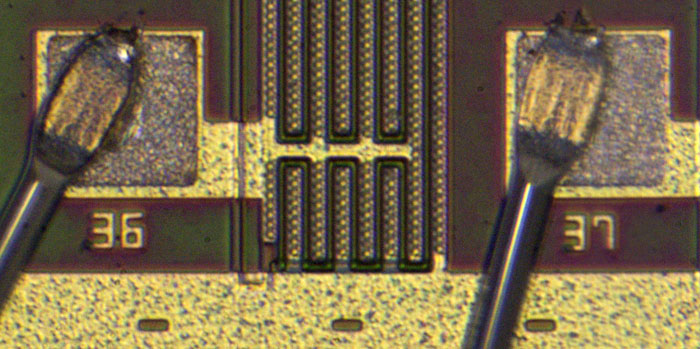

Die Bondpads sind durchnummeriert.

Neben dem Eingang für den Arbeitstakt befinden sich sehr große Transistoren, die höchstwahrscheinlich das Taktsignal aufbereiten und puffern.

Auf den Takteingang folgen mehrere Ausgänge mit entsprechend großen Strukturen. Die kleineren Strukturen dienen der Ansteuerung der großen Transistoren.

Eingänge sind mit den üblichen Schutzstrukturen ausgestattet.

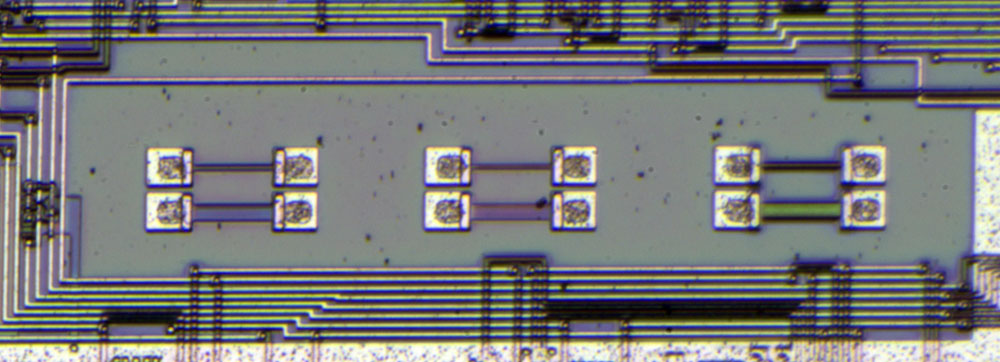

In der unteren rechten Ecke ist der Parameter-RAM und der FIFO-Puffer deutlich zu erkennen. Der untere FIFO-Puffer ist etwas größer (16x9) als der obere Parameter-RAM (16x8).

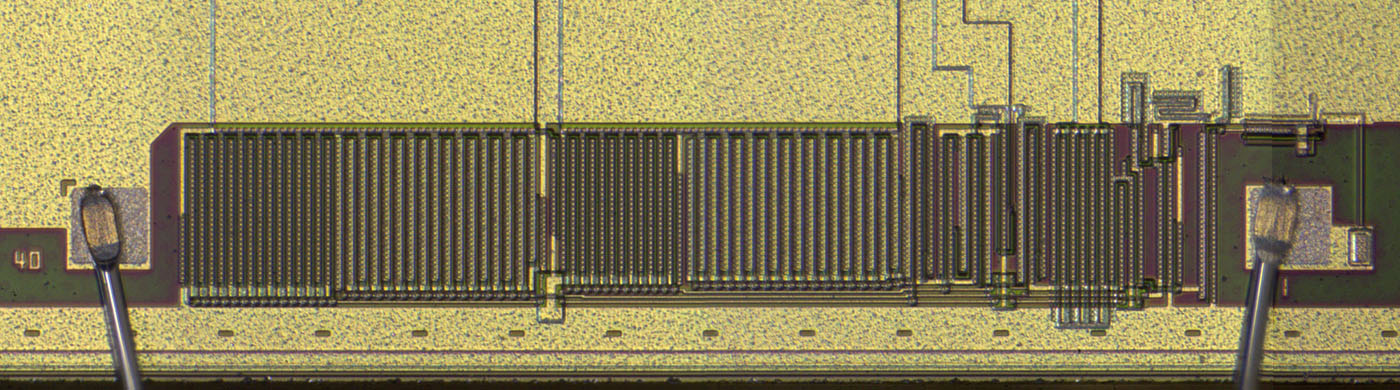

Der linke Block stellt den ROM dar, der die Steuerbefehle enthält. Da eine ROM-Zelle sehr viel weniger komplex ist als eine RAM-Zelle, belegt der Steuerungs-ROM trotz seiner Größe von 128x14 nur verhältnismäßig wenig Fläche. Man kann erkennen, dass die tatsächliche Aufteilung des ROMs nicht 128x14 sondern 65x32 ist.