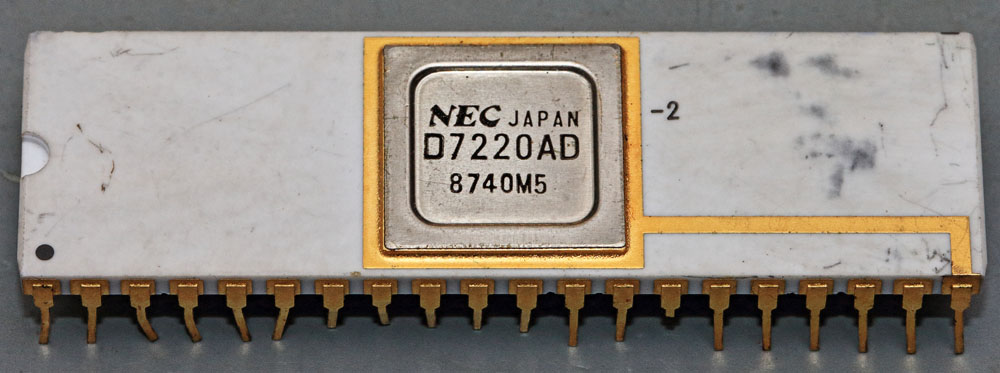

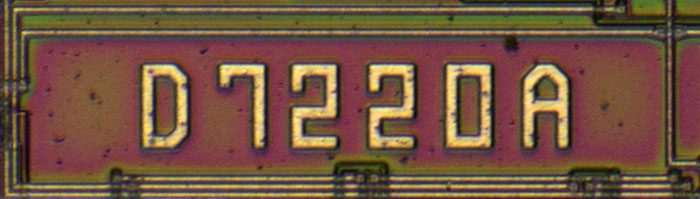

Der NEC µPD7220A ist der Nachfolger des µPD7220 und kam 1983 auf den Mark. Neben kleineren Änderungen kann der µPD7220A mit höheren Taktfrequenzen betrieben werden. Verfügbar waren die drei Varianten µPD7220AD, µPD7220AD-1 und µPD7220AD-2, die Taktfrequenzen von 6MHz, 7Mhz und 8MHz erlauben. Höchstwahrscheinlich handelt es sich auch hier um Sortierungen. Dazu passt, dass der Index -2 nicht auf dem Metalldeckel, sondern auf dem Keramikgehäuse aufgebracht wurde, was vermutlich während eines finalen Tests erfolgte.

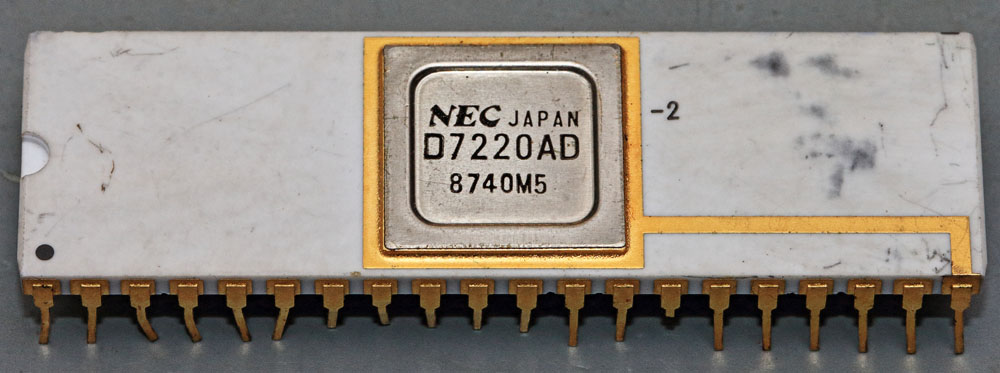

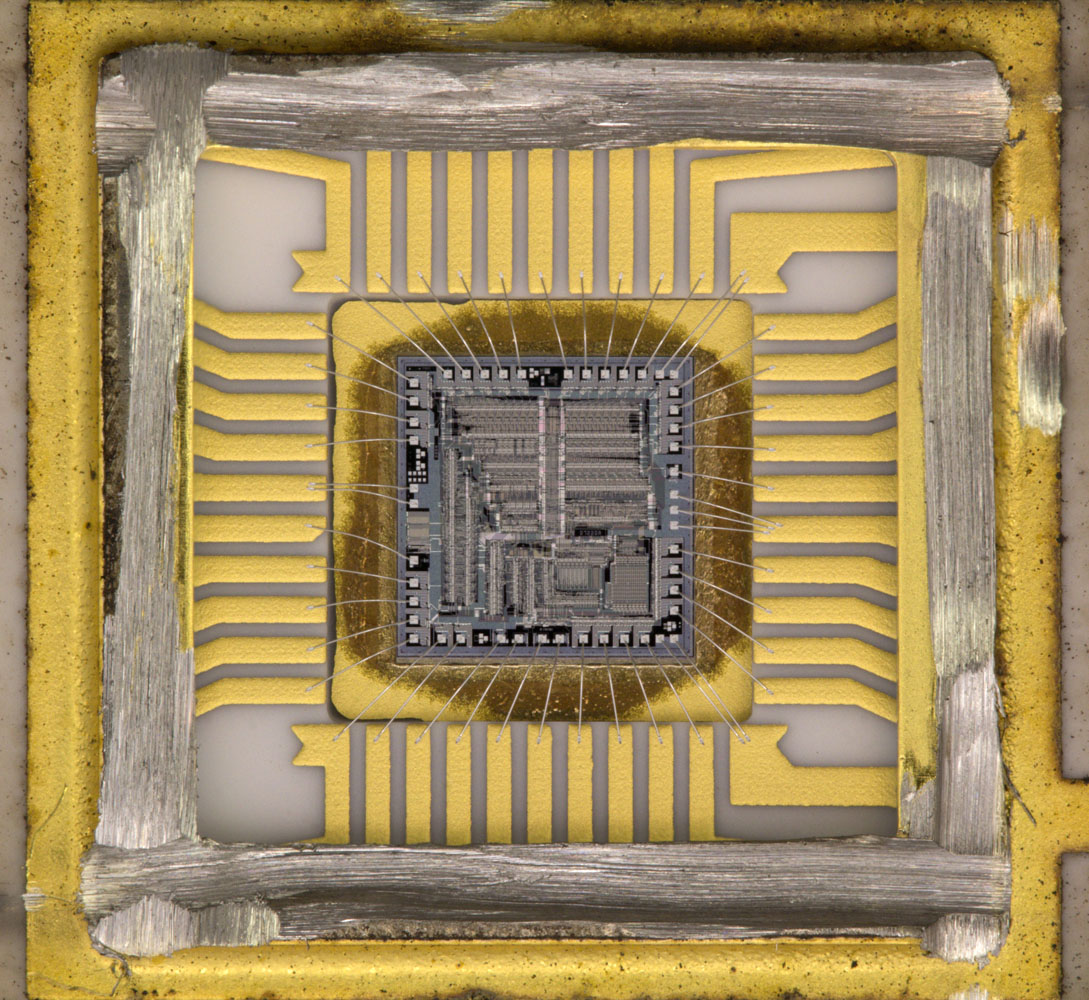

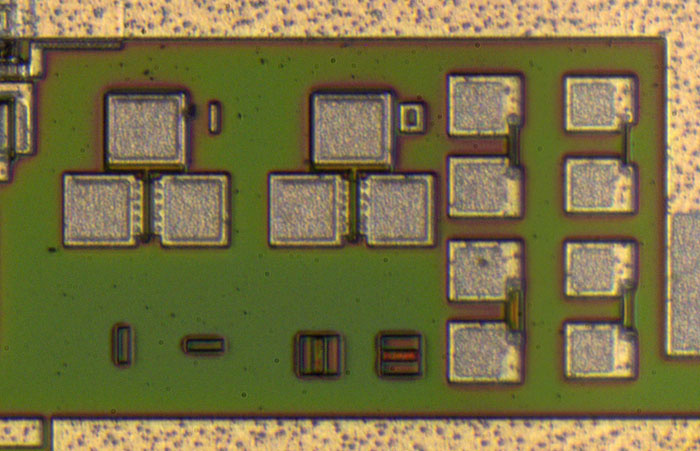

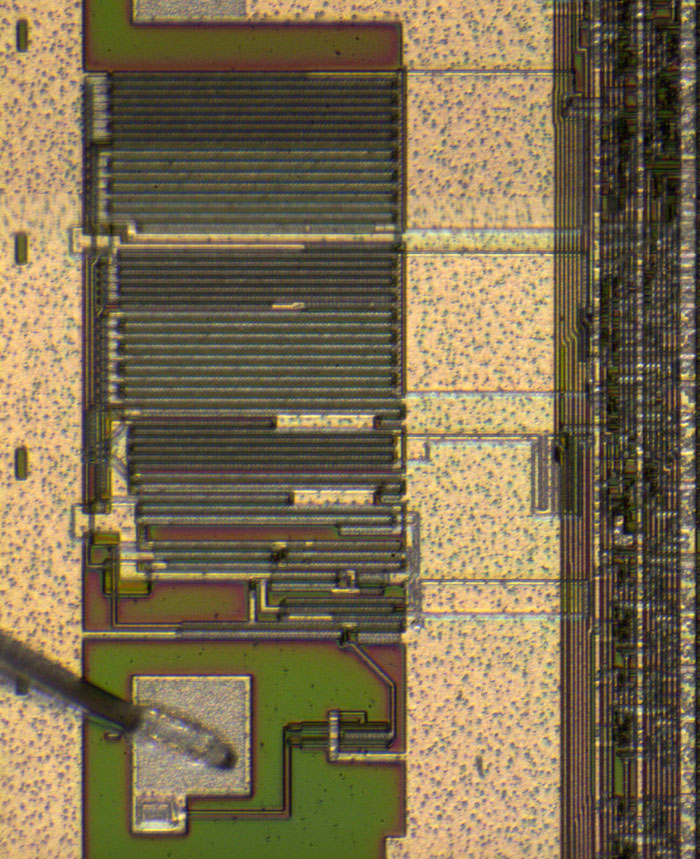

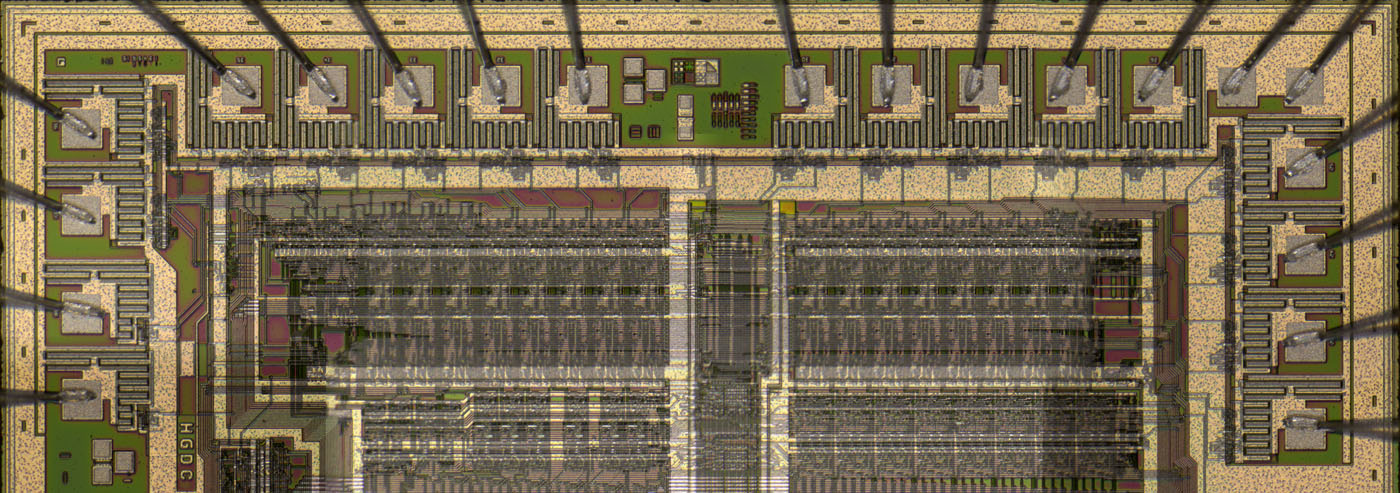

Nach dem Öffnen des Packages zeigt sich sofort, dass das Dies deutlich kleiner ist als das Die des Vorgängers µPD7220.

Die Abmessungen des Dies betragen 4,3mm x 4,2mm. Das Die des µPD7220 war noch 5,3mm x 5,2mm groß. Anscheinend ist man mit dem µPD7220A auf einen moderneren Prozess mit kleineren Strukturbreiten umgestiegen, was auch die höheren Taktfrequenzen erklären würde. Ausgehend vom Flächenverhältnis könnte hier ein Prozess mit einer minimalen Strukturbreite von 2,5µm zum Einsatz gekommen sein.

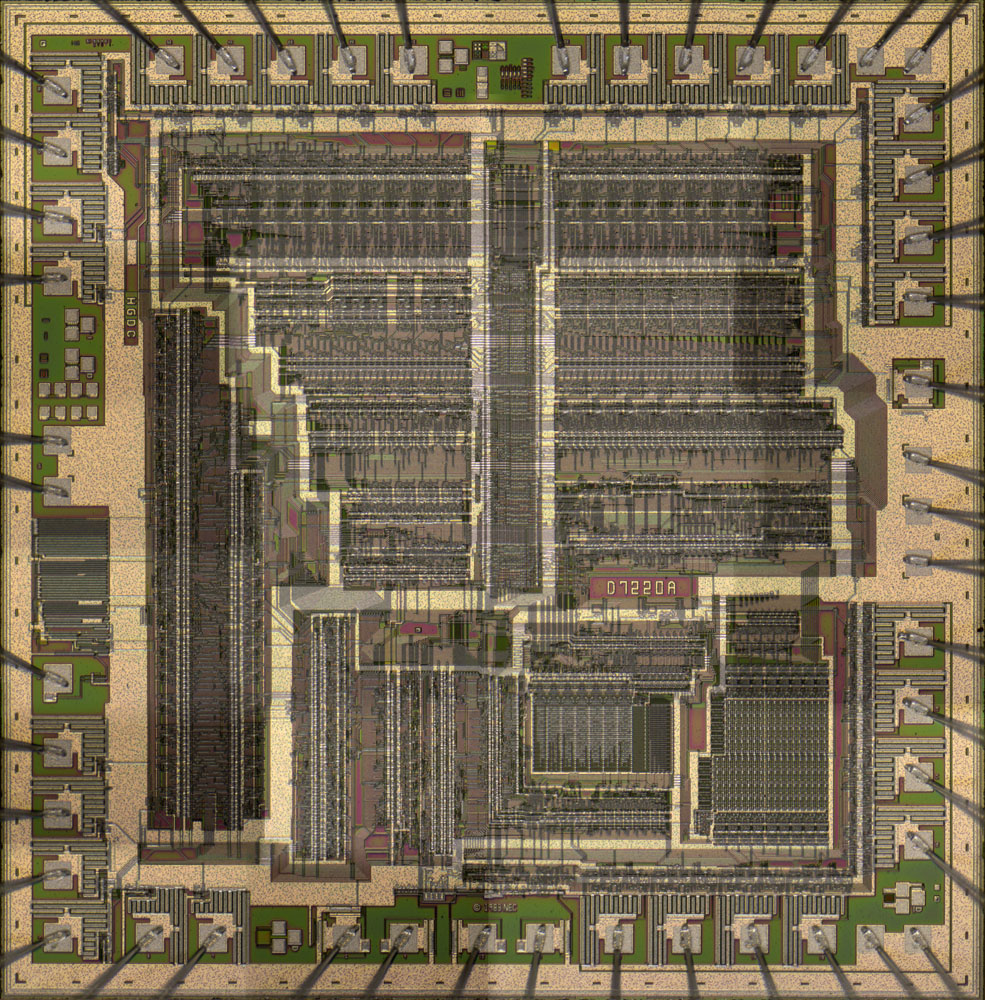

Oberflächlich betrachtet hat sich der grundsätzliche Aufbau des Grafikprozessors nicht geändert. Bei der Energieversorgung findet sich allerdings eine interessante Modifikation.

Der µPD7220A wurde im Jahr 1983 entwickelt.

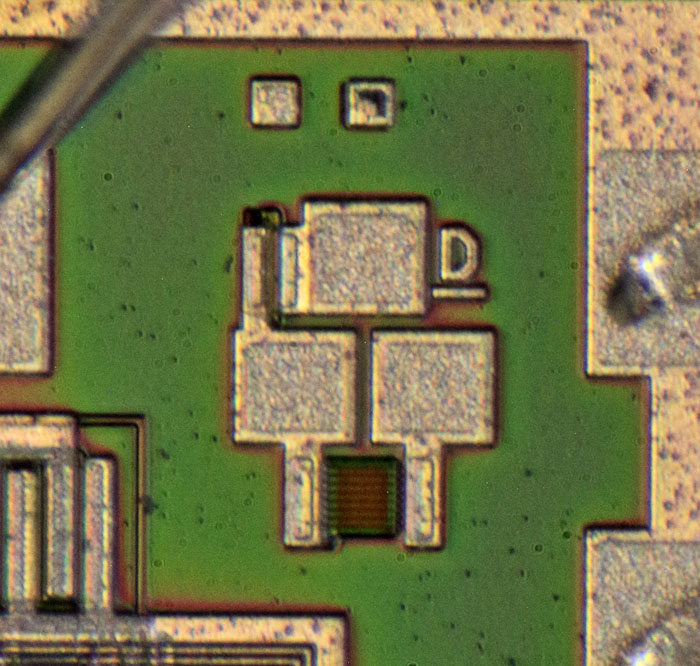

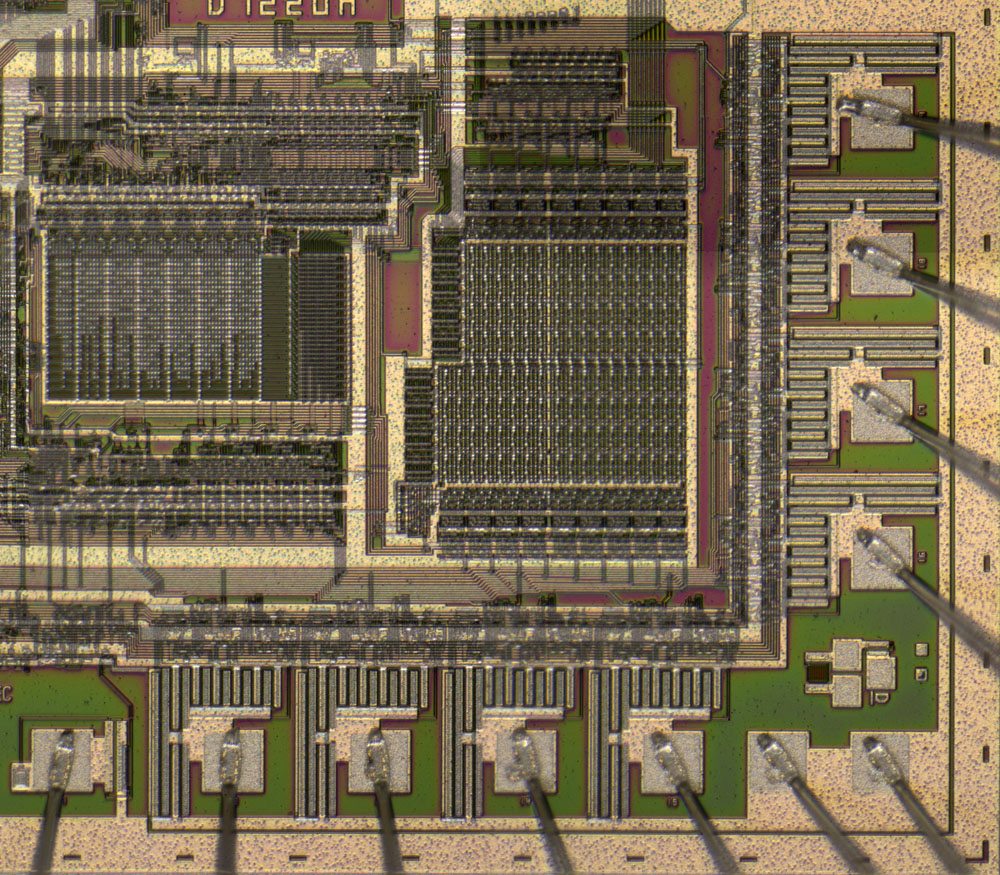

Während beim µPD7220 nur die Buchstaben GDC abgebildet war, was für "Graphics Display Controller" stand, wurde hier noch ein H vorangestellt. Laut Datenblatt steht das für "High Performance Graphics Display Controller".

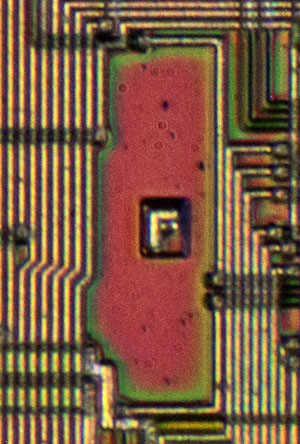

In der Mitte des Dies befindet sich ein Element in einer Freifläche, das sich nicht sauber auflösen lässt.

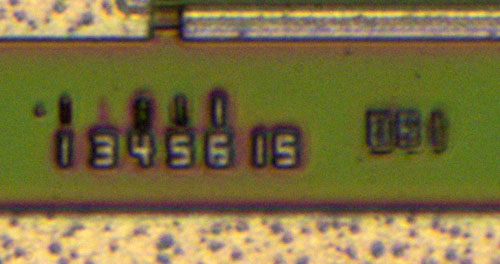

Die Maskenkennzeichnungen lassen keinen Unterschied zum µPD7220 erkennen. Die daneben abgebildeten Zeichen könnten die Zahl 61 darstellen. Im Hinblick auf die Zahl 52 des µPD7220 könnte es sich um eine Art Versionierung des Designs oder um die Bezeichnung eines Herstellungsprozesses handeln.

Am Rand des Dies sind diverse Teststrukturen integriert. Auf Teststrukturen im Inneren der Schaltung wurde verzichtet.

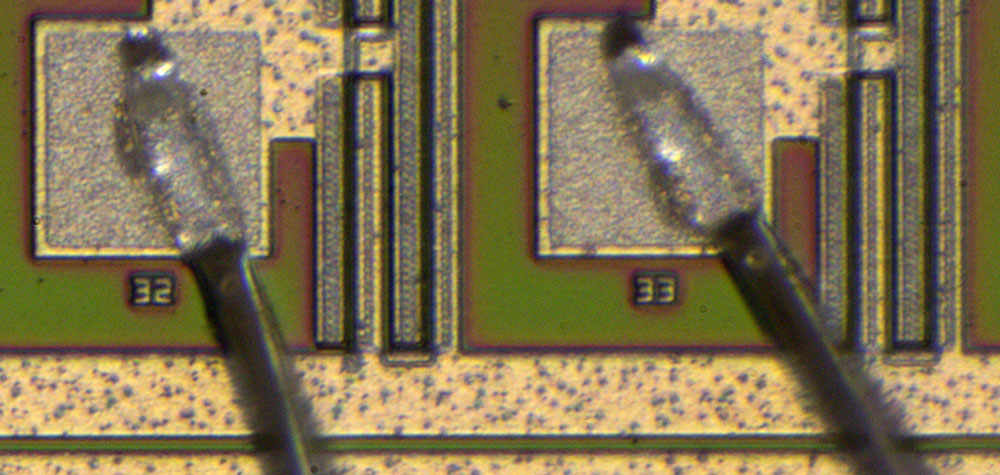

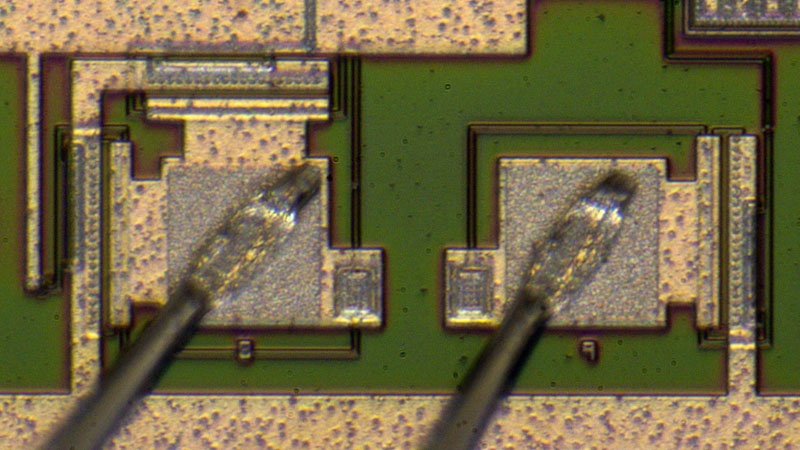

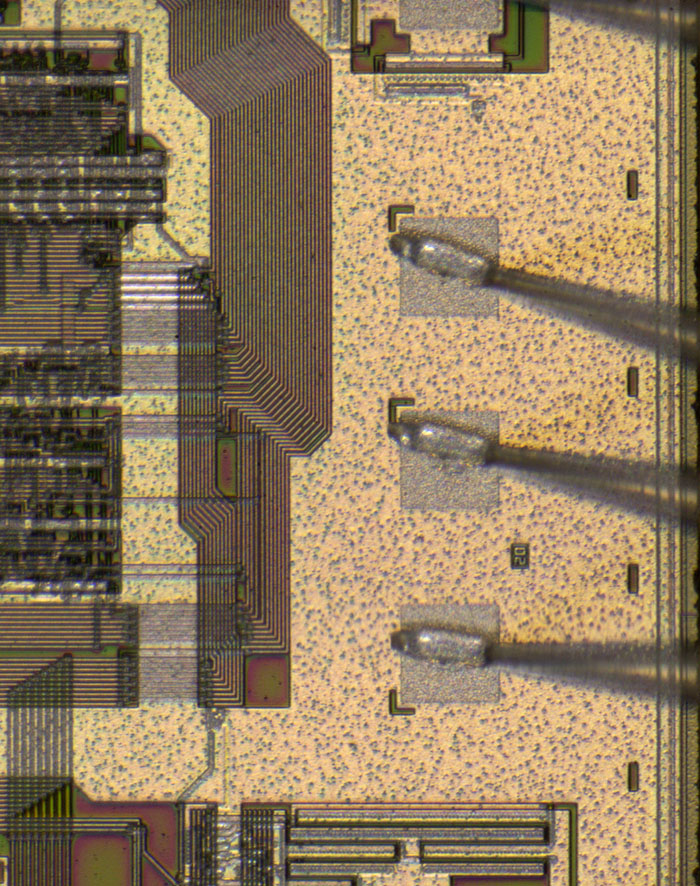

Die Bondpads sind auch hier sauber durchnummeriert.

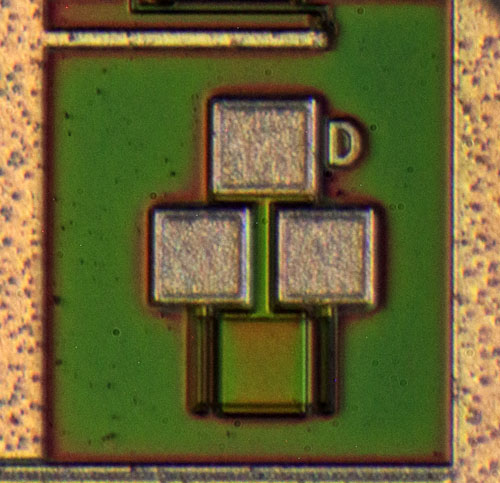

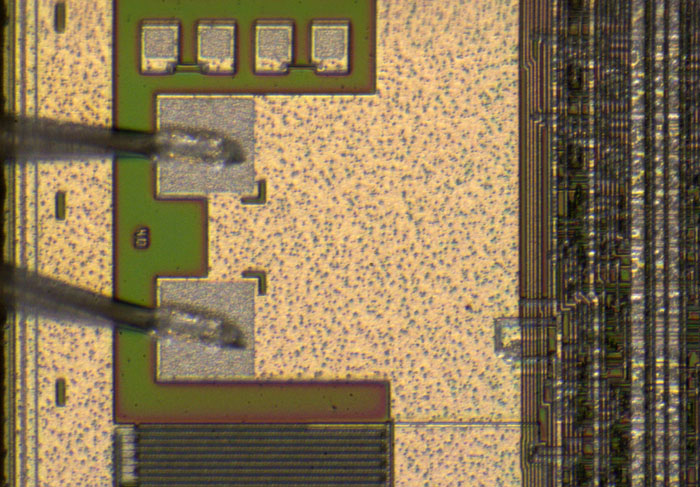

Die Aufbereitung des Taktsignals wurde etwas kompakter ausgeführt.

Auch die Ausgangstreiber sind stärker integriert.

Die Schutzstrukturen an den Eingängen scheinen minimal anders aufgebaut zu sein.

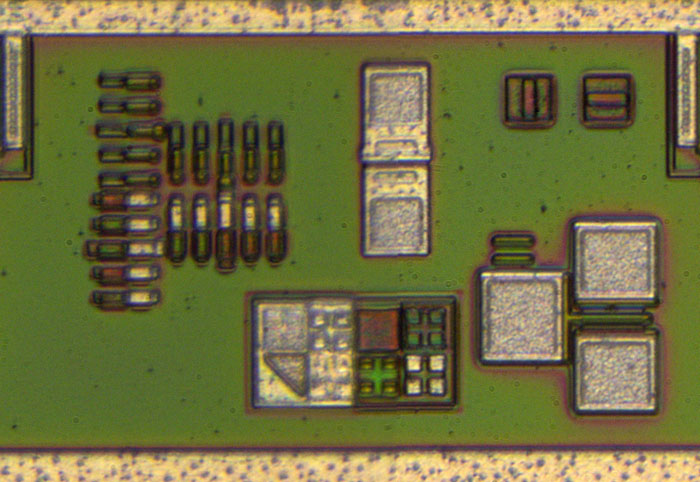

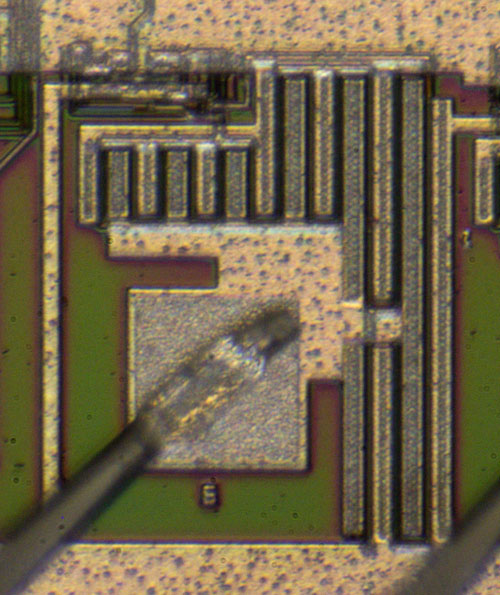

Der optisch größte Unterschied zum µPD7220 ist die spezielle Masseanbindung der Bus-Schnittstellen. Hier sind die I/O-Pins der Prozessor-Bus-Schnittstelle zu sehen. Sie besitzen eine eigene, abgesetzte Masseanbindung, die über zwei Bonddrähte mit dem Massepotential des Gehäuses verbunden ist. Das Die des µPD7220 führt nur ein Massepotential, auf das alle Schaltungsteile zugreifen.

Die Schnittstelle zum Grafikspeicher wurde beim µPD7220A ebenfalls mit einer exklusive Masseanbindung erweitert, die über zwei Bonddrähte in der oberen rechten Ecke an das Massepotential des Gehäuses angebunden ist.

Trotz der zwei exklusiven Masseanbindungen hat man die Masseanbindung der restlichen Schaltung von zwei auf drei Bonddrähte erweitert.

Beim Versorgungspotential waren zwei Bonddrähte weiterhin ausreichend.

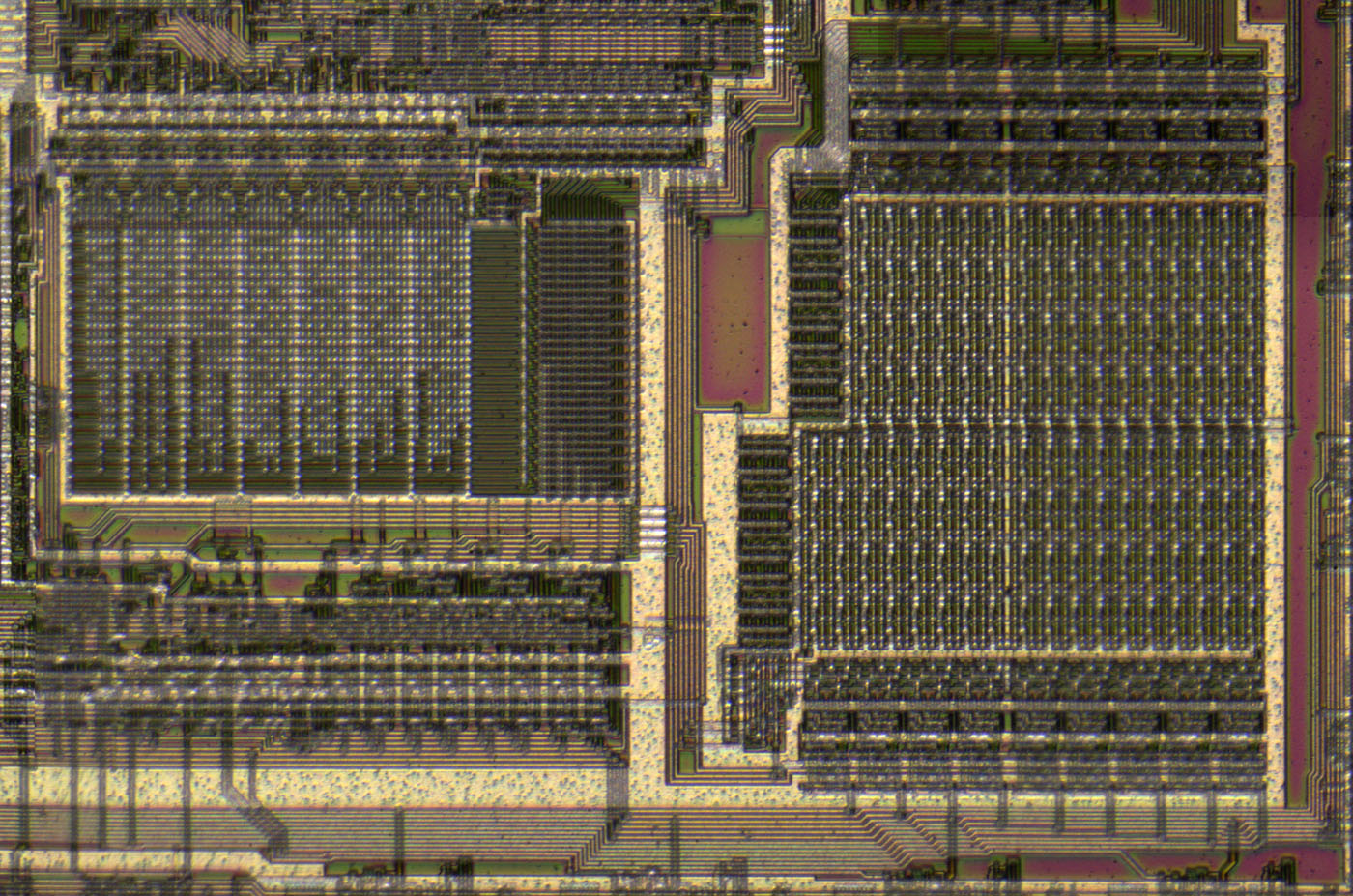

Parameter-RAM und FIFO-Puffer sind in der unteren rechten Ecke des Dies weiterhin deutlich zu erkennen. Durch die geringere Strukturbreite lassen sich die Konturen aber etwas schlechter auflösen als beim µPD7220.