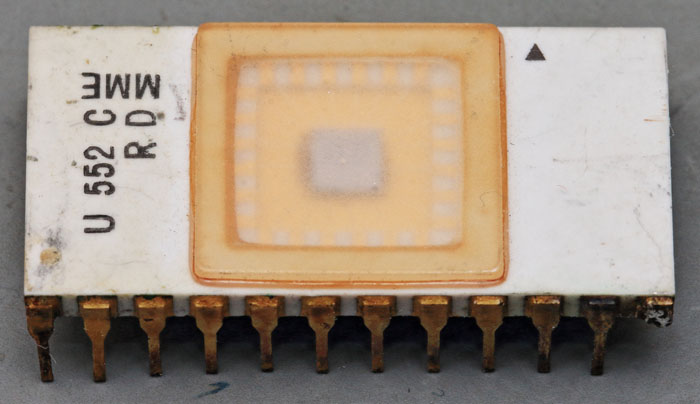

Der U552C ist ein p-Kanal-EPROM mit einer Speichertiefe von 256B. Der Baustein ist vergleichbar mit dem 1702A, dem ersten kommerziell verfügbaren EPROM, der ursprünglich von Intel entwickelt wurde. Hersteller war der VEB Mikroelektronik Karl Marx, abgekürzt MME. Die Buchstaben RD stehen für eine Fertigung im vierten Quartal 1983.

Um den Speicher mit UV-Licht löschen zu können, besitzt das Package ein lichtdurchlässiges Fenster. Laut Datenblatt konnte der U552 in zwei Varianten bezogen werden. Das hier vorliegende Modell besitzt ein spezielles Keramikfenster, das für UV-Licht durchlässig ist. Die zweite Gehäusevariante war mit einem Quarzglasfenster ausgestattet. Zum sicheren Löschen des Speichers benötigt man beim Keramikfenster eine Strahlungsdosis von mindestens 15Ws/cm² (254nm), während beim Quarzglasfenster 6Ws/cm² ausreichend sind.

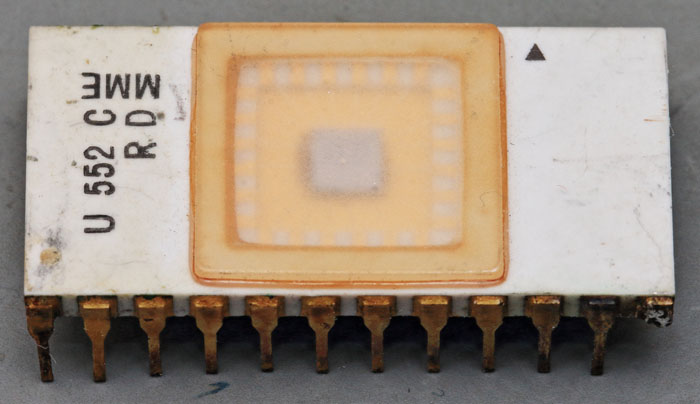

Das Datenblatt zeigt die Zuordnung der Pins. Als p-Kanal-EPROM benötigt der Baustein im Lesebetrieb neben einer 5V Versorgung an Ucc zusätzlich eine -9V Versorgung an Ugg und Udd. Über Ubb wird das Ucc-Potential mit dem Substrat verbunden. Zum Programmieren sind bis zu -48V notwendig. Gleichzeitig liegen dabei an Ubb bis zu 13,2V an.

Der Pin CS aktiviert den Speicher. PR dient zum Programmieren. P1 und P2 werden als Prüfeingänge bezeichnet.

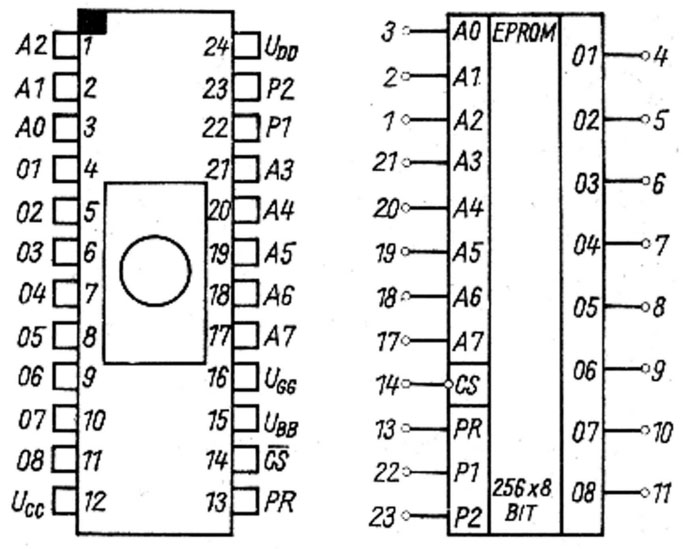

Die Potentiale Udd und Ucc sind jeweils über zwei Bonddrähte angebunden. Die Fläche des Ubb-Potentials ist nicht direkt kontaktiert, wird aber im Package mit der Metallisierung unter dem Die verbunden. Der Pin des Ubb-Potentials ist auf dem Gehäuse extra mit einem Pfeil markiert.

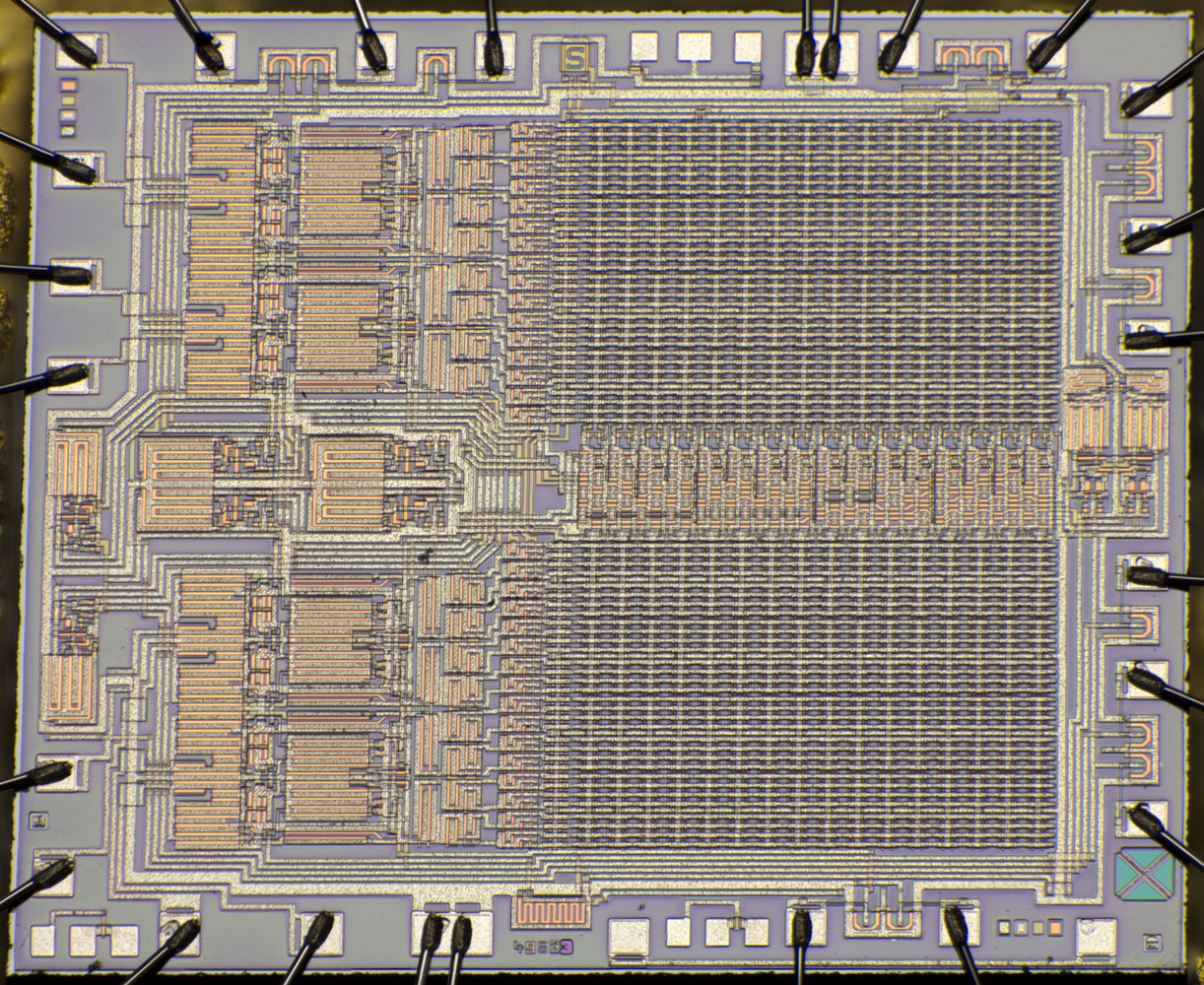

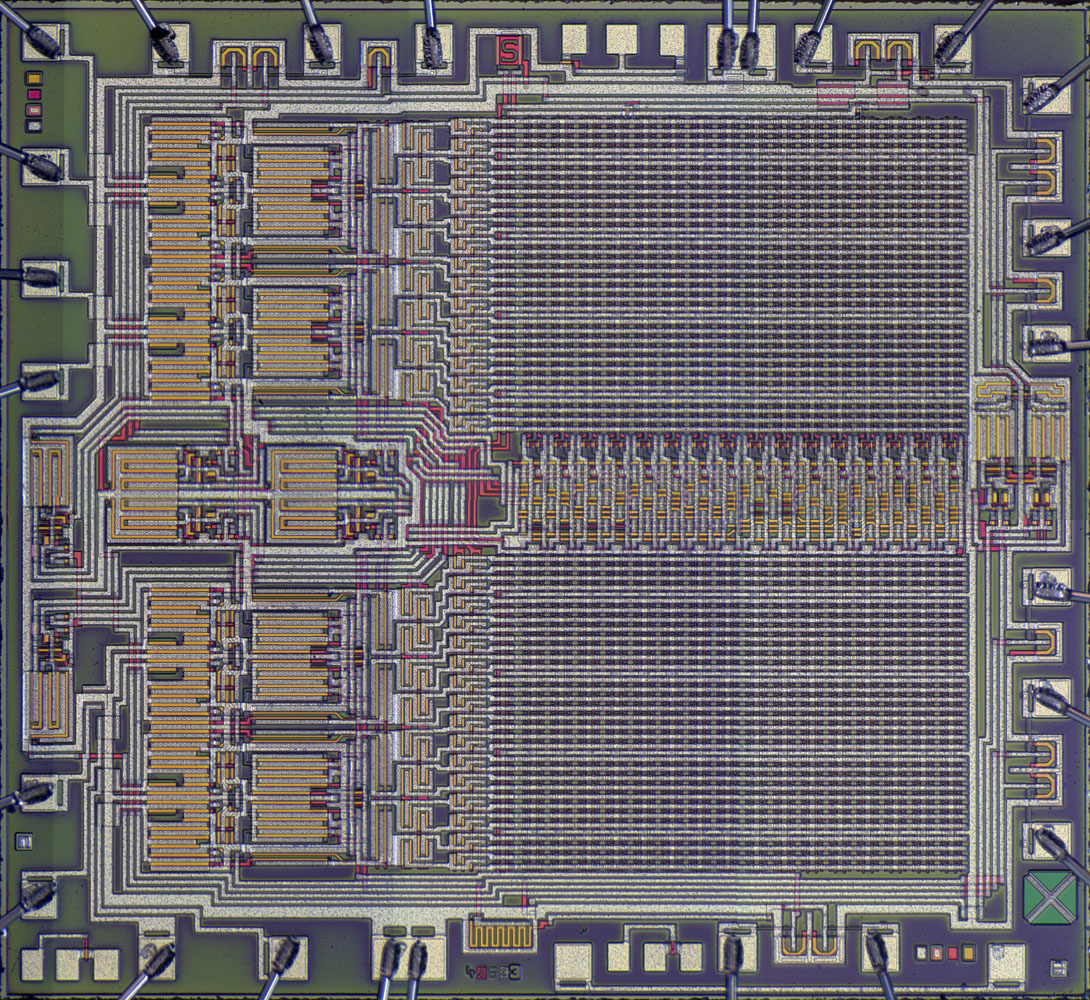

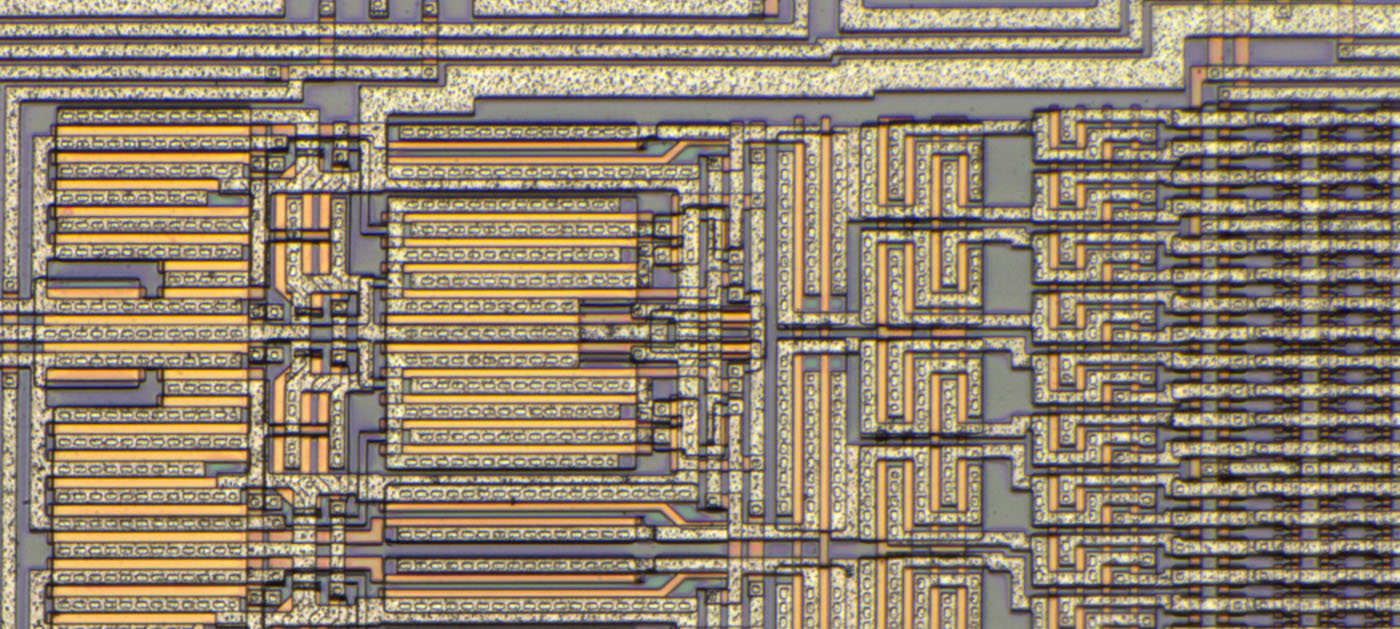

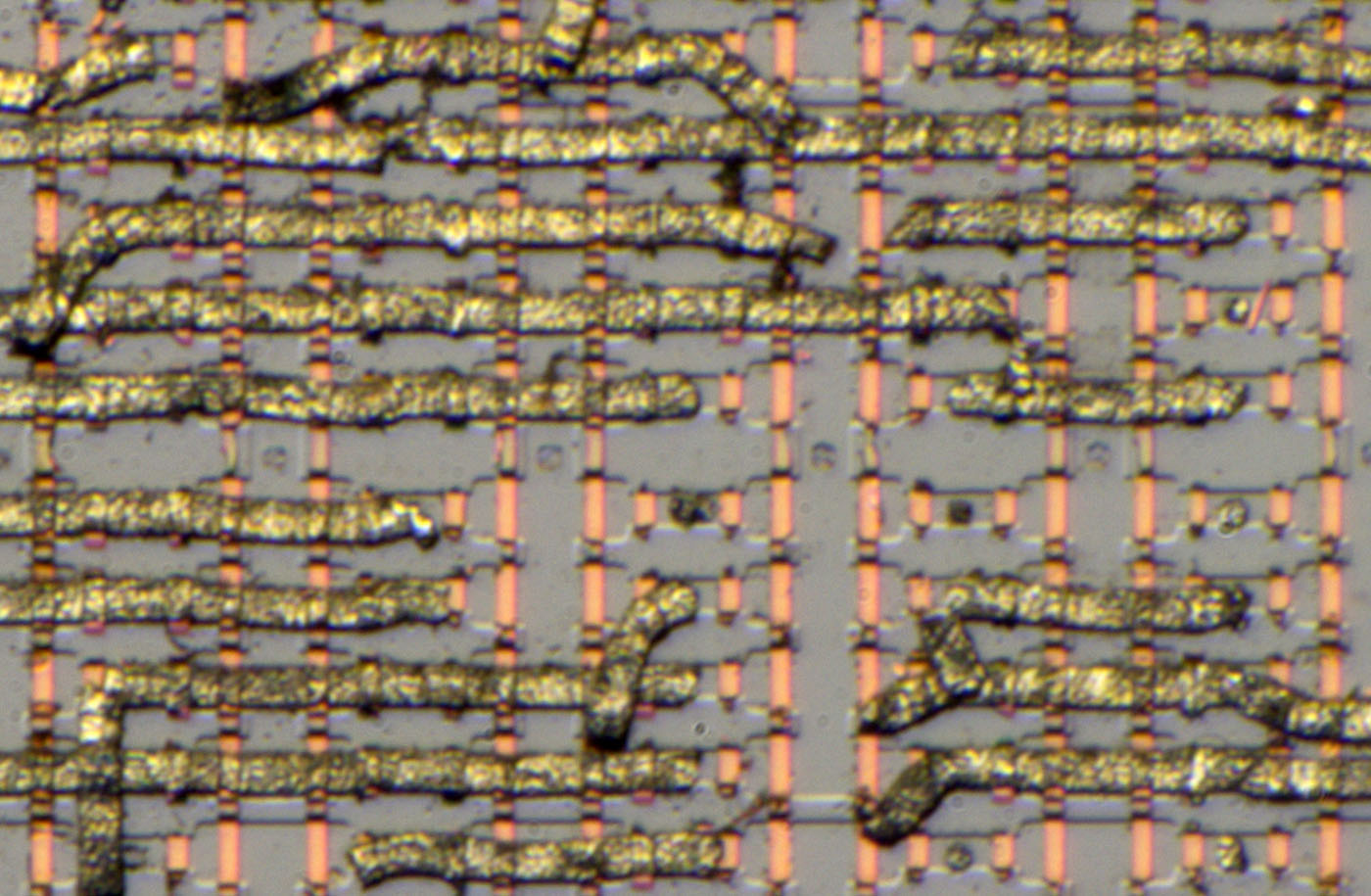

Die Abmessungen des Dies betragen 3,5mm x 3,2mm. Die minimalen Strukturbreiten sind nur etwas kleiner als 10µm, so dass sich die Schaltung relativ gut nachvollziehen lässt.

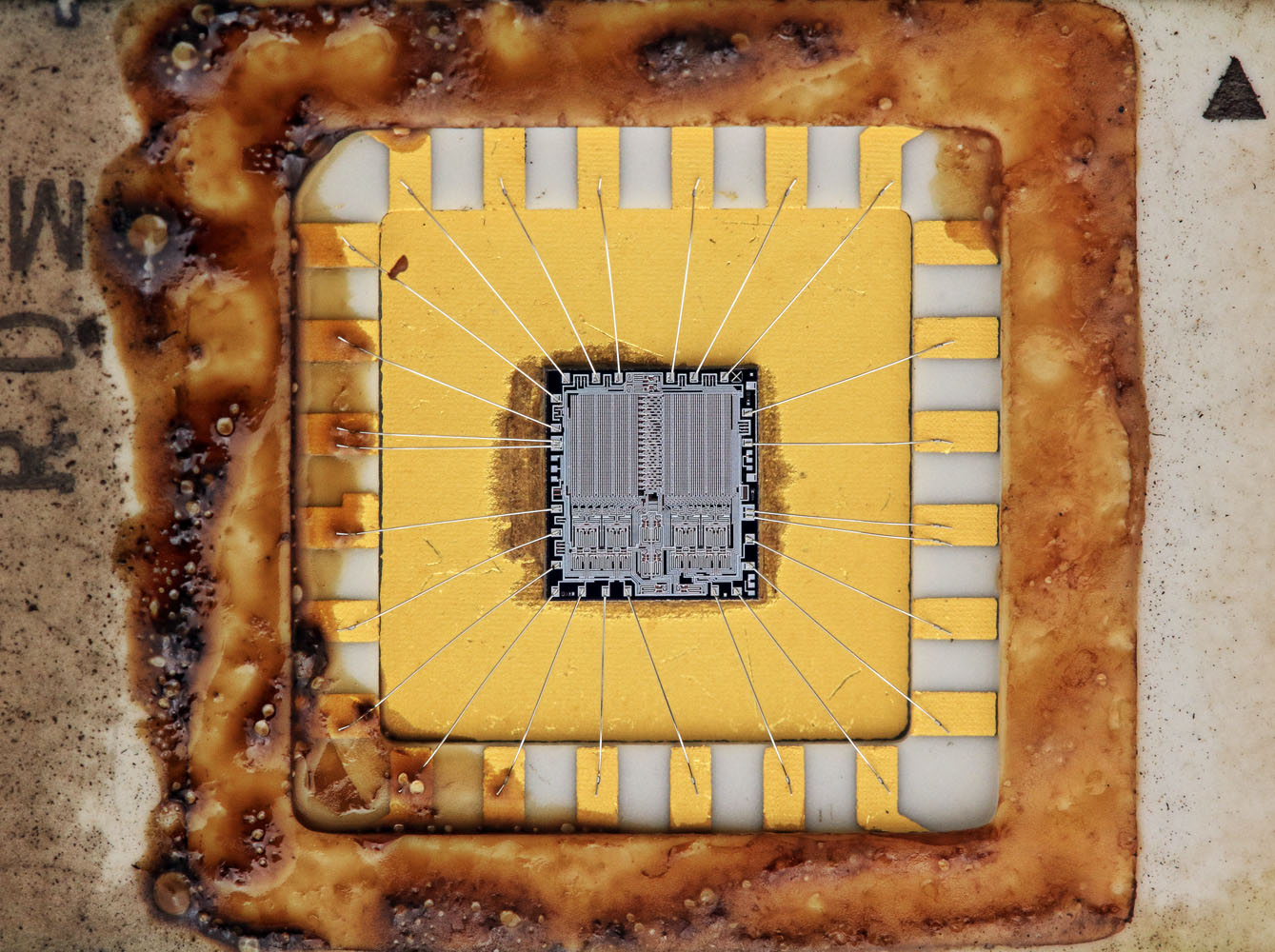

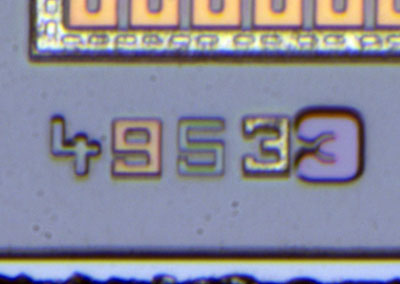

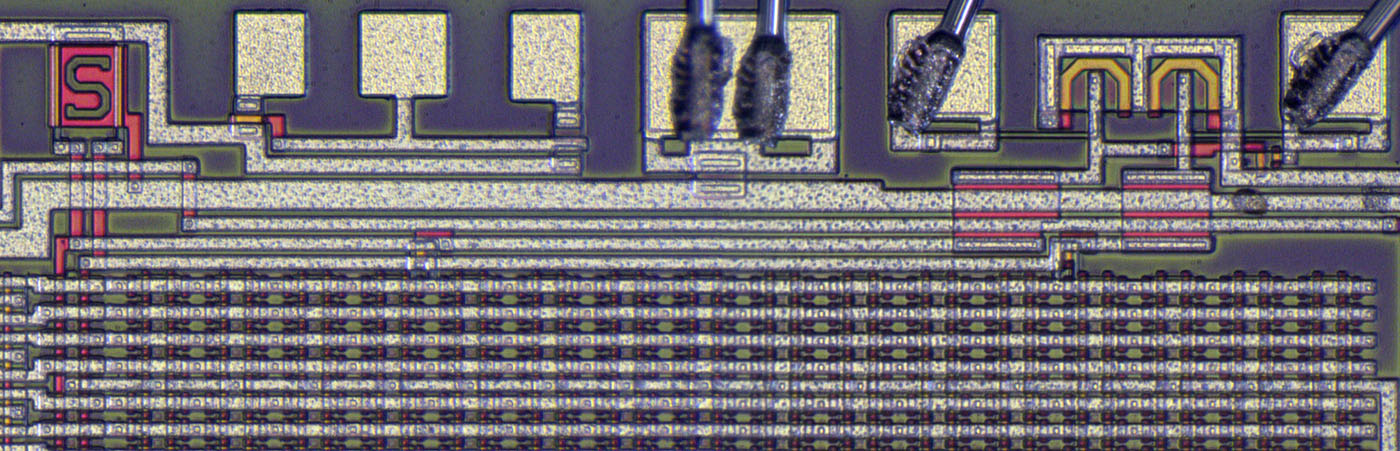

In der oberen linken Ecke des Dies befinden sich einige Strukturen zur Überprüfung der Fertigungsqualität. An der unteren Kante sind mit den verschiedenen Masken fünf Zahlen abgebildet. In der DDR wurden die unterschiedlichen Masken meist mit Buchstaben und die Revisionen der Masken mit Zahlen beschriftet. Demnach wurde hier eine Maske bereits acht Mal überarbeitet.

Die Metalllage ist eindeutig erkennbar. Die Maske ganz rechts scheint Öffnungen in der obersten Siliziumoxid zu erzeugen, um die Bondpads frei zu legen. Das orange Material (9) kommt als Gateelektrode zum Einsatz. Es muss sich dabei folglich um eine Polysiliziumschicht handeln. Eine der Masken links und rechts davon (4 und 5) entfernt höchstwahrscheinlich im ersten Schritt der Fertigung das sogenannte Feldoxid, um aktive Bereich zu definieren. Die andere der beiden Masken erzeugt wahrscheinlich die Durchkontaktierungen zwischen den aktiven Bereichen und der Metalllage.

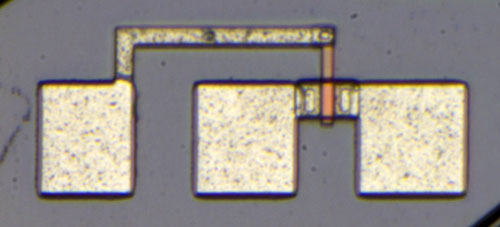

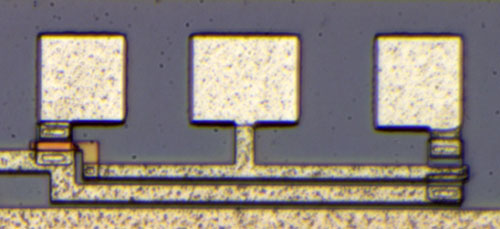

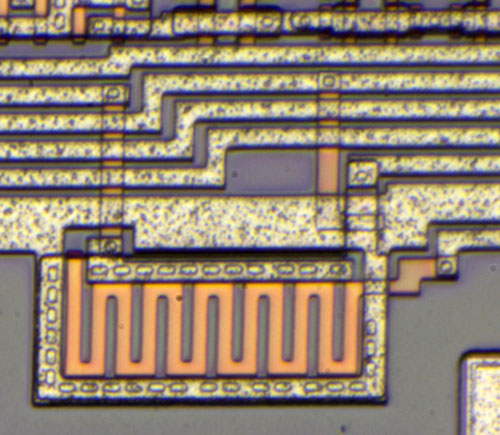

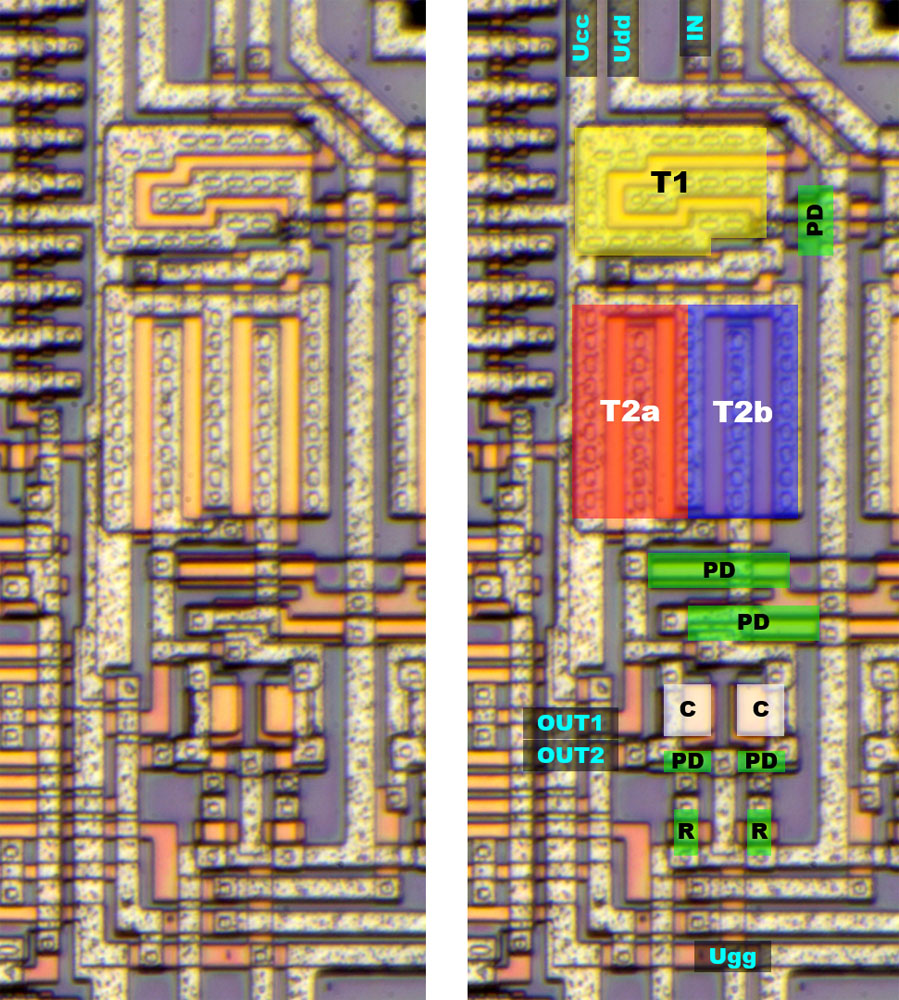

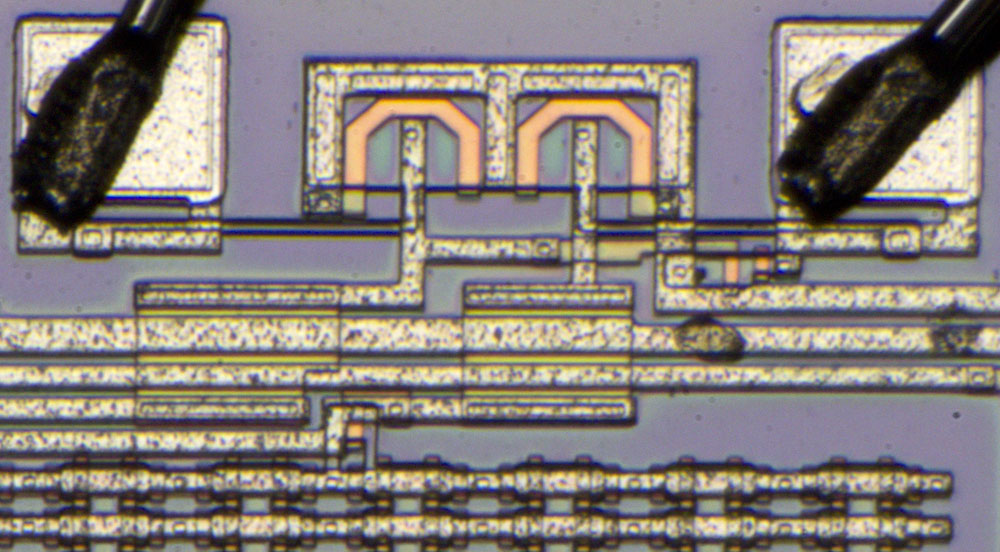

An der unteren und der oberen Kante des Dies sind mehrere Teststrukturen integriert. Die oberste Teststruktur scheint einen normalen p-Kanal-MOSFET mit einer Polysilizium-Gateelektrode zu enthalten.

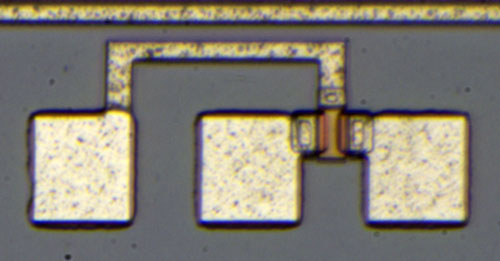

Im mittleren Bild ist eine Teststruktur mit zwei MOSFETs abgebildet. Links scheint es sich um einen normalen MOSFET zu handeln. Der rechte MOSFET nutzt als Gatelektrode die Metalllage. Wegen des dickeren Gateoxids ergibt sich eine hohe Thresholdspannung. Derartige Transistoren können für Sonderfunktionen zum Beispiel als Schutzstruktur an Eingängen eingesetzt werden. Ausführlicher ist diese Technik im Rahmen des U821D beschrieben.

Bei der unteren Teststruktur kann man unter einem Polysiliziumstreifen zwei sich nicht berührende Bereiche erkennen. Der Farbe nach könnte es sein, dass die kleinen Strukturen rechts und links von dünnem Gateoxid bedeckt sind, während sich in der Mitte das dicke Feldoxid befindet. Damit könnte man vermessen, inwieweit sich ein parasitärer Transistor ausbildet, wenn eine Polysiliziumschicht den Bereich zwischen zwei Gateflächen überdeckt.

An der unteren Kante des Dies befindet sich sogar ein Streifen der Metalllage, der über zwei Testpads vermessen werden kann.

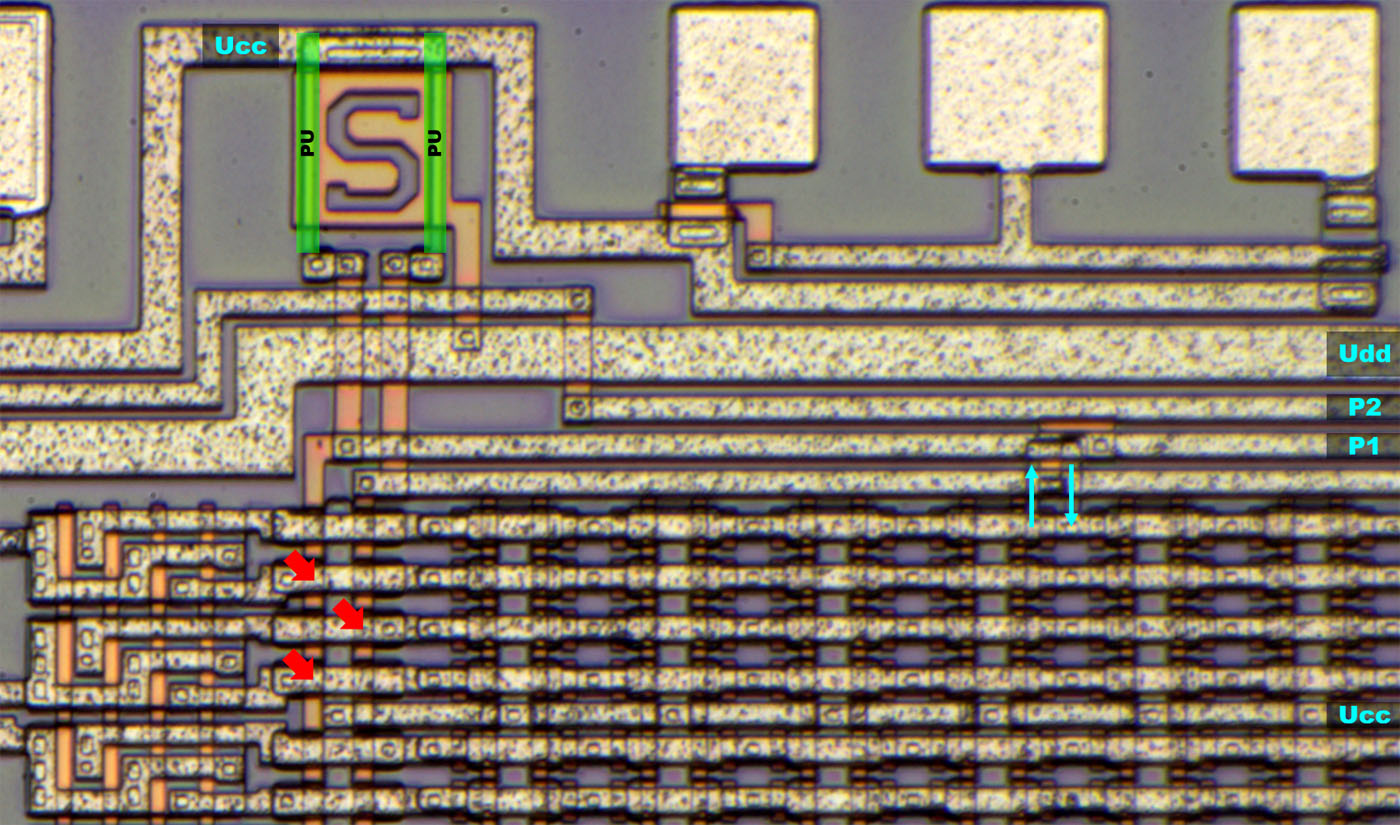

An der oberen Kante des Dies ist ein S abgebildet. Im Gegensatz zu vielen anderen Symbolen und Logos, die man auf integrierten Schaltkreisen findet, ist dieses S in eine aktive Struktur eingebunden. Die umgebende Fläche dient an den Rändern links und rechts als Gateelektrode.

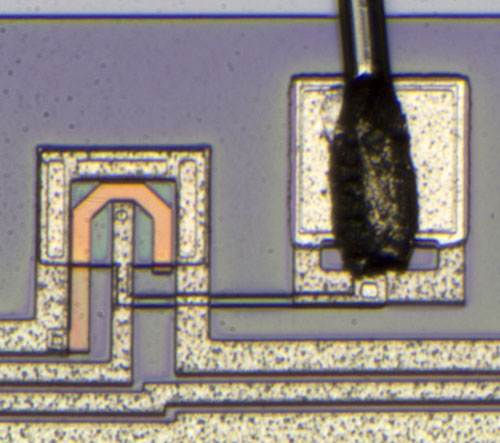

Im Datenblatt steht, dass die Eingänge mit Schutzbeschaltungen ausgestattet sind. Von den Bondpads führt ein Widerstandsstreifen zu einer Fläche, die an das Ucc-Potential angebunden ist. Die beiden Potentiale trennt ein Streifen der Polysiliziumlage, der ebenfalls mit dem Ucc-Potential verbunden ist. Es handelt sich hier um die komplementäre Version des grounded Gate NMOS (ggNMOS). Bei einem ESD-Impuls wird der parasitäre Bipolartransistor unterhalb des MOSFETs leitend und leitet die Energie ab.

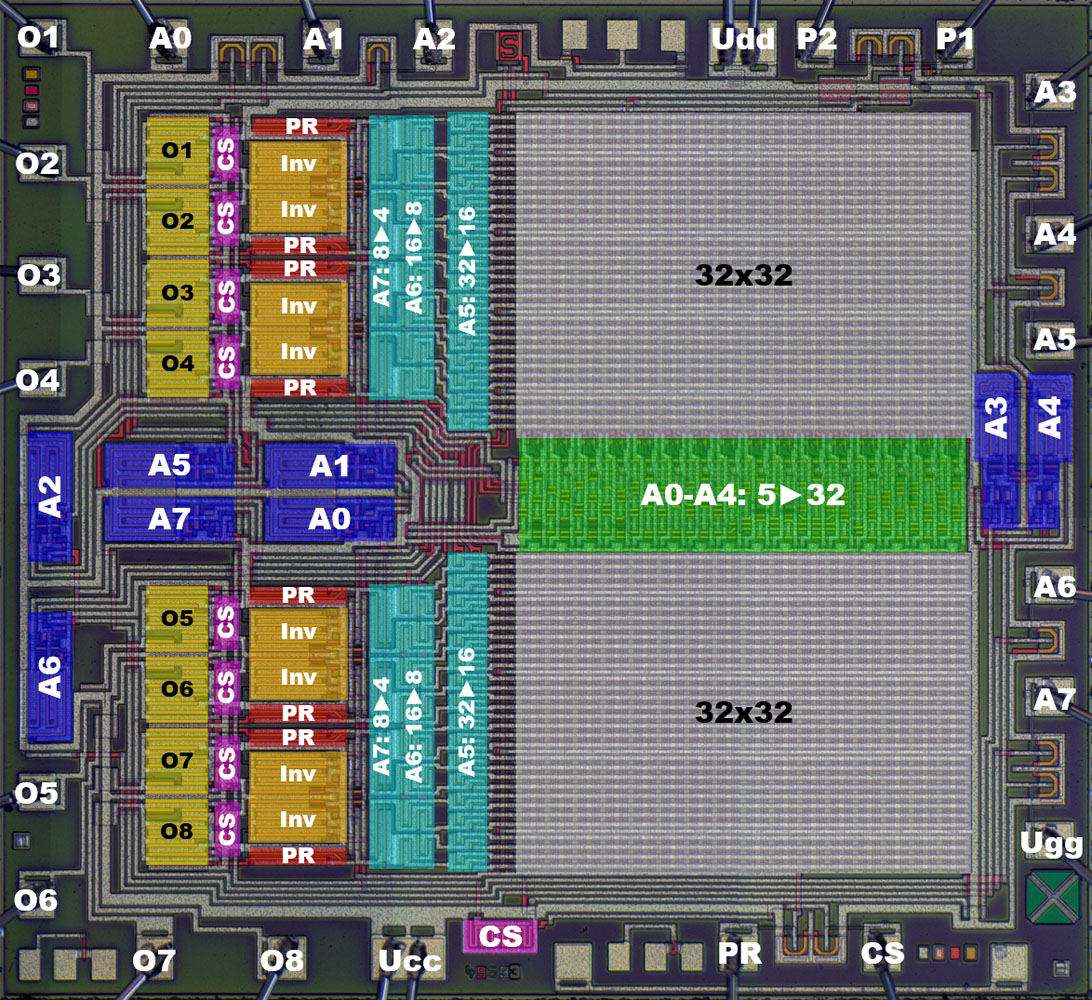

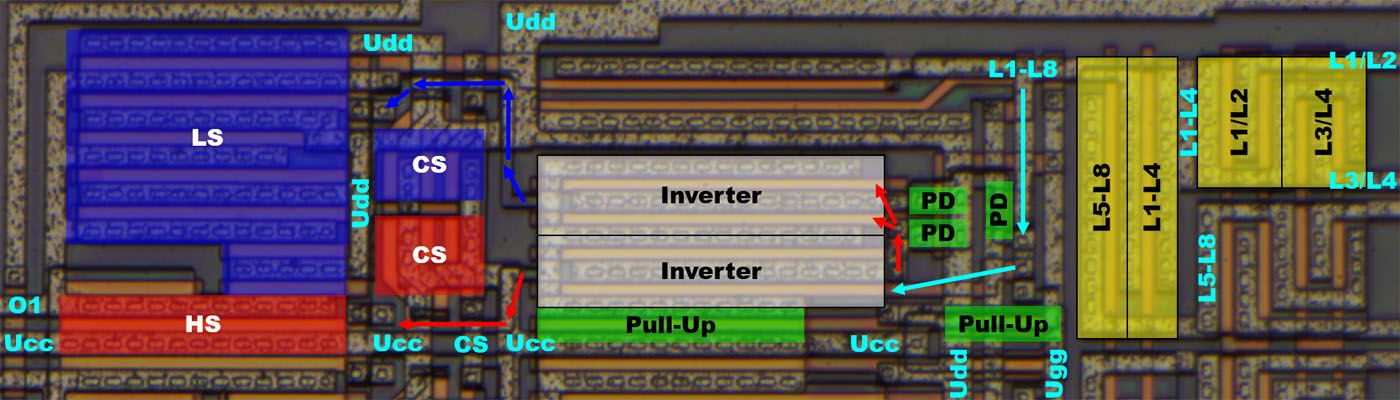

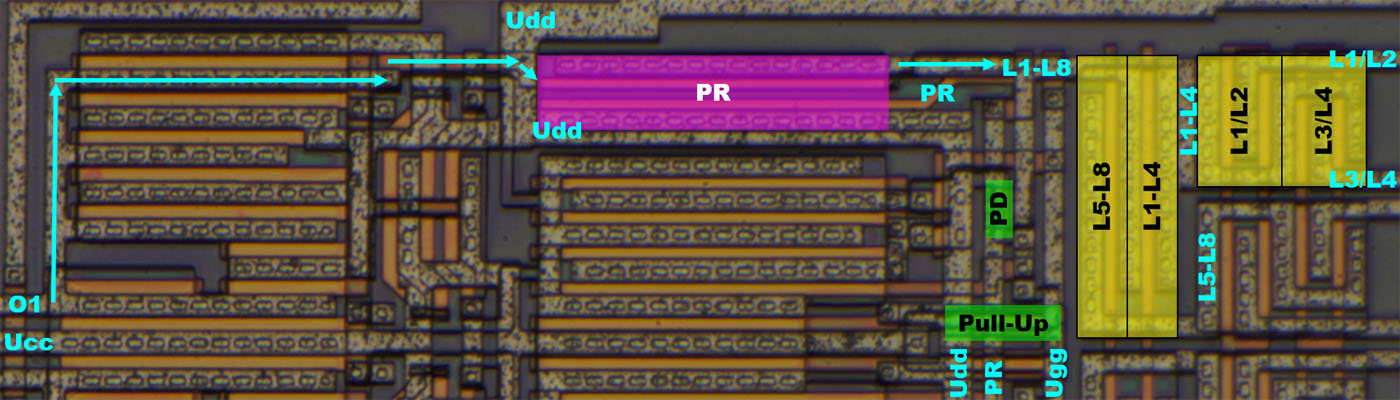

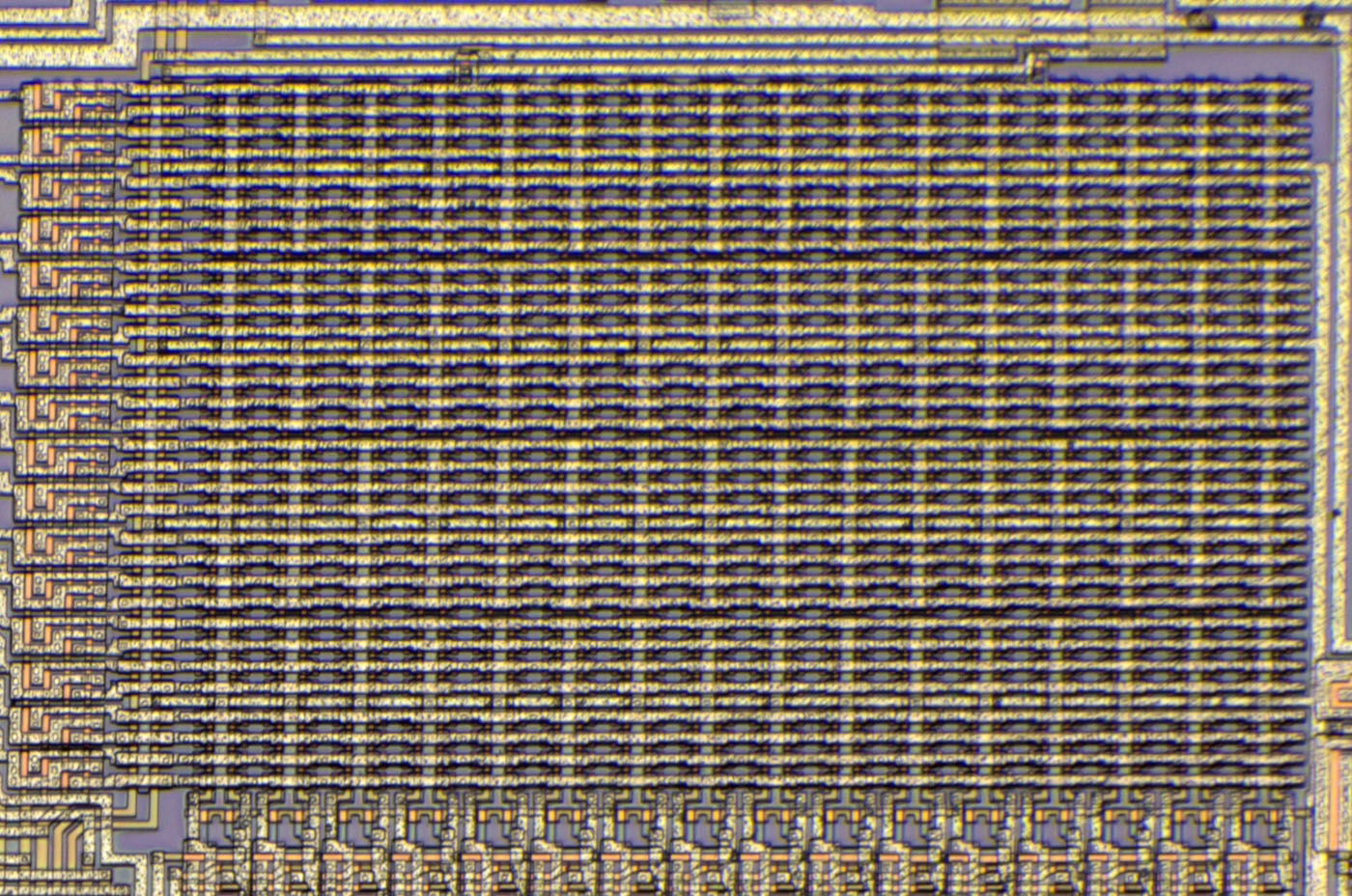

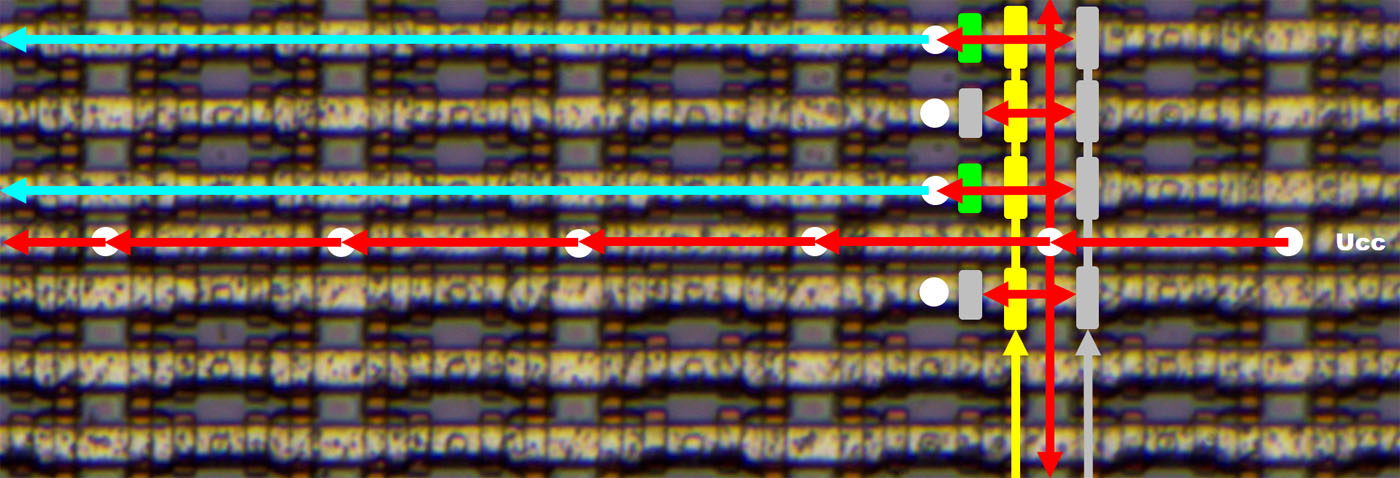

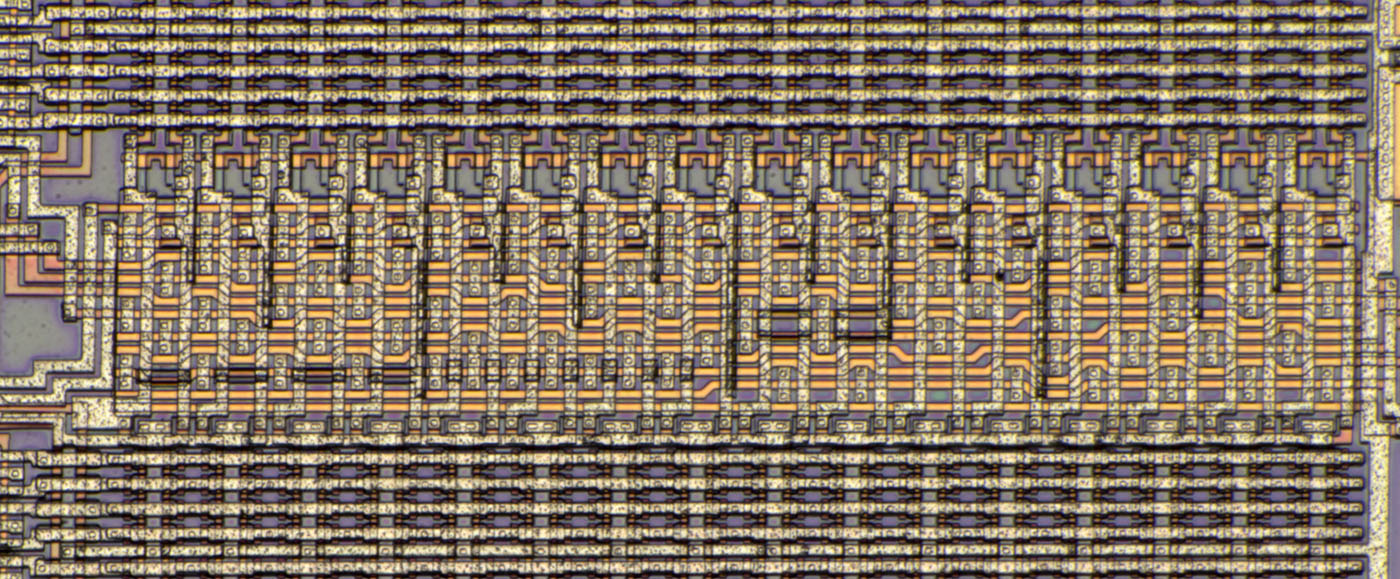

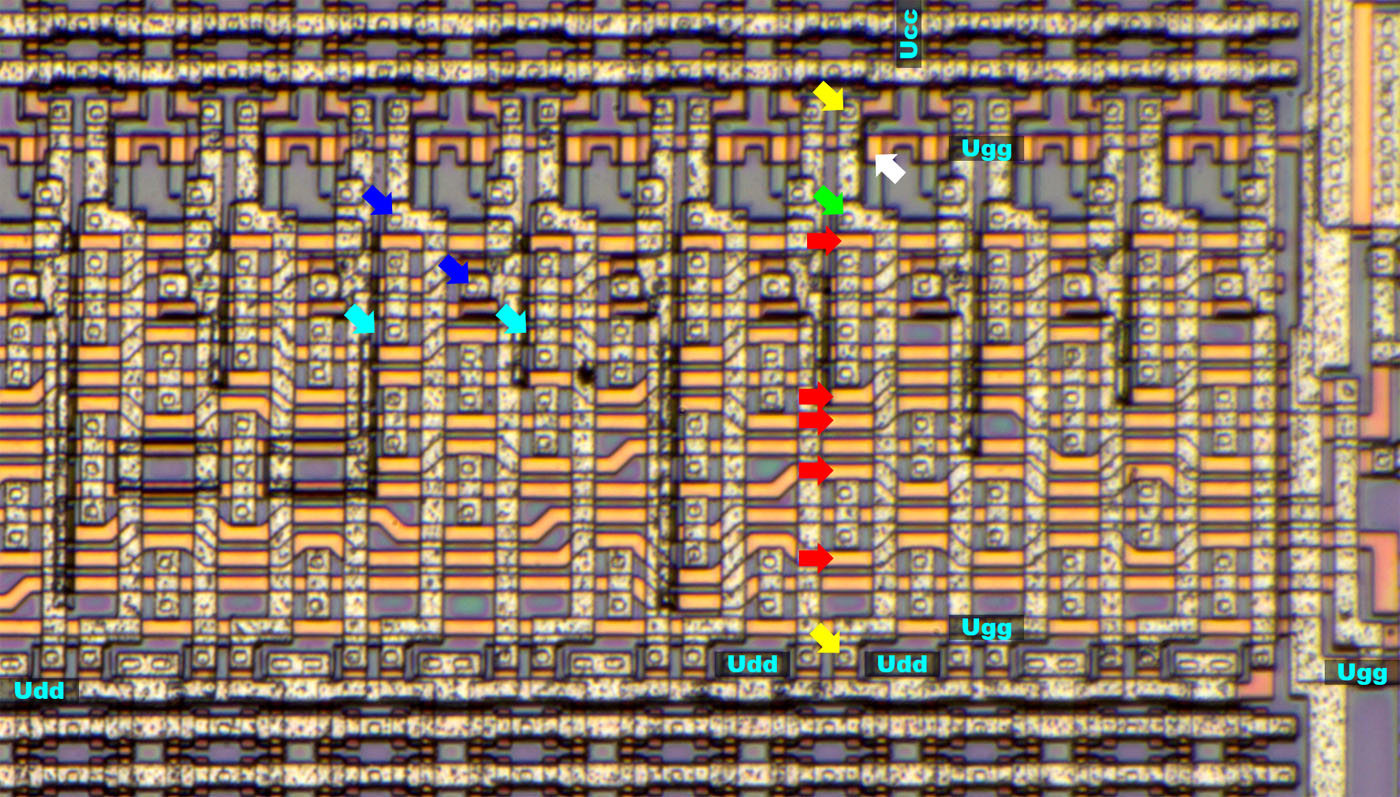

Den größten Bereich auf dem Die nehmen die zwei 32x32 großen Speichermatrizen ein (weiß). Jeder Adresseingang (A0-A6) wird in einer Schaltung vorverarbeitet, die das Steuersignal differentiell ausgibt (blau). Die Adresseingänge A0-A4 werden zwischen den Speicherbereichen verarbeitet (grün) und aktivieren immer eine der 32 Spalten. Der Adresseingang A5 steuert eine erste Umschaltstufe links der Speicherbereiche (türkis). Dort werden die zweimal 32 Zeilen in zweimal 16 Leitungen zusammengeführt. Die Adressleitungen A6 und A7 steuern ähnliche Umschaltstufen (türkis), so dass zuletzt für den oberen und für den unteren Bereich jeweils 4 Ausgangssignale bleiben. Die insgesamt 8 Ausgangssignale durchlaufen eine Inverterstufe (orange), die differentielle Steuersignale ausgeben. An der unteren Kante des Dies befindet sich eine Verstärkerstufe für das Chipselect-Signal, das von dort aus zu acht Abschaltstufen geführt wird (pink). Die acht Endstufen (gelb) enthalten jeweils einen Push-Pull-Treiber für die Ausgänge O1-O6. Beim Beschreiben des EPROMs überbrücken zusätzliche Transistoren neben den Inverterstufen (rot) die Ausgangstreiber.

Links des Speicherbereichs sind die Zeilen des Speichers mit einer vergleichsweise komplexen Schaltung verbunden, die Lese- und Schreibzugriffe auf den Speicher steuert.

Rechts liegen die Potentiale der Zeilen des Speicherbereichs an (L1, L2,...). In drei Stufen werden die Potentiale von acht Zeilen über Doppeltransistoren zusammengefasst. Hier sind die letzten zwei Multiplexstufen abgebildet (gelb). Abhängig vom Status der Adresseingänge wird eine Zeile ausgewählt. Das Potential der ausgewählten Speicherzeile ist an einen Pull-Up- und einen Pull-Down-Widerstand angebunden (grün) und durchläuft dann eine Inverterstufe (weiß), die ein differentielles Steuersignal erzeugt. Die Inverter teilen sich einen Pull-Up-Widerstand. Der untere Inverter steuert den oberen Inverter. Die Ausgangssignale der Inverterstufe steuern einen größeren Lowside- und einen kleinere Highsidetransistor (blau/rot), die den Ausgang O1 bedienen. Zwischen Inverter und Ausgangstreiber sind Transistoren integriert, die über das Chipselect-Signal die Ansteuerung der Push-Pull-Endstufe kurzschließen können.

Das Ugg-Potential dient als Gatepotential für einige der Transistoren, die Widerstände darstellen. Das Datenblatt weist darauf hin, dass man zur Reduktion der Verlustleistung diese Betriebsspannung takten kann.

Im Schreibbetrieb aktiviert das Steuersignal PR einen zusätzlichen Transistor (pink). Das Eingangssignal am Pin O1 wird dann am Ausgangstreiber vorbei zu den Speicherzeilen geführt. Die Adresseingänge definieren, welche der acht zugeordneten Zeilen das Potential erreicht.

An der unteren Kante des Dies befindet sich ein größerer Transistor, der das CS-Potential verstärkt. Der Transistor schaltet gegen Udd. In der rechten oberen Ecke befindet sich, verdeckt von der Metalllage, ein kleiner Transistor als Pull-Up-Widerstand.

Der Speicherbereich ist mit horizontalen Leitungen der Metalllage durchzogen, dabei handelt es sich um die Zeilenleitungen. In regelmäßigen Abständen durchlaufen zusätzlich Ucc-Leitungen den Speicher, so dass sich zwischen einer Speicherzeile und einer Ucc-Leitung maximal drei andere Speicherzeilen befinden. Vertikal bilden Polysiliziumleitungen die Spaltenleitungen. Die Durchkontaktierungen von der Metalllage zum Silizium sind gut zu erkennen.

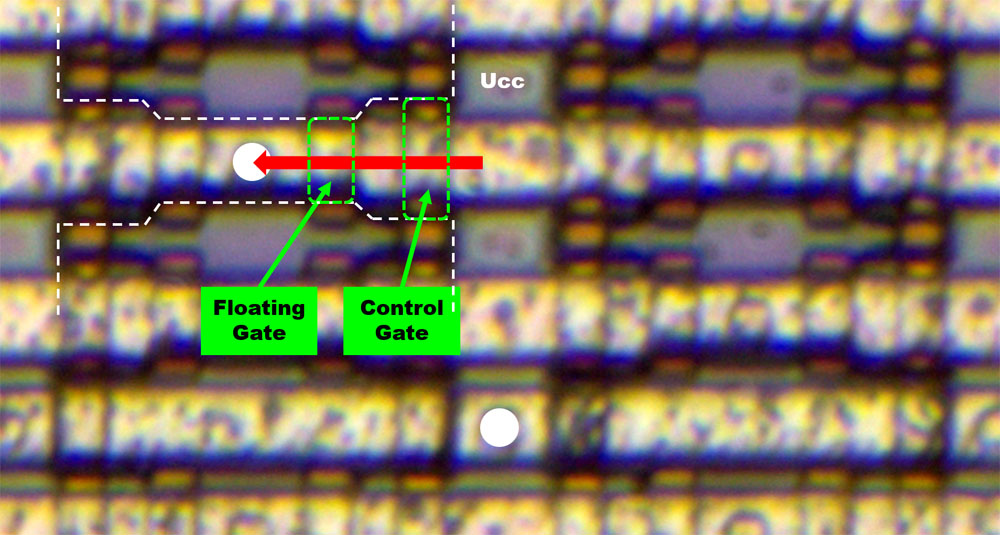

Die Speicherzellen ähneln den Speicherzellen des HML087. Immer zwei Speicherzellen sind über eine Durchkontaktierung mit einer Zeilenleitung verbunden. Der aktive Bereich im Substrat ist wie ein Gitter aufgebaut. Die vertikalen Streifen verteilen das Ucc-Potential. Die horizontalen Streifen durchlaufen die Speicherzellen. Jede Speicherzelle besteht aus einem Control Gate und einem Floating Gate. Das Control Gate aktiviert die Spalte, die ausgelesen werden soll. Der Zustand des Floating Gates bestimmt dann, ob das Ucc-Potential mit der Zeilenleitung verbunden wird oder nicht. Der Pull-Down-Widerstand, der für saubere Low-Pegel sorgt, befindet sich in der Auswerteschaltung links des Speicherbereichs.

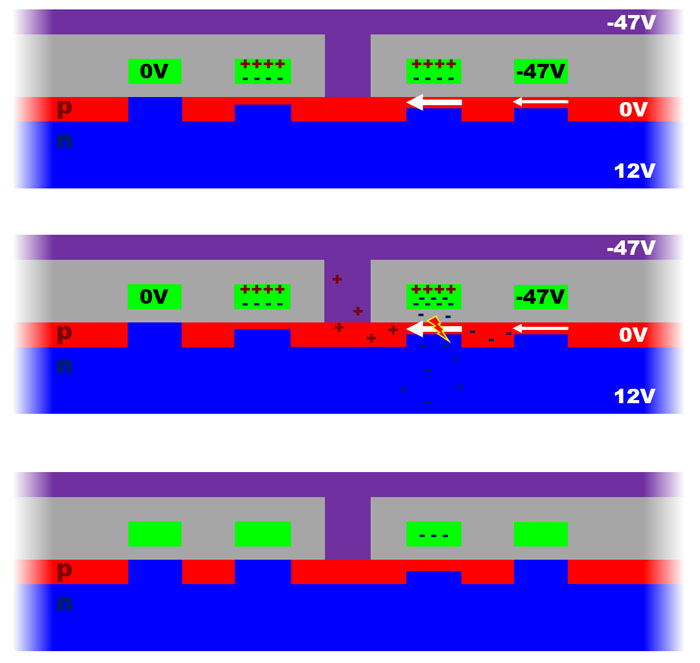

Das Floating Gate ist isoliert von anderen Potentialen. In dieses Gate lassen sich Ladungen einlagern, wenn man an die Speicherzellen verhältnismäßig hohe Spannungen anlegt. Das Datenblatt gibt für einen Programmiervorgang 0V an Ucc vor. Die Zeilenleitungen, die über die Adresseingänge aktiviert werden, führen aus dem Udd-Potential -46V bis -48V zu. An den Spaltenleitungen und damit an den Control Gates liegt ebenfalls Udd an. Bei diesen hohen Spannungen wird die Speicherzelle auch bei entladenem Floating Gate leitend. Durch die hohen elektrischen Felder entstehen im Kanal schnelle Ladungsträger, die sich teilweise in das Floating Gate einlagern. Im Lesebetrieb sind die Spannungen geringer, so dass sich keine weiteren Ladungen einlagern. Befinden sich im Floating Gate Ladungen, dann ist der Bereich darunter leitend und bildet so die gespeicherte Information ab.

Das Ubb-Potential soll beim Programmieren zwischen 10,8V und 13,2V liegen. Die hohe positive Spannung ist notwendig, da verhältnismäßig viele freie Ladungsträger entstehen. Abgesehen von den Ladungen, die im Floating Gate einlagert werden, sollen freie Ladungen möglichst schnell aus dem Substrat abfließen, damit sie keine unerwünschten Reaktionen in den Schaltungen auslösen. Damit liegen beim Programmieren bis zu 61,2V an den Sperrschichten an.

Das Löschen des Bausteins erfolgt mit UV-Licht. UV-Licht erzeugt freie Ladungsträger in allen Strukturen, was dazu führt, dass Elektronen aus dem Floating Gate abfließen können. Das Beschreiben und auch das Löschen des Speichers schädigen das Gateoxid unter dem Floating Gate, was der Grund ist warum ein EPROM nicht beliebig oft beschrieben werden kann. Durch die steigenden Leckströme können dann im Floating Gate keine Ladungen mehr gehalten werden.

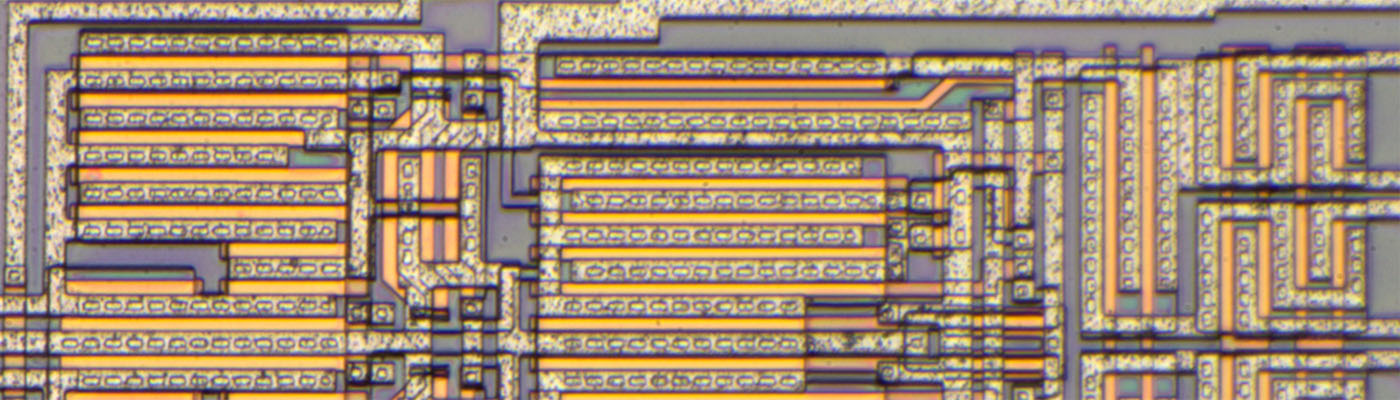

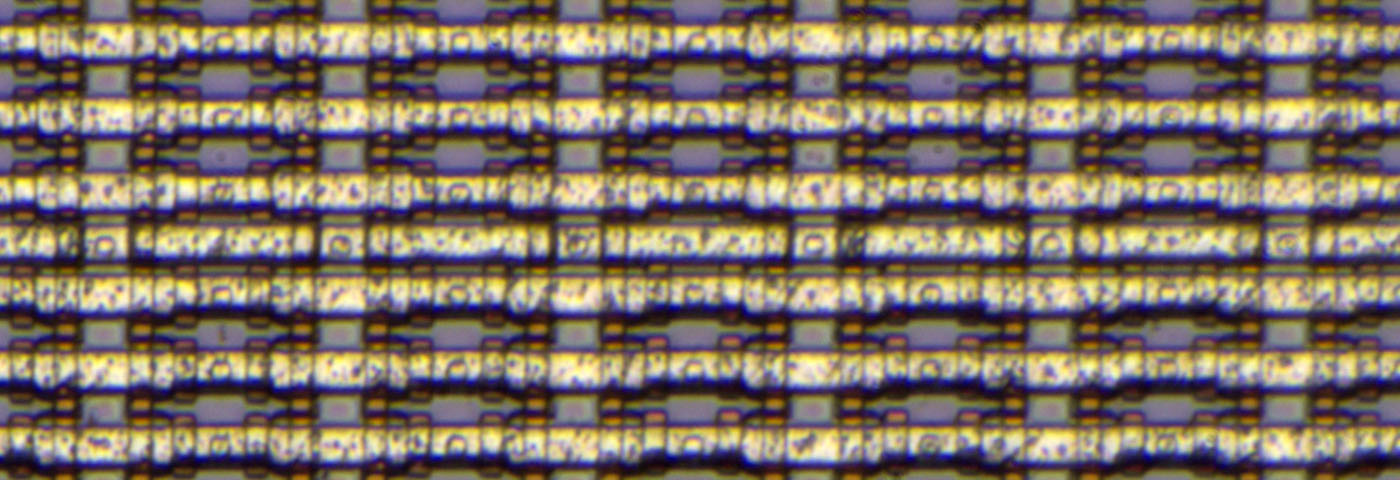

Entfernt man die schützende Passivierungsschicht und die Metalllage, so wird der Aufbau der Speicherzellen noch etwas klarer. Die Bereiche unter der Metalllage bleiben undurchsichtig und müssen mit der darunter liegenden Siliziumoxidschicht aufgelöst werden. Dabei entfernt man allerdings auch nach und nach die Polysiliziumstreifen.

Wie bereits dargestellt, verengt sich die aktive Schicht unter den Speicherzellenpaaren zu dem mittigen Kontakt hin, der sie mit der Zeilenleitung verbindet. Im schmäleren Bereich befindet sich das isolierte Floating-Gate. Zur Ucc-Verteilung hin aktiviert das durchgezogene Control-Gate alle zur Spalte gehörenden Speicherzellen. In diesen Bildern ist nun auch zu erkennen, dass sich die Ucc-Verteilung in der aktiven Schicht nicht durch den kompletten Speicherblock zieht, sondern nach acht Zeilen unterbrochen wird.

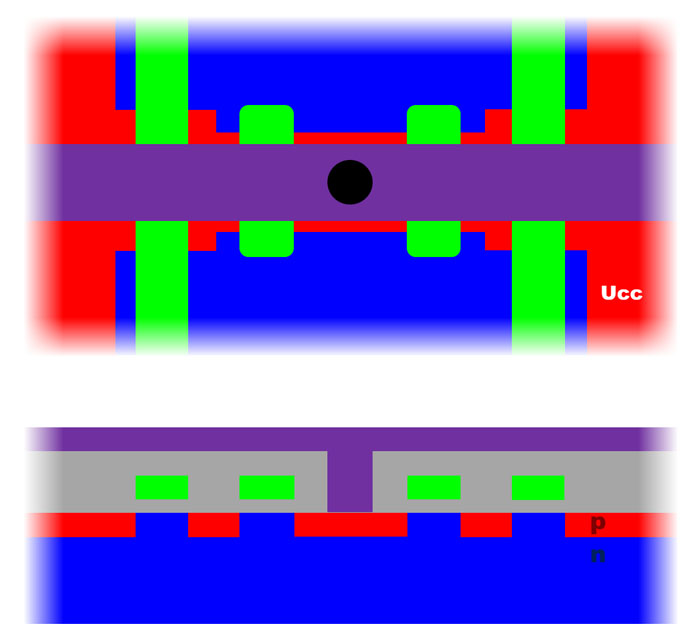

Der Aufbau eines Speicherzellenpaars stellt sich folgendermaßen dar. Die aktiven Bereiche sind p-dotiert (rot). Lediglich unter den Polysilizium-Gateelektroden (grün) befindet sich weiterhin die n-Dotierung des Substrats (blau). In der Mitte kontaktiert die Metalllage das Speicherzellenpaar (lila/schwarz).

Beim Programmieren einer Speicherzelle liegen an der zugehörigen Zeilen- und Spaltenleitung -47V an. Das Control-Gate erzeugt damit einen leitfähigen Kanal. Das Potential der Zeilenleitung sorgt im Floating-Gate für eine Ladungsverschiebung. Die hohe Spannung reicht aus, um auch unter dem Floating-Gate einen leitfähigen Kanal zu erzeugen und es fließt ein Strom. Links ist das Potential des Control-Gates auf 0V fixiert, so dass sich darunter kein leitfähiger Kanal ausbilden kann.

Da sich der aktive Bereich vor dem Floating-Gate verengt, steigt dort die Stromdichte an. Die hohe Stromdichte erzeugt sehr viele freie Ladungsträger. Ein Teil der Ladungsträger fließt über den aktiven Bereich ab. Die negativen Ladungsträger sind mobiler als die positiven. Ein Teil verteilt sich im Substrat und muss darüber abgeleitet werden. Ein gewisser Teil durchdringt aber auch das dünne Gateoxid des Floating-Gates und lagert sich dort ein.

Die im Floating-Gate eingelagerten negativen Ladungen sorgen von nun an dafür, dass unter dem Floating-Gate ein leitfähiger Kanal verbleibt. Wird die zugehörige Spalte aktiviert, so ist die Zeilenleitung mit dem Ucc-Potential verbunden.

Hier ist noch einmal dargestellt, wie das Auslesen des Speichers erfolgt. In der gewünschten Spalte sind die Control Gates aktiv (gelb), während die anderen Control Gates inaktiv sind (grau). Das Ucc-Potential steht so an den Floating Gates der aktiven Spalte an. Die Floating Gates mit gespeicherten Ladungen (grün) verbinden das Ucc-Potential über eine Durchkontaktierung mit der zugehörigen Zeile (türkis). Die inaktiven Floating Gates sperren (grau) und die zugehörigen Zeilen verbleiben auf ihrem initialen Low-Pegel.

Zwischen den Speicherblöcken befindet sich die Zeilenauswahl. Von links und von rechts werden dem Bereich differentielle Steuersignale zugeführt, die auf den Potentialen der Adressleitungen A0-A4 basieren.

Die sich gegenüberliegenden Spaltenleitungen des oberen und des unteren Speicherbereichs sind über eine Leitung der Metalllage miteinander verbunden (gelb). Unter dem oberen Speicherbereich befinden sich Transistoren, die als Pull-Up-Widerstände dienen (weiß) und die Spaltenleitungen initial mit einem positiven Potential belegen (grün).

Wo der Pull-Up-Widerstand die Leitung kontaktiert, beginnt ein aktiver Bereich, der sich nach unten über die quer verlaufenden Polysiliziumleitungen erstreckt. Die Polysiliziumleitungen stellen Transistoren dar, die abhängig von ihrer Ansteuerung das Potential der Spalte nach unten durchverbinden können (rot). Einige der Transistoren werden von der Metalllage überbrückt. Teilweise befindet sich die Überbrückung nicht direkt in einer vertikalen Linie unter der zugehörigen Spalte. Das untere Ende der Spaltenauswahl ist an das Udd-Potential angebunden. Sind die richtigen Transistoren aktiv, so nimmt die zugehörige Spalte einen Low-Pegel an und die darin befindlichen Speicherzellen werden aktiv.

Die Spaltenauswahl ist so aufgebaut, dass immer nur eine Spalte aktiv wird. Um die Spalten voneinander zu isolieren, ist die aktive Fläche an einigen Stellen mit Schlitzen unterbrochen (türkis). Dazu kommt eine spezielle Verschaltung der obersten drei Polysiliziumstreifen. Die Streifen 2 und 3 führen das inverse Potential des ersten Streifens. Die Spalten des Speichers kontaktieren abwechselnd aktive Flächen, die sich oberhalb des ersten Streifens befinden und Flächen, die zwischen den Streifen 2 und 3 eingeschlossen sind (blau). Durch diese Maßnahme ist immer nur eine der direkt nebeneinander liegenden Spalten mit den restlichen Transistoren verbunden.

Auch hier wird das Ugg-Potential genutzt, das zur Reduktion der Verlustleistung getaktet werden kann.

Jeder Adresseingang ist an eine kleine Schaltung angebunden. Hier trifft das Eingangssignal von oben ein. Auf den ersten Transistor T1 folgt ein Doppeltransistor, der differentielle Steuersignale erzeugt. Die Ausgänge sind mit länglichen Transistoren verbunden, die konstante Pull-Down-Widerstände darstellen. Im unteren Bereich folgen weitere Pull-Down-Transistoren, die allerdings über Ugg beeinflusst werden können. Außerdem scheinen in diesem Bereich zwei Kapazitäten integriert worden zu sein.

Die Prüfeingänge P1 und P2 bieten mehrere Funktionen. Sie steuern zwei Transistorreihen am linken Ende der Speicherbereiche (rote Pfeile). Jeder Transistor schaltet eine Speicherzeile auf das Ucc-Potential. Die Speicherzeilen sind abwechselnd mit einer der beiden Transistorreihen verbunden. Das Muster der Kontaktierungen ist allerdings nicht durchgehend gleich. Die oberste Zeile wird unbeeinflusst zu den Ausgangstreibern geführt.

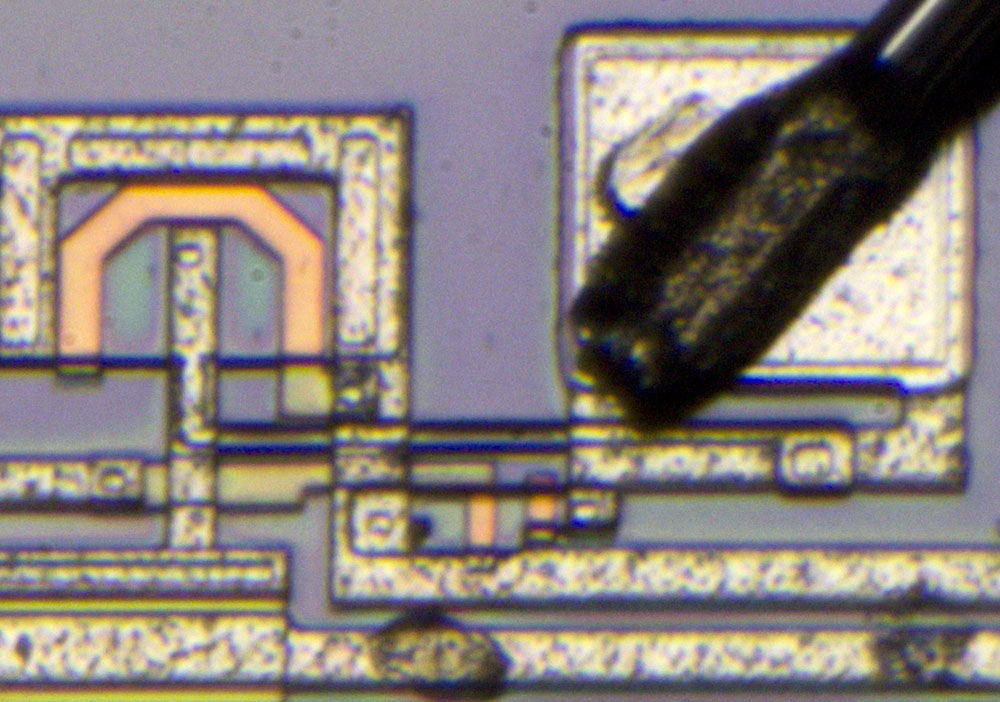

Der Prüfeingang greift zusätzlich an zwei Stellen in die oberste Speicherzeile ein und ermöglicht es dort jeweils eines der Floating Gates zu überbrücken.

Man kann nur vermuten was mit den Prüfeingängen getestet wurde. Die Überbrückung der zwei Floating Gates ermöglicht es auch ohne eine Programmierung des Chips einen rudimentären Funktionstest durchzuführen. Während alle Speicherzellen inaktiv sind, kann man in der ersten Zeile an zwei Stellen eine aktive Speicherzelle simulieren. Das Deaktivieren aller Speicherzellen mit Ausnahme der obersten könnte bei der Vermessung von bestimmten Eigenschaften vorteilhaft sein. Für was man die Hälfte der Zeilen deaktivieren wollte bleibt offen. Die Verteilung der Zeilen auf die beiden Prüfeingänge lässt kein nützliches Muster erkennen. Man kann zum Beispiel bei einem fehlerhaften Baustein keine Teilbereiche deaktivieren, da die restlichen Bereiche verhältnismäßig chaotisch im Adressraum verteilt wären.

Direkt am Bondpad des Prüfeingangs P1 ist eine Struktur angebunden, die einer Speicherzelle entspricht. Links ist die Struktur an das Ucc-Potential angebunden. Der Prüfeingang P2 steuert das Control Gate. Nach rechts ist schön zu erkennen, dass sich der aktive Bereich vor dem Floating Gate verjüngt.