Der U821 stammt aus dem Kombinat Mikroelektronik Erfurt, genauer aus dem Funkwerk Erfurt, später Mikroelektronik Karl Marx. Es handelt sich um einen Taschenrechner-Controller, der dem TMS0105 nachempfunden ist und unter anderem im Taschenrechner Konkret 100 eingesetzt wurde. Die Buchstaben RD kennzeichnen die Produktion im vierten Quartal 1983. Dazu passt das Kürzel MME, das für Mikroelektronik Karl Marx steht. Vor 1983 war auf dem U821 das Kürzel FWE für Funkwerk Erfurt aufgedruckt.

Der U821 entspricht grundsätzlich dem Vorgänger U820, wurde aber für den Batteriebetrieb optimiert. Die Stromaufnahme konnte nicht unerheblich reduziert werden: Über Ugg fließen beim U821D nur noch 9mA (gegenüber 15mA), über Uss fließen nur noch 20mA (gegenüber 35mA). Die Taktrate wurde von 200kHz-330kHz auf 100kHz-270kHz reduziert. Die Darstellung der Zahlen auf den 7-Segment-Anzeigen wurde optimiert, so dass im Mittel weniger Elemente aktiv sind, was zusätzlich Strom spart. Gleichzeitig konnte der Maximalstrom der 7-Segment-Treiber von 1mA auf 5mA erhöht werden. Ein Vergleich zwischen dem U820 und dem U820 findet sich am Ende dieser Seite.

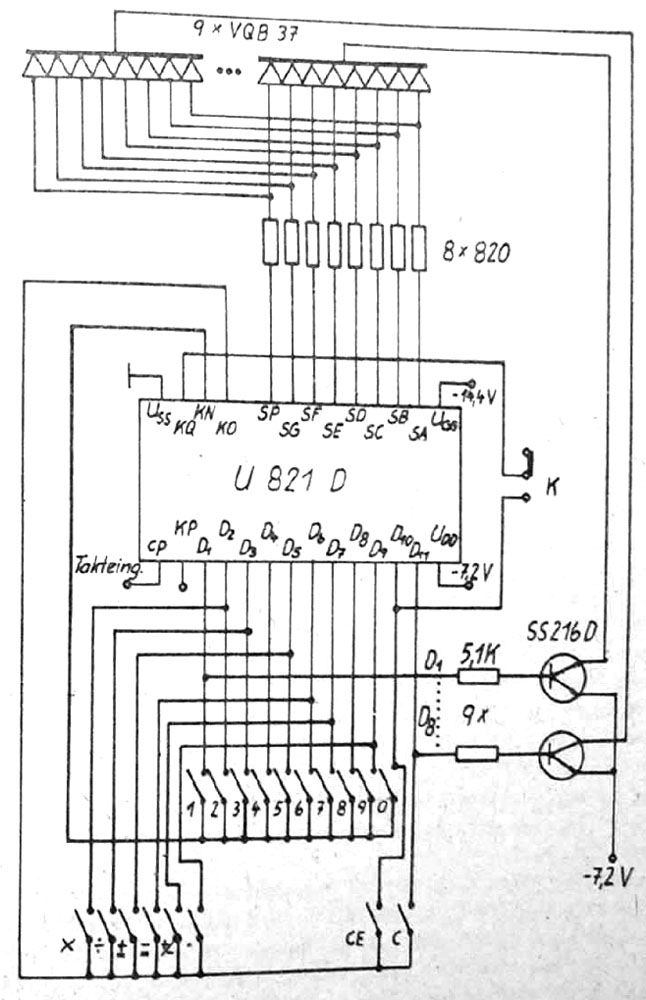

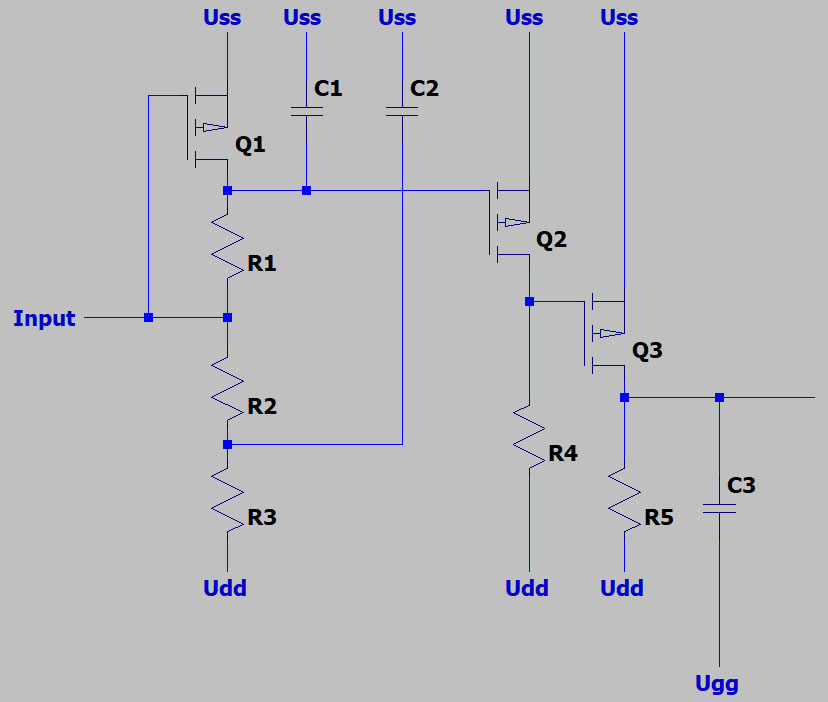

Die Broschüre "Halbleiter-Anfallbauelemente - Daten und Anwendungsbeispiele" des Funkwerk Erfurt enthält einen Schaltungsvorschlag, der die Funktionsweise des Controllers und die notwendige Beschaltung aufzeigt. Da es sich um einen PMOS-Schaltkreis handelt, benötigt er eine negative Versorgungsspannung mit -14,4V. Die zweite Versorgungspannung mit -7,2V lässt vermuten, dass im U821 nur Enhancement-MOS-Transistoren zum Einsatz kamen. Man kann Logikgatter mit Pull-Up-Widerständen aufbauen. Derartige Gatter bringen allerdings eine hohe Verlustleistung mit sich. Alternativ kann man auf als Stromquellen verschaltete Depletion-MOSFETs zurückgreifen. Depletion-MOSFETs benötigen in der Herstellung allerdings einen zusätzlichen Implantationsprozess. Eine Alternative ist die Nutzung der vorhandenen Enhancement-MOSFETs, die dann allerdings für eine ordnungsgemäße Funktion eine Hilfsspannung benötigen, in diesem Fall -7,2V.

Nicht im Schaltplan dargestellt ist der Oszillator, der dem U821 den Systemtakt liefert.

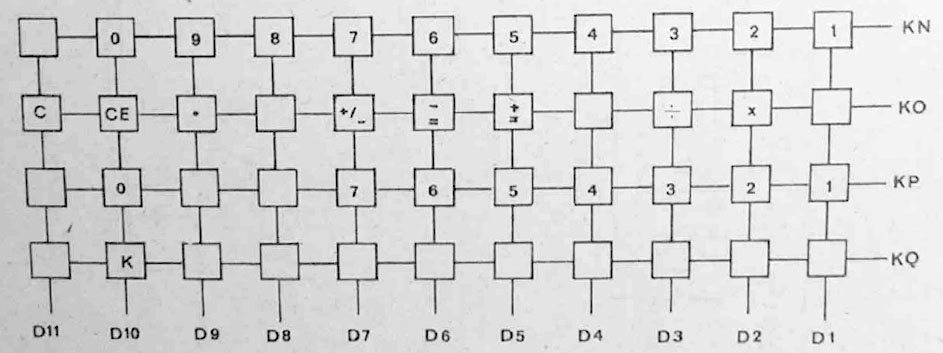

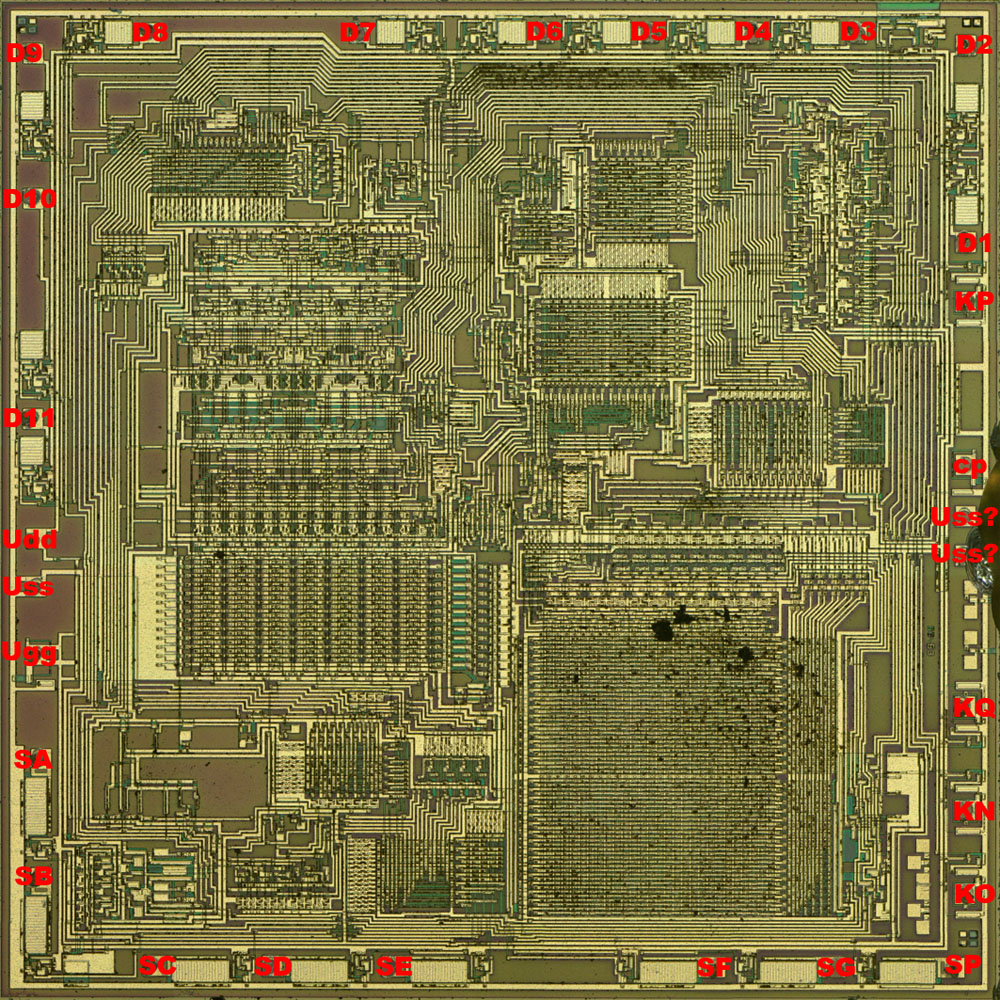

Die Ausgänge SA bis SP steuern neun 7-Segment-Anzeige an (jeweils sieben Segmente und ein Punkt). Über die Ausgänge D1-D8 und D11 wird das Multiplexing der 7-Segment-Anzeigen realisiert. Neun Transistoren sorgen für die notwendige Stromtragfähigkeit. Die Ausgänge D1-D11 dienen zusätzlich dazu die Tastaturmatrix auszulesen.

Durch das abwechselnde Aktivieren der Ausgänge D1 bis D11 kann an den

Eingängen KN bis KQ bestimmt werden, welche Taste gerade gedrückt ist.

Die Zeilen KN und KO bilden die Zahlen und die Operatoren ab. Über KP kann

der Festkommabetrieb konfiguriert werden. KQ dient lediglich

dazu die Rechnung mit Konstanten zu aktivieren.

(Bildquelle:

"Halbleiter-Anfallbauelemente - Daten und Anwendungsbeispiele")

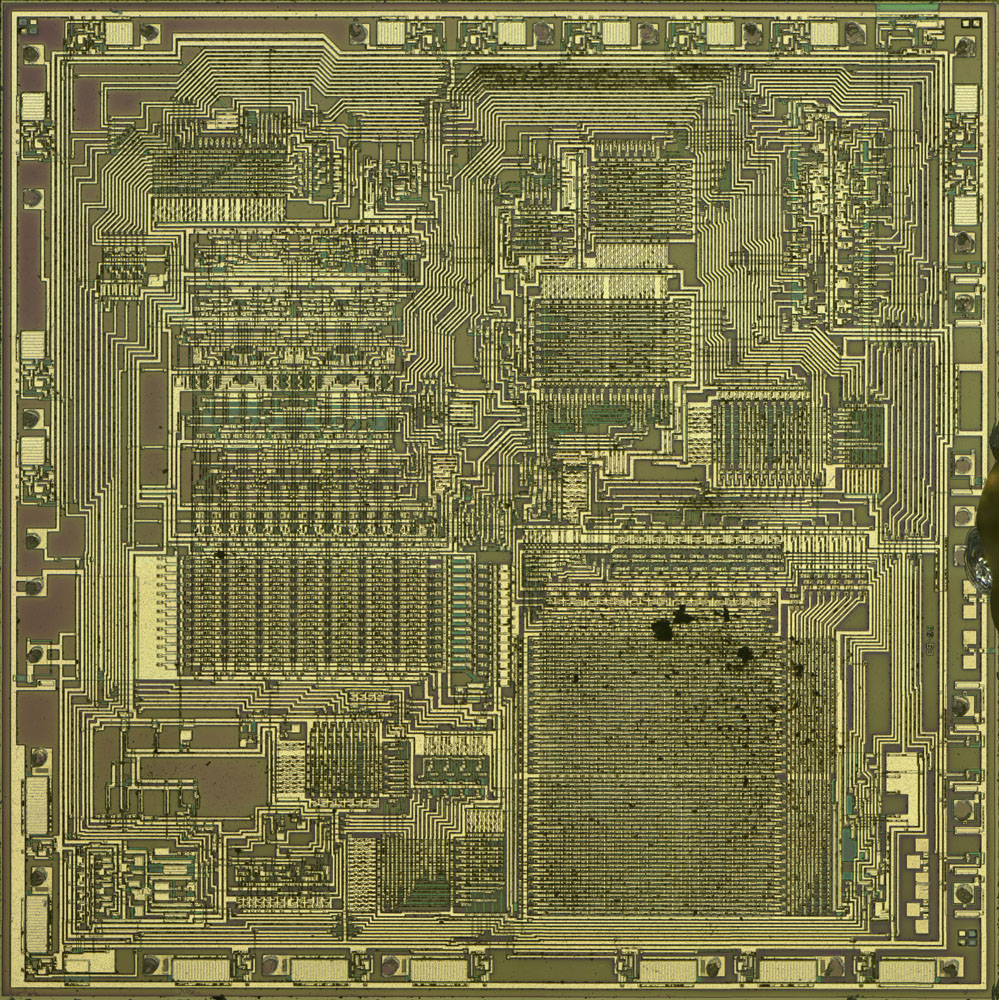

Das Die ist mit einer Fläche von 5,8mm x 5,8mm relativ groß. Am Ende dieser Seite befindet sich ein Bild mit höherer Auflösung.

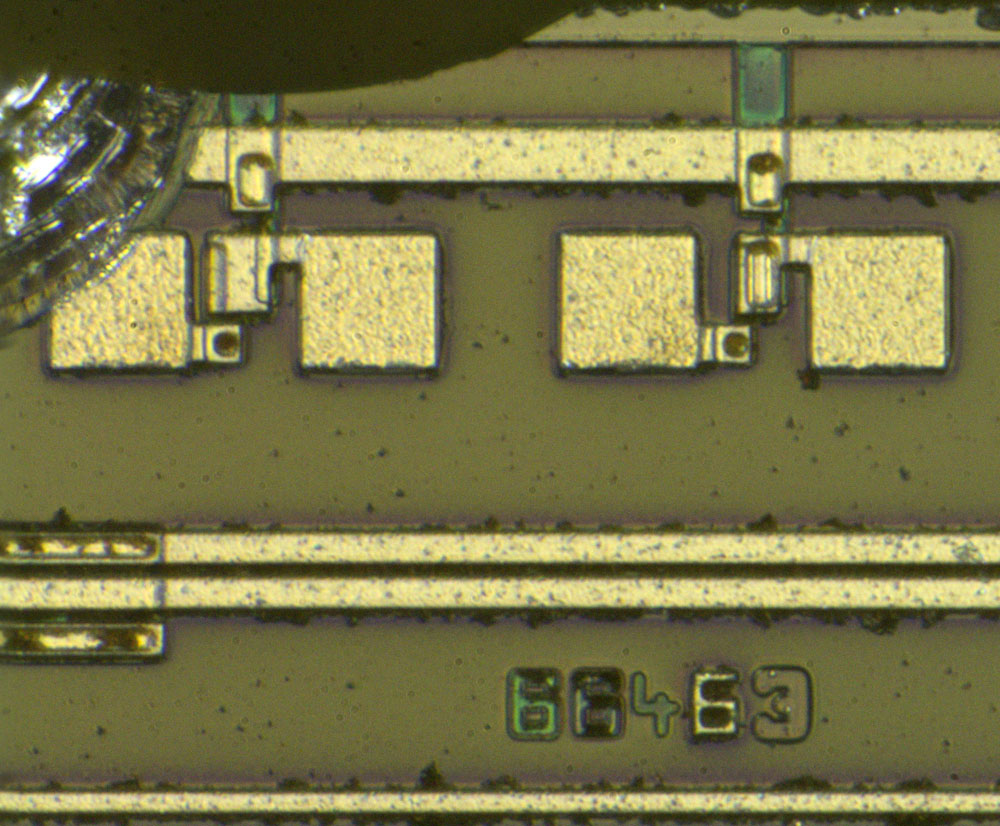

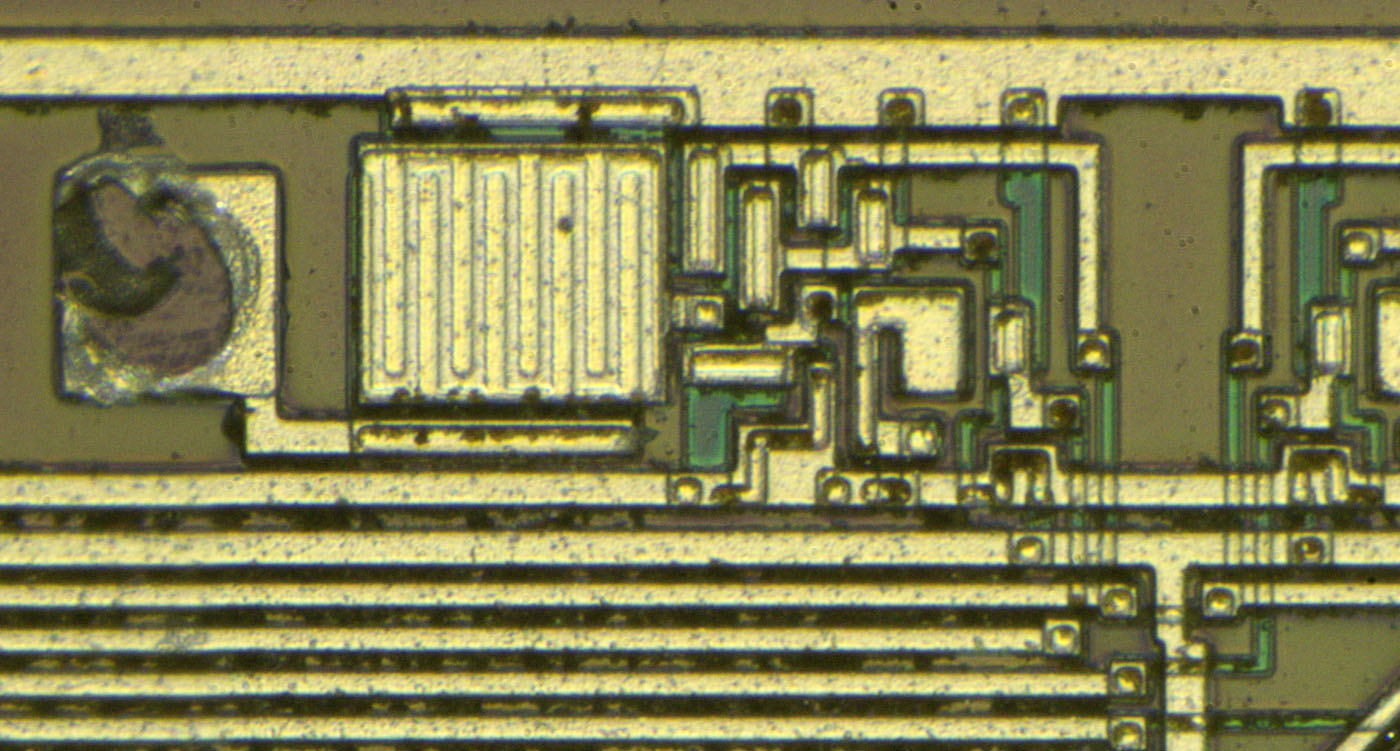

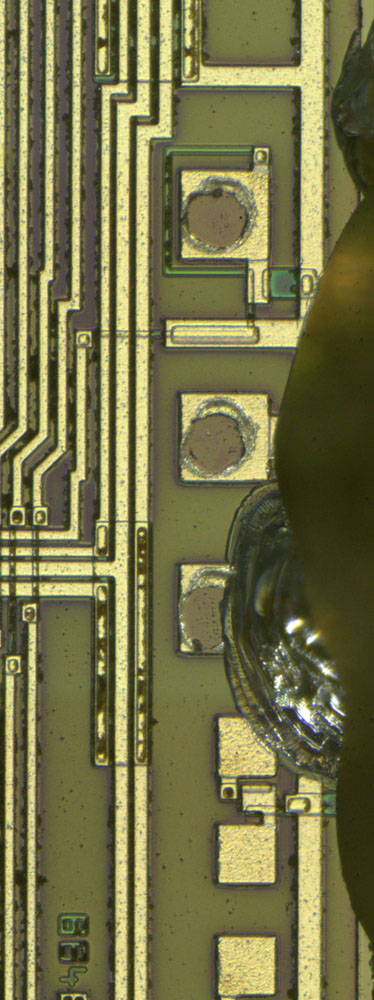

In der unteren rechten Ecke hat man zwei Teststrukturen integriert. Jede Struktur besteht aus zwei grünlichen Rechtecken, die mit einem gewissen Abstand in das Substrat integriert wurden. Die Lücke zwischen den Rechtecken überdeckt ein Metallstreifen, wodurch sich ein MOSFET ausbildet. Damit ein PMOS-Transistor entsteht, muss das Substrat n-dotiert sein und die grünen Rechtecke müssen eine p-Dotierung enthalten.

Beim linken MOSFET befindet sich unter der Gate-Elektrode ein Rechteck, das die beiden grünen Elemente überlappt. Man könnte spekulieren, dass dort eine zusätzliche Dotierung eingebracht wurde, um einen selbstleitenden MOSFET aufzubauen. Das ist aber nicht der Fall. Das Rechteck entstand dadurch, dass unterhalb des Gates die Siliziumoxidschicht dünner ausgeführt wurde. Das dünne, sogenannte Gateoxid führt zu sinnvollen Schaltschwellen. Das dickere Feldoxid des rechten MOSFETs benötigt demgegenüber sehr viel höhere Spannungen, um zu schalten. Das ist nützlich, da so bei einfachen Kreuzungen zwischen Metalllagen und p-dotierten Leitungen keine parasitäreren Transistoren entstehen.

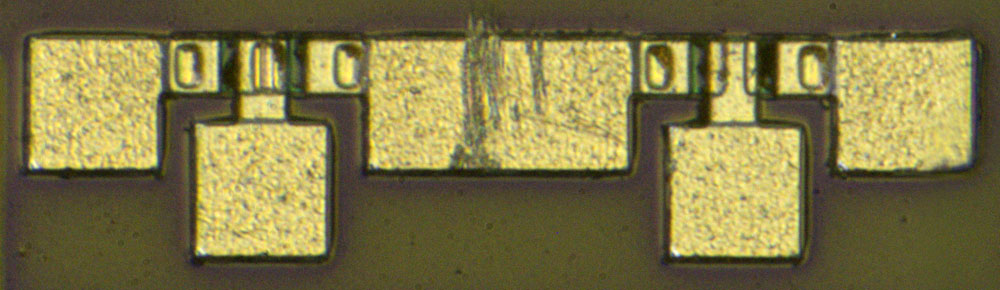

Etwas weiter oberhalb sind noch einmal zwei Teststrukturen mit den gleichen Transistortypen abgebildet. Bei diesen Transistoren ist die Source-Elektrode an das Vss-Potential angebunden.

Unter den Transistoren sind anscheinend die Revisionen von fünf Masken

abgebildet. Demnach gab es bis zu fünf Überarbeitungen innerhalb des

Maskensatzes. Über den genauen Ablauf der Fertigung kann man nur spekulieren.

Die erste Maske bildet der Farbe nach die p-Dotierung ab, die mit

dem n-dotierten Substrat die Grundstruktur der MOSFETs ausbildet, als kurze Verbindungsleitung und

als Widerstand dienen kann. Danach muss eine dicke Oxidschicht aufgetragen

werden, um später darüber Leitungen der Metalllage verlegen zu können. Die

zweite und die dritte Maske dürften dann festlegen wo Durchkontaktierungen von der Metalllage zum Silizium

entstehen und wo sich das dünne Gateoxid ausbilden soll. Es folgt die recht

eindeutig erkennbare Maske der Metalllage. Die letzte Maske wird wahrscheinlich

dazu dienen die Passivierungsschicht über den Bondpads zu entfernen, so dass der

Bondprozess sauber erfolgen kann.

Die Potentiale der Bondpads lassen sich relativ gut zuordnen.

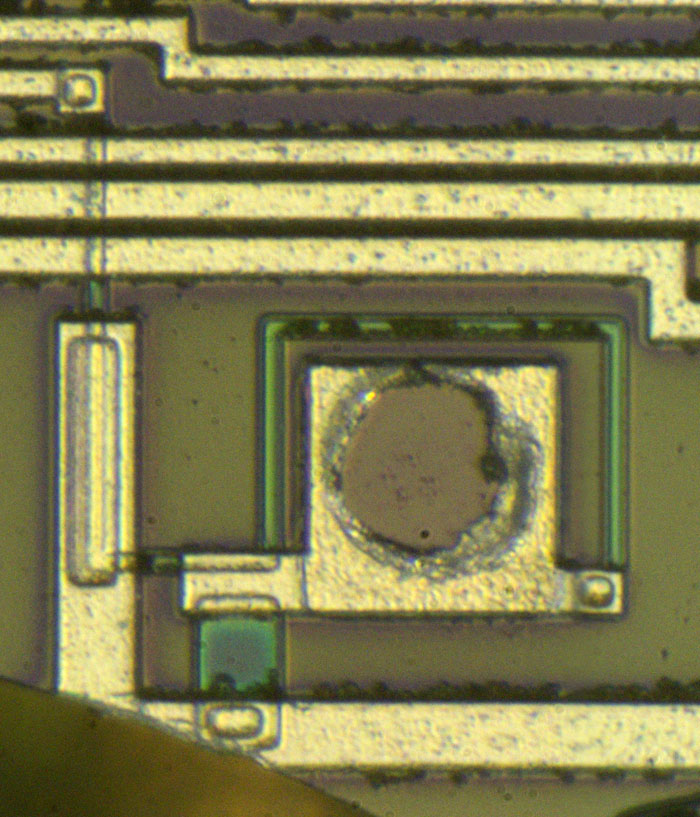

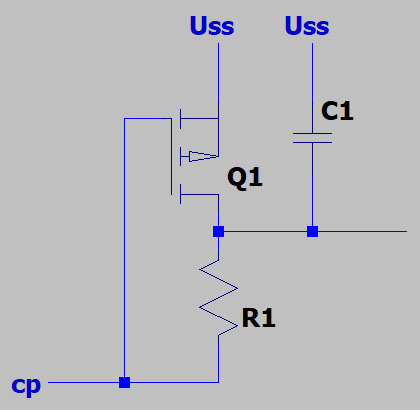

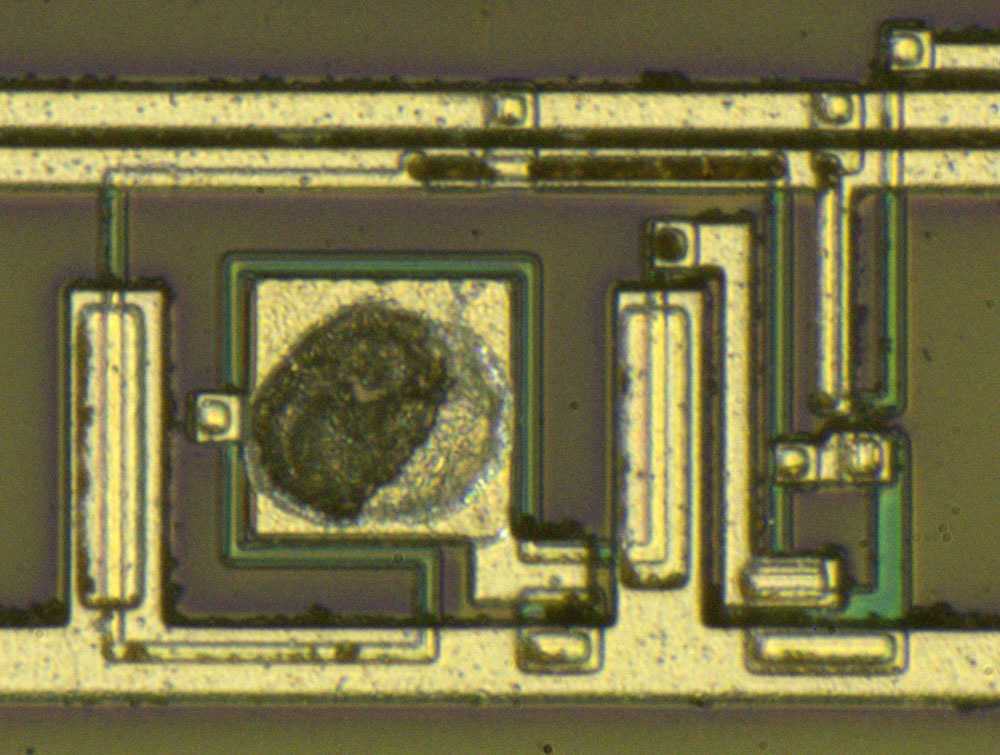

Hier ist der Eingang des Systemtakts zu sehen. Die Bondpads, die Eingänge darstellen, besitzen Schutzstrukturen. Es handelt sich um einen Widerstand in Form einer p-dotierten Schleife, einem mit dem Feldoxid aufgebauten MOSFET und einem kleinen Kondensator. Der Kondensator besteht aus einem Stück des p-dotieren Materials und der Metalllage. Dazwischen befindet sich das dünne Gateoxid, was für eine verhältnismäßig hohe spezifische Kapazität sorgt.

Der Transistor der Schutzstruktur sperrt sowohl bei einem High-, als auch bei einem Low-Pegel, da er mit dem dicken Feldoxid aufgebaut ist. Kommt es allerdings zu einem problematischen, negativen Überschwinger, so wird der Transistor leitend und hebt das Potential an. Der Widerstand R1 entkoppelt die folgenden Schaltungsteile ein Stück weit vom Potential am Bondpad. In Kombination mit dem Kondensator C1 entsteht außerdem ein RC-Glied, das Störungen filtert.

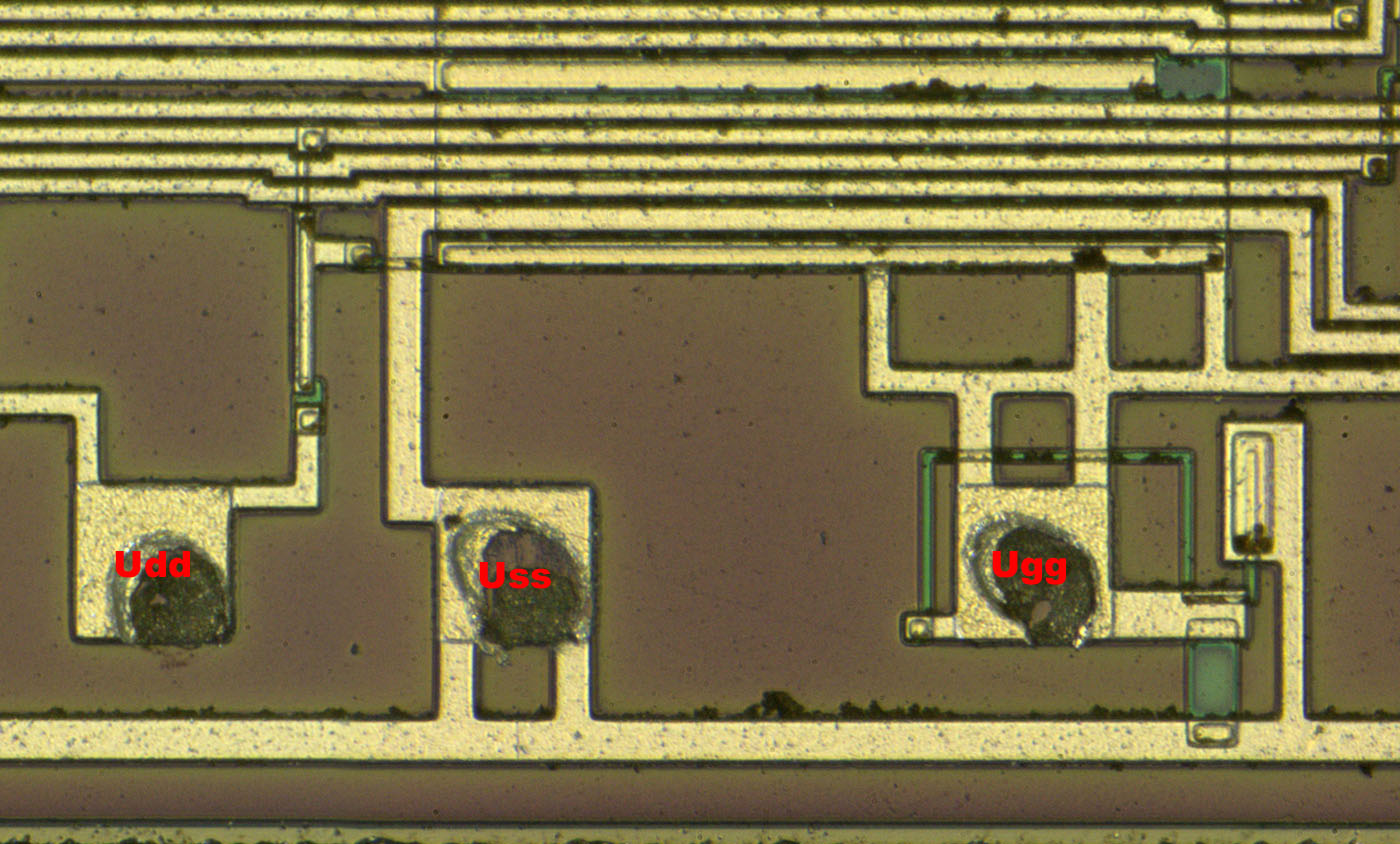

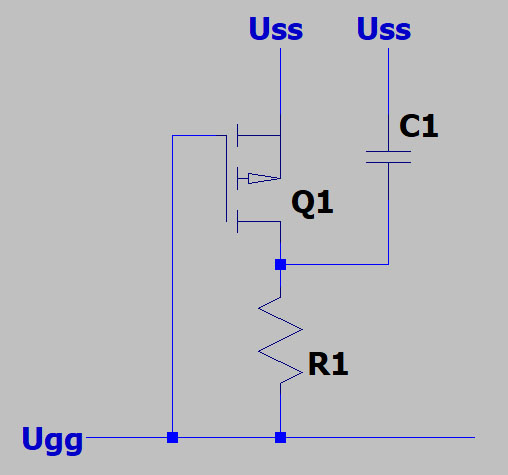

Uss ist das positivste Potential auf dem Die. Es wird unter anderem über eine Rahmenstruktur verteilt. Das Udd-Potential bewegt sich zwischen Uss und Ugg, so dass problematische Überschwinger unwahrscheinlicher sind. Das Ugg-Bondpad führt das negativste Potential und besitzt eine leicht modifizierte Schutzschaltung.

Auch am Ugg-Bondpad wurde die Standard-Schutzschaltung übernommen, musste aber etwas angepasst werden. Der Widerstand R1 dient hier nicht als Längswiderstand. Das reduziert zwar die Schutzwirkung der Schaltung, verhindert aber auch, dass durch den relativ hohen Strom über Ugg ein problematischer Spannungsabfall auftritt.

Die Eingänge der Tastaturmatrix sind etwas komplexer aufgebaut als der Takteingang. Neben der bekannten Schutzschaltung befindet sich dort ein Pull-Down-Widerstand (R2/R3). Auf die Entstörung folgen zwei Pufferstufen (Q2/R4 und Q3/R5). Da beide Puffer Inverter darstellen, hat das Ausgangssignal wieder den gleichen Pegel, wie das am Bondpad anliegende Signal. Zuletzt ist mit dem Kondensator C3 eine weitere Entprellung integriert.

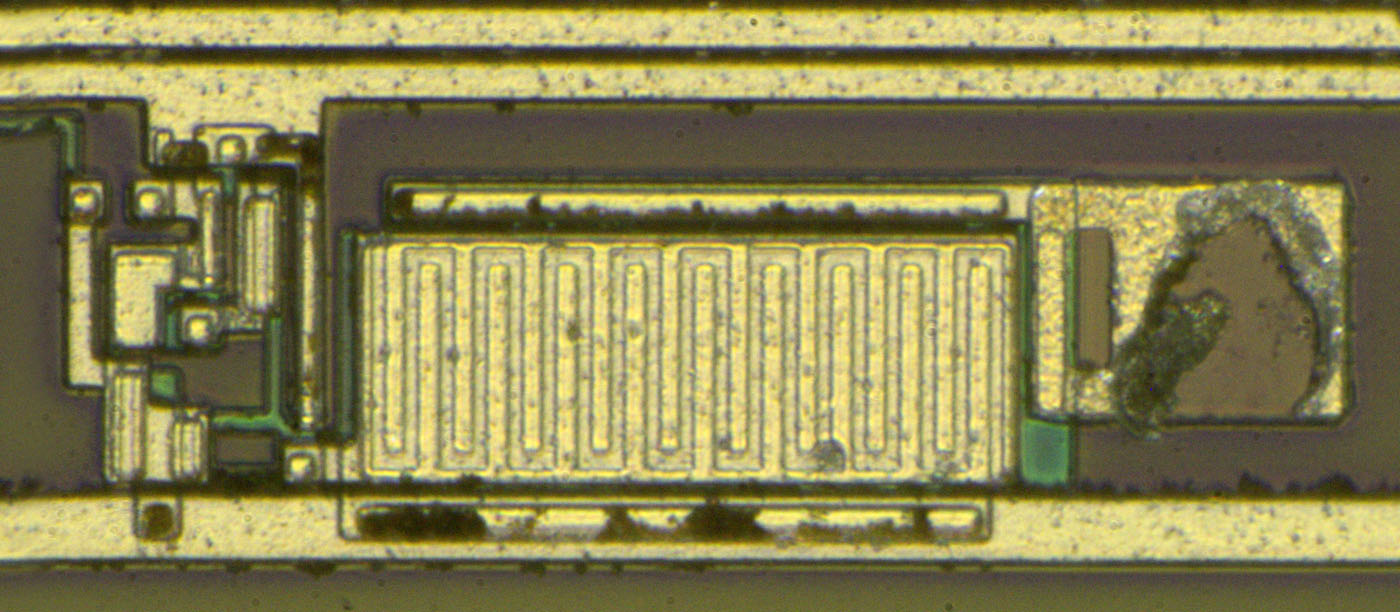

Die Ausgänge, die die Anzeigen mit Strom versorgen, sind relativ groß ausgeführt, so dass sie den im Datenblatt spezifizierten Strom von typischerweise 5mA tragen können (7mA maximal). Der durch die Metalllage erkennbare Mäander ist die Lücke zwischen zwei p-dotierten Flächen. Darüber befindet sich mit dem Rechteck der Metalllage die Gateleketrode und es bildet sich ein großer MOS-Transistor aus. Der kleine Schaltungsteil links des Leistungstransistors stellt eine Push-Pull-Stufe zur sauberen Ansteuerung dar.

Die Leistungstransistoren, die die Tastaturmatrix und die Digit-Treiber versorgen, sind etwas kleiner ausgeführt und können entsprechend höchstens 1,4mA leiten. Die Ansteuerung ist noch etwas komplexer als bei den Anzeigentreibern.

Die leichte Beschädigung am rechten Rand des Dies führt dazu, dass sich die elektrische Anbindung von zwei Bondpads nicht mehr mit endgültiger Sicherheit bestimmen lässt. Da allerdings keinerlei Leitungen aus diesem Bereich herausführen, kann man davon ausgehen, dass die Bondpads entweder Vss-Potential geführt haben oder elektrisch überhaupt nicht angebunden waren.

Der U821 besitzt einen mit "i.V." ("innere Verbindung") bezeichneten Pin, der nicht beschaltet werden darf. Es scheint, dass dieser Pin beim vorliegenden U821 keinerlei elektrische Funktion besitzt.

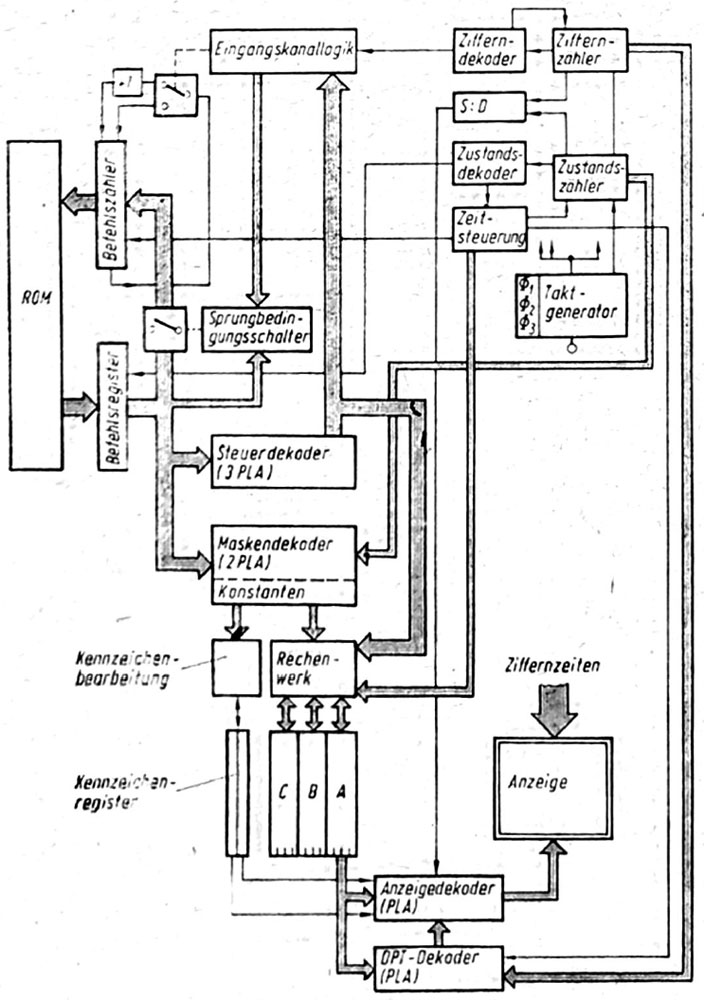

Die Zeitschrift Radio Fernsehen Elektronik 5/1978 enthält ein grobes Blockschaltbild des U821.

Ein US-Patent zeigt den Aufbau der Taschenrechner-Familie detaillierter (aufbereitet durch Dunkelwind aka bITmASTER).

Das hochaufgelöste PDF findet sich hier.

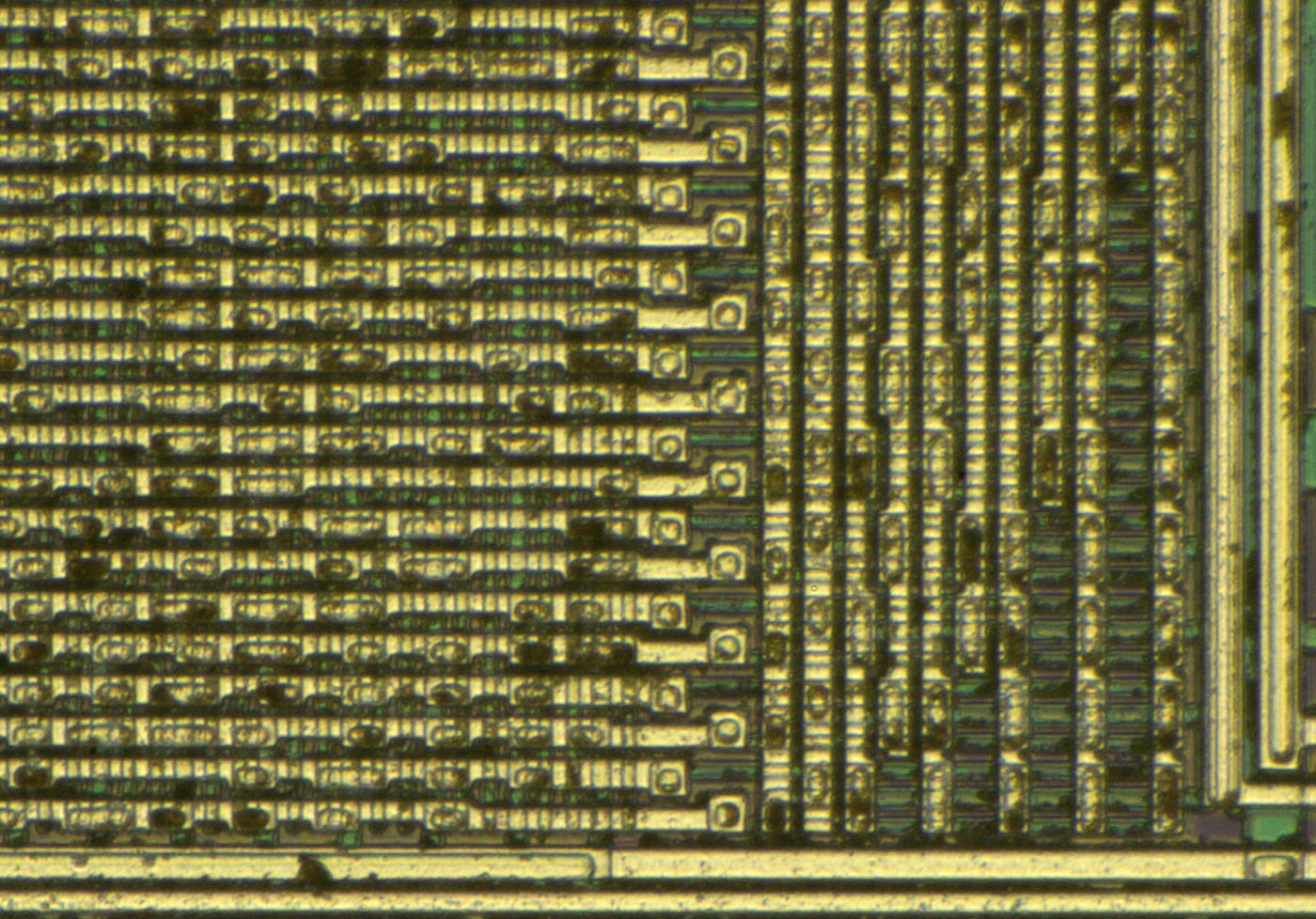

Dunkelwind (aka bITmASTER) konnte alle relevanten Funktionsblöcke des U821 herausarbeiten.

Dieses Bild ist in Originalgröße verfügbar (140MB).

Mit den Erkenntnissen war es Dunkelwind (aka bITmASTER) dann auch möglich einen Emulator des U821 zu programmieren.

Der Emulator findet sich hier.

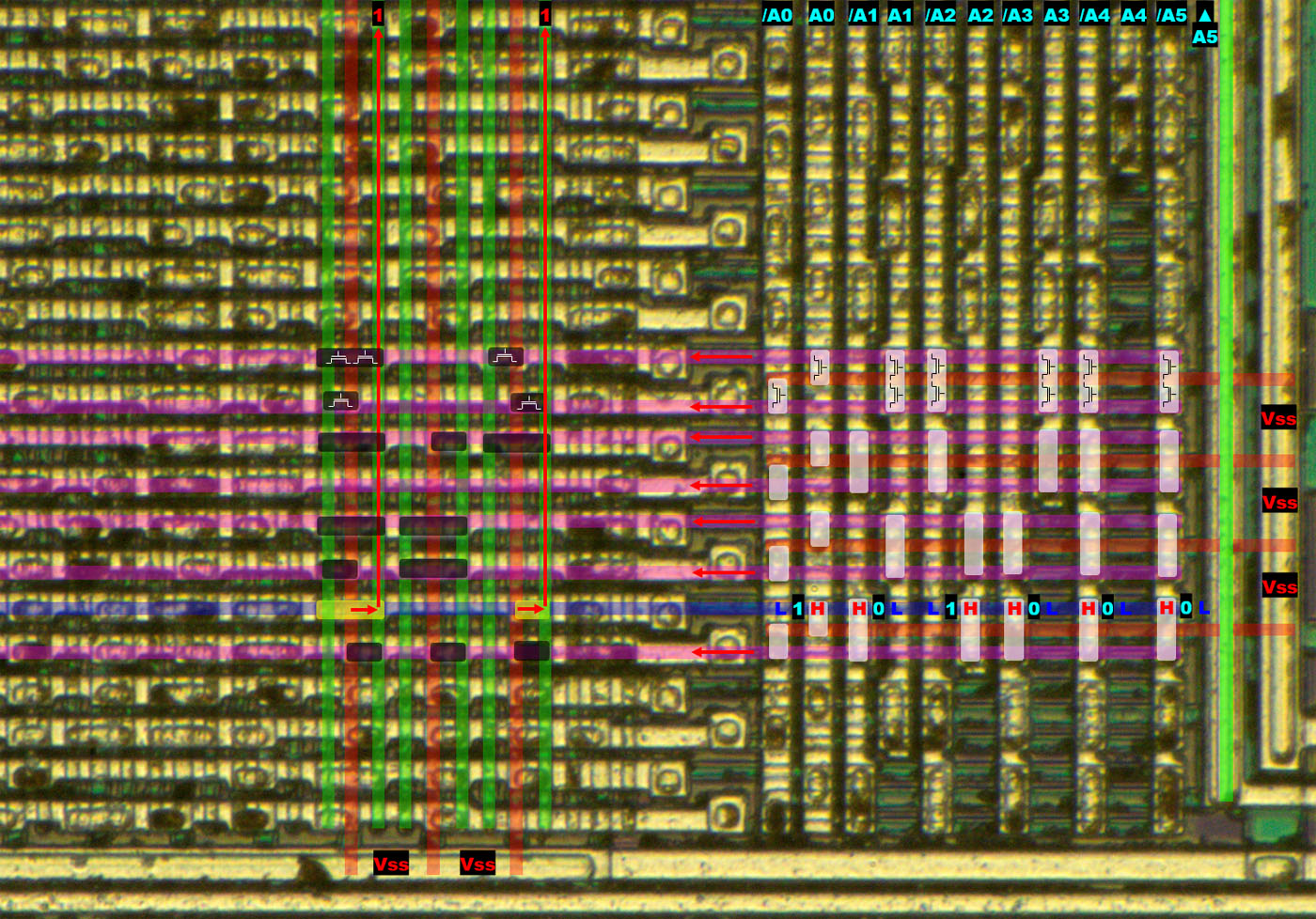

Obwohl die Bilder die Strukturen nicht perfekt abbilden, kann man mit etwas Aufwand auch die einzelnen Schaltungsteile rekonstruieren. Hier ist der maskenprogrammierte Speicher zu sehen, der die auszuführenden Funktionen in die notwendigen Steuersignale umwandelt.

An der rechten Kante des Speicherblocks befinden sich zwölf vertikale

Leitungen, die einen sechs Bit breiten Adressbus inklusive dessen

komplementären Signale übertragen (türkis). Auf den Adressleitungen sind Transistoren verteilt (weiß), die

eine leitende Verbindung zwischen den 64 horizontalen Adressleitungen (lila) und

den horizontalen, von rechts zugeführten Vss-Leitungen (rot) schaffen können.

Die

blau markierte Zeile zeigt, wie der Auswahlprozess abläuft. In allen inaktiven

Zeilen ist irgendein Transistor der Adress-Spalte aktiv, so dass sich fast alle

Zeilen des ROM-Arrays auf Vss-Potential befinden (rosa). Nur eine Zeile wird über den

Adress-Bus ausgewählt. In dieser Zeile ist kein Transistor aktiv, so dass

sich dort ein Low-Pegel einstellt (blau).

Rechts

der Adressspalte befindet sich ein grün markierter, vertikaler

Transistor, der sich über die ganze Adressspalte erstreckt und die Versorgung des Adressbereichs mit dem Vss-Potential

steuert. Es handelt sich anscheinend um einen Pull-Up-Transistor.

Innerhalb der Speichermatrix befinden sich immer zwischen zwei vertikalen Vss-Leitungen (rot) zwei vertikale Steuerleitungen (grün). Wird eine Adressleitung aktiviert, also auf Low-Pegel geschaltet (blau), so aktiviert das die daran angeschlossenen Transistoren (gelb), während alle anderen Transistoren gesperrt bleiben (schwarz). Leitende Transistoren übertragen das Vss-Potential auf die jeweilige Steuerleitung. In der Folge führen die Steuerleitungen High-Pegel, die an ihrer Kreuzung mit der ausgewählten Adressleitung einen Transistor besitzen. Durch die Platzierung der Transistoren kann man so die gewünschte Steuerungslogik programmieren.

Dieses Bild des U821 ist auch in einer höheren Auflösung verfügbar: 114MB

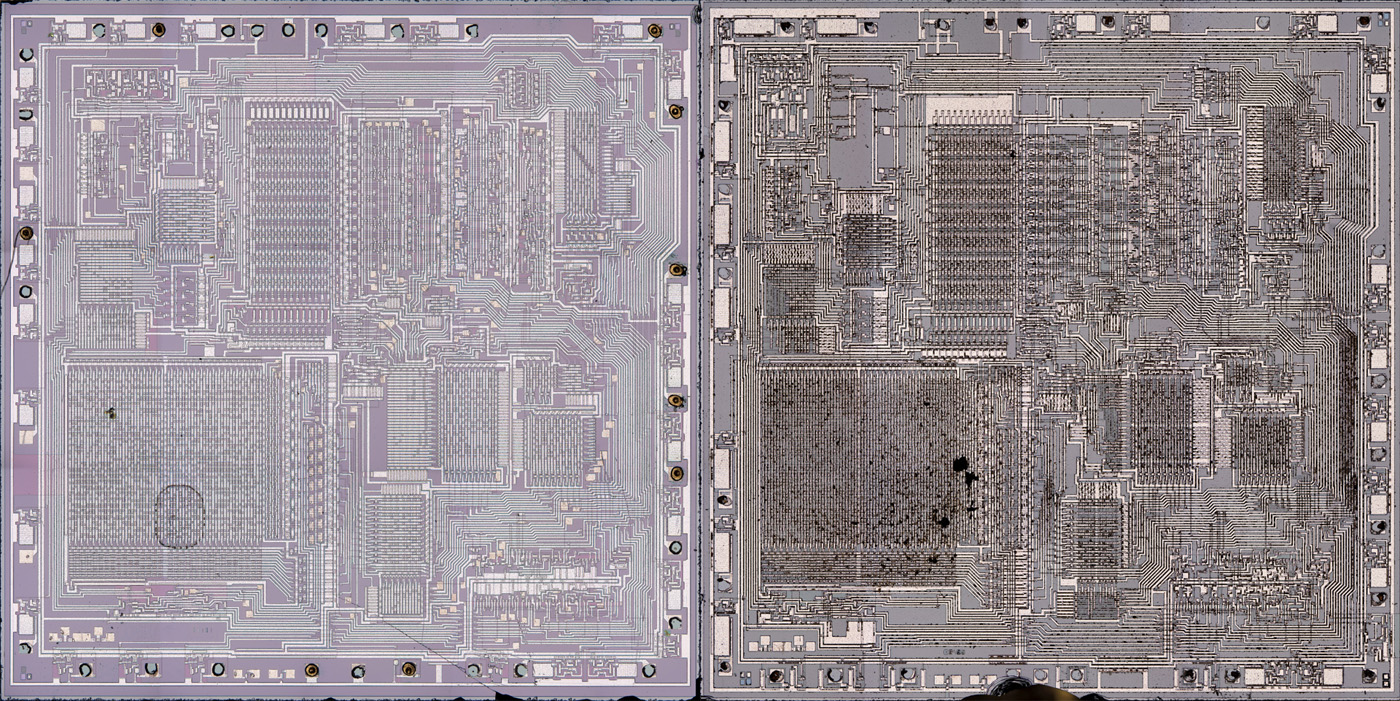

Vergleicht man den U820 mit dem U821, so zeigt sich, dass sehr viele Funktionsblöcke übernommen wurden. Die größten Änderungen finden sich in der linken oberen Ecke, aber auch an anderen Stellen hat man Schaltungen angepasst.