Der HML087 ist ein von Hughes Electronics produzierter PROM. Bei Hughes Electronics wurde der erste EEPROM entwickelt, der mit sehr dünnen Gateoxidschichten das sogenannte Fowler-Nordheim-Tunneln nutzte (US4115914). Maßgeblich daran beteiligt war Eli Harari, später CEO von Sandisk.

Zum HML087 findet sich kein Datenblatt. Er hat eine gewisse Bekanntheit erlangt, da er in Kombiinstrumenten von BMW eingesetzt wurde. Dort dient er der Konfiguration der Anzeigen. Wie sich noch zeigen wird, ähnelt der Aufbau der Speicherzellen des HML087 einem klassischen EEPROM. Wenn der Baustein online erwähnt wird, dann als nicht löschbarer PROM.

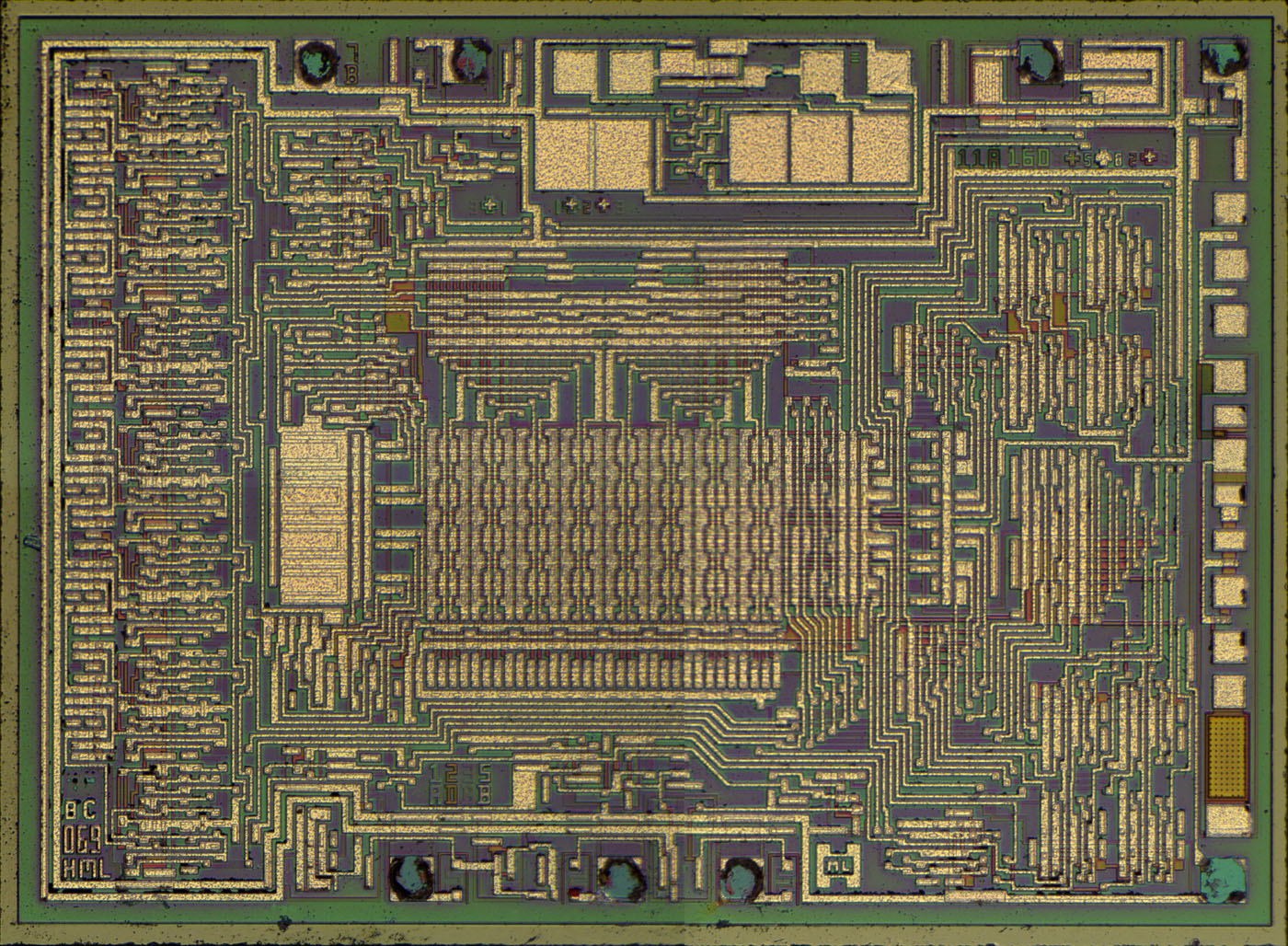

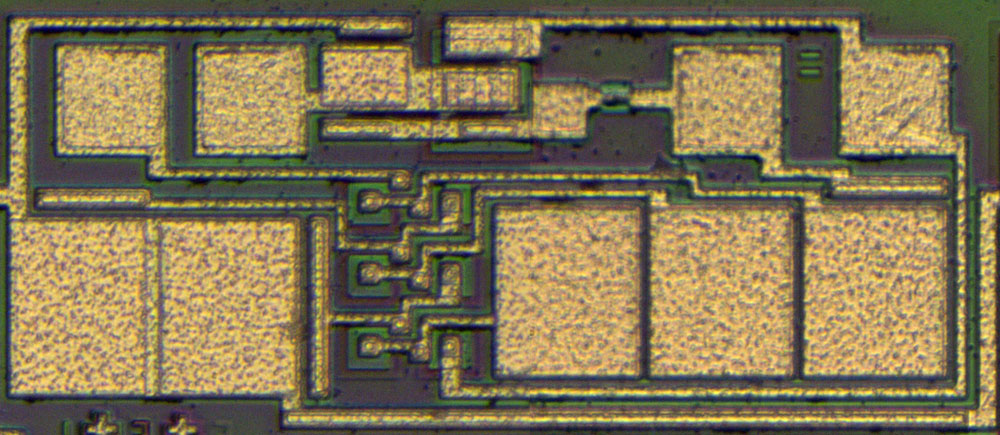

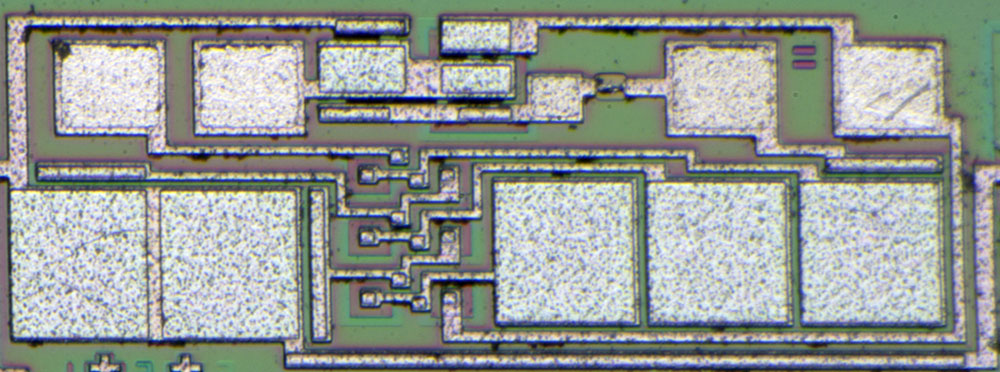

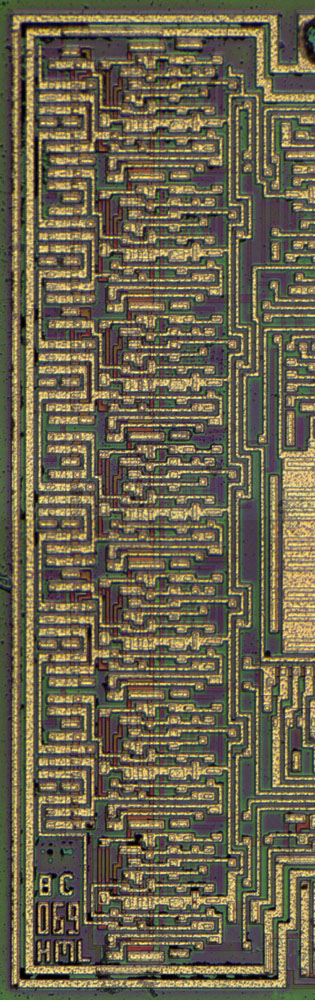

Die Abmessungen des enthaltenen Dies betragen 2,9mm x 2,1mm.

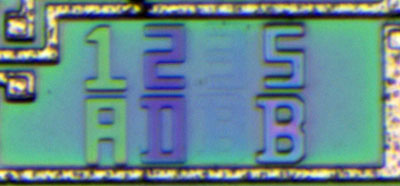

An der unteren Kante des Dies stellt ein Symbol die Buchstaben HML dar.

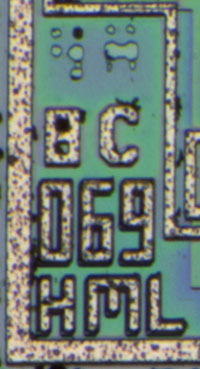

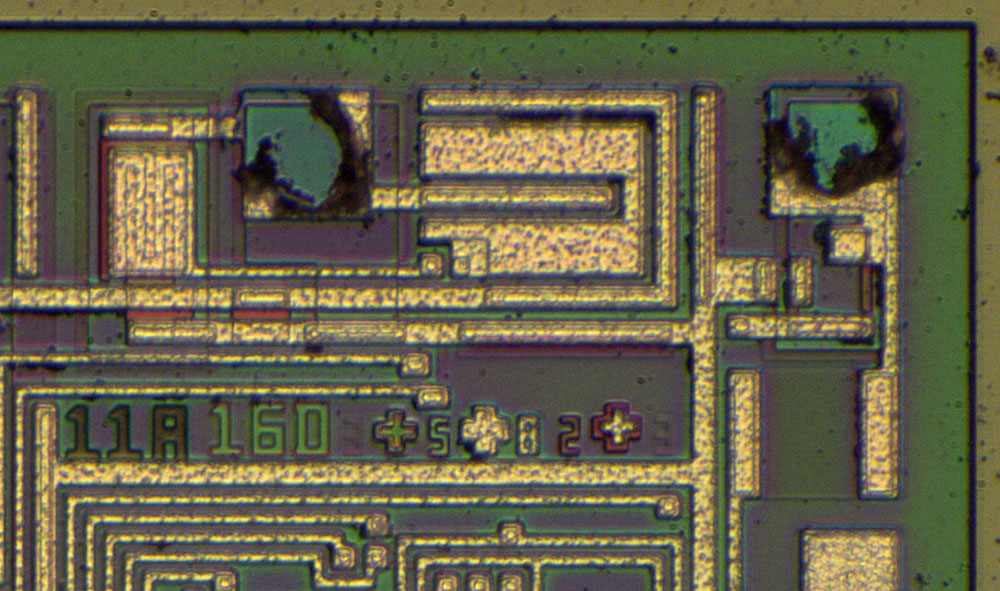

Die Beschriftung in der linken unteren Ecke lässt vermuten, dass es sich eigentlich um einen HML069 handelt. Zum HML069 finden sich leider ebenso wenige Informationen. In den Kompatibilitätslisten alter Universal-Programmiergeräte wird der Baustein als PROM geführt, der mit 12,25V zu programmieren ist.

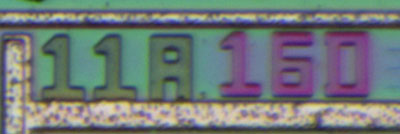

Über der Bezeichnung sind zwei Maskenrevisionen dargestellt: Die Zeichen 8C befinden sich in der Metalllage. Darüber meint man die Zeichen 4A oder 4H erkennen zu können.

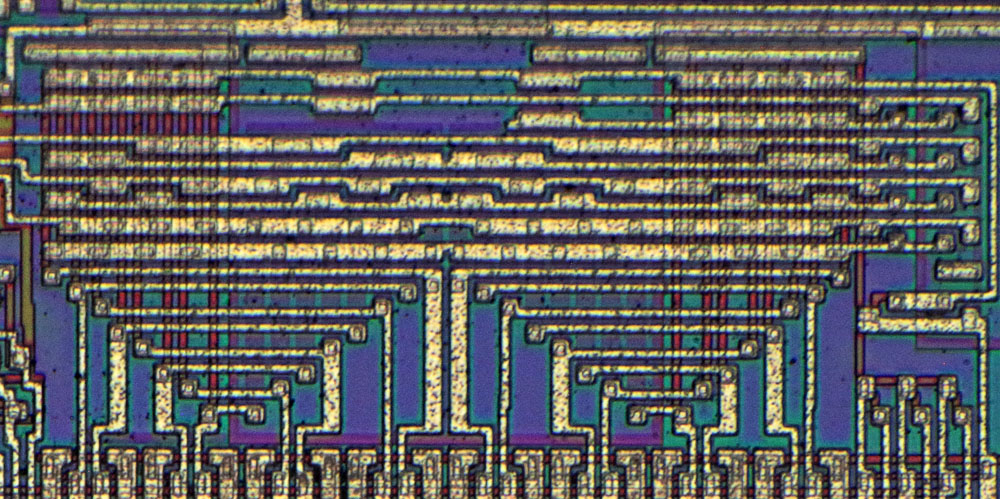

Im Auflicht, spätestens mit leicht schräg aufgenommenen Bildern, lassen sich meistens die unterschiedlichen Materialien und Strukturen eines integrierten Schaltkreises unterscheiden. Hier ist der Kontrast der Schicht 3B sehr schlecht, was die Analyse der Schaltung erschwert.

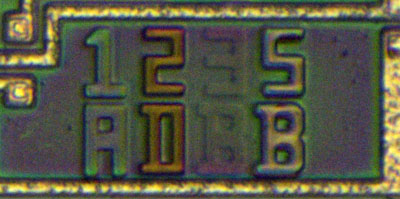

Zieht man alle über das Die verteilte Maskenrevisionen zusammen so ergibt sich die umfangreiche Liste: 1A, 2D, 3B, 4A, 5B, 7B, 8C, 11A, 16D

Viele der Masken beinhalten Kreuze, die in unterschiedlichen Kombinationen übereinander liegen. Das erlaubt es die Ausrichtung der Masken im Bezug zueinander zu überprüfen.

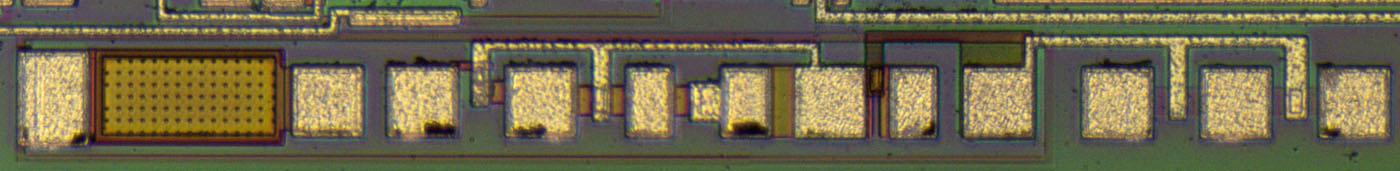

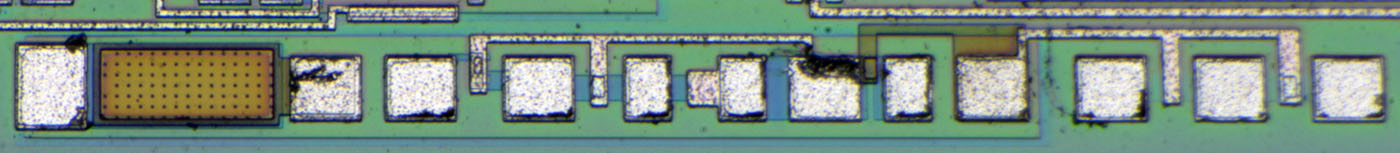

An der rechten Kante sind einige Teststrukturen integriert.

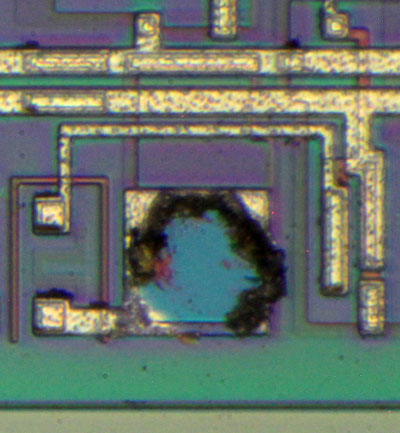

An der oberen Kante befindet sich eine verhältnismäßig große Teststruktur mit mehreren Kondensatoren und Transistoren. Es scheint sich hier um eine Art Ringoszillator zu handeln, über den die Qualität des Fertigungsprozesses überwacht werden konnte. Die Teststruktur besitzt sogar einen fusible Link in der Metalllage.

An den meisten Bondpads befinden sich ähnliche Schutzstrukturen.

Der Ausgang des HML087 ist gut zu erkennen. Rechts und links dieses Bondpads sind die verhältnismäßig großen Highside- und Lowsidetransistoren integriert. Von links treffen zwei differentielle Steuerleitungen ein.

In der rechten oberen Ecke des Dies befindet sich der Eingang für die erhöhte Programmierspannung. Das ergibt sich aus der Verschaltung des Potentials auf dem Die. Außerdem besitzt dieses Bondpad eine andere Schutzstruktur.

Die Funktionen der restlichen Bondpads lassen sich über den Schaltplan des BMW-Kombiinstruments und der Verschaltung auf dem Die rekonstruieren.

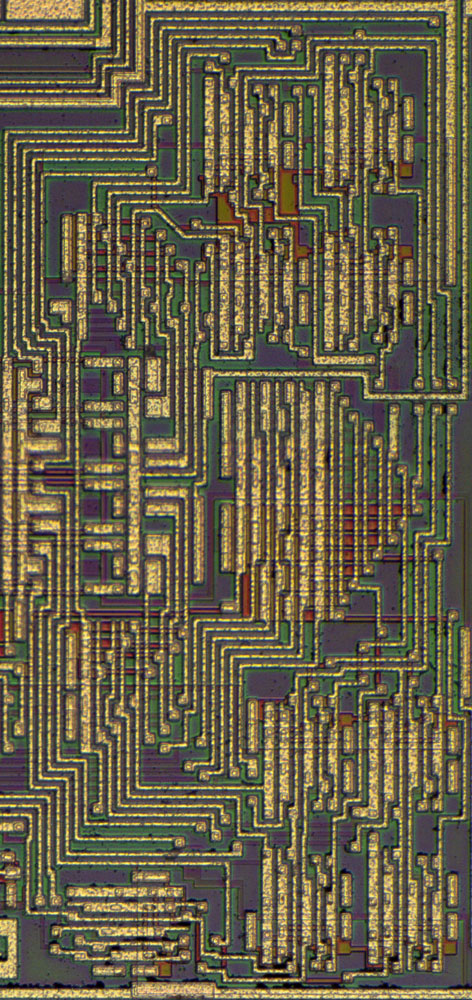

An der linken Kante des Dies finden sich sieben gleiche Schaltungen übereinander. Jeder Block ist mit dem Chip-Select-Signal und dem Taktsignal verbunden. Die Anbindung an den Speicherbereich zeigt, dass die unteren drei Blöcke die Zeilenauswahl steuern, während die oberen vier Blöcke die Spaltenauswahl kontrollieren. Es handelt sich höchstwahrscheinlich um sieben als Frequenzteiler verschaltete Flip-Flops, die einen vom Taktsignal gesteuerten, binären Zähler abbilden. So wird eine Zelle nach der anderen ausgewählt.

Links des Zählers befindet sich ein Streifen mit sechs gleichen Strukturen, die anscheinend den oberen sechs Frequenzteilern zugeordnet sind. Nachdem sie mit keinem anderen Bereich verbunden sind, kann man davon ausgehen, dass es sich um Hilfsschaltungen für den Zähler handelt.

Im rechten Bereich des Dies befinden sich acht gleiche Schaltungen, die alle mit dem Eingangs-Bondpad verbunden sind. In der Mitte wird die im linken Bereich generierte Zeilenauswahl weiter aufbereitet. Daraus erhält jede der acht Schaltungen ein exklusives Steuersignal. Daraus werden wiederum acht zusätzliche Zeilensignale erzeugt und zurück zum Speicherbereich geführt.

Mit ziemlicher Sicherheit handelt es sich hierbei um acht Flip-Flops, die als Zwischenspeicher für die seriell eintreffenden Daten dienen. Bei einem Schreibvorgang aktiviert die im linken Bereich generierte Zeilenauswahl nacheinander die Übernahme der Daten in die Flip-Flops. Danach geben die Flip-Flops die Daten an den Speicherbereich weiter.

An der unteren Kante des rechten Bereichs befindet sich ein Block, der den Zwischenspeichern gleicht, allerdings gedreht angeordnet und anders verschaltet ist. Auch dieser Block erhält das Eingangssignal, er ist aber nicht an die Zeilensteuerung des Speicherbereichs angebunden. Zwei Potentiale werden in den linken Bereich des Dies geführt. Die weitere Verschaltung lässt sich dort nicht rekonstruieren. Die Funktion des neunten Blocks bleibt entsprechend unklar. Wahrscheinlich müssen nach dem Senden von 8 Datenbits bestimmte Potentiale an den Pins anliegen, um das Schreiben der Daten auszulösen. Vielleicht wird dabei auch der finale Eingangspegel ausgewertet.

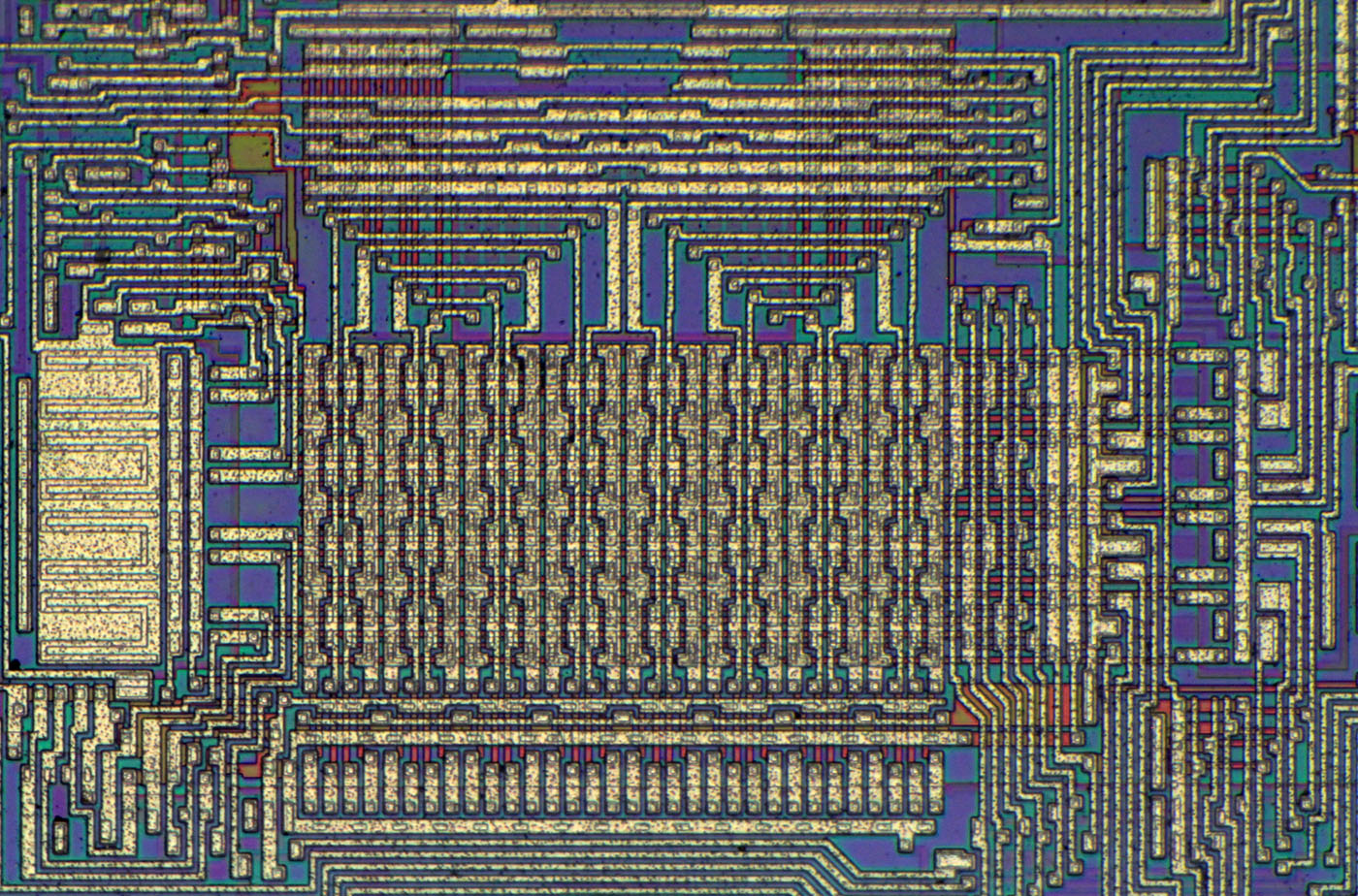

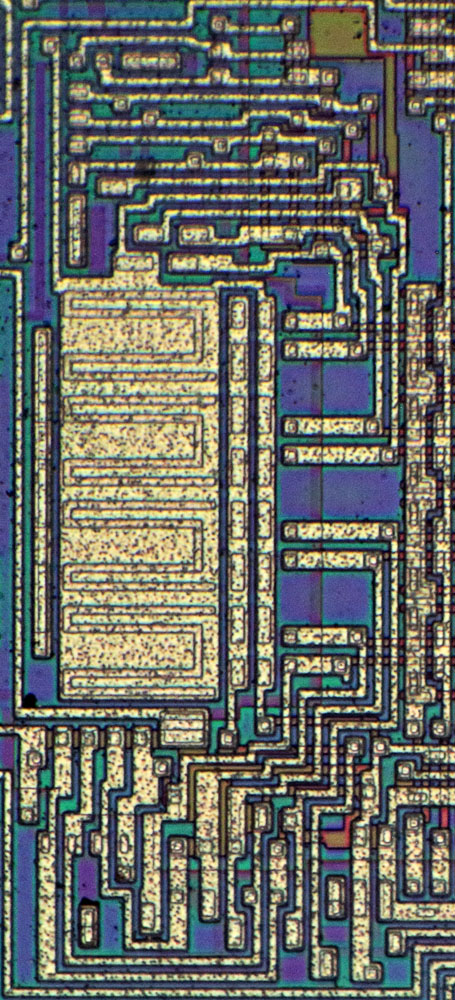

Die regelmäßige Struktur des Speicherbereichs in der Mitte des Dies lässt sich verhältnismäßig gut auflösen. Man kann bereits erkennen, dass die Speicherzellen wie klassische EEPROM-Zellen aufgebaut sind und dass es sich um 128 Zellen handelt. Oberhalb des Speichers befindet sich die Spaltenauswahl, rechts ist die Zeilenauswahl integriert. An der unteren Kante scheinen sich Hilfsschaltungen zur Bias-Einstellung zu befinden. Der linke Bereich muss die Ausleseschaltung sein, da von dort aus die differentiellen Leitungen zum Ausgangsbondpad verlaufen.

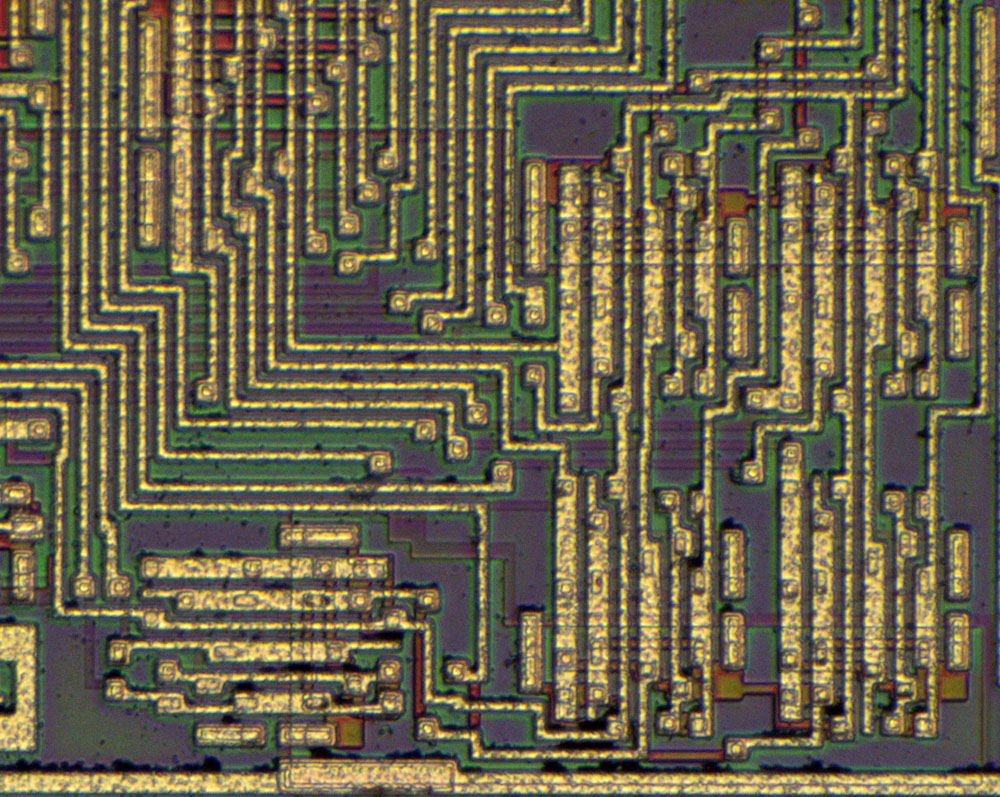

Die Spaltenauswahl besteht aus zwei gleichen Teilbereichen, die jeweils acht Spalten steuern. Jeder Bereich enthält einen Block mit Lowside- und einen Block mit Highsidetreibern, die für jede Spalte miteinander verbunden werden. Die einzelnen Lowsidetreiber ergeben sich durch die Überbrückung von zwei roten Leitungen über einen Gatebereich. Die Highsidetreiber sind Gatebereiche, die sich über einem Streifen des dunkelblauen, schlechter zu erkennenden Materials befinden. Während rechts genau der passende Binärwert anliegen muss, damit ein High-Pegel ausgegegen wird, gibt der linke Bereich nur bei diesem Wert keinen Low-Pegel aus. In der Folge wird für jeden Binärwert genau eine einzelne Spalte aktiviert.

Die Ausgangsbeschaltung ist schwer zu analysieren. Dass es sich um die Ausgangsbeschaltung handelt, ergibt sich aus der Verschaltung des Speicherbereichs und daraus, dass von dort die differentielle Leitung zum Ausgangstreiber entspringt.

Die Zeilenauswahl ist relativ komplex aufgebaut, da sie für Lese- und Schreibprozesse unterschiedliche Funktionen darstellen muss.

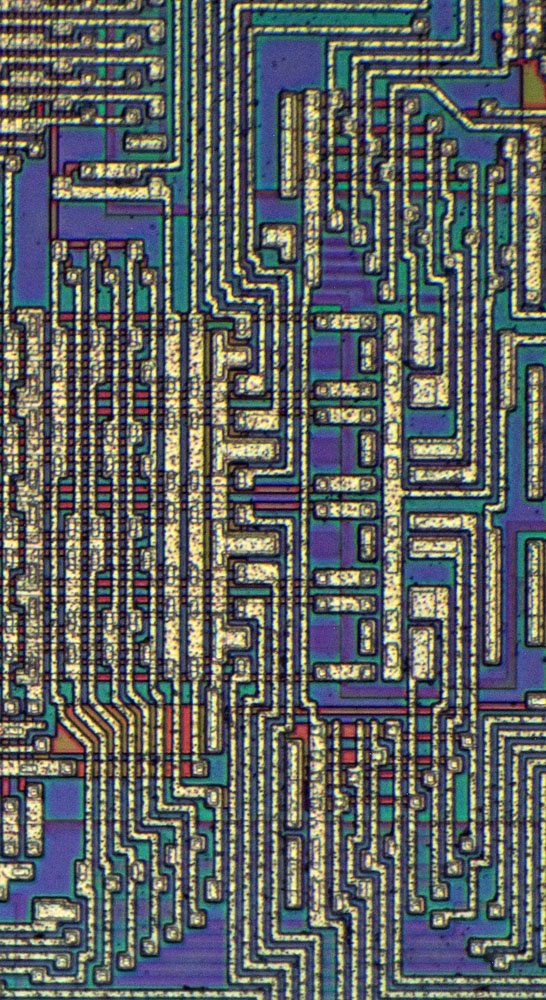

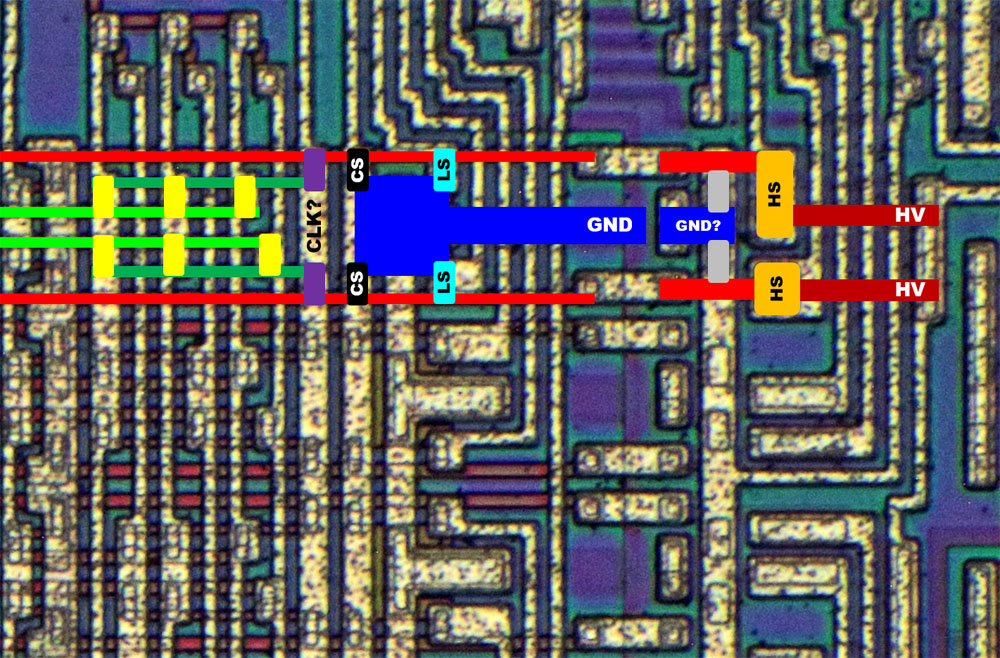

Von rechts trifft die erhöhte Programmierspannung ein (dunkelrot), die abhängig von den Eingangsdaten für die jeweilige Zeile freigeschaltet wird (orange). Die Leitungsführung ist hier nicht zu erkennen. Die Geometrien der nach unten folgenden Highsidetransistoren erscheint nicht besonders logisch. Links der Highsidetransistoren befinden sich weitere Transistoren, die die roten Leitungen mit dem Massepotential verbinden können (grau). Die vertikale Leitung, die diese Transistoren steuert, führt das Potential des Dateneingangs. Der funktionale Zusammenhang dieser Schaltung ist nicht ganz klar. Nach links folgt eine verhältnismäßig große Fläche innerhalb der Doppelzeile (blau), die anscheinend an die Masseleitung angebunden ist, die von unten heraufgeführt ist. Zwei MOSFETs, die von den Zwischenspeichern angesteuert werden, stellen Lowsidetransistoren dar, die die roten Leitungen mit dem Massepotential verbinden können (türkis). So ergibt sich eine Push-Pull-Ansteuerung, was plausibel wäre. Links davon befinden sich weitere MOSFETs, die an das Chipselect-Potential angebunden sind (schwarz).

Links der Steuerung für das erhöhte Potential verbinden an das Taktsignal angebundene MOSFETs (lila) die roten Leitungen mit den dunkelgrünen Leitungen. Aus diesen Potentialen speisen weitere MOSFETs (gelb) die grünen Leitungen, die innerhalb der roten Leitungen in den Speicherbereich führen. Die Steuerung der MOSFETs auf den grünen Leitungen erfolgt über die Zeilenauswahl.

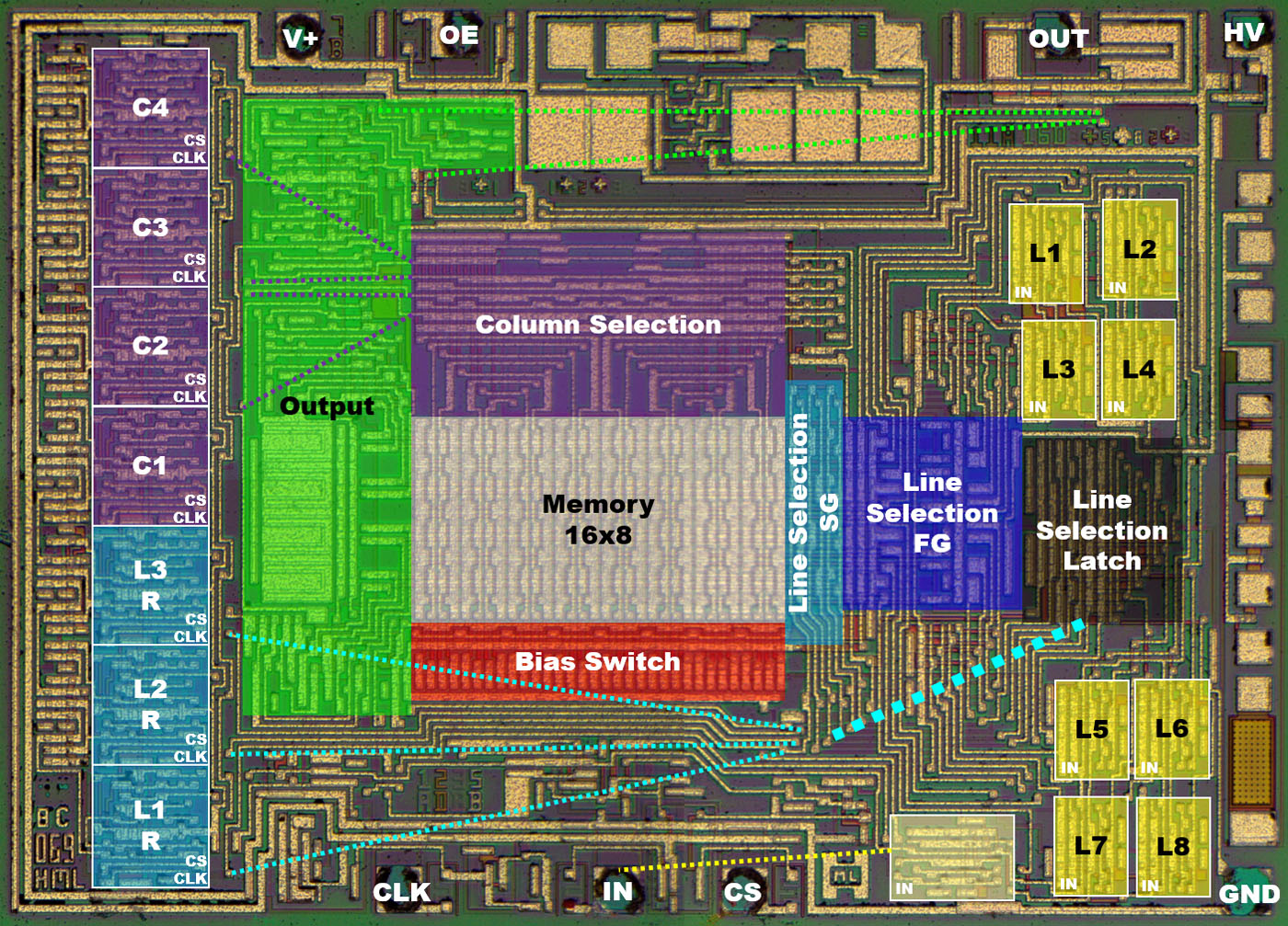

Markiert man die entsprechenden Bereiche auf dem Die, so ergibt sich das obige Bild. Zentrales Element ist der Speicherbereich (weiß). An der linken Kante befinden sich die Frequenzteiler, die die Ansteuerung der Zeilen (türkis) und Spalten (lila) darstellen. Die Verbindungen zu den entsprechenden Schaltungen um den Speicher herum sind gut zu erkennen. Die acht Zwischenspeicher für das Eingangssignal (gelb) sind mit dem Eingangsbondpad verbunden und werden über den Block "Line Selection Latch" (schwarz) angesteuert, der wiederum mit der Zeilenauswahl verbunden ist. Auch die Zeilenauswahl der Floating-Gate-Transistoren (blau) erhält aus dem Block "Line Selection Latch" seine Steuersignale, die teilweise oberhalb und unterhalb noch aufbereitet werden. Unterhalb des Speicherbereichs befinden sich Hilfsschaltungen, die die Potentiale im Speicher optimieren und gewisse Steuerungsaufgaben übernehmen (rot). Links des Speicherbereichs folgt die Auswerteschaltung (grün), die letztlich mit dem Ausgangstreiber verbunden ist.

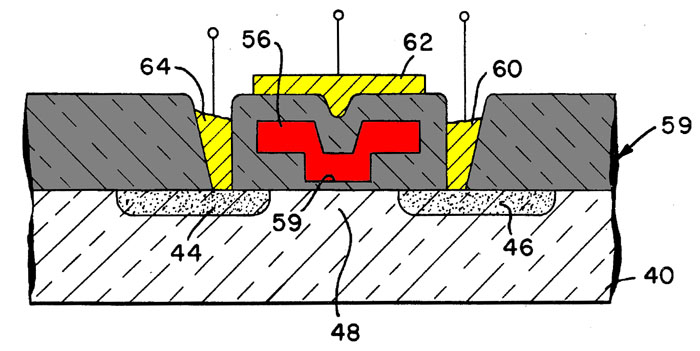

Das eingangs beschriebene Patent US4115914 zeigt den grundsätzlichen Aufbau eines EEPROM-Speichertransistors (nachträglich eingefärbt). In den verschiedenen Generationen von EEPROMs haben sich die Geometrien und Details mehrfach geändert, es findet sich aber immer ein Floating-Gate (59) unter einer Gatelektrode (62). Legt man an den Anschlüssen erhöhte Spannungen an, so lagern sich Ladungen in das Floating-Gate ein. Diese Ladungen verändern die Thresholdspannung des Transistors, was sich später wieder auslesen lässt. Das Ein- und Auslagern der Ladungen erfolgt über die sogenannte "hot electron injection" oder, wie im Patent beschrieben, über das Fowler-Nordheim-Tunneln. Vor allem die hot electron injenction schädigt das Gateoxid, was die begrenzten Lese-/Schreibzyklen von EEPROMs erklärt.

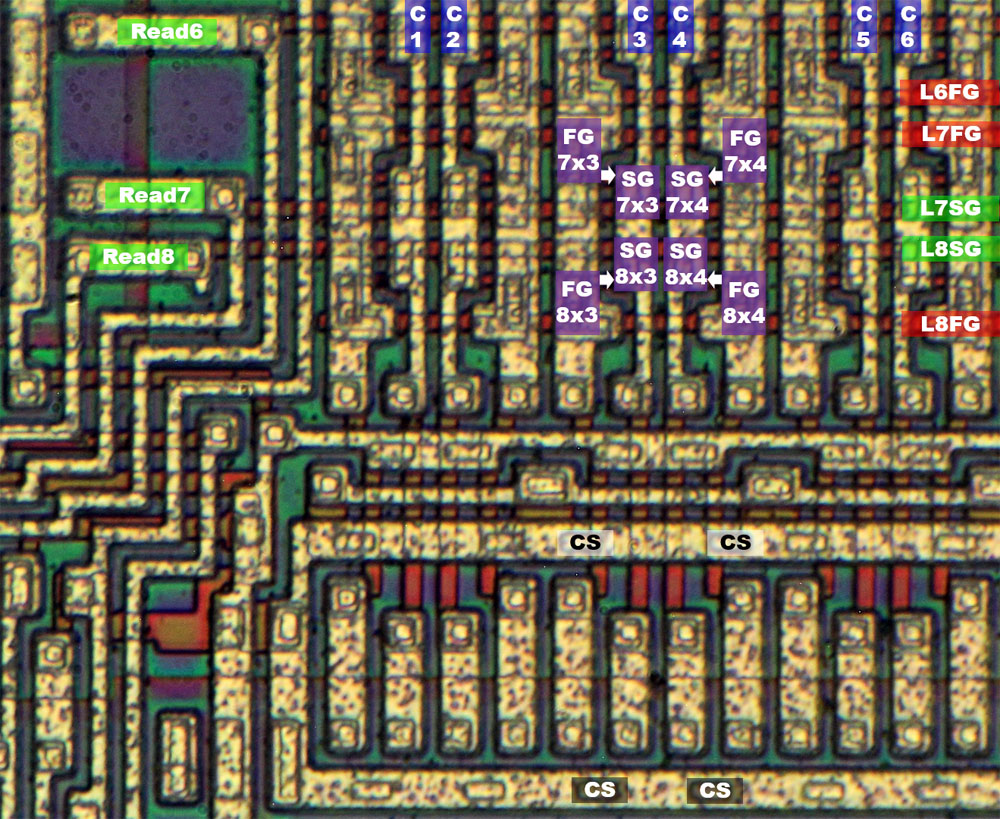

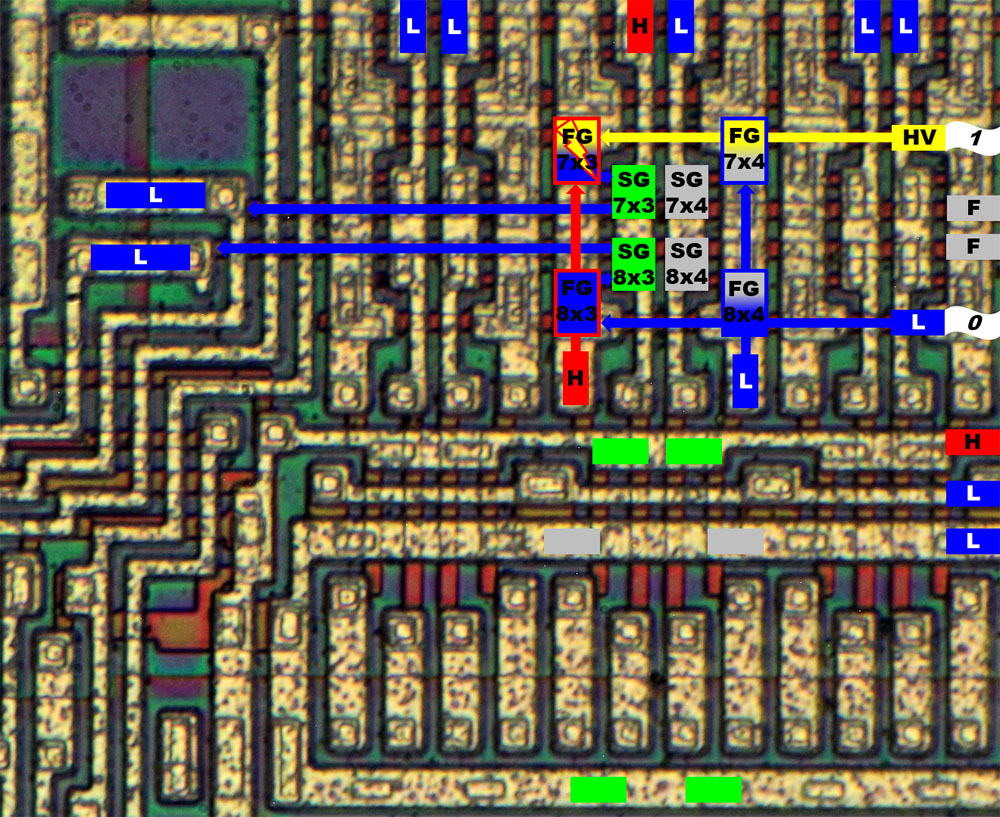

Der grundsätzliche Aufbau des Speicherbereichs ist gut zu erkennen. Jede Speicherzelle besitzt zwei Transistoren, einen Floating-Gate-Transistor (FG), der die Information abspeichert und einen Selection-Gate-Transistor (SG), der es erlaubt die Speicherzelle auszuwählen. Jeweils vier Speicherzellen bilden eine Gruppe.

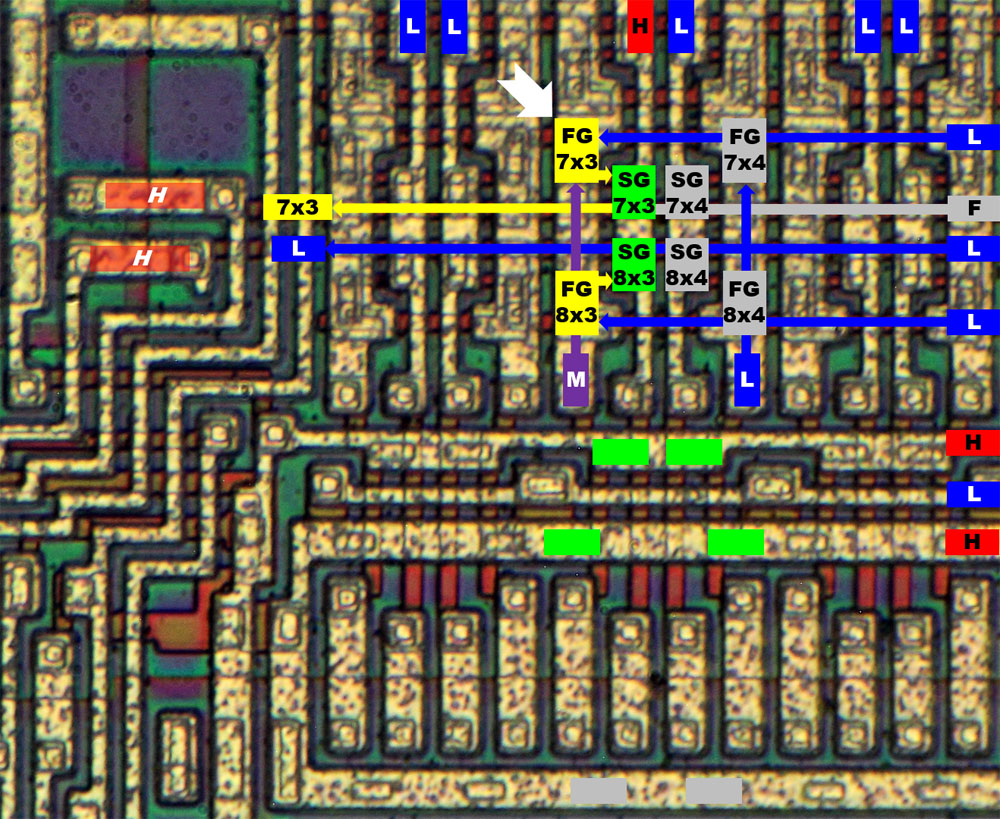

Die Spaltenauswahl (blau) steuert das Selection-Gate. Die Zeilenauswahl besteht aus zwei Elementen. Die äußeren Leitungen (rot) versorgen die Floating-Gate-Transistoren. Über sehr kurze rote Leitungen sind die Floating-Gate-Transistoren mit den Selection-Gate-Transistoren verbunden. Die Ausgänge der Selection-Gate-Transistoren einer Zeile kontaktieren eine gemeinsame rote Leitung, die sowohl zum linken Ausgang des Speichers (grün), als auch zur rechten Zeilenauswahl führt (grün).

Unterhalb des Speichers befinden sich mehrere Schaltungsteile, deren Funktionen sich nicht vollständig erklären lassen. Das Chipselect-Signal steuert zwei Reihen von Transistoren, die anscheinend komplementär sind. Was die unteren Transistoren (schwarz) schalten bleibt unklar. Die oberen Transistoren (weiß) können die Spalten der Floating-Gates mit einer Leitung der Metalllage verbinden, die das Massepotential führt. Die oberste Leitung des Bereichs ermöglicht es die Floating-Gates mit den Selection-Gates zu verbinden.

Das Auslesen von gespeicherten Informationen (hier Zelle 7x3) erfolgt wahrscheinlich folgendermaßen: Die Spaltenauswahl hebt die Spalte 3 auf einen High-Pegel. Über die direkt unterhalb des Speichers quer verlaufende Leitung und deren MOSFETs (grün) wird dieser High-Pegel auch zu den Floating-Gates der Spalte 3 übertragen. In diesem Zustand sind die Selection-Gate-Transistoren der Spalte 3 leitend, alle anderen sperren. Um die Floating-Gate-Transistoren korrekt auslesen zu können, muss an deren Gates üblicherweise ein mittleres Potential angelegt werden. Es ist denkbar, dass die leitenden Transistoren in der Mitte des unteren Bereichs (grün) den High-Pegel mit dem seitlich zugeführten Low-Pegel auf das optimale Potential ziehen. Je nachdem ob in den Floating-Gates Ladungen gespeichert sind, wird der zugehörige Transistor bei dem mittleren Gate-Potential leitend oder er bleibt gesperrt (gelb).

In dieser Konfiguration würde jede Speicherzelle der Spalte 3 seinen gespeicherten Zustand ausgeben. Die Daten müssen aber nacheinander ausgegeben werden. Die Zeilenauswahl auf der rechten Seite kann in diesem Zustand lediglich einen Low-Pegel zu oder abschalten. Wahrscheinlich befindet sich in der Ausgangsbeschaltung ein hochohmiger Pull-Up-Widerstand. Die nicht ausgewählten Zeilen zieht die Zeilenauswahl auf einen Low-Pegel. Das Potential der ausgewählten Zeile 7 bestimmt die aktive Zelle 7x3. Abhängig vom gespeicherten Wert ist die Zelle isolierend oder leitend, wodurch das Potential der Zeile 7 entweder auf einem High-Pegel verbleibt oder über die Zelle auf einen Low-Pegel gezogen wird.

Das Beschreiben der Speicherzellen erfolgt Spalte für Spalte, da die Zwischenspeicher jeweils acht Bit enthalten, die gleichzeitig in den Speicher geschrieben werden können. Um Ladungen in den Floating Gates einbringen können, benötigt man eine erhöhte Spannung. Über die Zeilenauswahl wird das erhöhte Potential (HV) an die Floating-Gate-Transistoren angelegt, die geladen werden sollen, hier die Zelle 7x3. Die Zelle 8x3 soll dagegen inaktiv bleiben.

Die Spaltenauswahl aktiviert wie beim Lesen der Daten die Selection-Gate-Transistoren. Eine Querverbindung im unteren Bereich führt den High-Pegel der aktivierten Spalte auch zu den Floating-Gates. Man kann davon ausgehen, dass die Ausgangsschaltung beim Schreibvorgang einen Low-Pegel auf die Zeilen legt. Anders lässt sich ein gezielter Schreibvorgang nicht erklären. Das würde auch erklären warum die Ausgangsbeschaltung verhältnismäßig aufwändig ist.

Beim Schreibvorgang handelt es sich um die sogenannte "Drain Avalanche Hot-Carrier Injection". Dabei wird der Floating-Gate-Transistor mit einer hohen Drain-Source-Spannung und einer verhältnismäßig mittleren Gate-Source-Spannung betrieben. Durch die hohe Drain-Source-Spannung entstehen im Kanal des Transistors freie Ladungsträger, die sich im Floating Gate einlagern. Der Vorgang ist sehr belastend für das Gateoxid, erfolgt in einem PROM allerdings nur einmal.