Analog Devices brachte 1978 den 12Bit-Digital-Analog-Wandler AD565 auf den Markt. 1981 wurde er anscheinend auf den AD565A umgestellt. Der AD565 weist minimal bessere Spezifikationen auf. Um eine Sortierung kann es sich dabei nicht handeln, da der zweite Buchstabe bereits die Qualitätsstufe des D/A-Wandlers ausweist. Es ist durchaus denkbar, dass der Fertigungsprozess umgestellt wurde und damit die ursprünglichen Spezifikationen nicht mehr eingehalten werden konnten.

Der AD565A ist mit den Indizes J, K, S und T erhältlich. Die Varianten K und T sind typischerweise um einen Faktor 2 genauer (+/-1/8 LSB statt +/-1/4 LSB). Die Varianten S und T sind für einen größeren Temperaturbereich von -55°C bis 125°C spezifiziert.

Der Offset beträgt typischerweise 0,01% der Vollaussteuerung und driftet mit nur 1ppm/°C. Der Verstärkungsfaktor driftet typischerweise mit 15ppm/°C. Bemerkenswert war zur damaligen Zeit die schnelle Einschwingzeit. Um einer Änderung des Sollwerts von 0% auf 100% zu folgen benötigt der AD565A nur 15ns bis 50ns (10% - 90%). Bis der Sollwert auf 1/2LSB eingestellt ist vergehen maximal 400ns. Der AD565A ist damit deutlich schneller als sein Vorgänger, der AD562.

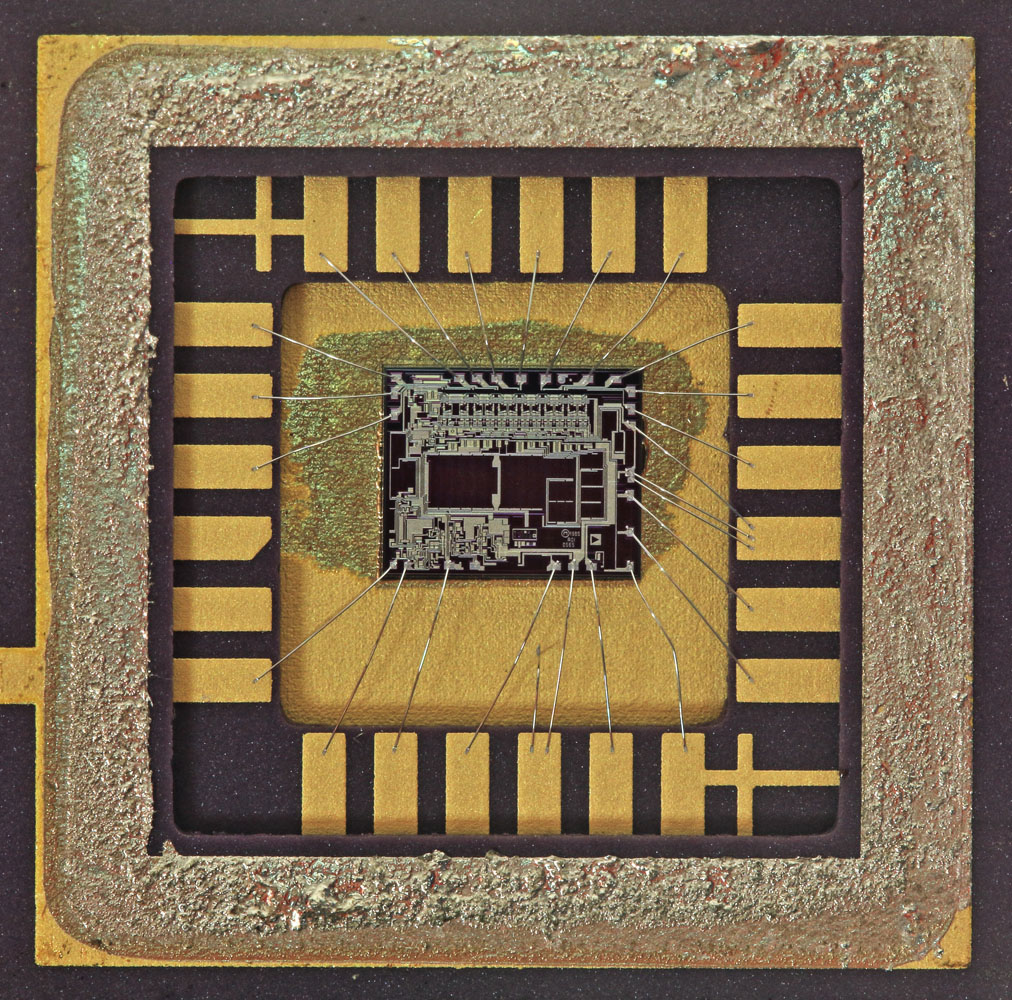

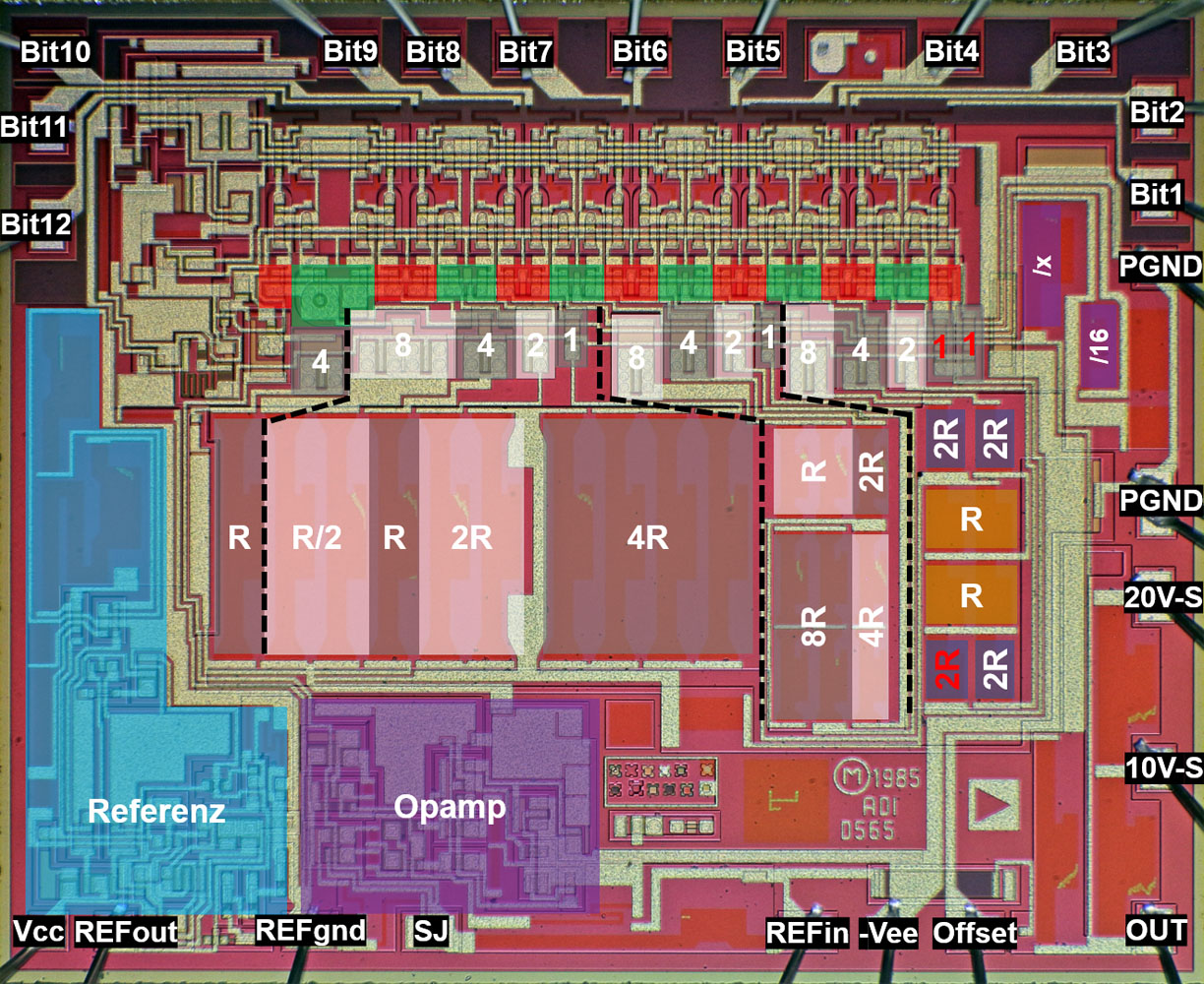

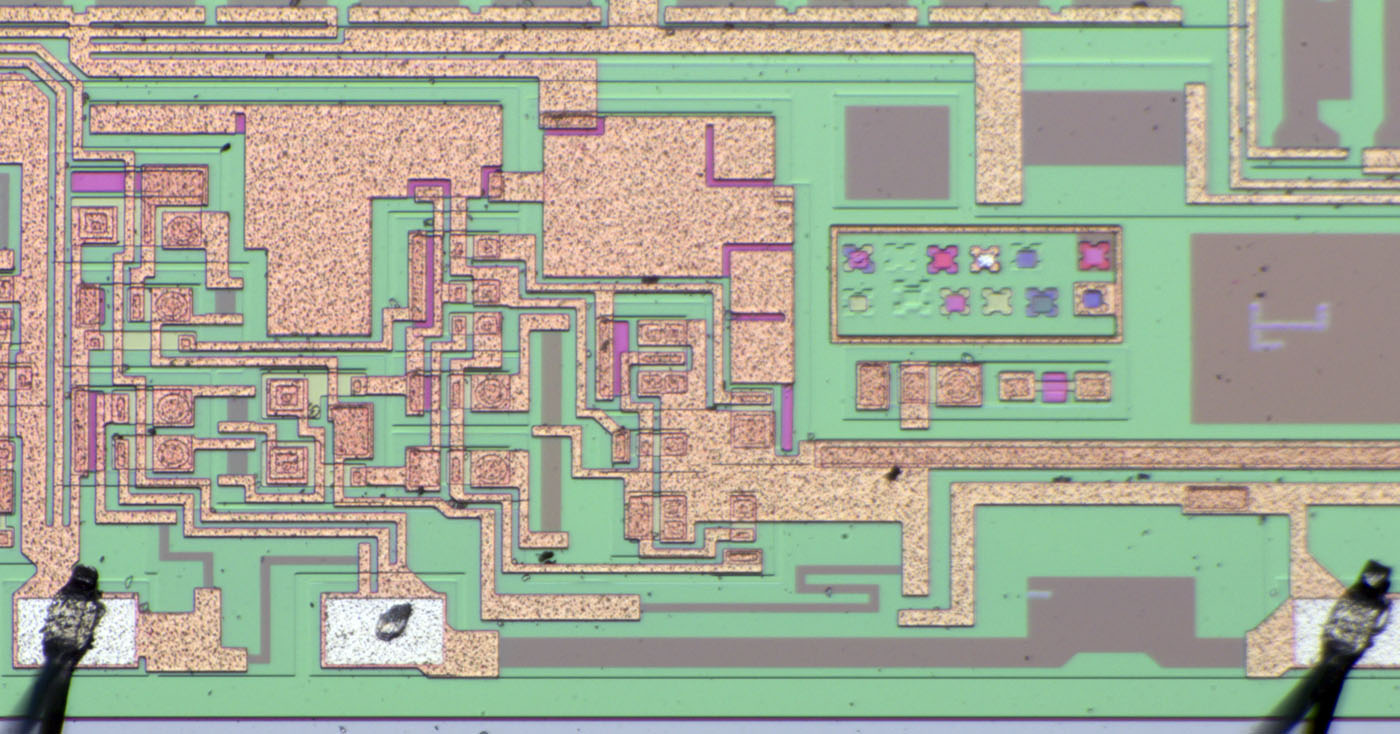

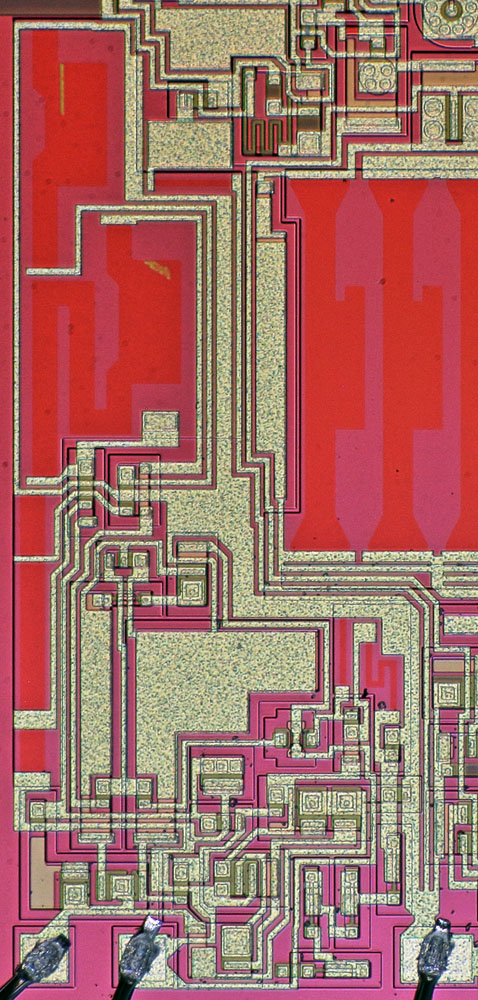

Das Die ist nicht ganz mittig platziert, vermutlich um die Grundplatte des Gehäuses einfacher mit dem negative Versorgungspotential (unten mittig) verbinden zu können. Das PGND-Potential der rechten Kante führen drei Bonddrähte zu zwei Bondpads auf dem Die.

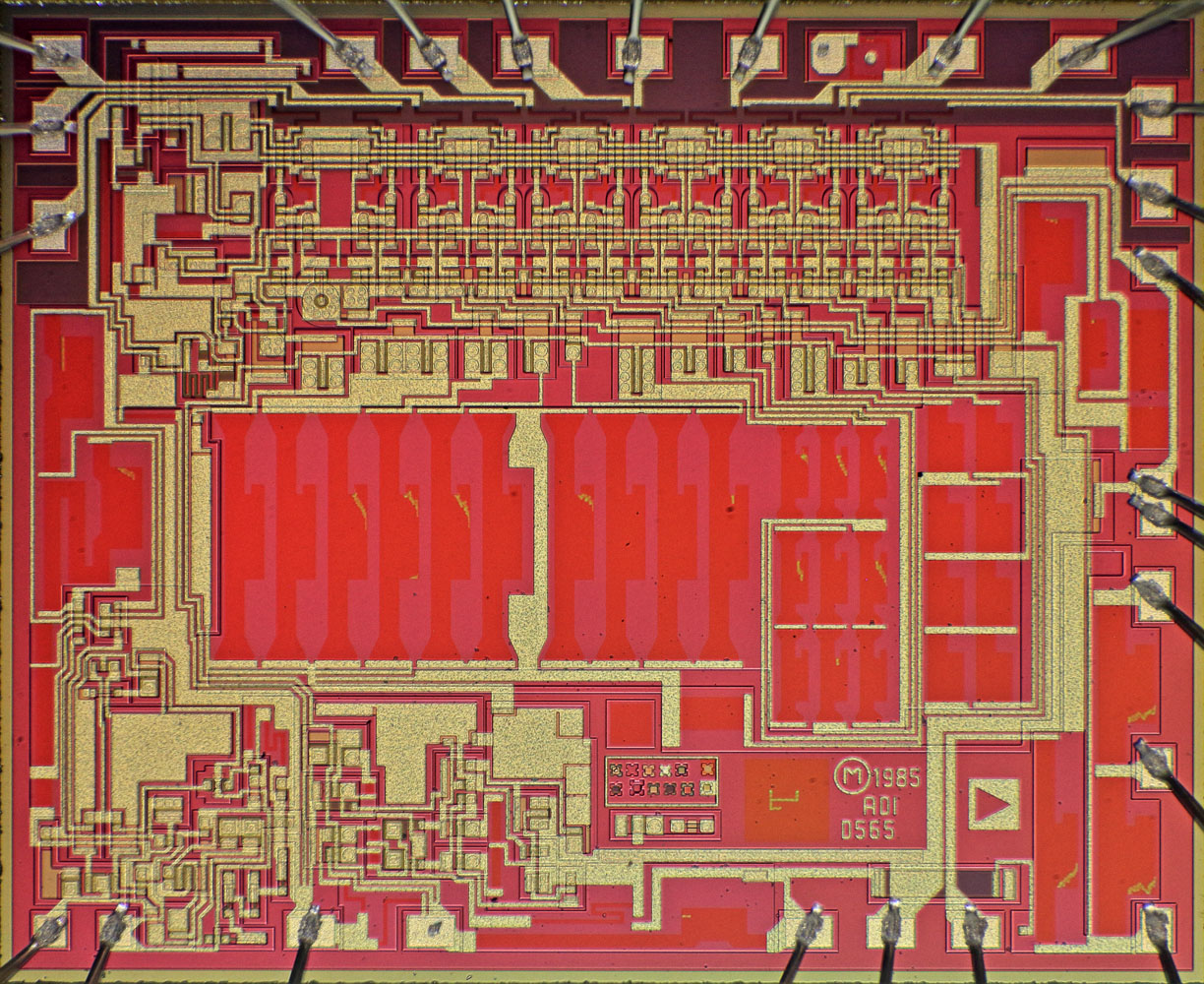

Das Die ist noch einigermaßen übersichtlich aufgebaut. Einen großen Teil der Fläche nehmen die abgeglichenen Widerstände ein.

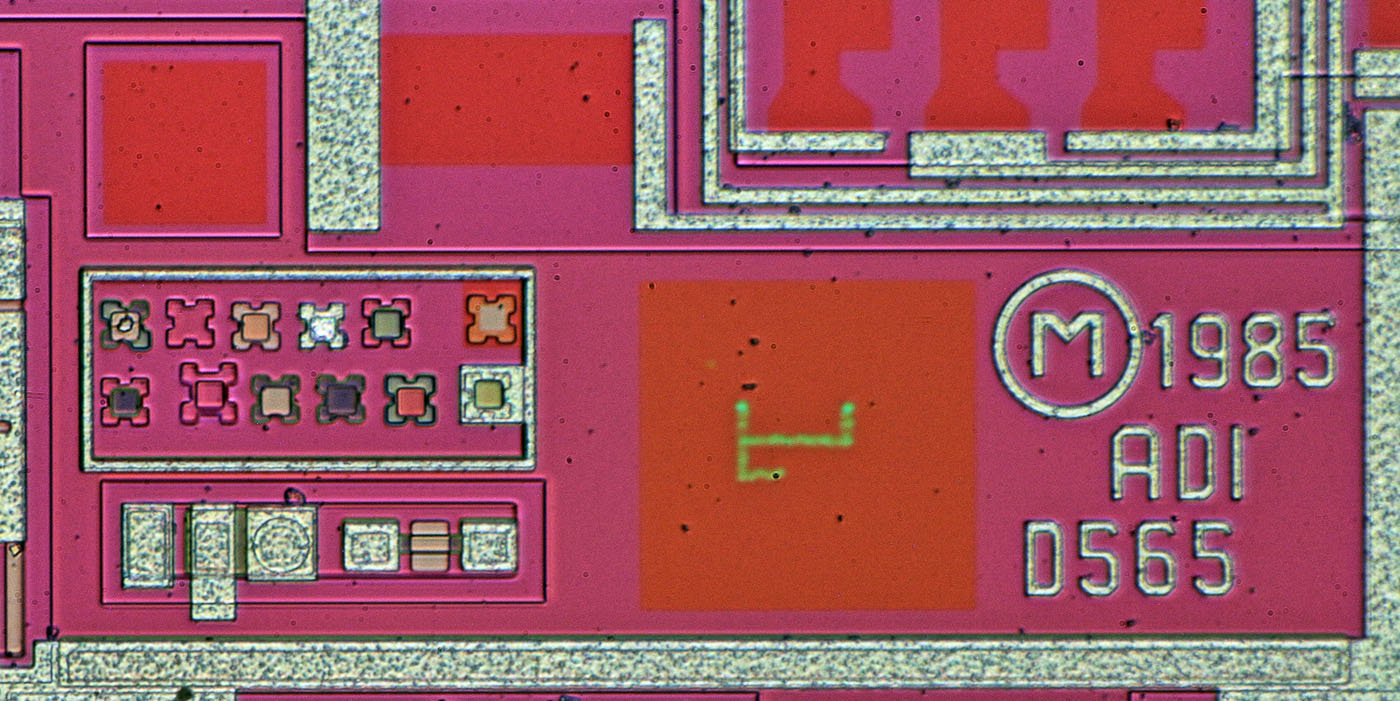

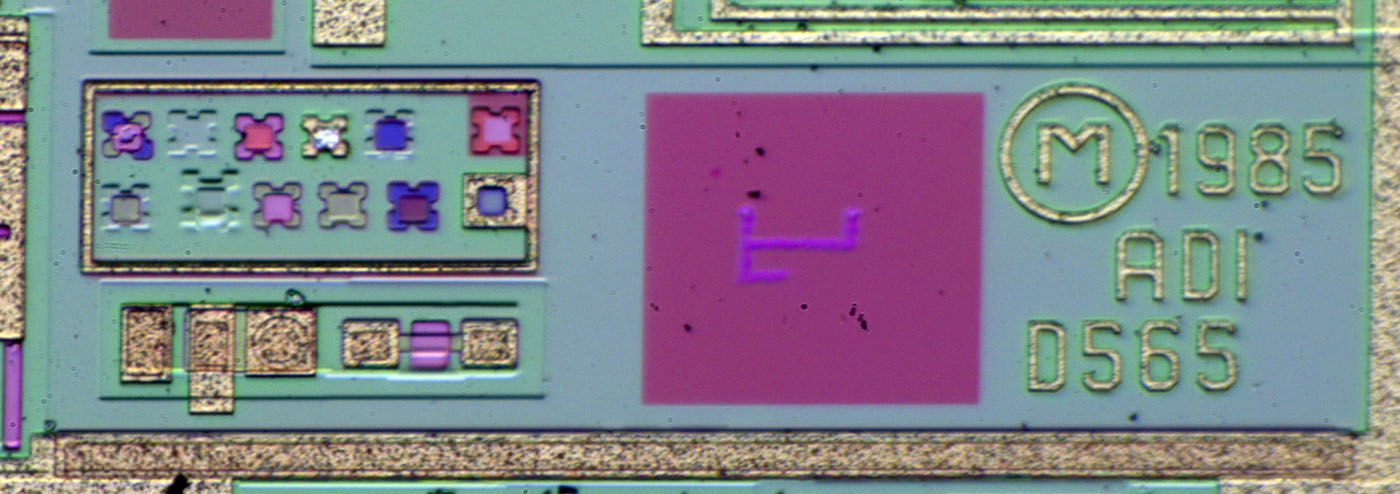

Das Design scheint aus dem Jahr 1985 zu stammen. Der AD565A wird allerdings bereits 1981 verkauft. Das spricht dafür, dass 1985 eine Überarbeitung des Designs erfolgte.

Während des Abgleichs der Widerstände wurde anscheinend die Zahl 1 in ein Quadrat eingebrannt. Eine solche Markierung ist auch in der Referenzspannungsquelle AD587 zu sehen. Die Zahl könnte eine Qualitätsstufe des Abgleichprozesses kennzeichnen. Es könnte aber auch sein, dass mehrere Abgleichanlagen vorhanden waren und über die Zahl die verwendete Anlage zurückverfolgt werden kann.

Links im Bild befinden sich zwölf Formen, die vermutlich als Ätzmarker dienen

und es so ermöglichen den Herstellungsprozess zu überwachen.

Unter den

Ätzmarkern ist zu Testzwecken links ein Transistor und rechts ein

Pinch-Widerstand integriert.

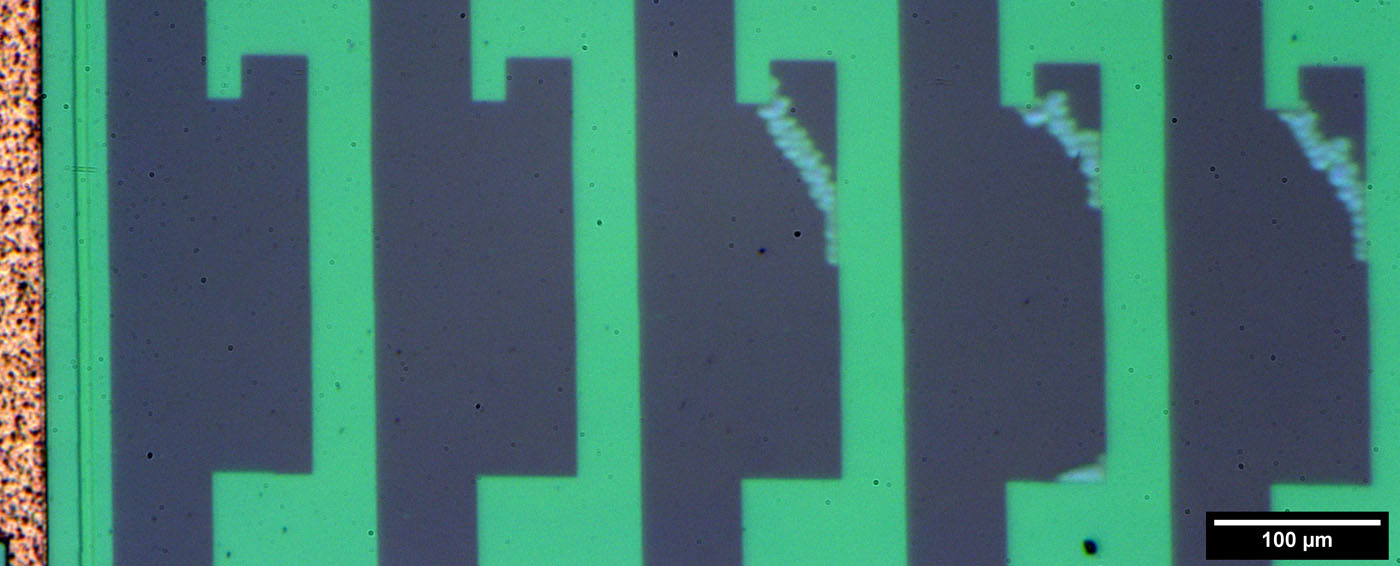

Es scheint, dass nicht alle Widerstände abgeglichen wurden. Die Widerstände

sind aber zum Großteil parallel und seriell geschaltet, weswegen es ausreichend

war nur ein Element der zusammenhängenden Widerstände abzugleichen.

Der

Abgleich erfolgte von einer Einkerbung aus zum Rand hin. Durch diesen Weg ändert

sich der Widerstandswert zu Beginn stärker,

was vorteilhaft ist für den Abgleichvorgang. An der unteren rechten Ecke scheint

teilweise eine zusätzliche Korrektur erfolgt zu sein.

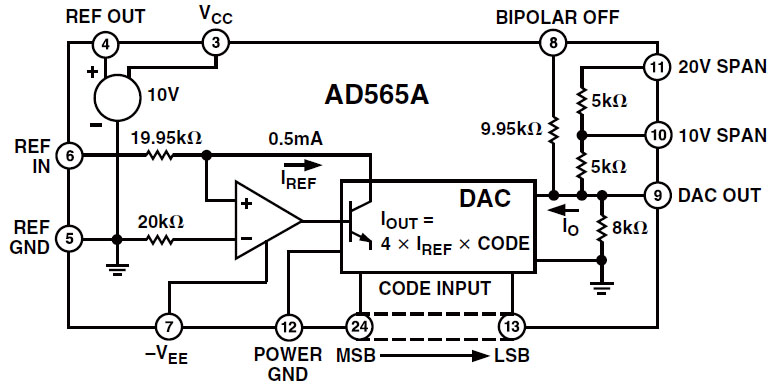

Im Datenblatt des AD565 ist ein Blockschaltbild abgedruckt, das nichts Außergewöhnliches enthält. Der Aufbau ähnelt dem DAC80.

Der AD565A enthält eine 10V-Referenzspannungsquelle, deren Potential aus dem Gehäuse herausgeführt wird. Durch diesen Aufbau kann entweder diese Referenzspannungsquelle oder eine externe Referenzspannung genutzt werden. Ein integrierter Operationsverstärker generiert daraus den Referenzstrom für den eigentlichen Digital-Analog-Konverter. Für die Referenzspannungsquelle und den Operationsverstärker steht das exklusive Bezugspotential "REF GND" zur Verfügung.

Der eigentliche DAC-Bereich ist nur angedeutet und stellt einen Strom zwischen 0mA und dem vierfachen Referenzstrom ein. Der DAC bezieht sich auf das Bezugspotential "POWER GND".

Am Ausgang des DAC-Blocks sind vier Widerstände integriert, die es ermöglichen mit einem externen Operationsverstärker den Ausgangsspannungsbereich und den Offset einzustellen. Auf die Integration eines Ausgangs-Operationsverstärkers in den AD565 wurde verzichtet.

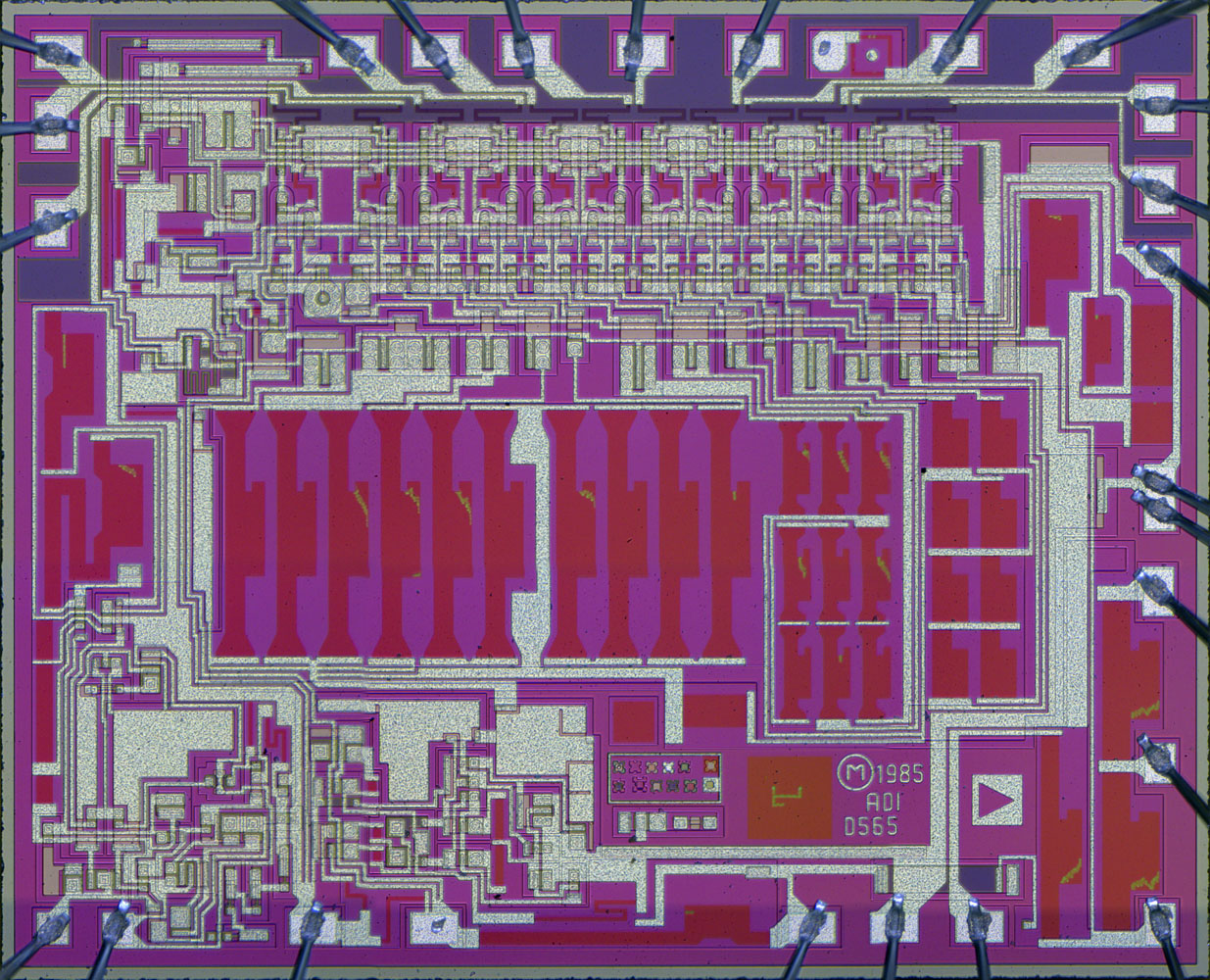

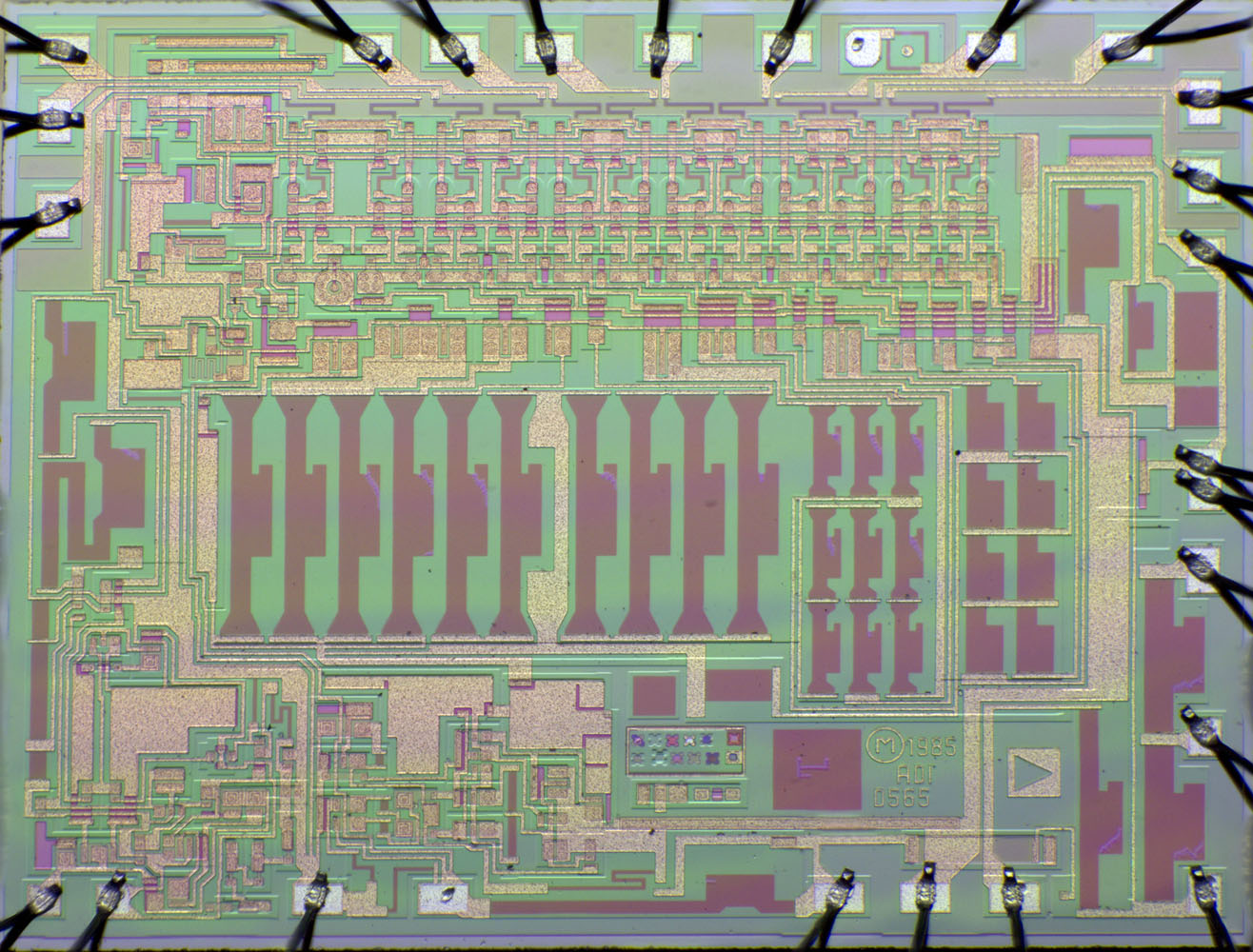

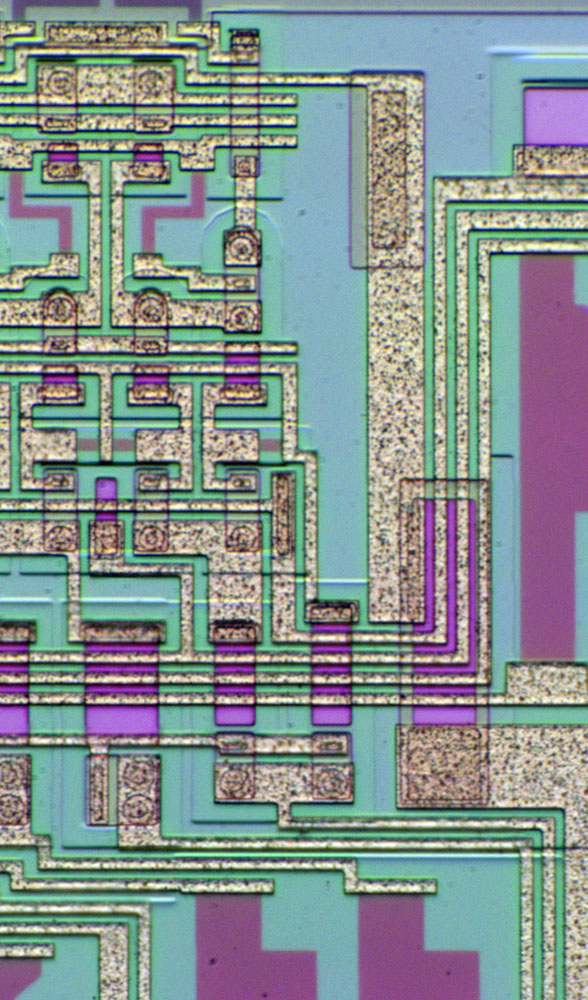

Der eigentliche DAC besteht wie der

DAC80 aus drei 4Bit breiten DACs. Das Verhältnis der

Widerstandswerte im ersten DAC-Block beträgt 0,5:1:2:4 bezogen auf den ganz

links platzierten Referenzwiderstand. Über den Widerständen sind Transistoren

integriert, deren unterschiedlichen Größen (8:4:2:1) dafür sorgen, dass die

Stromdichten in den Transistoren gleich bleiben und sich so die Transistoren

möglichst gleich verhalten.

Der zweite DAC-Block arbeitet mit kleineren

Widerständen, die entsprechend weniger genau eingestellt werden können. Das ist

ausreichend, da der in diesem Block generierte Strom noch einmal herunter geteilt

wird und sich daher Fehler weniger stark auf den Gesamtstrom auswirken. Das

Verhältnis der Widerstände untereinander beträgt aber auch hier 1:2:4:8. Das Flächenverhältnis

der zugehörigen Transistoren liegt bei 8:4:2:1.

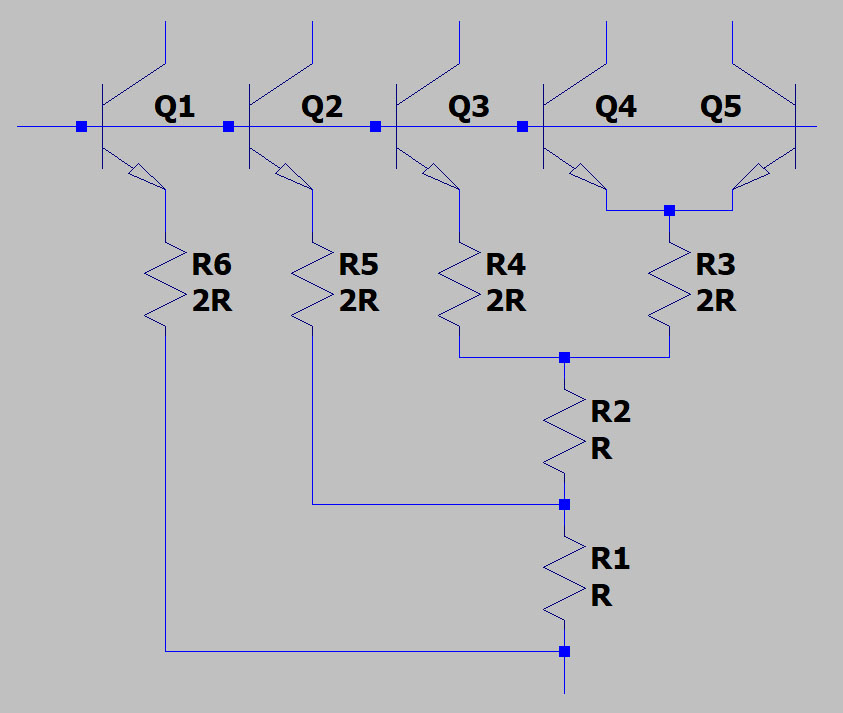

Die Widerstände des dritten DAC-Blocks sind anders

verschalten als die der ersten beiden. Der höchstwertigste Transistor des Blocks

arbeitet lediglich auf einen 2R-Widerstand. Der darauf folgende Transistor

besitzt

am Emitter einen eigenen 2R-Widerstand, der in Serie mit einem R-Widerstand

geschaltet ist. Das Widerstandverhältnis von 1:1,5

alleine würde nicht zum gewünschten Stromverhältnis führen. Durch den zusätzlichen

Widerstand R fließt allerdings zusätzlich der Strom der noch folgenden

Transistoren, so dass sich letztlich doch das gewünschte Verhältnis von 1:2

einstellt. Mit dem dritten Transistor verhält es sich genauso. Der vierte

Transistor fällt allerdings aus der Reihe. Er speist nach seinem 2R-Widerstand

parallel zum dritten Transistor ein. Damit würde sich ein Stromverhältnis von

8:4:2:2 ergeben. Dem letzten Transistor ist allerdings ein zweiter Transistor

parallel geschaltet, der das Verhältnis wieder korrigiert. Dazu später mehr.

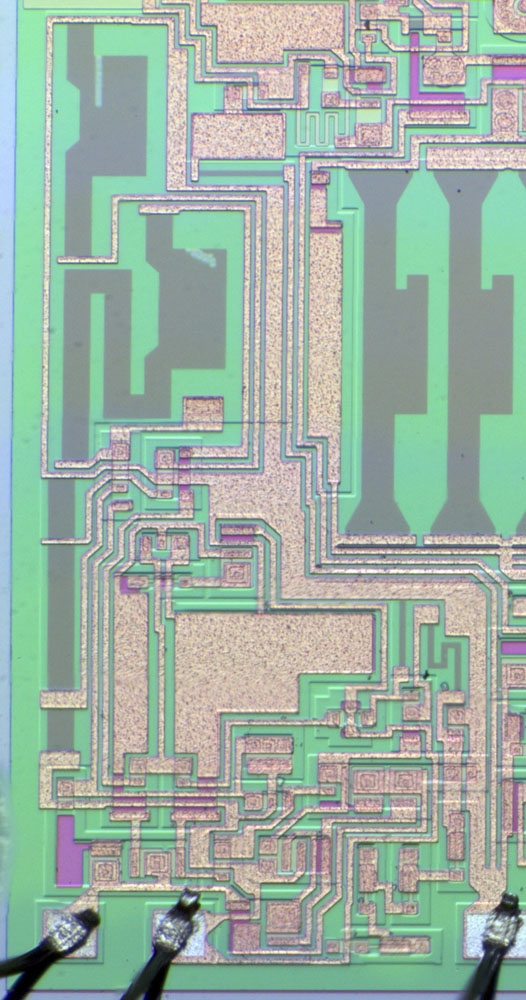

Oberhalb der drei DAC-Blöcke befinden sich Umschalter, die den generierten

Strom des jeweiligen Bits entweder zum Ausgang (grün) oder auf eine

Sammelschiene (rot) leiten. Die Sammelschiene führt zum oberen

PGND-Bezugspotential an der rechten Kante. Die getrennten PGND-Bondpads sollen

vermutlich eine möglichst störungsfreie Ableitung der nicht genutzten Ströme

garantieren. Auf das PGND-Potential beziehen sich zwei Widerstandsteiler.

Außerdem wird das PGND-Potential zusätzlich flächig auf dem Die angebunden, die

genaue Funktion dieser Verbindung erschließt sich allerdings nicht.

Oberhalb der Umschalter befindet

sich die Eingangsbeschaltung für die digitalen Eingänge. Der Bereich, wo sich

die Bondpads für die Digitalsignale befinden ist mit einer dunklen Schicht

hinterlegt. Entweder stellt diese Schicht einen Teil einer kollektive Schutzbeschaltung

dar oder die

dunkle Fläche soll Störungen auf den digitalen Potentialen von den analogen

Schaltungsteilen isolieren. Innerhalb der dunklen Fläche befinden sich die

Eingangswiderstände, die bereits eine gewisse Hürde für Störungen

bilden.

Die drei DAC-Blöcke liefern ihre Ströme getrennt nach rechts, wo sich für die

beiden niederwertigeren DAC-Blöcke Widerstandsteiler befinden (lila). Hinter den

Teilern werden die Ströme zusammengeführt und zum Ausgang geleitet.

In der

rechten unteren Ecke wurden drei abgeglichene Widerstände integriert, über die

der Ausgangsspannungsbereich und der Offset des externen Operationsverstärkers

eingestellt werden kann.

Unterhalb der DAC-Widerstände befindet sich der Operationsverstärker, der den Referenzstrom regelt (lila).

In der linken unteren Ecke ist die Referenzspannungsquelle platziert.

Unterhalb des Operationsverstärkers befindet sich ein freies Bondpad ("SJ"). Dabei handelt es sich um den Summenknoten des Operationsverstärkers, der die Stromsenken des DACs steuert. Dieses Bondpad wird beim AD566A, der mittlerweile obsolet ist, kontaktiert und nach außen geführt. Dafür entfällt beim AD566 die interne Referenzspannungsquelle. Es ist nicht unwahrscheinlich, dass mit dem AD566A Teile verkauft wurden, bei denen die Referenzspannungsquelle nicht innerhalb der Spezifikationen arbeitete und daher nicht genutzt werden konnte.

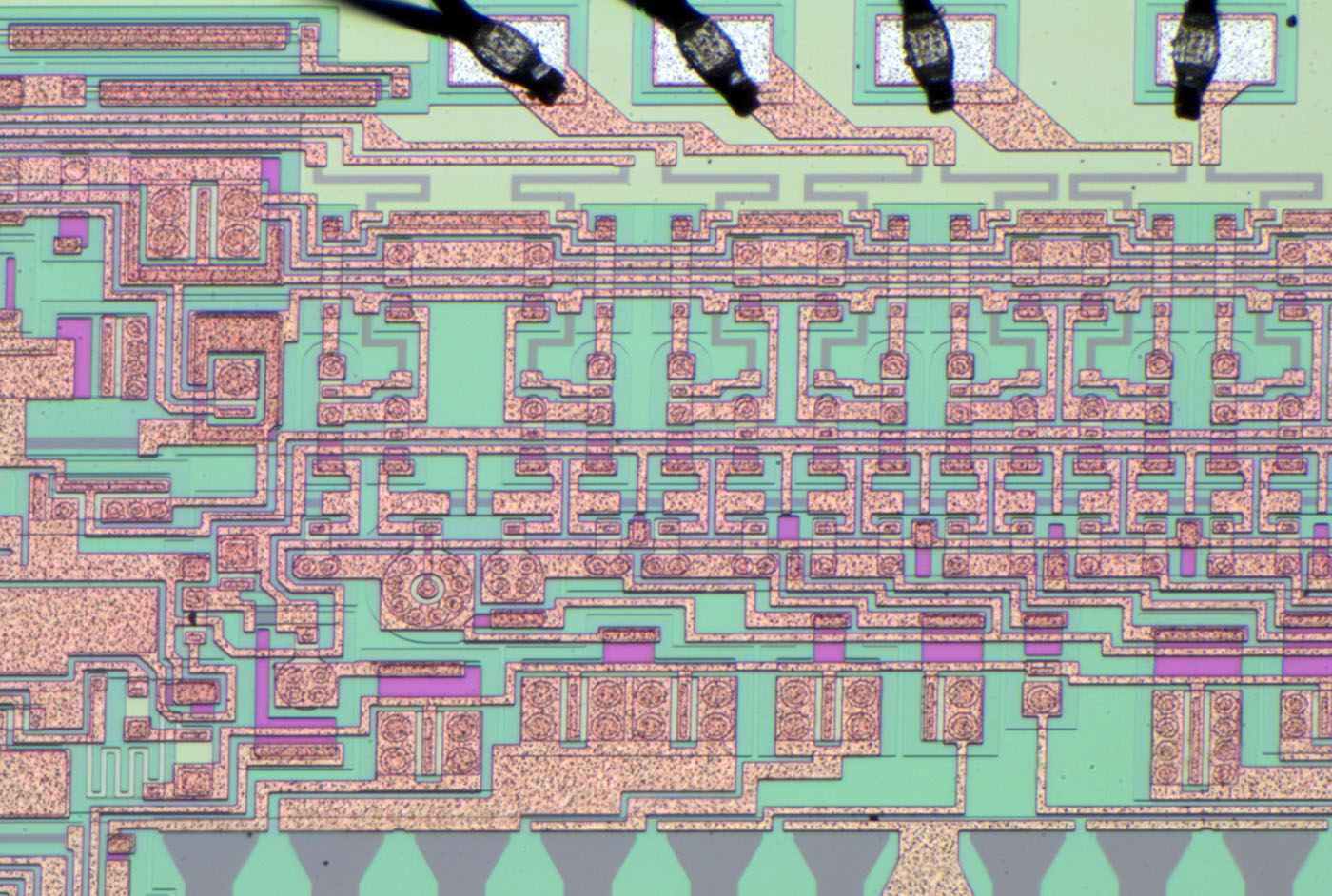

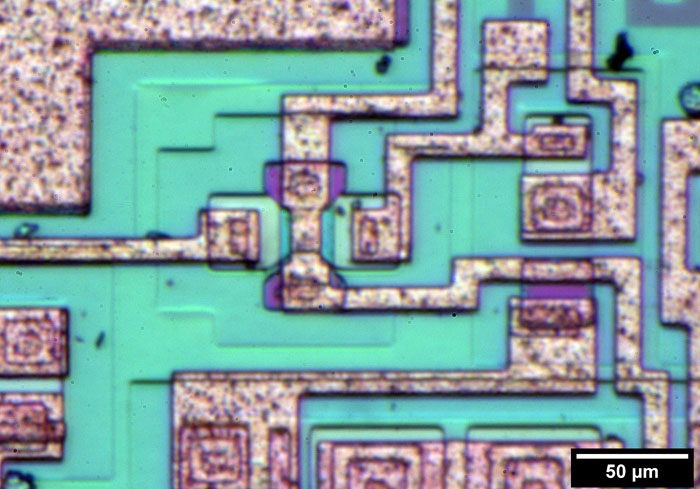

Im Detail sind die Größenverhältnisse der DAC-Transistoren gut zu erkennen. Während der Transistor im Referenzpfad vier Emitter besitzt, arbeitet der Transistor des MSB mit acht Emittern. Darauf folgen ein Transistor mit vier, ein Transistor mit zwei und ein Transistor mit einem Emitter. Daneben ist der erste Transistor des zweiten DAC-Blocks zu sehen, der wieder acht Emitter beinhaltet, die aber etwas kleiner sind.

Für den ersten DAC-Block wurden sogar die zugehörigen Umschalter oberhalb der Stromsenkentransistoren unterschiedlich groß ausgeführt. Das wünschenswerte Flächenverhältnis von 8:4:2:1 weisen allerdings nur die Transistoren auf, die die Ströme zum Ausgang leiten.

Hier noch einmal die vier Transistoren des ersten DAC-Blocks.

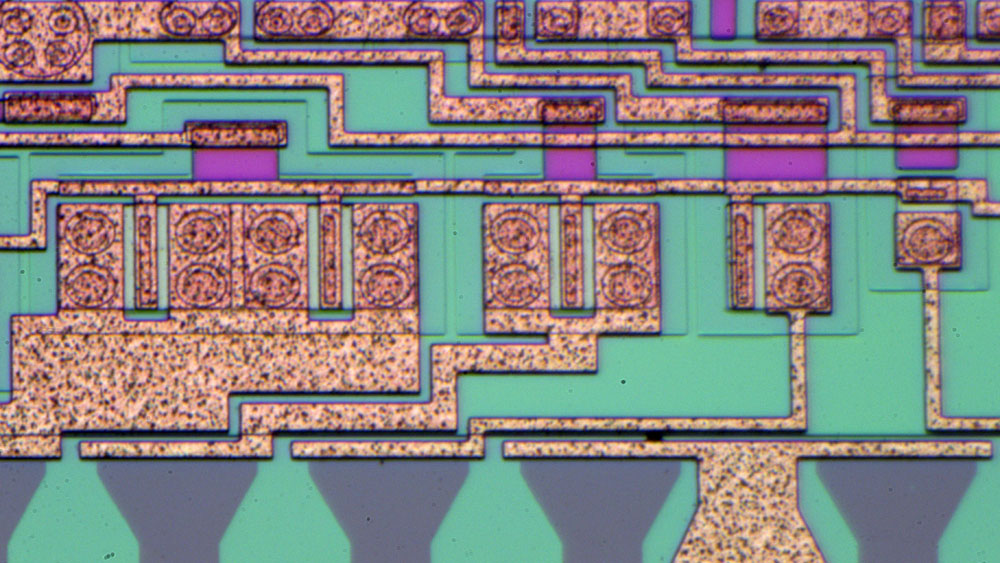

Abgeglichen wurden nur die oberen beiden DAC-Blöcke, die Widerstände des untersten DAC-Blocks zeigen keine Spuren eines Abgleichs. Es ist gut denkbar, dass dieses Widerstandsarray nur bei den enger spezifizierten AD565A-Varianten abgeglichen wird.

Im Detail ist die Paralle- und Seriellschaltung der Widerstände gut zu erkennen. Die Zusammenführung der Ströme an den unteren Anschlüssen der Widerstände erfolgt teilweise sternförmig, damit sich durch eine Stromquelle verursachte Spannungsabfälle nicht auf die anderen Stromquellen auswirken.

Die Stromsenke des LSB passt nicht in die Reihe. Die hier als Q3 und Q4

bezeichneten Transistoren speisen mit ihren 2R-Widerständen in den gleichen

Knoten ein. Diese Verschaltung würde wie weiter oben beschrieben ein Stromverhältnis von 8:4:2:2

erzeugen. Erst durch den Transistor Q5, der dem Transistor Q4 parallel

geschaltet ist, ergibt sich das gewünschte Stromverhältnis von 8:4:2:1. Der

Stromfluss durch den Widerstand R3 teilt sich dabei gleichmäßig auf die beiden

Transistoren Q4/Q5 auf.

Im Widerstandsarray ist der Vorteil der Verschaltung,

dass auf einen Widerstand verzichtet werden konnte. Der durch den Transistor Q5

erzeugte Stromfluss wird in der Umschaltlogik über den Stromsenken genutzt.

Dabei ist natürlich zu beachten, dass keine Störungen in die Stromsenke des LSB

eingespeist werden.

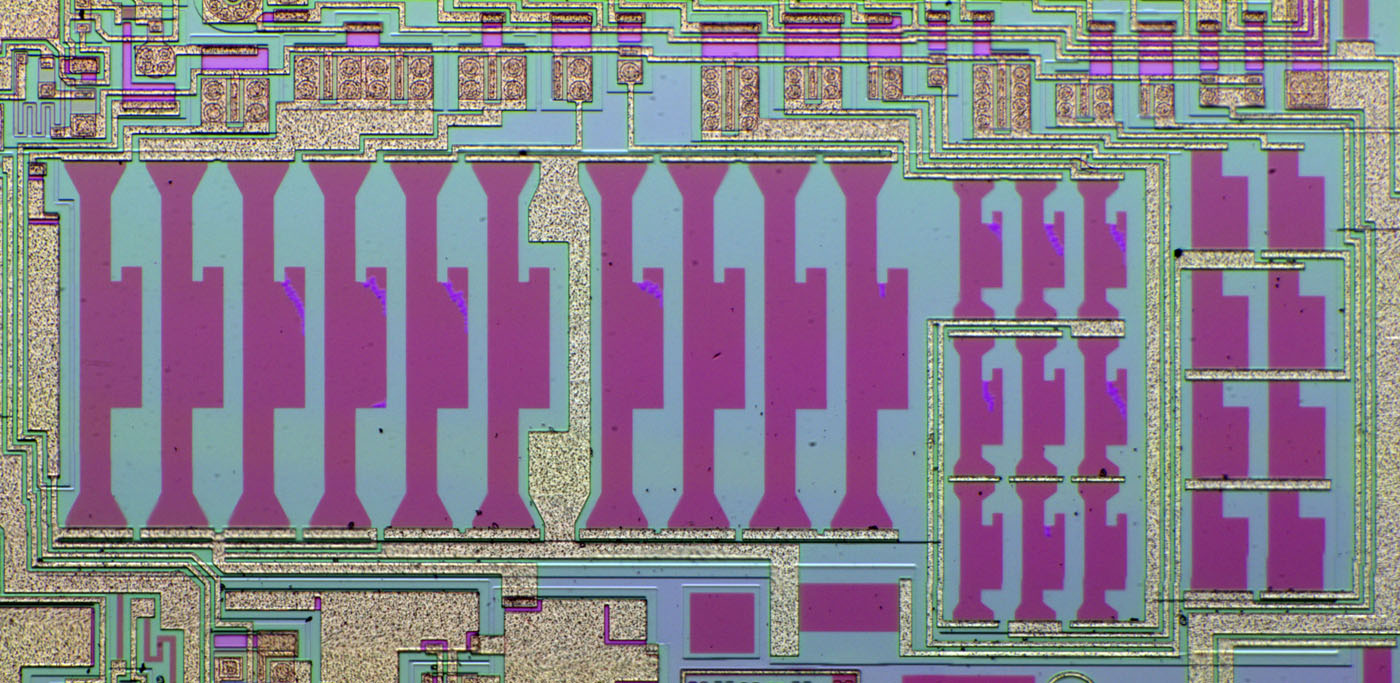

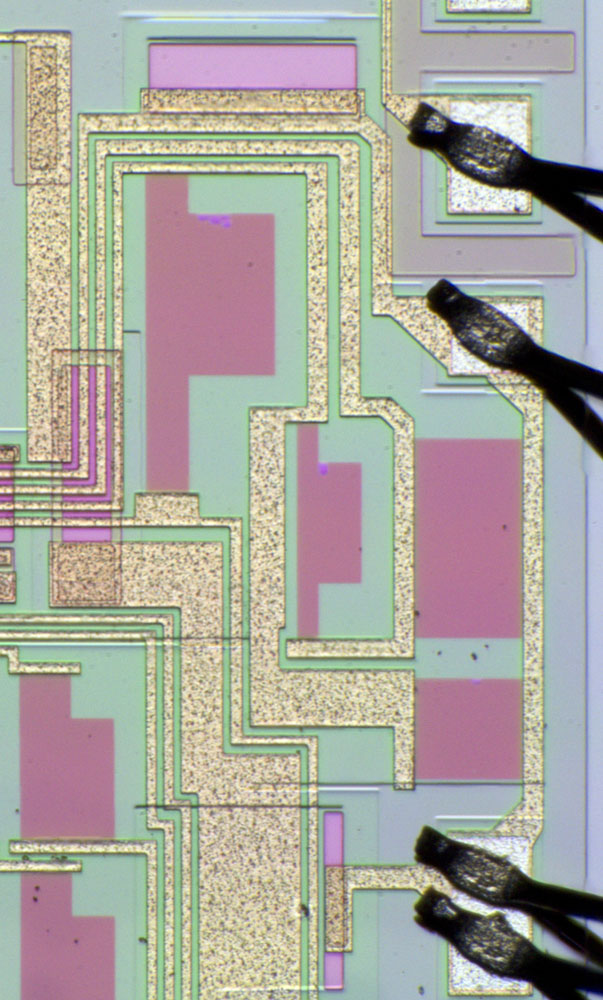

An der unteren Kante des Dies ist der Operationsverstärker platziert, der die Stromsenken steuert. Links befindet sich der Eingang, dessen symmetrische Struktur klar zu erkennen ist. Darüber wurden zwei große Kondensatoren in das Die integriert, die den Frequenzgang des Operationsverstärkers bestimmen. Die Metalllage des rechten Kondensators ist in viele Segmente unterteilt, der linke Kondensator besitzt ein Segment. Durch diesen Aufbau lassen sich die Kapazitäten über eine relativ einfache Modifikation der Metalllage justieren.

Der Operationsverstärker ist anders verschaltet als im Datenblatt dargestellt. Sein Ausgang steuert nicht die Transistoren der Stromsenken, sondern regelt den Stromfluss aus den zugehörigen Widerständen (oben) in das negative Versorgungspotential (rechts), wie es auch beim DAC80 der Fall ist. Durch diesen Aufbau ist der Strom der Stromsenken relativ unabhängig von der Stabilität des negativen Versorgungspotentials.

An der unteren Kante befindet sich ein Widerstand. Am rechten Bondpad trifft das Referenzpotential ein. Das linke Bondpad stellt den Summenknoten dar, der beim AD566 aus dem Gehäuse herausgeführt wird. Vom Summenknoten aus führen sternförmige Leitungen der Metalllage das Potential zum Operationsverstärker und zur Versorgung der Stromsenken.

In der oberen rechten Ecke des Dies befinden sich zwei in Serie geschaltete Widerstandsteiler, die die Ströme der unteren beiden DAC-Blöcke so anpassen, dass sich über die 12 Bit die gewünschte Abstufung ergibt. Den Transistorflächen nach zu urteilen erzeugen die unteren beiden DAC-Blöcke die gleichen Ströme. Der untere Widerstandsteiler dürfte daher einen Teilefaktor von 1:16 darstellen. Der obere Widerstandsteiler könnte, abhängig vom Verhältnis der Ströme zwischen dem oberen und dem mittleren DAC, auch ein anderes Verhältnis einstellen.

In der linken unteren Ecke des Dies befindet sich die Referenzspannungsquelle, die eine relativ große Fläche einnimmt. Im Gegensatz zu anderen Digital-Analog-Konvertern wie dem DAC80 befindet sich dort nicht nur eine Z-Diode als grundlegende Referenzspannungsquelle, sondern auch ein Operationsverstärker, der aus der stabilen, aber nicht genau spezifizierten Spannung einer Z-Diode genau spezifizierte 10V erzeugt.

Im oberen Bereich befinden sich zwei relativ große, abgeglichene Widerstände. Wahrscheinlich definiert ein Widerstand die Ausgangsspannung, während der andere es ermöglicht den Temperaturkoeffizienten auf einen möglichst niedrigen Wert einzustellen.

Die Z-Diode ist eine buried Z-Diode mit einer entsprechend guten Stabilität. Die Bauform scheint typisch für Analog Devices gewesen zu sein, das sie auch in den Referenzspannungsquellen AD587 und AD588 zu finden sind.