Der AD679 ist ein von Analog Devices entwickelter Analog-Digital-Wandler, der 128kS Digitalwandlungen mit einer Auflösung von 14Bit ermöglicht. Bei den Indizes K, B und T werden alle AC und DC Parameter nach der Produktion getestet. Bei den Indizes A, J und S werden nur die AC Parameter getestet und sie sind etwas schlechter spezifiziert. Der Index K bietet die besten Spezifikationen der Varianten K, B und T. Ein Grund dürfte der eingeschränkte Temperaturbereich von 0°C bis 70°C sein. Der AD679T kann dagegen in einem sehr weiten Temperaturbereich von -55°C bis +125°C eingesetzt werden. Für den Index K garantiert Analog Devices über den kompletten Temperaturbereich (0°C-70°C) unter anderem folgende Spezifikationen:

Nichtlinearität: +/-1LSB typ. +/-2,5LSB max.

Offset: 0,04%FSR typ. 0,05%FSR

max.

Verstärkungsfehler: 0,09%FSR typ. 0,11%FSR max.

Referenzspannung:

4,98V - 5,02V

SNR bei einem Eingangspegel von -0,5dB: 78dB min. 81dB typ.

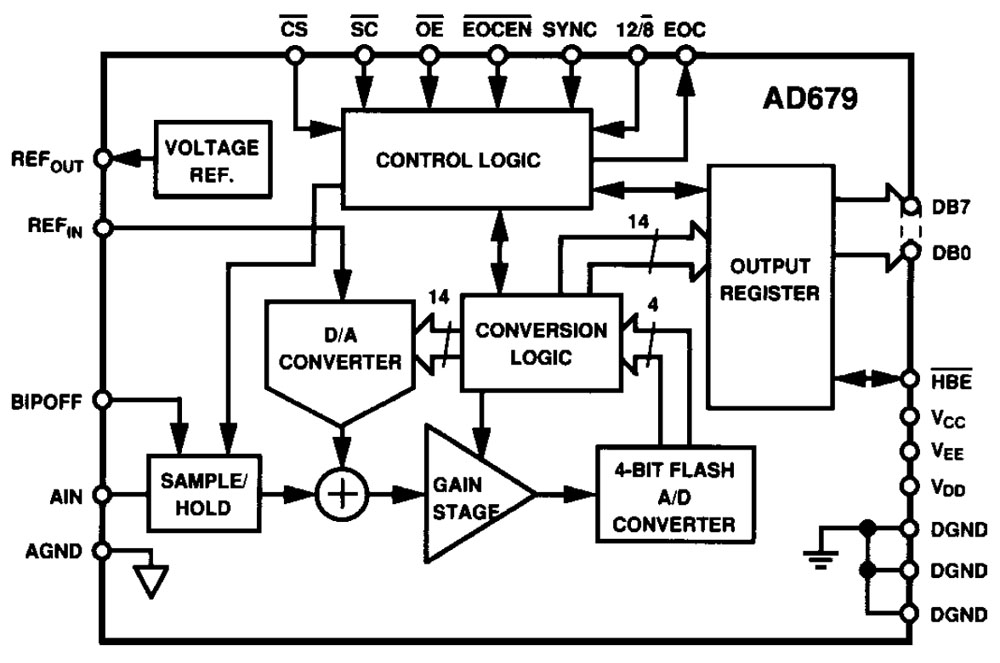

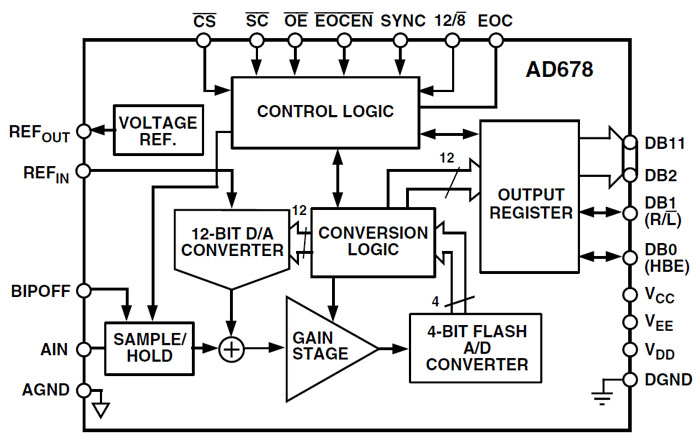

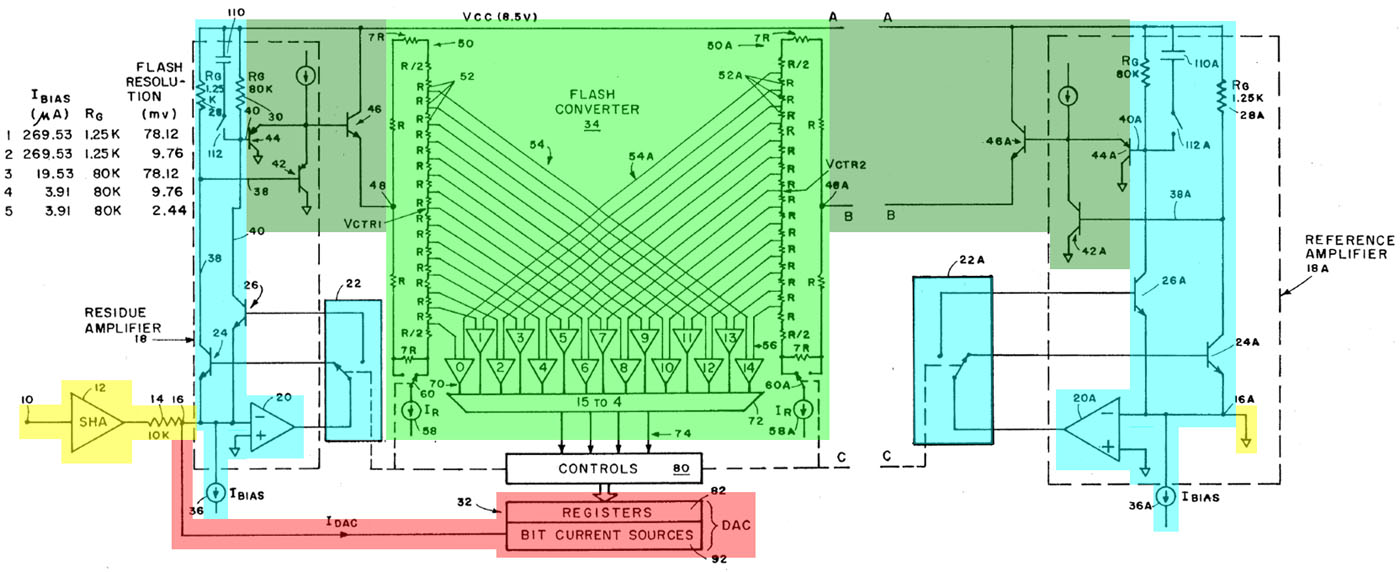

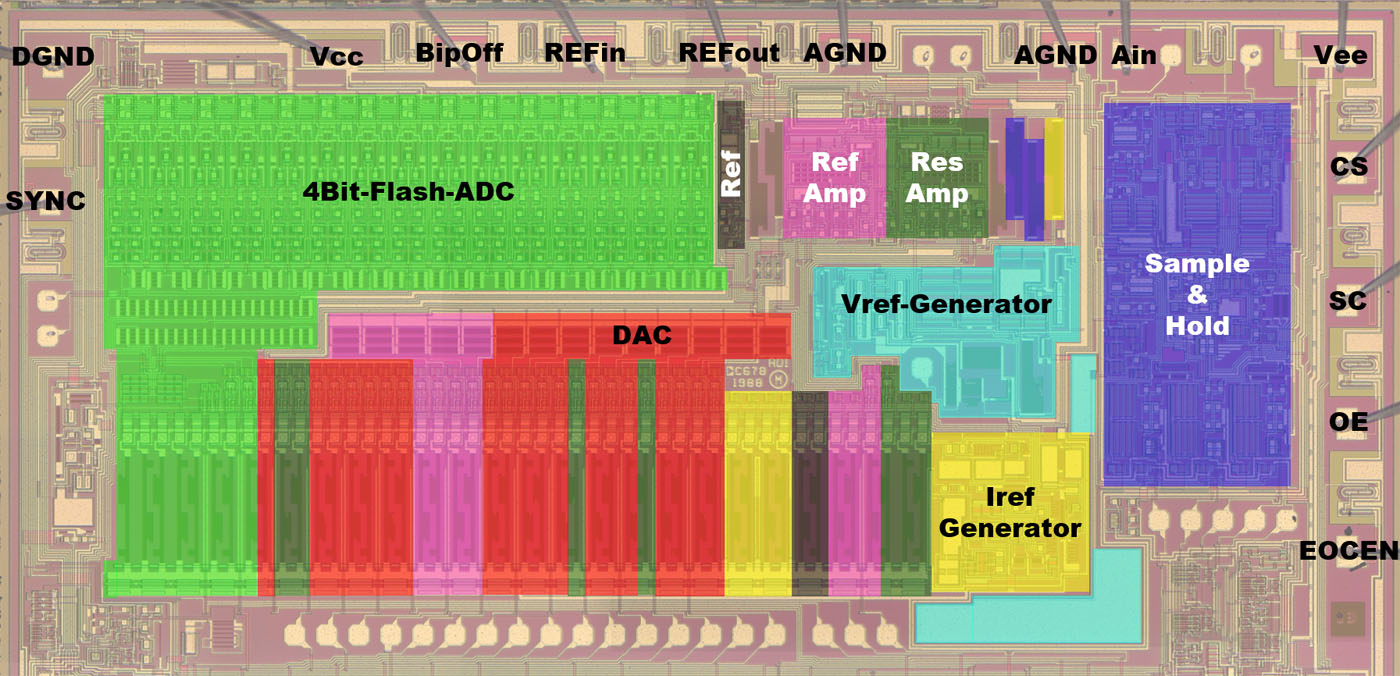

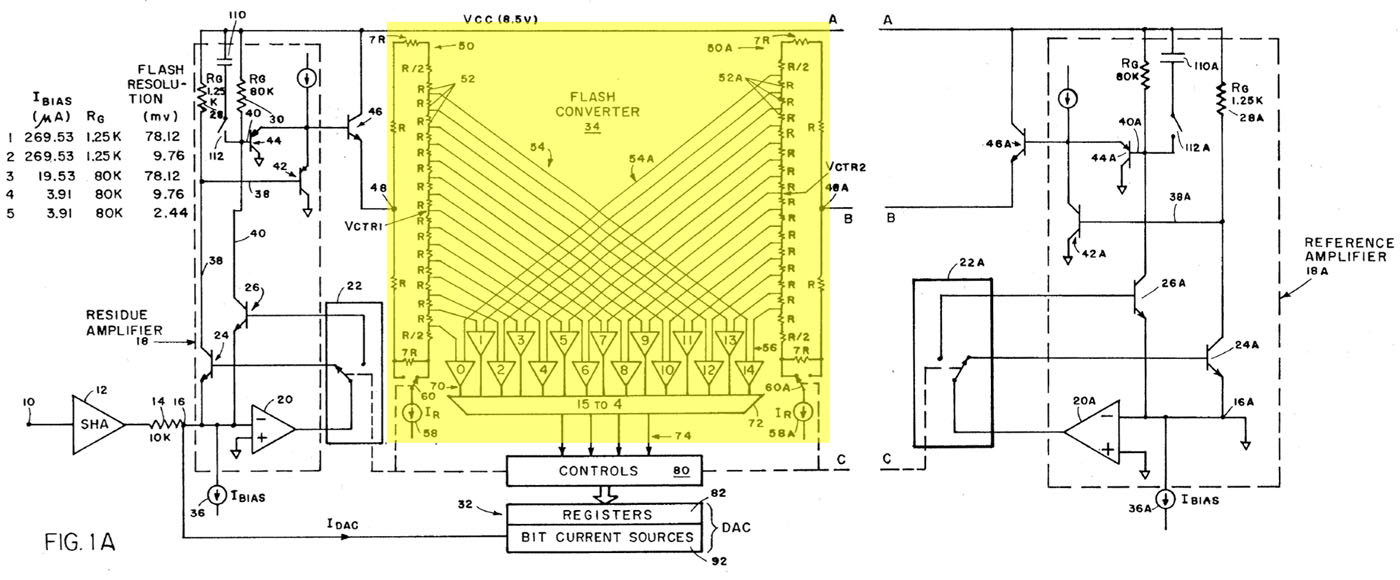

Wie das Blockschaltbild im Datenblatt des AD679 zeigt, beinhaltet der Baustein alle notwendigen Schaltungsteile, um einen Analogwert in einen Digitalwert zu wandeln. Das analoge Eingangssignal durchläuft zuerst eine Sample&Hold-Stufe, die einen Eingangswiderstand von 10MΩ und eine Eingangskapazität von 10pF garantiert. Bis zu einer Frequenz von 500kHz beträgt die Dämpfung des Eingangssignals maximal -0,1dB, so dass auch Frequenzen oberhalb der Arbeitsfrequenz des Analog-Digital-Wandlers abgetastet werden können. Dem Schaltbild nach ist der Offset-Eingang, der es ermöglicht den Eingangsspannungsbereich von 0-10V auf +/-5V zu verschieben, an die Sample&Hold-Stufe angebunden.

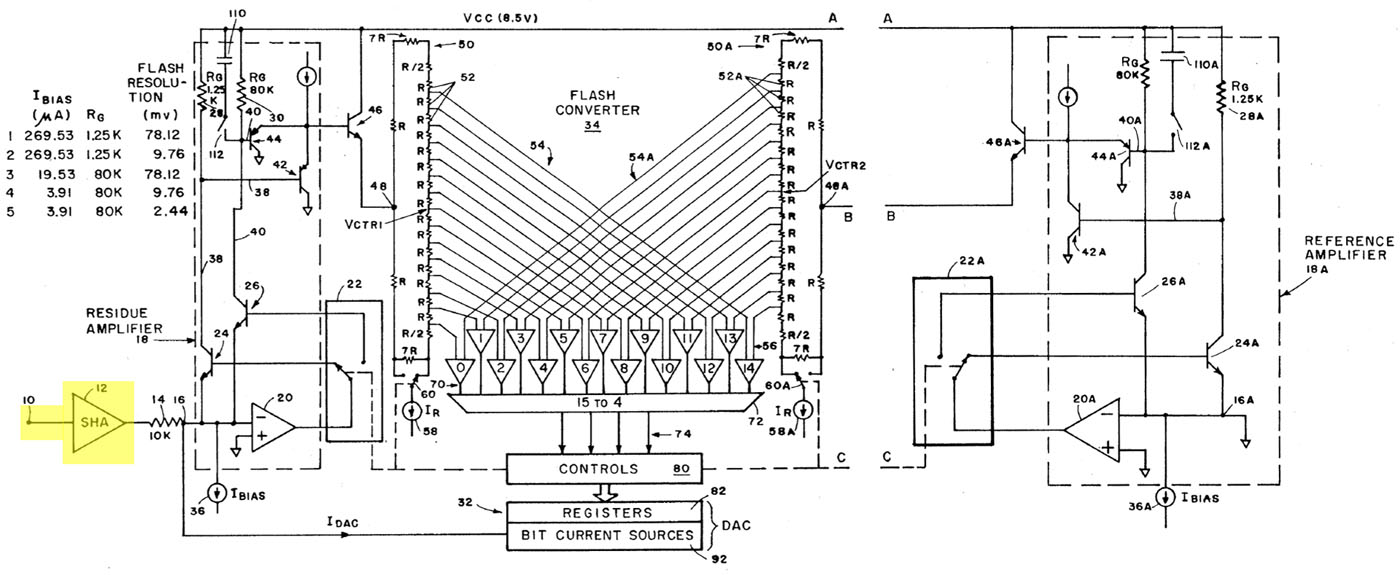

Der Analog-Digital-Wandler arbeitet nach dem SAR-Prinzip ("Successive Approximation Register"). Das aufbereitete Eingangssignal wird mit dem Strom eines 14Bit-Digital-Analog-Wandlers überlagert und dann das Ergebnis bestimmt. Im einfachsten Fall erfolgt die Auswertung wie beim ADC574 über einen Komparator. Bis das Ergebnis der Wandlung bereits steht, müssen dann alle Bits des DACs einmal geschaltet werden. Dazu kommen die Einschwingzeiten und die Auswertung über den Komparator und die Steuerlogik. Im AD679 ist die Auswertung der gebildeten Summe komplexer ausgeführt. Statt einem Komparator kommt hier ein schneller Flash-ADC mit einer Auflösung von 4Bit zum Einsatz. In Kombination mit einer davor platzierten, konfigurierbaren Verstärkerstufe reichen so fünf Zyklen, um das Eingangssignal mit einer Auflösung von 14Bit zu digitalisieren. Diese Architektur nennt man Subrangig-ADC und wird im Tutorial MT-024 von Analog Devices ausführlich beschrieben.

Der AD679 enthält außerdem eine Referenzspannungsquelle und ein Ausgangsregister. Das Blockschaltbild zeigt mit dem Anschluss 12/8 eine Schnittstelle, die im Pinning nicht auftaucht und auch so im Datenblatt nicht erwähnt wird. Der analoge Schaltungsteil wird mit +/-12V, der digitale Schaltungsteil mit 5V versorgt. Neben drei digitalen Masseanschlüssen bietet der AD679 eine dediziertes analoges Massepotential. Die Leistungsaufnahme liegt typischerweise bei 560mW.

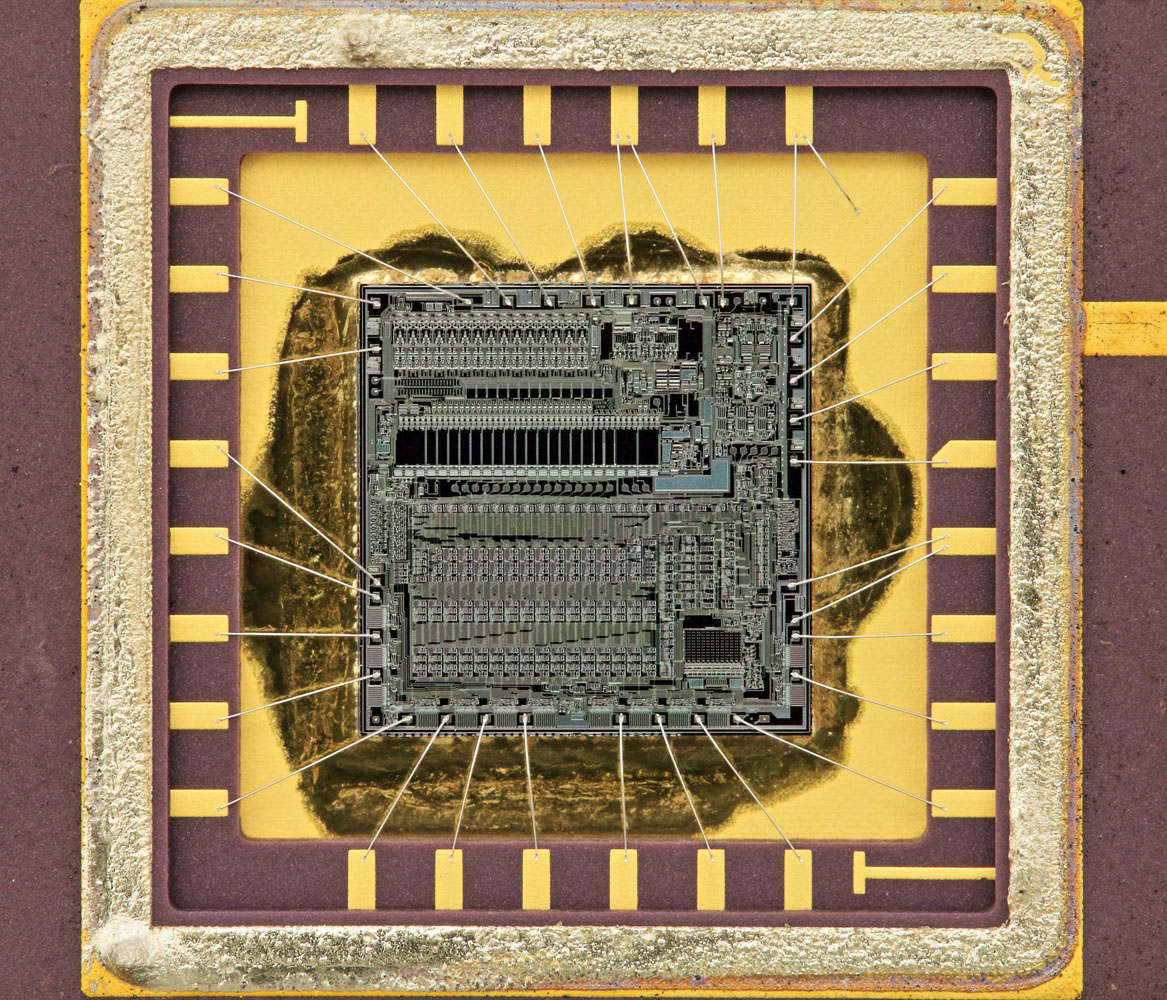

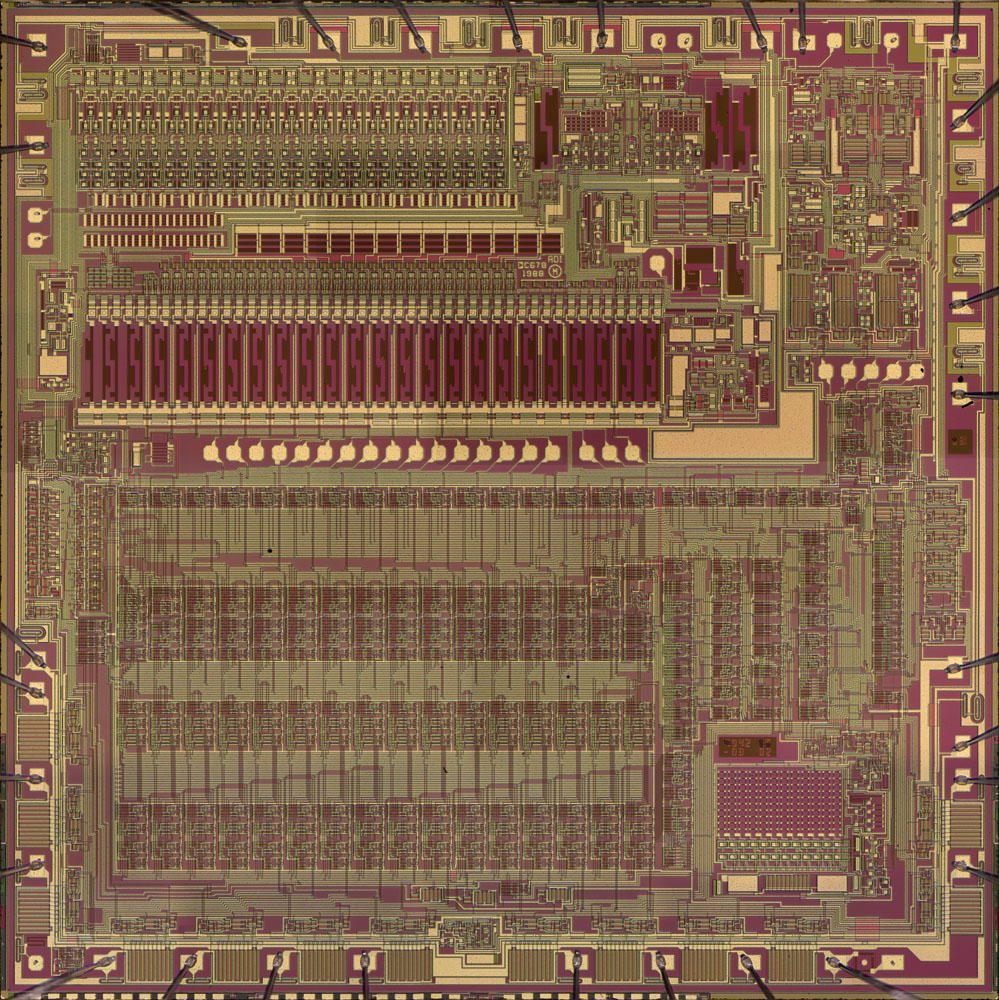

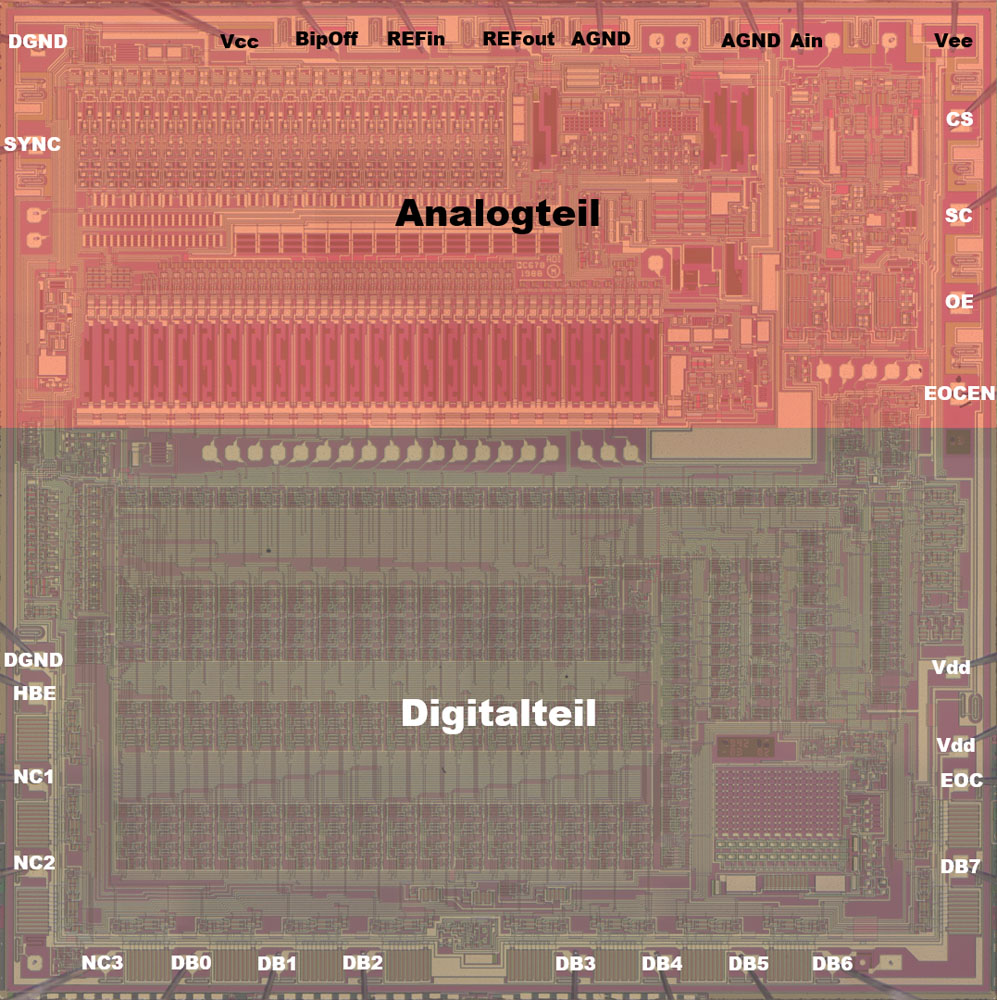

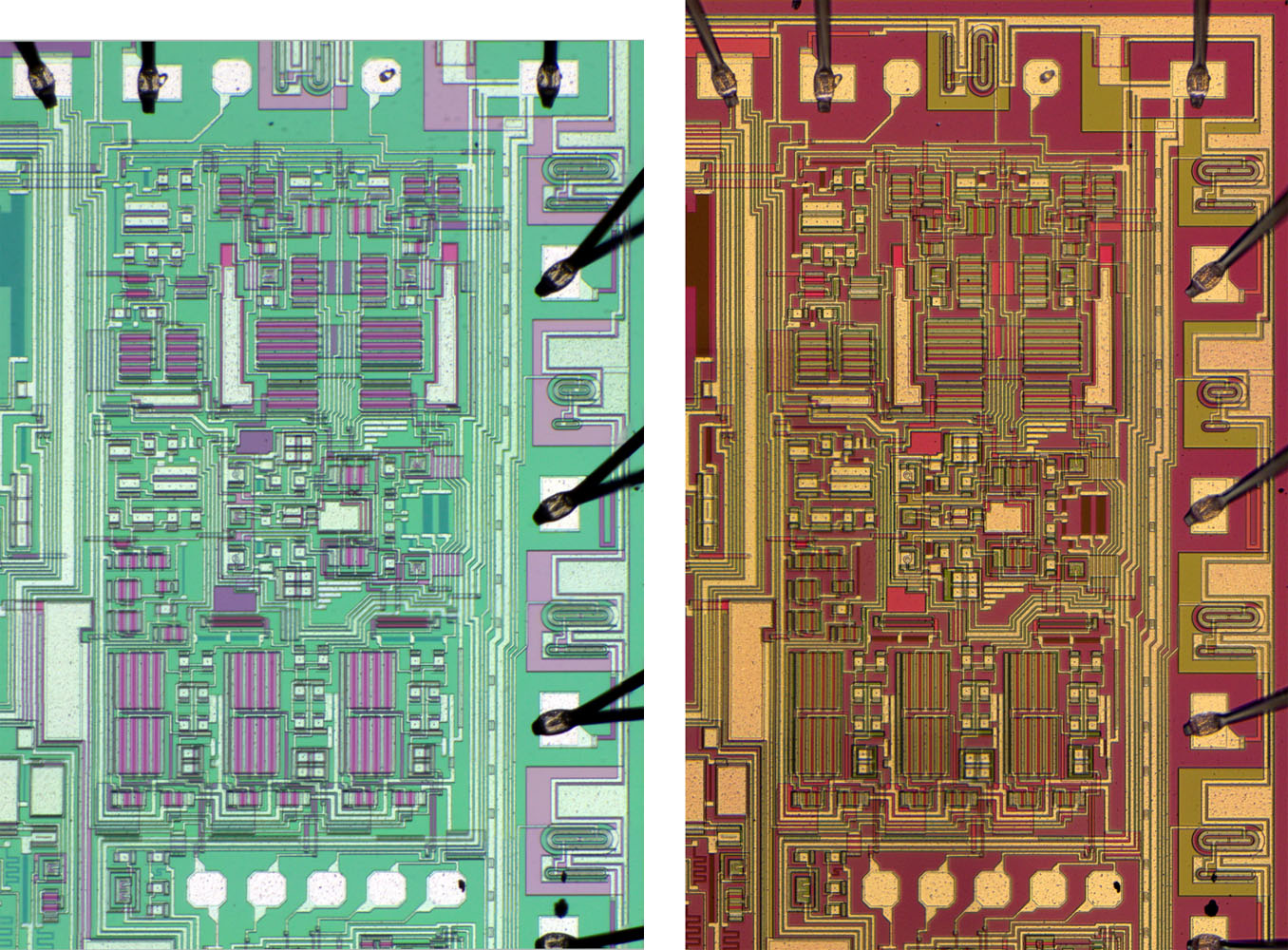

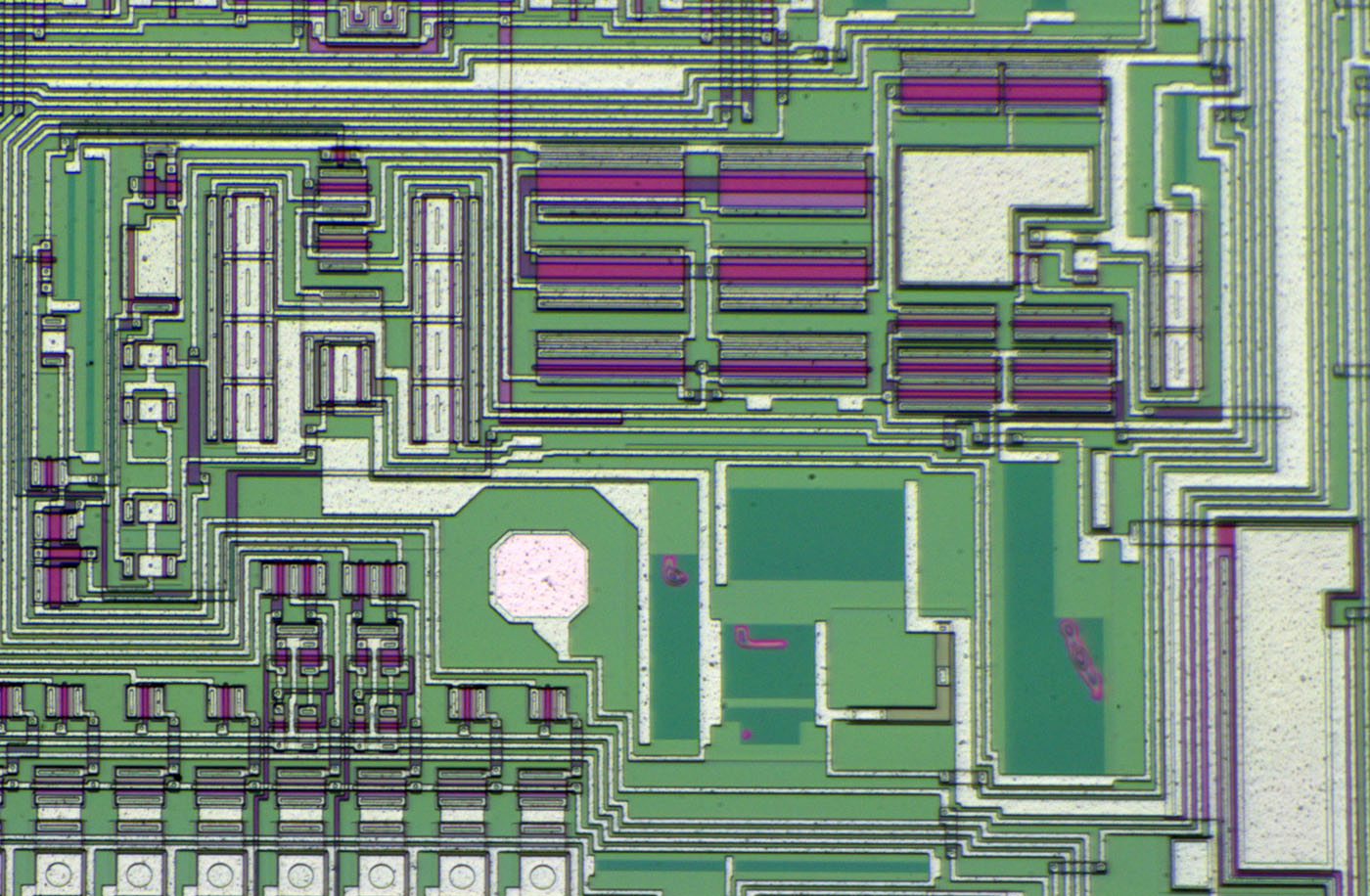

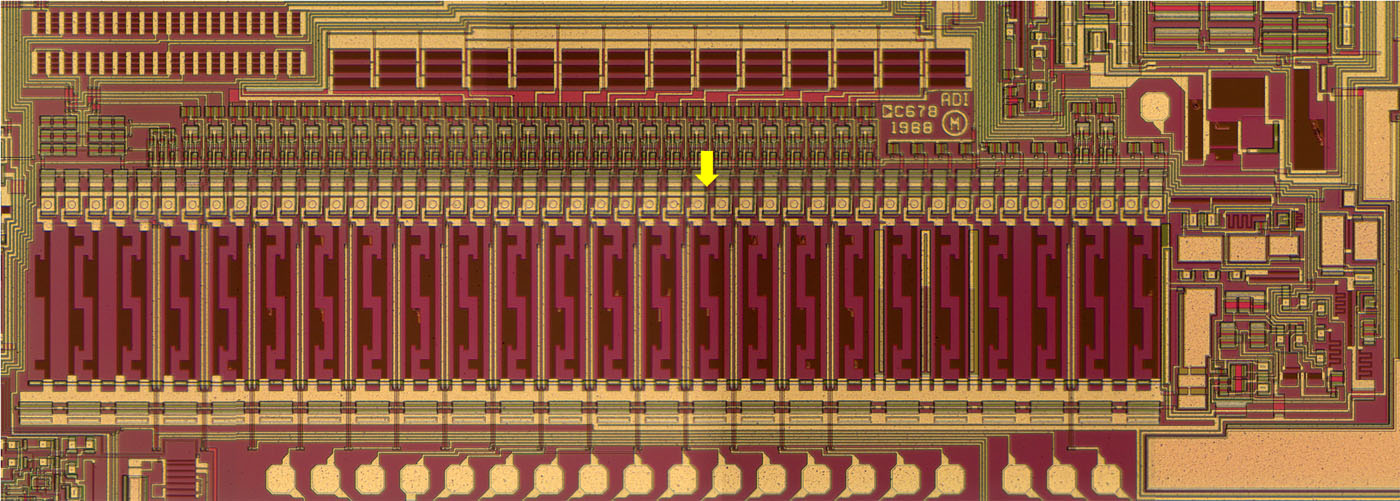

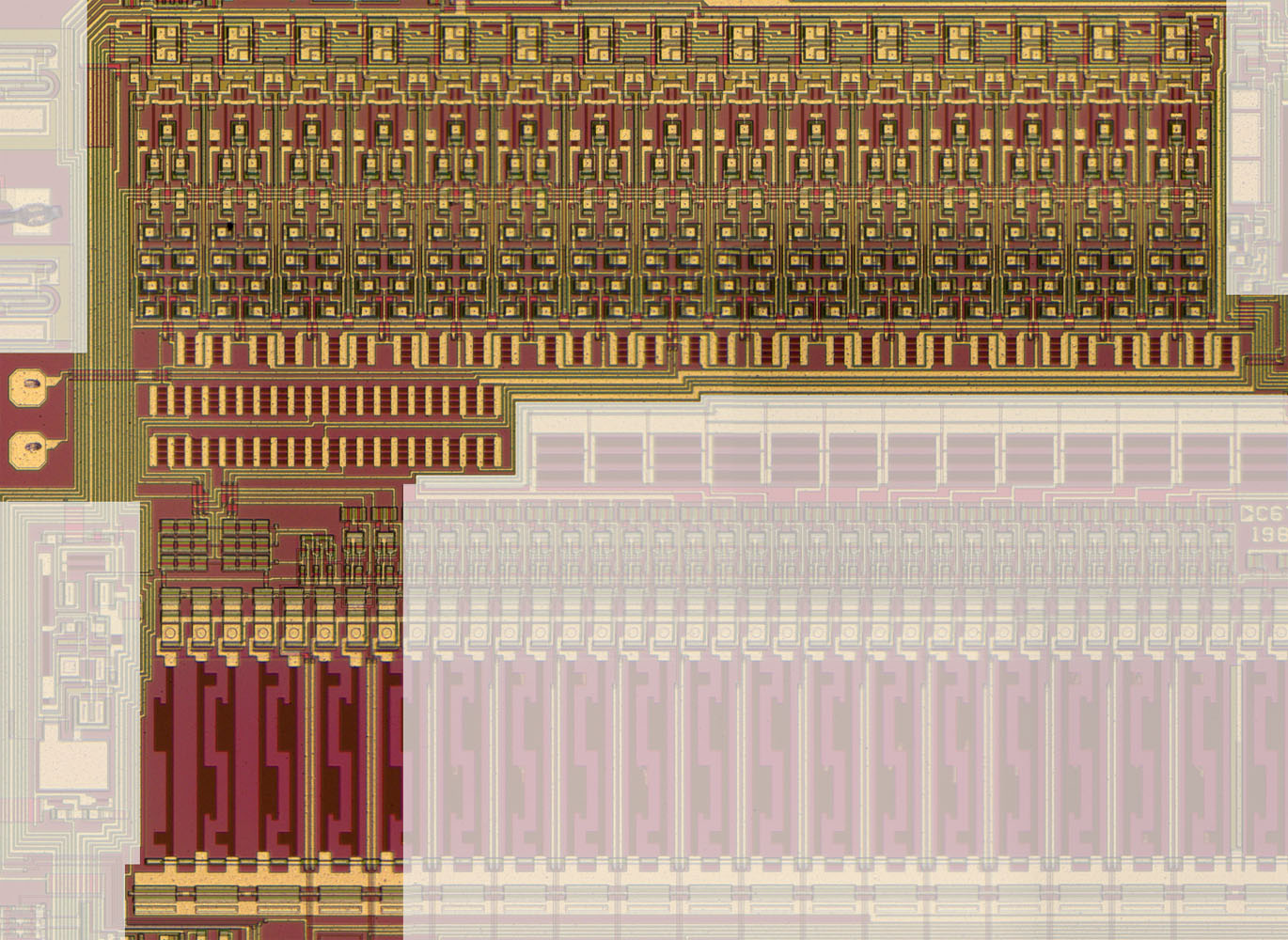

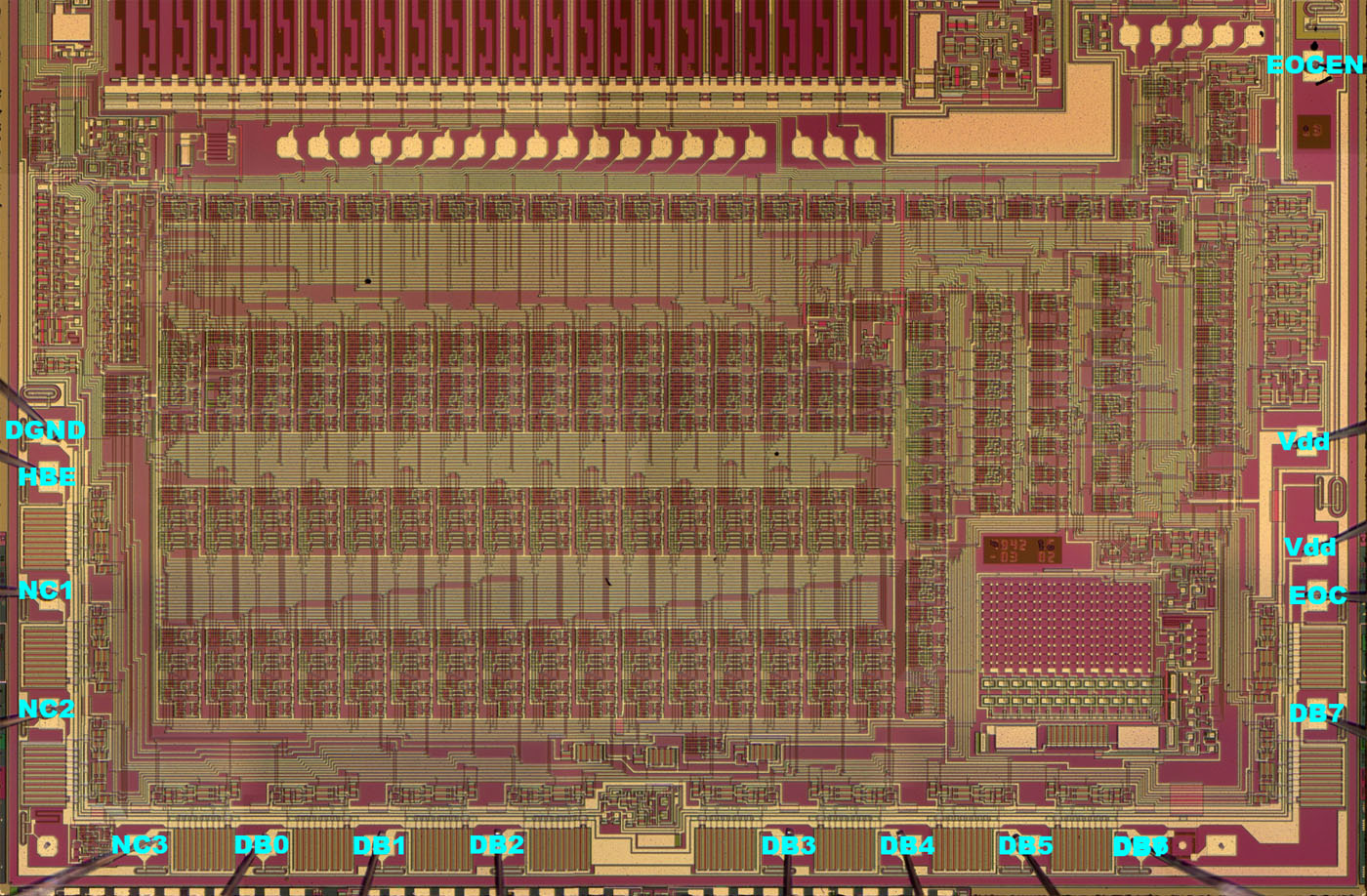

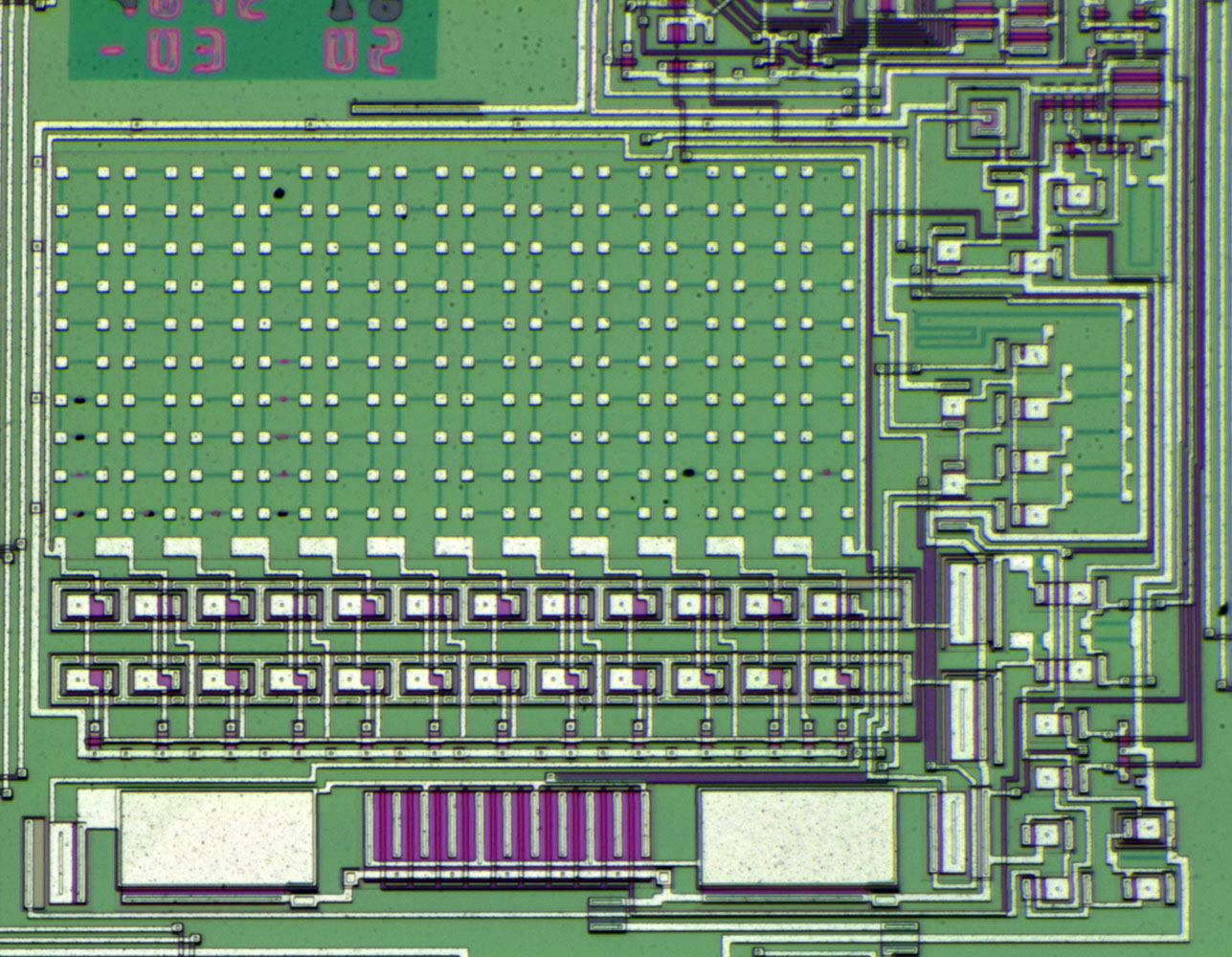

Mit einer Kantenlänge von 6,5mm ist das Die sehr groß.

Der analoge Schaltungsteil nimmt nicht ganz die Hälfte der Fläche ein.

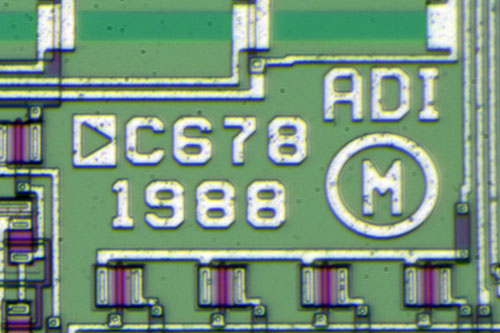

Das Design stammt aus dem Jahr 1988 und trägt die Bezeichnung C678. Das zeigt, dass es sich bei AD678 und AD679 im Grunde um dieselben Analog-Digital-Wandler handelt. Die Spezifikationen sind entsprechend sehr ähnlich. Während der AD679 14Bit mit einer Geschwindigkeit von 128kS/s darstellen kann, bietet der AD678 nur eine Auflösung von 12Bit, die dafür mit 200kS/s abgegriffen werden kann.

Hier zeigt sich auch, woher der beim Blockschaltbild des AD679 fälschlicherweise eingezeichnete 12/8-Pin rührt. Der AD678 bietet alternativ zum 8Bit breiten Ausgang eine 12Bit breite Schnittstelle, die sich über den 12/8-Pin aktivieren lässt.

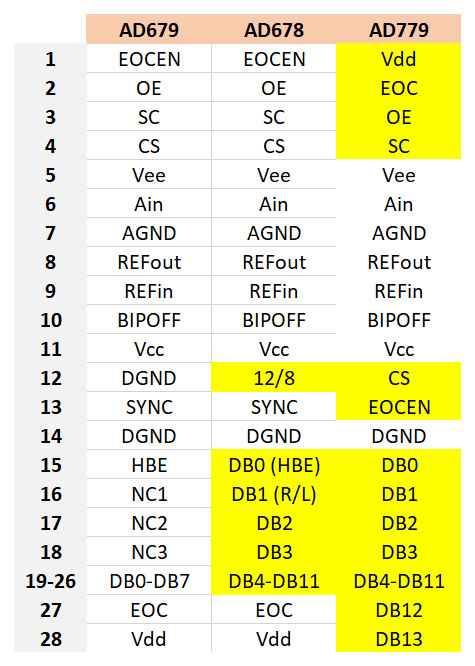

Ein Vergleich des Pinnings lässt eine grundsätzliche Pinkompatibilität zwischen dem AD679 und dem AD678 erkennen. Man könnte vermuten, dass es sich auch beim AD779 um den gleichen Baustein handelt. Der AD779 ist nicht pinkompatibel, besitzt aber ansonsten die gleichen Spezifikationen wie der AD679. Das AD779-Blockschaltbild zeigt die selbe Funktionsweise. Im Fall des AD779 ist allerdings ein 14Bit breiter Datenbus aus dem Gehäuse herausgeführt. Wie sich noch zeigen wird, bietet das AD678-Die nicht genug Ausgangstreiber, um 14Bit direkt darstellen zu können. Der AD779 muss folglich auf einem anderen Die basieren.

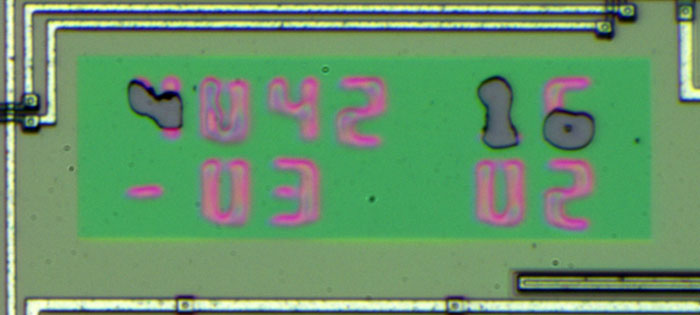

Auf dem Die wurden mehrere Widerstände mit einem Laser abgeglichen. In zwei Flächen finden sich diverse Zahlen. Es könnte sich dabei um Qualitätsstufen handeln. Vielleicht dienen die Zahlen auch der Rückverfolgbarkeit des Bauteils und des Abgleichprozesses. An mehreren Stellen scheint sich dabei die Passivierungsschicht aufgelöst zu haben.

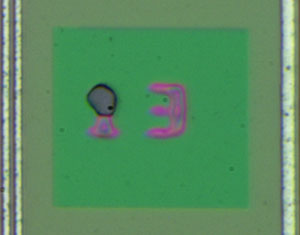

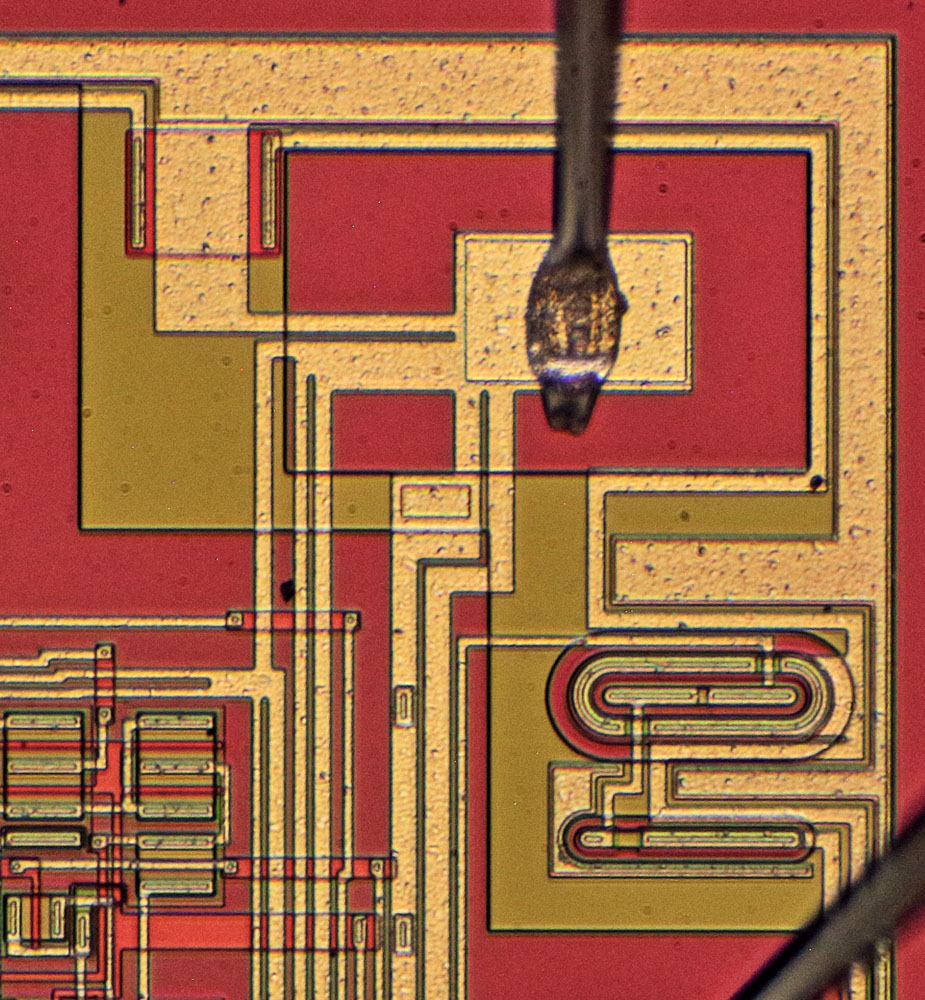

Am Bondpad DB6 befindet sich ein Quadrat aus dem abgleichbaren Widerstandsmaterial und ein Testpad. In Schaltkreisen, die nach der Produktion mit einem Laser abgeglichen werden, ist eine derartige Struktur üblich. Sie ermöglicht einen Abgleich des Lasers.

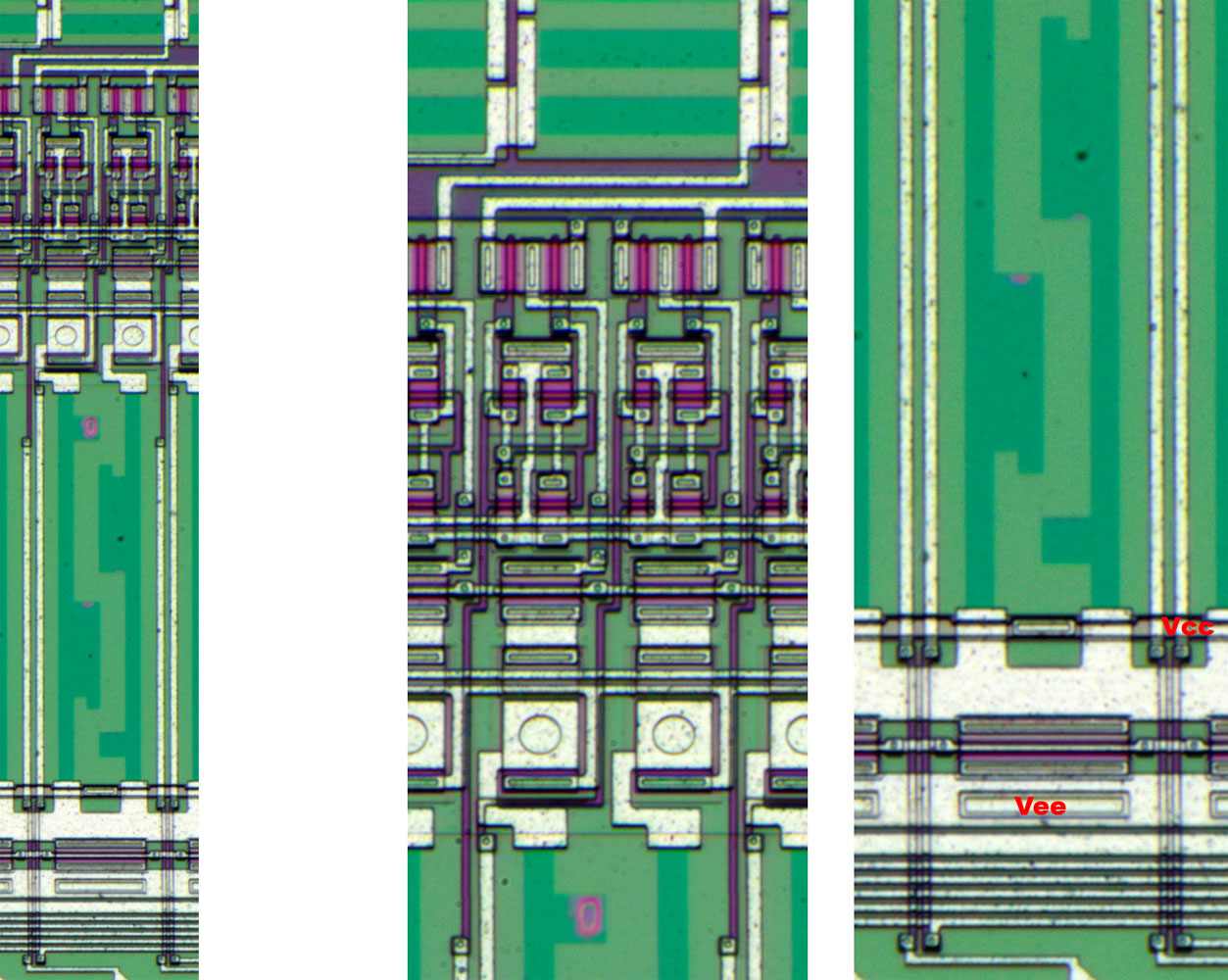

Sensible Potentiale, wie hier das negative Versorgungspotential Vee, werden sternförmig verteilt. Teilweise befinden sich in den abgehenden Leitungen weitere Sternpunkte.

Jedem Eingang ist eine Schutzstruktur zugeordnet. Auf einen Widerstand zur Strombegrenzung folgen zwei Dioden, die das Eingangssignal auf den Versorgungsspannungsbereich begrenzen. Bemerkenswert sind die kurzen Unterbrechungen der Metalllage innerhalb der Dioden. Anscheinend soll diese Maßnahme den Stromfluss durch das Silizium zwingen, so dass Über- und Unterspannungen möglichst effizient abgeleitet werden.

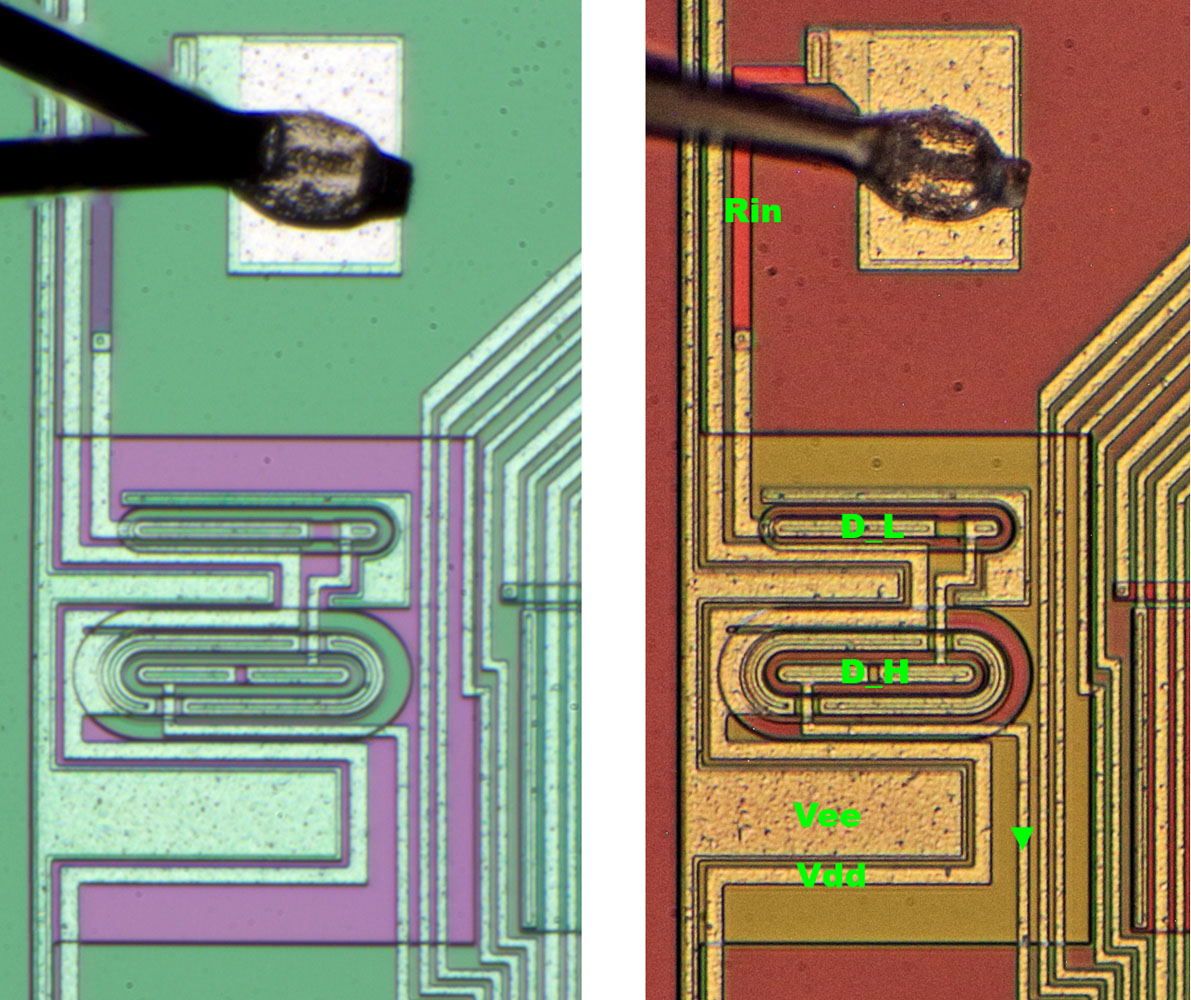

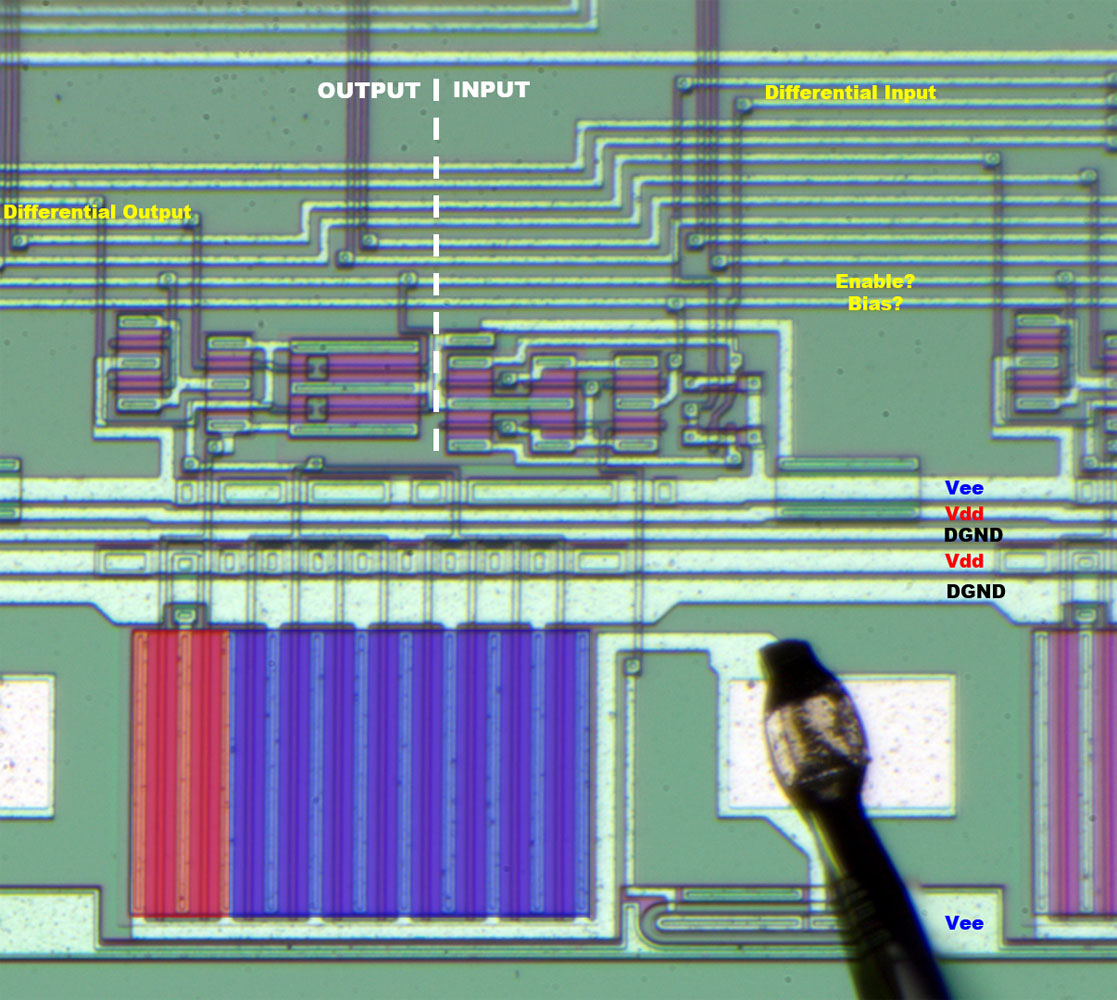

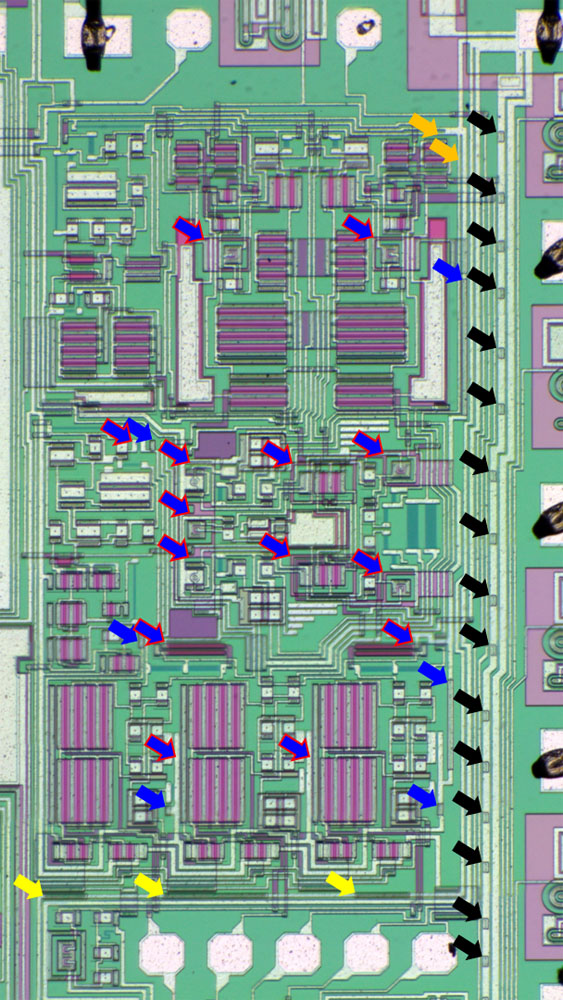

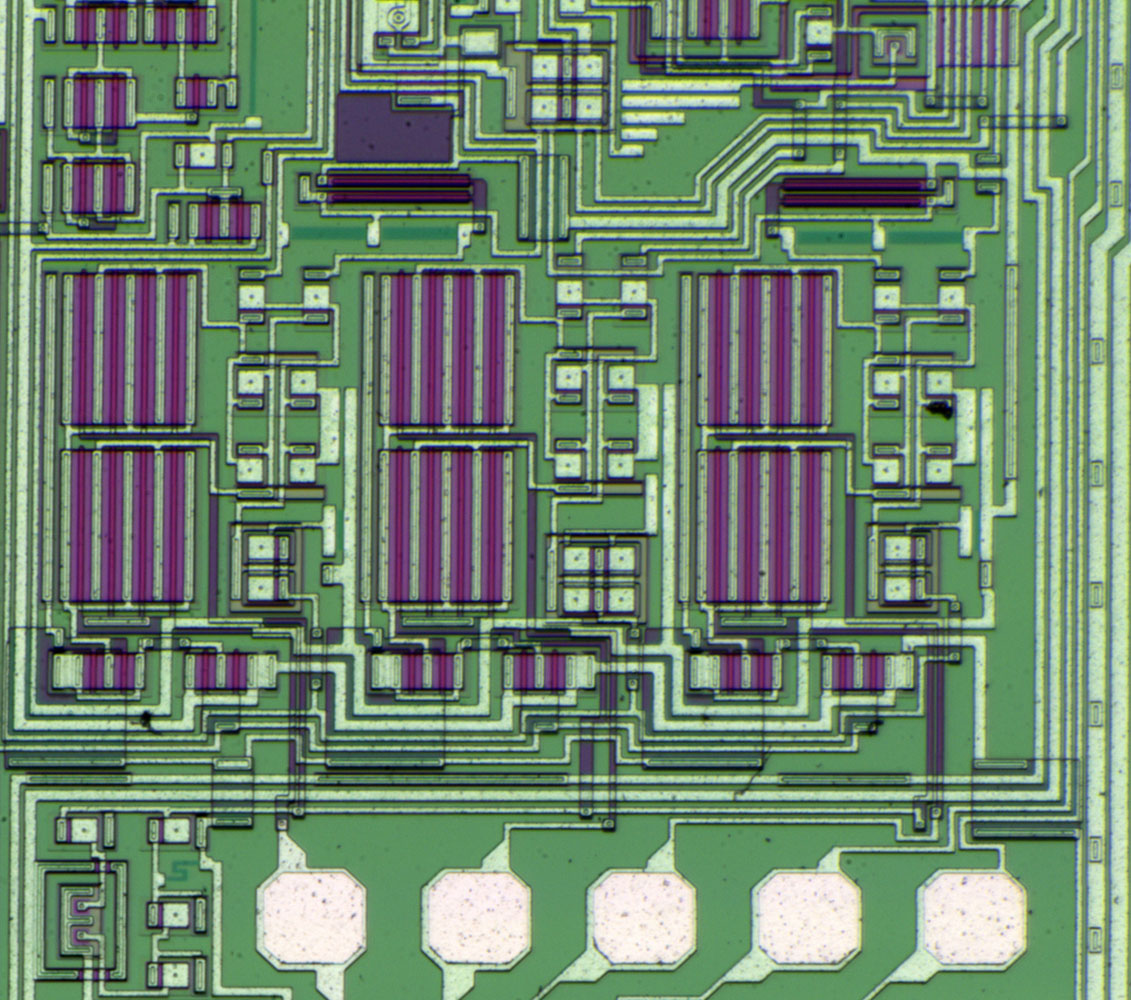

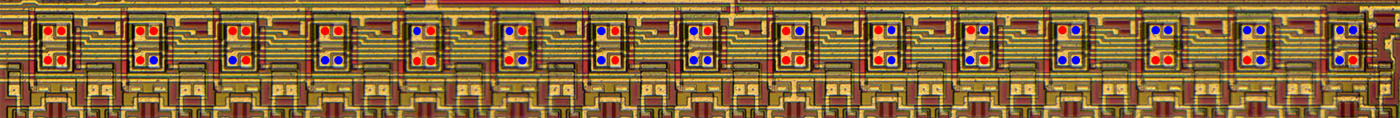

Im unteren Bereich des Dies befinden sich die Ausgänge des AD679. Sie sind gut durch ihre großen Leistungstransistoren zu erkennen. Es zeigt sich, dass nur 13 Ausgänge integriert wurden. Neben dem EOC-Signal (End Of Conversion) bleiben zwölf Ausgänge für den Datenbus. Das bedeutet, dass mit diesem Die nicht ohne Weiteres der AD779 mit seiner 14Bit breiten digitalen Schnittstelle dargestellt werden kann.

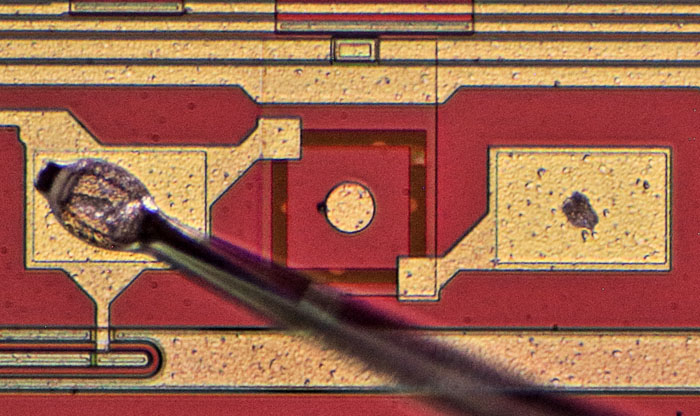

Im Detail betrachtet zeigt sich, dass es sich um eine Push-Pull-Ausgangsstufe handelt, die mit einem kleinen Highside-Transistor (rot) und einem großen Lowside-Transistor (blau) arbeitet. Oberhalb des Transistors verlaufen mehrere Versorgungsleitungen, so dass für die Endstufen eine vom Rest abgesetzte Versorgung zur Verfügung steht. Unterhalb des Bondpads befindet sich eine Schutzdiode mit Bezug auf Vee (-12V). Ein Schutz vor zu hohen Potentialen ist auf den ersten Blick nicht zu erkennen. Wahrscheinlich sind die vielen Durchkontaktierungen in der unteren Vdd-Leitung (5V) der Pfad, über den zu hohe Potentiale abgeleitet werden.

Bei genauerer Betrachtung der über den Leistungstransistoren liegenden Steuerschaltung zeigt sich, dass die Bondpads auch als Eingang dienen. Von links trifft das differentielle Ausgangssignal ein, dass im linken Bereich der Steuerschaltung verarbeitet wird. Ein weiteres Potential scheint eine Art Enable-Funktion zu übernehmen. Der rechte Bereich nimmt das Potential des Bondpads von der Vee-Schutzdiode entgegen. Nach einer Aufbereitung liefert die Steuerschaltung ein differentielles Eingangssignal. Eine Leitung, die zur Eingangsschaltung führt, könnte ein Bias-Potential darstellen. Oftmals wird so eine gemeinsame Schaltschwelle für die Eingänge festgelegt. Im Datenblatt findet sich kein Hinweis darauf, dass die Ausgänge auch Eingänge sind. Vielleicht wird die Doppelfunktion während der Produktion zu Testzwecken genutzt.

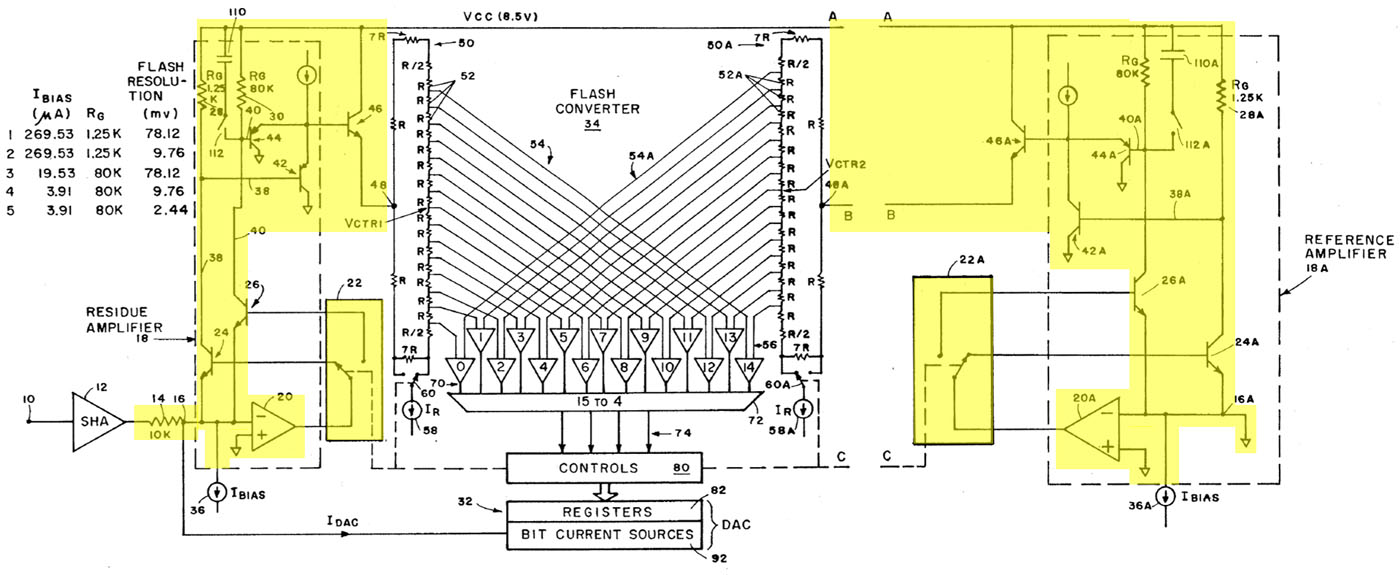

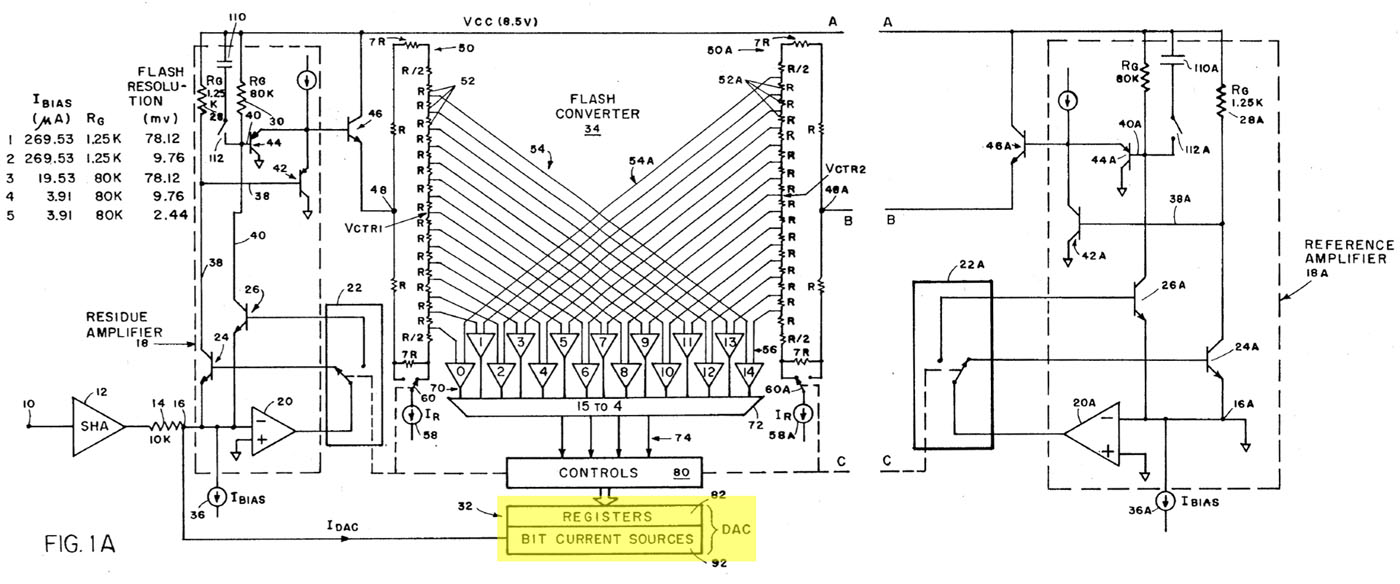

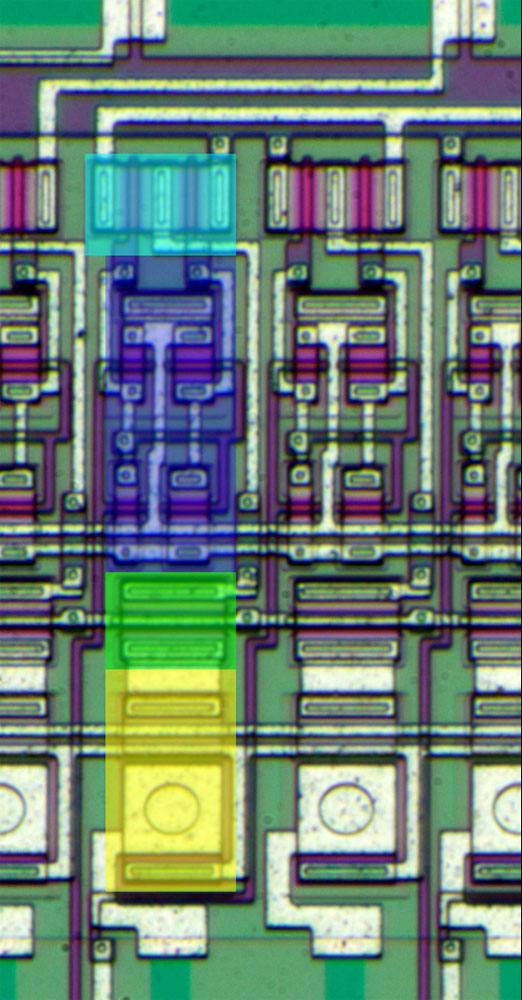

Das Datenblatt des AD679 erwähnt mehrere Patente, darunter das Patent US4804960, das den Aufbau des Analog-Digital-Wandlers sehr ausführlich beschreibt. Wie üblich für einen SAR-Wandler wird das analoge Eingangssignal, das die Sample&Hold-Stufe (gelb) fixiert hat, mit dem Ausgangssignal eines Digital-Analog-Wandlers (rot) gemischt. Der Operationsverstärker 20 verstärkt mit dem Transistor 24 oder dem Transistor 26 die Summe aus den beiden Stromwerten (türkis). Darauf folgt ein Pufferverstärker bestehend aus den Transistoren 42, 44 und 46 (dunkelgrün).

Die Auswertung der Differenz von Eingangssignal und DAC-Ausgang erfolgt nicht mit einem einfachen Komparator, sondern mit einem 4Bit-Flash-ADC (hellgrün). Der Flash-ADC besteht aus 15 Komparatoren, die an zwei großen Spannungsteilern angebunden sind. Die Stromsenken 58 und 58A treiben laut Patentschrift einen Strom durch die Widerstände, der initial einen Spannungsabfall von 78,12mV über jeden der Widerstände erzeugt. Das über die linke, dunkelgrüne Schaltung eingespeiste Eingangssignal hebt oder senkt das Potential des gesamten Spannungsteilers und so auch die Potentiale an den Komparatoren. Das Referenzpotential wird auf der rechten Seite über exakt die gleichen Strukturen geleitet. Dieser Aufbau sorgt dafür, dass sich parasitäre Eigenschaften und Drifts zu einem Großteil kompensieren. Die spezielle Verschaltung im hellgrünen Bereich führt dazu, dass die letzten Bits des Wandlungsergebnisses, von den Komparatoren in der Mitte der Kette festgelegt werden.

Der 4Bit-Flash-ADC muss mit jedem Durchlauf einen kleineren Restwert umwandeln.

Um dies zu ermöglichen, lässt sich die Schaltung an drei Stellen konfigurieren.

In der linken oberen Ecke des Blockschaltbilds sind die möglichen Einstellungen

dargestellt. Nach dem ersten Durchlauf wird die Stromsenke 58

umgeschaltet. Das reduziert den Strom durch die Spannungsteilerkette um einen

Faktor 8 und erhöht damit dessen Auflösung auf 9,76mV.

Im dritten Durchlauf

ist die

Stromsenken 58 wieder in der Ausgangsstellung. Um den noch kleineren

Restwert bestmöglich wandeln zu können, schaltet die türkise Verstärkerstufe von

dem Transistor

24 auf den Transistor 26 um. Der um einen Faktor 64 höhere Kollektorwiderstand

sorgt dafür, dass der Restwert des Eingangssignals derart verstärkt wird, dass

die Einstellung des Flash-ADCs aus dem ersten Durchlauf wieder passend ist.

Im vierten Durchlauf schaltet die Stromsenke 58 am unteren Ende des

Spannungsteilers wieder in die 9,76mV-Stellung und erhöht die Auflösung weiter.

Gleichzeitig wird der Kondensator 110 zugeschaltet, der laut Patentschrift die

Bandbreite des ADCs von 6MHz auf 800kHz senkt. Diese Maßnahme reduziert die

Geschwindigkeit der Digitalwandlung ab dem vierten Durchlauf, sie reduziert aber

auch das Rauschen.

Im fünften Durchlauf erhöht sich noch einmal die Auflösung des

Spannungsteilers, indem dessen Strom auf ein Viertel des vierten Durchlaufs

reduziert wird.

Die Stromsenke 36 erzeugt einen gewissen Ruhestrom, so dass die Verstärkerstufe möglichst optimal arbeiten kann. Der Ruhestrom wird bei der Umschaltung zwischen den Transistoren 24 und 26 angepasst. Eine weitere Anpassung erfolgt beim Zuschalten der Bandbreitenbegrenzung.

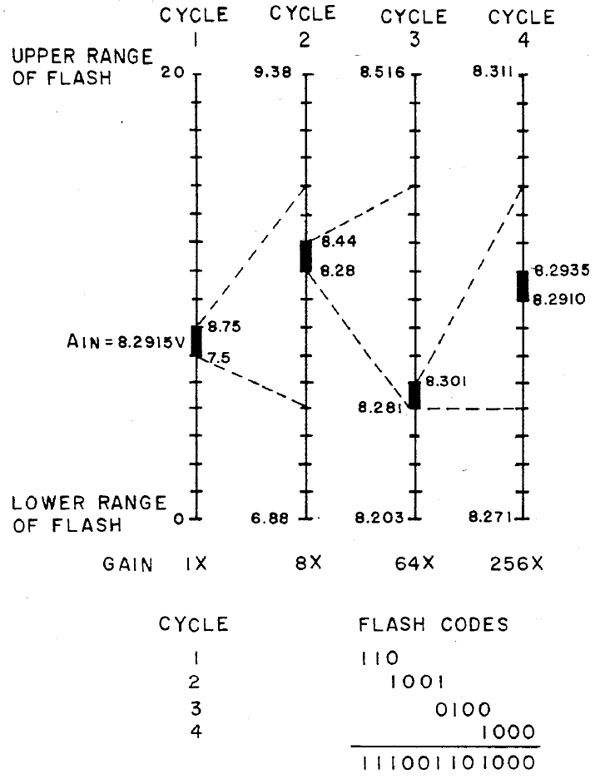

Das Patent US4804960 zeigt den Ablauf der Digitalwandlung. Die Eingangsspannung beträgt in diesem Beispiel 8,2915V. Im ersten Zyklus grenzt der FADC den Wert auf einen Bereich zwischen 7,5V und 8,75V ein und steuert im zweiten Zyklus die ersten Bereiche des DACs aus. Der neue Restwert wird um einen Faktor 8 verstärkt und der FADC kann den Bereich auf 8,28V - 8,44V einschränken. Im dritten Zyklus mit der noch genaueren Konfiguration des Digital-Analog-Wandlers und einem Verstärkungsfaktor von 64 vor dem FADC kommt der AD679 bereits auf einen Bereich von 8,281V - 8,301V. Im vierten Zyklus kommt man mit dem Wertebereich 8,2910V - 8,2935V auf eine Genauigkeit von 12Bit. Im fünften, hier nicht dargestellten Zyklus erhöht sich der Verstärkungsfaktor des FADC auf 1024, so dass daraus noch weitere zwei Bits für eine Genauigkeit von 14Bit (+/-0,3V) gewonnen werden können.

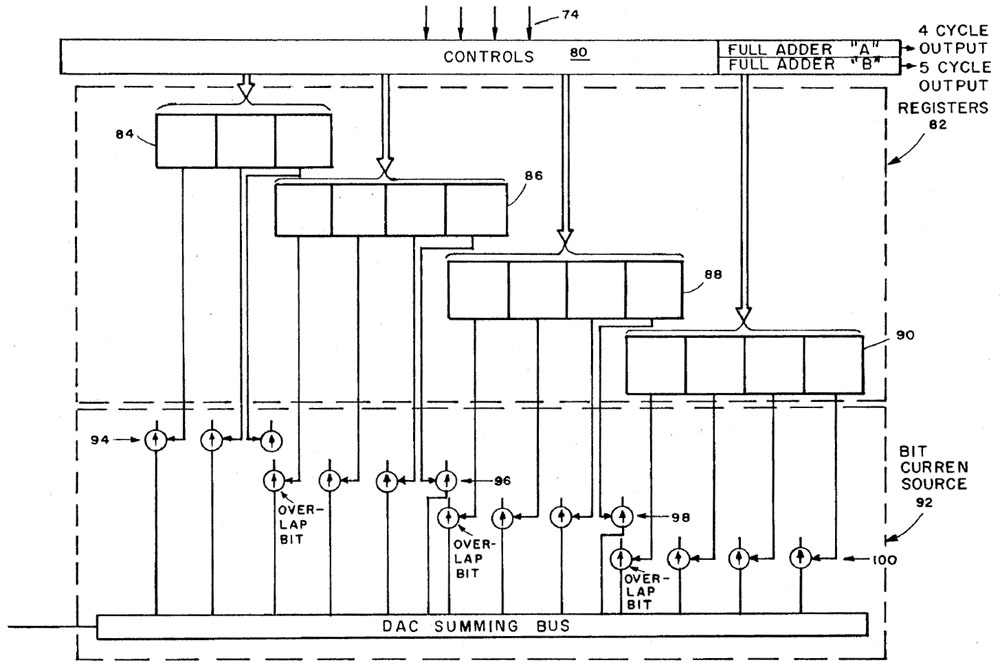

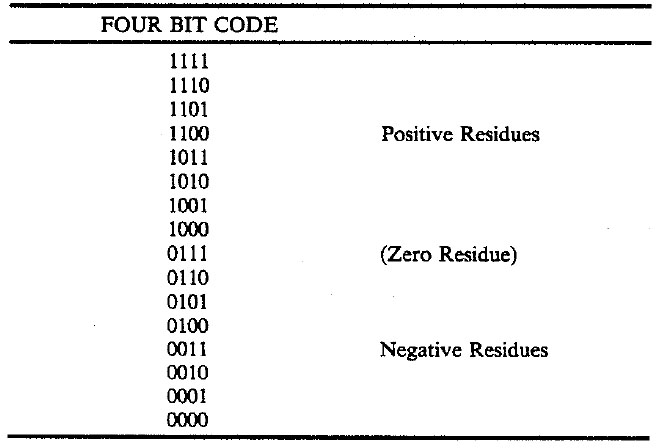

Die durch den FADC generierten digitalen Werte müssen letztlich entsprechend ihrer Gewichtung zusammengeführt werden, um den Digitalwert des analogen Eingangssignals zu erhalten. Hier sieht man bereits, dass das LSB des vorherigen und das MSB des aktuellen Zyklus die gleiche Gewichtung besitzen. Der FADC liefert folglich in den mittleren Zyklen vier Bit, von denen nur drei Bit direkt zum Ergebnis beitragen. Das MSB bietet lediglich eine Möglichkeit der Fehlerkorrektur für den vorherigen Zyklus.

Die Patentschrift zeigt die Möglichkeiten der Fehlerkorrektur noch etwas genauer. Abgesehen vom ersten Zyklus generiert der Flash-ADC bei jeder Digitalwandlung ein Overlap Bit, dessen Gewichtung dem LSB des vorherigen Durchgangs entspricht. Die Overlap Bits steuern zusätzliche Stromsenken im Digital-Analog-Wandler. So muss nicht zuerst eine digitale Korrektur erfolgen, die dann bereits fixierte Stromsenken umkonfiguriert.

Das Patent US4804960 beschreibt auch den genauen Ablauf der Digital-Analog-Wandlung mit und ohne Korrekturvorgang. Initial sind alle Stromsenken des Digital-Analog-Wandlers aktiv mit Ausnahme der überlappenden Stromsenken. Im ersten Zyklus werden die ersten drei Stromsenken entsprechend der Ausgabe des FADCs deaktiviert. In einem idealen Aufbau verbleibt ein negativer Rest und es können im nächsten Zyklus die drei nächstkleineren Stromsenken entsprechend der Vorgabe des FADCs deaktiviert werden.

Ergibt sich durch Fehlerbeiträge ein positiver Rest, so kann im aktiven Zyklus über die aufgedoppelte Stromsenke quasi nachträglich das LSB des vorherigen Zyklus wieder gesetzt werden. Der Restwert bewegt sich dann in den negativen Bereich und es können weiter Stromsenken abgeschaltet werden, um den Analogwert zu bestimmen.

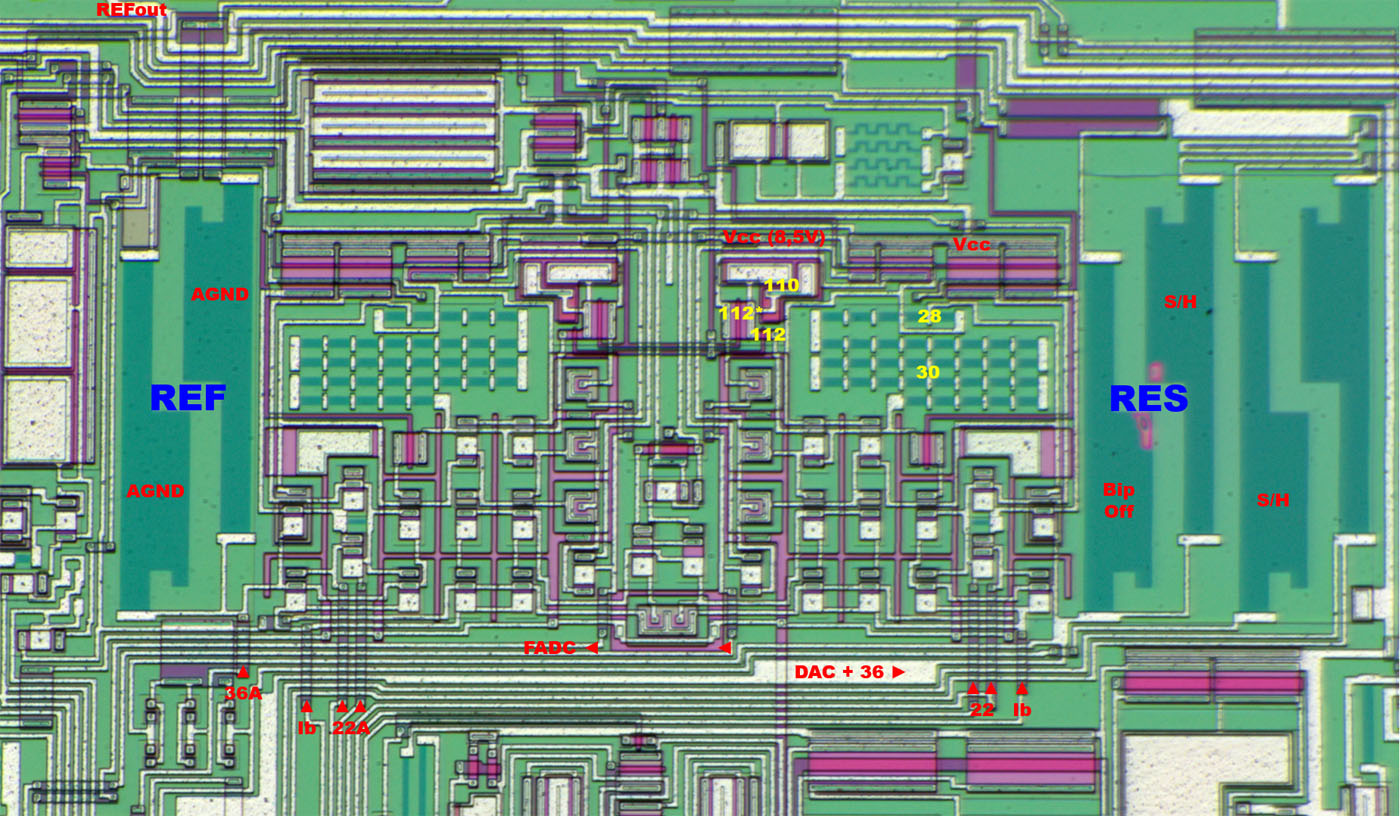

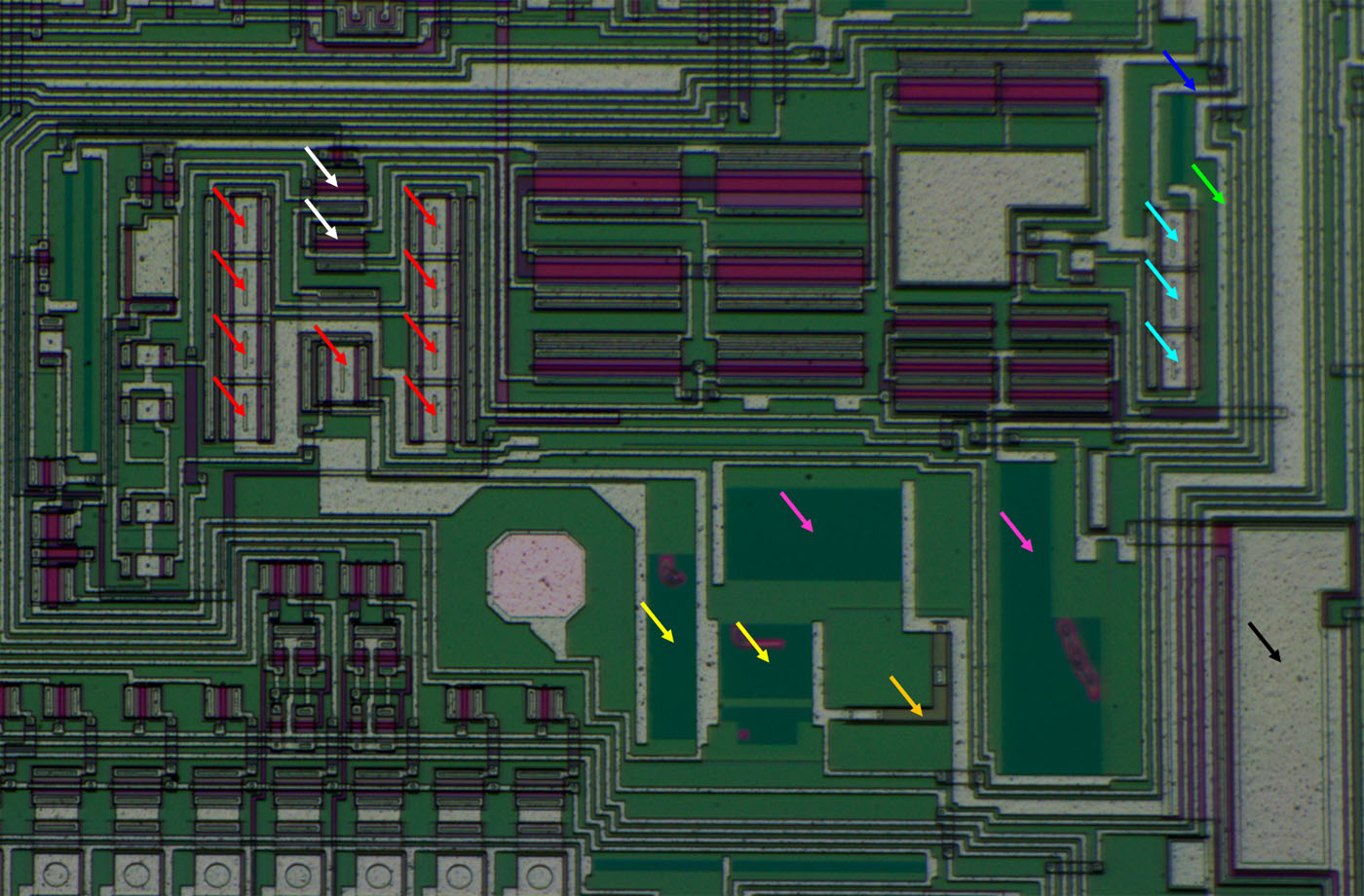

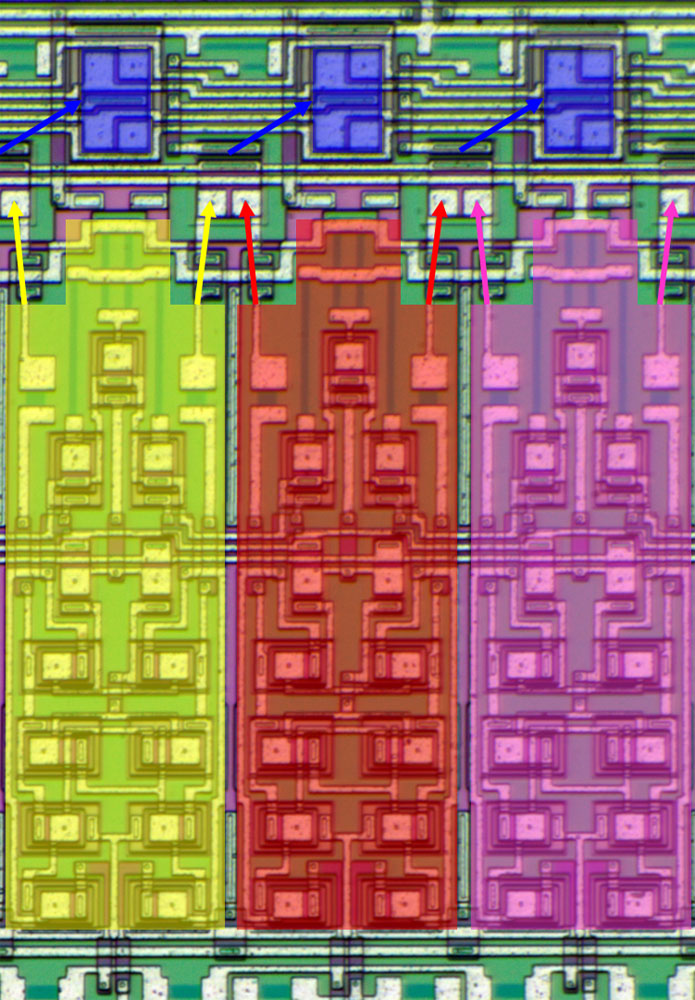

Im Analogteil des AD679 ist die Sample&Hold-Schaltung (blau) ganz rechts platziert. Nach links folgt die Referenzspannungserzeugung (türkis) und die Referenzstromerzeugung (gelb). Das Ausgangssignal der Sample&Hold-Schaltung wird differentiell übertragen. Oberhalb der Referenzen münden die zwei Leitungen in zwei Widerstände (blau). Der eine Widerstand führt zu einem Bezugspotential, das aktiv geregelt wird (schwarz). So ist sichergestellt, dass das zu Grunde liegende Bezugspotential nicht mit schwankender Last seinen Wert ändert. Die Ausgangsspannung der Sample&Hold-Schaltung wird über den zweiten Widerstand in einen Strom gewandelt, mit dem Ausgangsstrom des Digital-Analog-Wandlers (rot) zusammengefasst und dem Verstärker des Flash-ADCs zugeführt (dunkelgrün). Daneben befindet sich der Referenzverstärker (rosa). Beide Operationsverstärker nutzen Stromsenken aus dem Stromsenken-Array. Den größten Flächenanteil nimmt der 4Bit-Flash-ADC ein (hellgrün). Der Flächenbedarf macht deutlich, warum Analog-Digital-Wandler mit höherer Auflösung selten als Flash-ADCs umgesetzt werden.

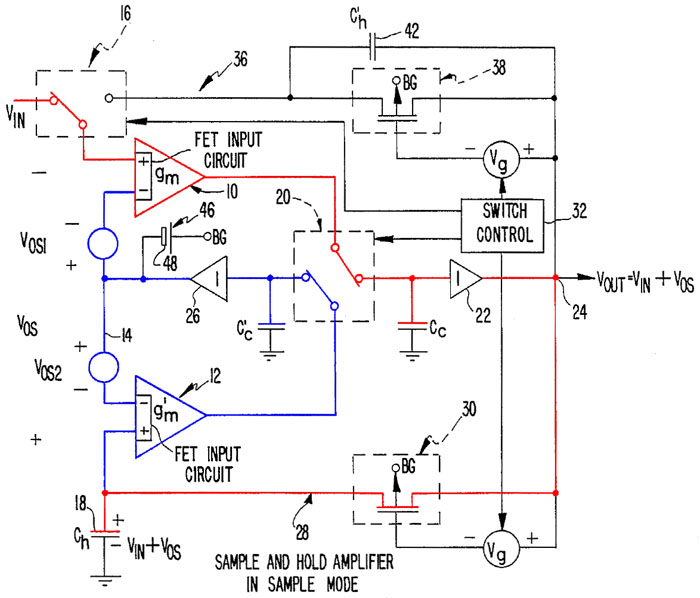

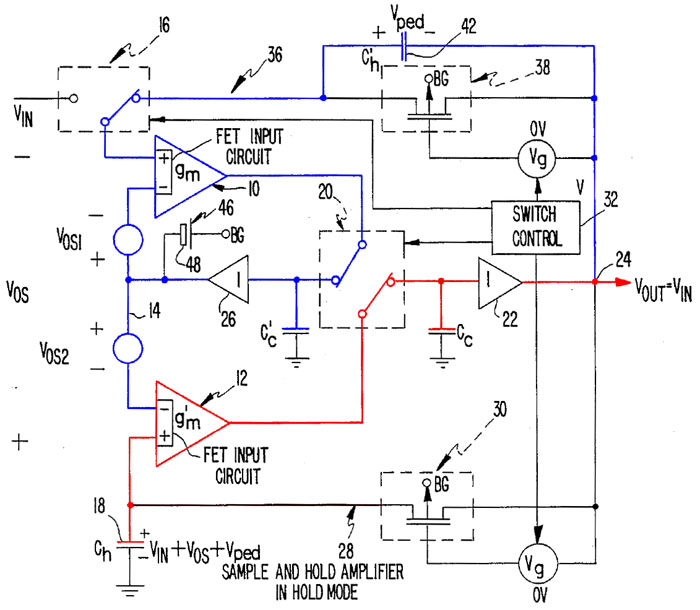

Die Sample&Hold-Schaltung muss den Wert am Eingang des AD679 abspeichern und soll dabei die Signalquelle möglichst wenig belasten. Dafür benötigt man Pufferverstärker und Schalter. Beide Bauelemente addieren teilweise erhebliche Fehler zum Nutzsignal. Will man bei einem Eingangsspannungsbereich von 10V eine Genauigkeit von 14Bit erreichen, so darf der Fehler des Gesamtsystems aber maximal +/-0,6mV betragen.

Im Datenblatt des AD679 wird das Patent US4833345 erwähnt, das eine Sample&Hold-Schaltung beschreibt. Im Großen und Ganzen scheint diese Schaltung im AD679 umgesetzt worden zu sein. Das in der Patentschrift abgebildete Schaltbild wurde zum besseren Verständnis eingefärbt. Die Schaltung versucht durch eine spezielle Schaltmimik möglichst viele Störungen zu kompensieren.

Im Sample-Modus wird über den roten Pfad der Speicherkondensator Ch geladen. Der obere Operationsverstärker 10 dient dabei als Puffer. Die FET-Eingangsstufen garantieren einen hohen Eingangswiderstand, addieren aber auch die Offsetspannung Vos1 auf das Nutzsignal. Die Rückkopplung (blau) erreicht den Operationsverstärker 10 nicht direkt, sondern wird über den Operationsverstärker 12 geführt, der die Offsetspannung Vos2 addiert. Im Hold-Modus schalten die Schalter 20 um. Auch die Schalter 30 und 38 werden deaktiviert. Das hat zur Folge, dass das Potential des Speicherkondensators Ch über den Operationsverstärker 12 zum Ausgang durchgereicht wird und der Operationsverstärker 10 der Rückkopplung dient. Die nun getauschte Konfiguration sorgt dafür, dass die im Sample-Modus addierte Offsetspannung im Hold-Modus wieder abgezogen wird.

Der Kondensator Vped dient ebenfalls dazu unerwünschte Effekte zu kompensieren. Beim Übergang in den Hold-Modus öffnet der Schalter 30 und stellt von da an eine Kapazität dar. Die vom Speicherkondensator Ch dorthin abfließenden Ladungen beeinflussen das abgespeicherte Nutzsignal. Dieser Fehler wird kompensiert, indem man zuerst alle Schalter in den Hold-Modus schaltet. Dabei wird auch der Transistor 38 leitend geschaltet. Nach der notwendigen Einschwingzeit öffnet das System den Transistor 38, wodurch es auch hier zu einer Ladungsverschiebung kommt. Der Kondensator 42 sorgt dafür, dass die Ladungsverschiebung eine Spannung erzeugt, die die Spannung Vqed kompensiert.

Die Spannungsquelle 48 sorgt dafür, dass die Bulkpotentiale der Transistoren 30 und 38 eine konstante Spannung über dem Nutzsignal liegen. Die Ansteuerung der beiden Transistoren erfolgt ebenfalls über Potentiale, die abhängig vom Nutzsignal sind. So ist sichergestellt, dass sich die Transistoren unabhängig vom Eingangspegel immer gleich verhalten.

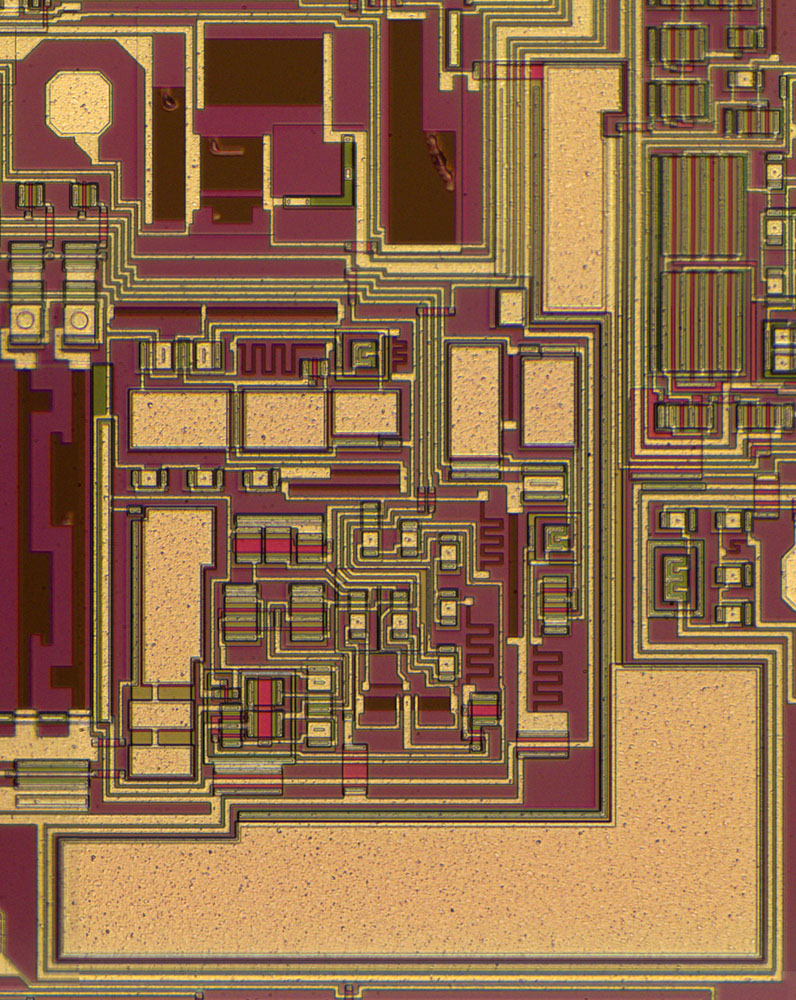

Die Sample&Hold-Schaltung lässt sich problemlos identifizieren. Mittig von oben trifft das zu wandelnde Analogsignal ein. Von unten, aus dem digitalen Schaltungsteil erfolgt die Zuführung der Steuersignale, die über fünf Testpads kontaktierbar sind. Das aufbereitete Eingangssignal verlässt die Schaltung in der linken oberen Ecke. Es wird differentiell über zwei Leitungen ausgegeben. Rechts und links flankieren das negative Versorgungspotential und das analoge Bezugspotential den Sample&Hold-Block.

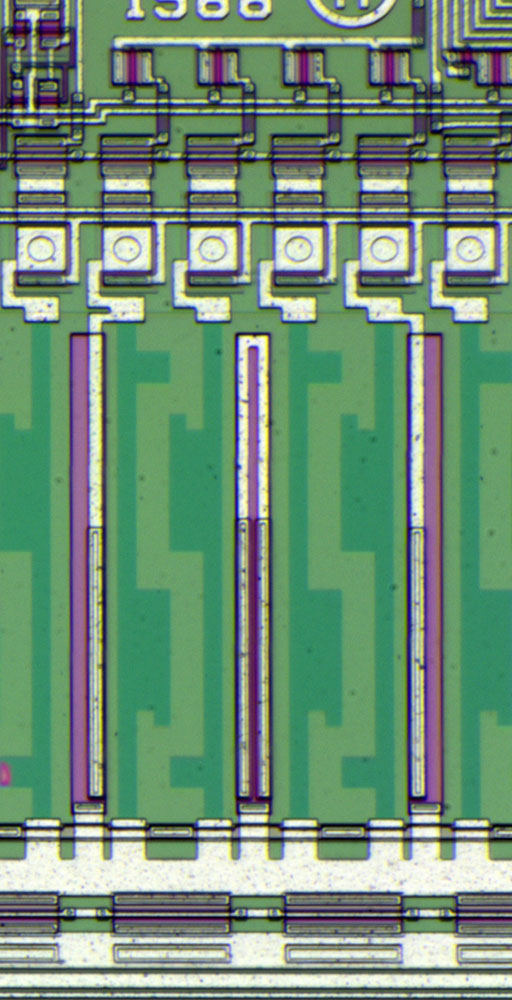

Beim negativen Versorgungspotential (Bondpad oben rechts) zeigt sich wie aufwändig die Potentialverteilung aufgebaut ist. Eine lange vertikale Leitung kontaktiert an der rechten Seite vielfach das Substrat (schwarz). Sie dient anscheinend als Abschirmung zu den Bondpads an der rechten Kante. Ein weiterer Vee-Strang stellt lokal zusätzliche Substratverbindungen her (blau) und dient einigen Schaltungsteilen als Arbeitspotential oder als Schirm (blau/rot). Ein dritter Vee-Strang führt zur Referenzspannungserzeugung, ist aber im unteren Bereich der Sample&Hold-Schaltung ebenfalls an das Substrat angebunden (gelb). Dazu kommen zwei weitere Vee-Leitungen, die die Sample&Hold-Schaltung versorgen und hier nur bei ihrem Sternpunkt markiert sind (orange).

Im unteren Bereich der Sample&Hold-Schaltung befinden sich drei große Treiber. Die äußeren Treiber bedienen die Schalter 30 und 38. Der mittlere Treiber steuert den Kreuzumschalter 20. Die Treiber werden aus dem Logikbereich über drei Leitungen mit Testpads angesteuert.

Die Steuerleitungen, die die rechten beiden Testpad durchlaufen, führen zum Umschalter 16 am Eingang der Sample&Hold-Schaltung.

Der Umschalter 16 am Eingang der Sample&Hold-Schaltung verteilt sich auf zwei symmetrische Pfade. Der rechte Pfad wird über die zwei Leitungen aus dem Logikbereich angesteuert. Im linken Pfad scheint es keine direkte Ansteuerung zu geben. Manche Gates sind mit dem Vee-Potential verbunden.

Nicht alle Funktionsblöcke der Sample&Hold-Schaltung lassen sich identifizieren. Bei genauerer Betrachtung gut zu erkennen sind der Sampling-Kondensator 18 und der Kondensator 42, der wie bereits beschrieben die parasitären Kapazitäten des Transistors 30 kompensiert.

Oberhalb der großen Treiber befindet sich der doppelte Umschalter 20. Er besteht aus zwei Doppeltransistoren oberhalb und unterhalb des mittigen Kondensators. Die Doppeltransistoren und auch andere Komponenten isolieren Rahmenstrukturen, die mit dem negativen Versorgungspotential verbunden sind.

In diesem Bereich scheinen auch die Operationsverstärker 22 und 26 integriert zu sein. Das erklärt den symmetrischen Aufbau. In der unteren Hälfte des Bildes findet sich eine Gruppe von vier quadratischen Transistoren. Von diesen Transistoren aus wird das Ausgangssignal der Sample&Hold-Schaltung sternförmig zu mehreren anderen Schaltungsteilen geführt. Das Signal erreicht unter anderem den Verstärker des FADCs, die Testpunkte an der oberen Kante des Dies und die Transistoren 30 und 38. Weiter oben befindet sich eine gleich aufgebaute Gruppe von vier Transistoren, die die zweite der differentiellen Leitungen bedient.

Die lila Flächen im linken Bereich des Bildes müssen die Kondensatoren Cc und Cc' sein. Dazu passt, dass sie nur aus einer Elektrode bestehen und sich auf das Substratpotential beziehen.

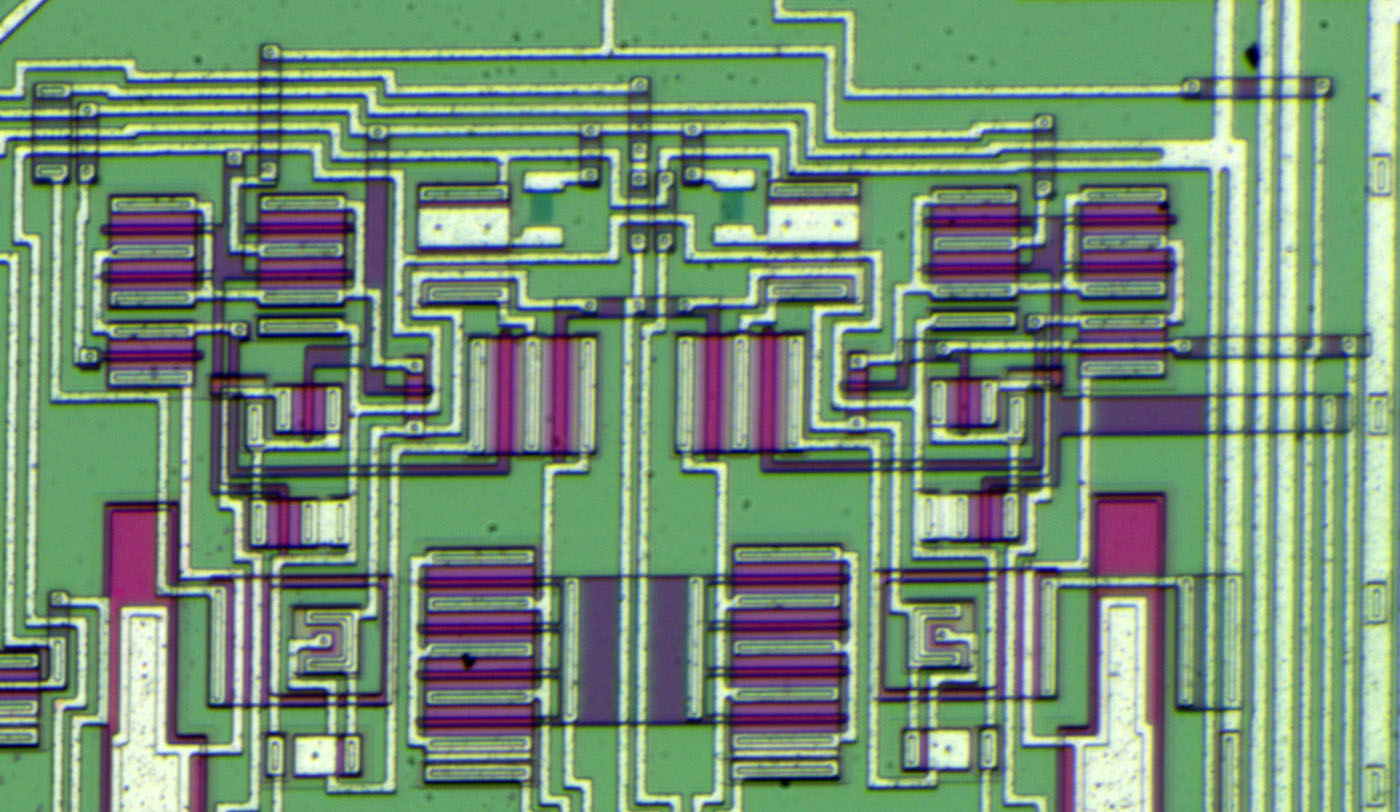

Der AD678 arbeitet mit den zwei Operationsverstärkern 20 und 20A, die das Restsignal aus der Summe des Eingangssignals und des Digital-Analog-Wandlers verstärken. Der linke Operationsverstärker, der im Schaltbild der Patentschrift als 20A bezeichnet wird, dient als Referenz, während der rechte Operationsverstärker (20) die Differenz aus dem Eingangssignals und dem Digital-Analog-Wandler-Ausgang verstärkt. Rechts und links der Operationsverstärker befinden sich jeweils zwei große, abgleichbare Widerstände. Rechts sind diese Widerstände an den Ausgang der Sample&Hold-Stufe und an den Eingang Bipolar Offset angebunden. Die linken beiden Widerstände führen das Massepotential zum Referenz-Verstärker.

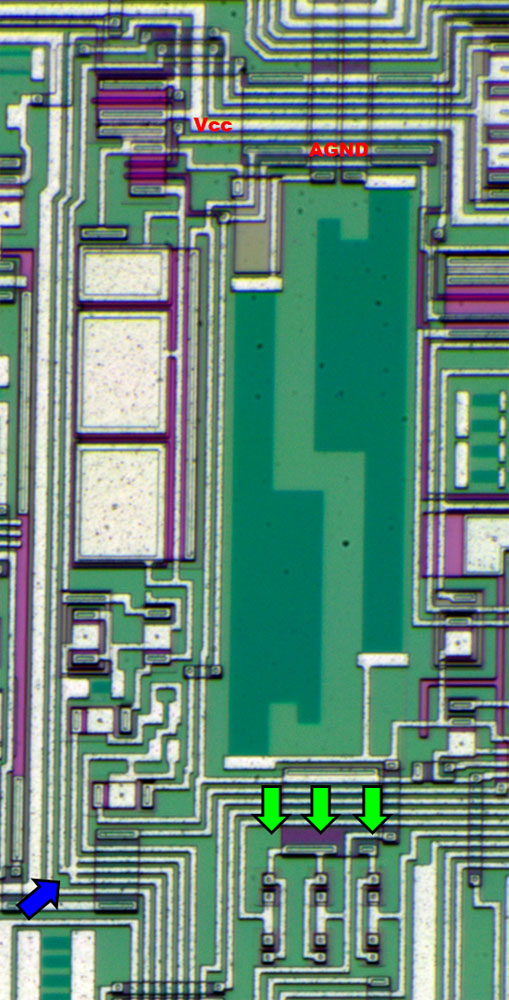

Auch hier lassen sich einige Schaltungsteile identifizieren. Der größere, unsymmetrische Block im oberen Bereich scheint ein Spannungsregler zu sein. Vermutlich handelt es sich um die Versorgung, die im Patent mit dem Potential von 8,5V angegeben wird. Der Regler ist mit der Versorgung Vcc und der internen Referenzspannung verbunden.

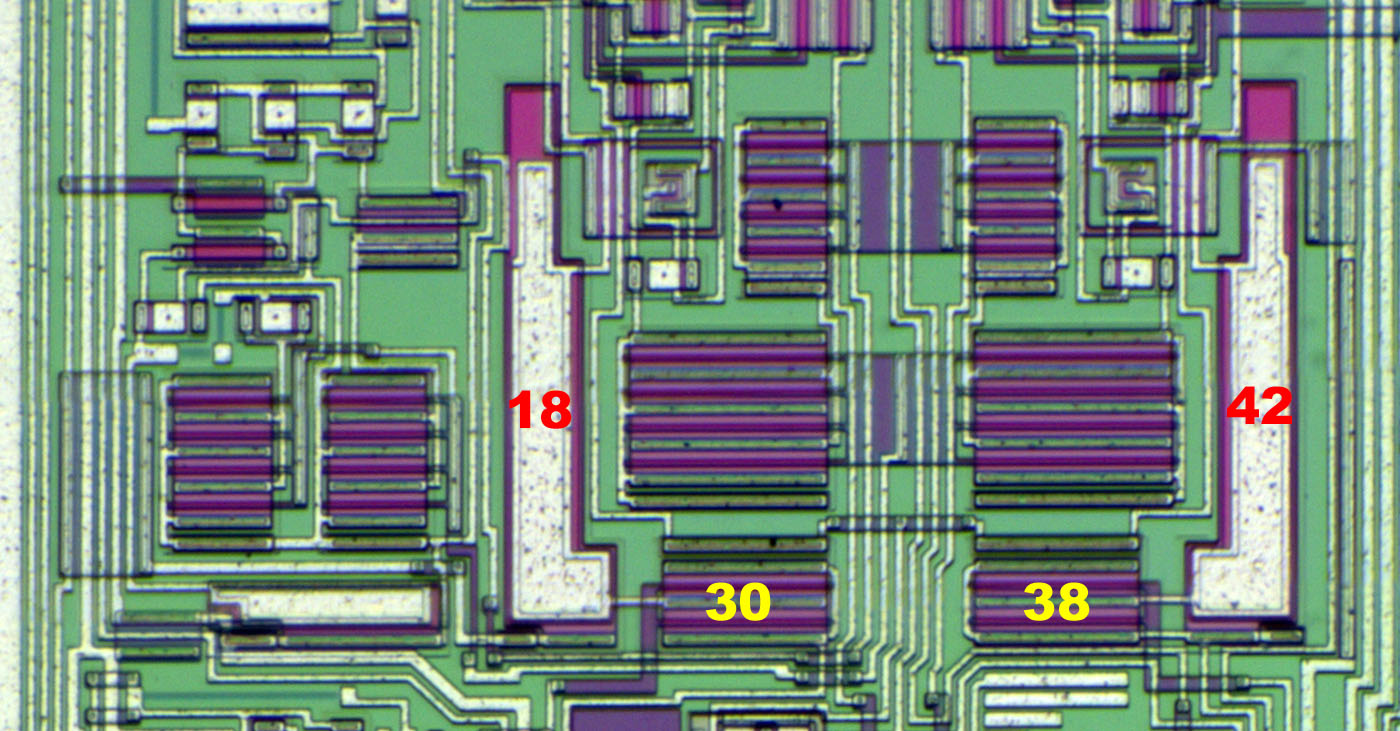

Die Widerstände 28 und 30, die zur Umschaltung des Verstärkungsfaktors dienen, sind aus vielen einzelnen Widerstandsstreifen aufgebaut. Daneben befindet sich der Kondensator 110, der bei der Umschaltung die Bandbreite der Schaltung optimiert. Der Kondensator ist aus zwei Elementen aufgebaut, vermutlich um den Wert über eine einfache Änderung der Metalllage anpassen zu können. Es zeigt sich, dass die Kapazität nicht nur über den Transistor 112 mit dem Widerstand 30 verbunden wird. Daneben schaltet der Transistor 112* einen Pfad zum Ausgang des Operationsverstärkers.

Ein Isolationsgitter sorgt für eine möglichst geringe gegenseitige Beeinflussung der einzelnen Transistoren. Die Eingänge der Operationsverstärker befinden sich in den unteren äußeren Ecken. Die Eingangsstufen arbeiten mit mehreren Stromsenken aus dem Bereich des Digital-Analog-Wandlers. Direkt an den Eingängen befinden sich die schaltbaren Stromsenken 36 und 36A, die den Ruhestrom des Verstärkers einstellen. Der Strom der Stromsenke 36 wird mit dem Strom des Digital-Analog-Wandlers übertragen. Die Eingangsstufen arbeiten außerdem mit den zwei konstanten Stromsenken Ib. Die Stromsenken 22 und 22A dienen der Umschaltung der zwei Verstärkerstufen, mit ihren unterschiedlichen Verstärkungsfaktoren.

Der AD679 besitzt eine Schaltung, die ein aktiv geregeltes Bezugspotential bereitstellt, wie man es zum Beispiel auch beim DAC709 findet. Es handelt sich meist um das Massepotential, dass mit Bezug auf das positive Versorgungspotential eingestellt wird. So ist sichergestellt, dass das Bezugspotential auch nicht schwankt, wenn im Rahmen der Analog-Digital-Wandlung verschieden hohe Ströme entnommen werden.

Das externe Massepotential ist niederohmig mit der Schaltung verbunden. Im unteren Bereich befindet sich der blau markierte Knoten, der als Sternpunkt für das geregelte Bezugspotential dient. Zu diesem Sternpunkt wird unter anderem eine Rückkopplungsleitung geführt, die es ermöglicht das Bezugspotential auch bei unterschiedlichen Belastungen möglichst optimal auszuregeln. Das geregelte Bezugspotential wird zu den Digital-Analog-Wandlern geführt, wo es sowohl als Bezugspotential für die R2R-Teiler, als auch als Alternativpotential für die Umschalter der Stromquellen dient. Außerdem ist eine der differentiellen Ausgänge der Sample&Hold-Schaltung dort angebunden.

Im unteren Bereich des Ausschnitts sind drei Strukturen zur Spannungsbegrenzung integriert, die sich auf das externe Massepotential beziehen. Zwei der Strukturen schützen die Eingänge der beiden Verstärker. Die dritte Schutzstruktur ist mit dem Ausgang der Sample&Hold-Schaltung verbunden, der gegen das geregelte Bezugspotential arbeitet.

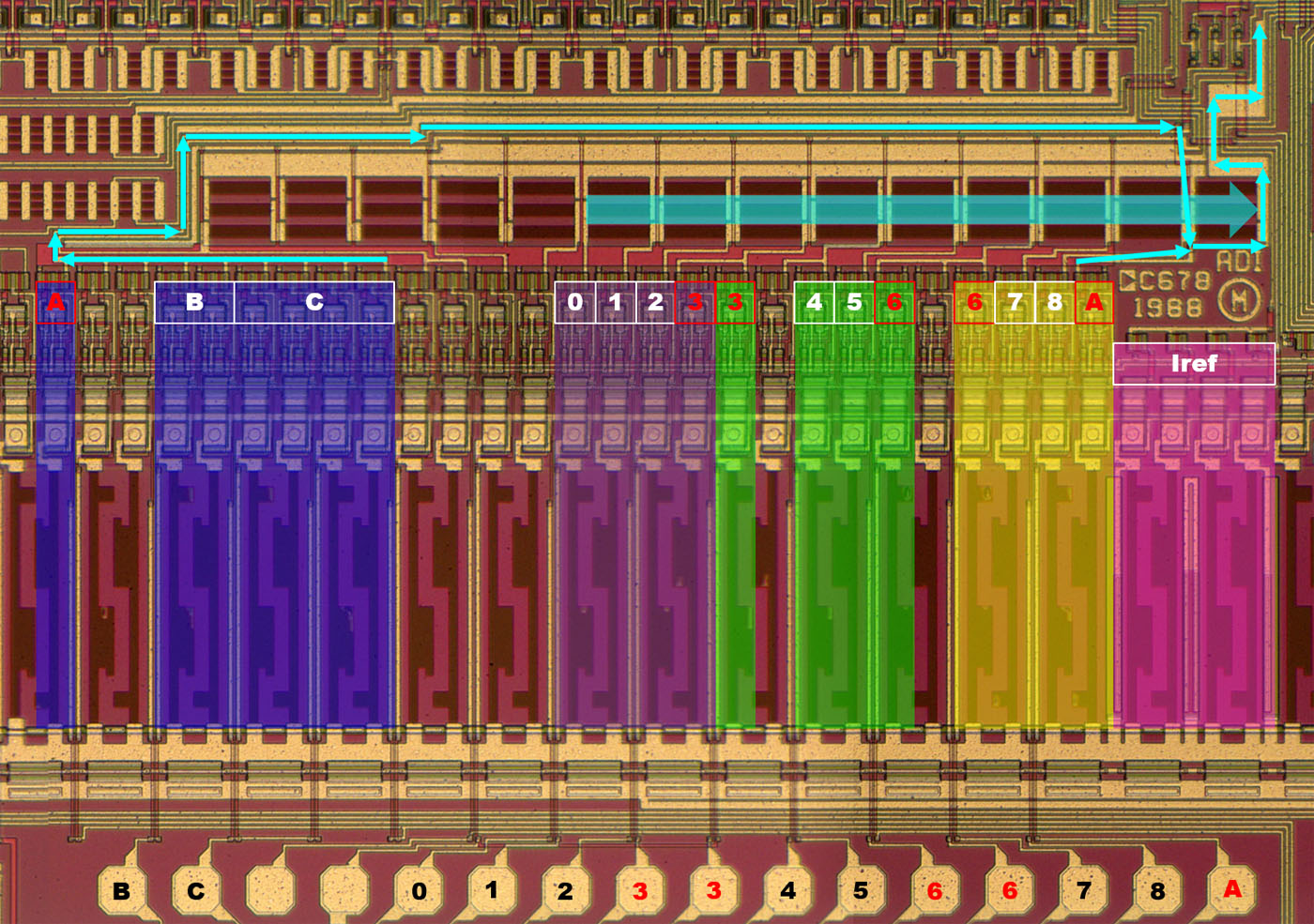

Der Digital-Analog-Wandler nutzt einen Großteil der auffälligen Stromsenken. Diese werden über Steuerleitungen aus dem Digitalteil aktiviert. Die meisten Steuerleitungen sind mit Testapds ausgestattet. Der Digital-Analog-Wandler arbeitet mit einem R2R-Stromteiler. Lediglich die obersten Bits werden direkt durch einzelne Stromsenken dargestellt. Ein ähnliches Konzept findet sich zum Beispiel bei dem Digital-Analog-Wandler AD7535. Die Stromsenken 0 bis 8 sind an den darüber liegenden R2R-Stromteiler angebunden. Es handelt sich um Vierergruppen (lila, grün, gelb). An den Übergangsstellen der Gruppen sind die Stromsenken aufgedoppelt (rot). Darüber kann, wie bereits beschrieben, ein Wandlungszyklus den Summenstrom aus dem vorherigen Zyklus noch etwas korrigieren.

Die Stromsenke A im gelben Bereich speist bereits direkt in die Sammelleitung, die zum Verstärker des FADCs führt. Auch diese Stromsenke ist im linken Bereich (blau) aufgedoppelt. Dazu kommen die Stromsenken B und C für die obersten zwei Bits. Um die notwendigen Stromwerte direkt darstellen zu können, ist die Stromsenke B doppelt so groß ausgeführt wie die Stromsenke A und die Stromsenke C ist wiederum doppelt so groß ausgeführt wie die Stromsenke B.

Aus den Werten, die sich im Patent US4804960 finden, kann man schließen, dass jede einzelne Stromsenke 125µA aufnimmt. Das LSB des Digital-Analog-Wandlers ("0") trägt demnach nur 244nA zum Strom in Summenknoten bei. Um eine Genauigkeit von 14Bit erreichen zu können, müssen die Stromsenken auf 31nA genau eingestellt werden. Der Strom darf selbstverständlich auch nicht in anderen Schaltungsteilen abfließen.

Im rechten Bereich befinden sich die Stromsenken, die als Referenz für die anderen Stromsenken dienen (rosa).

Zwischen den Stromsenken des eigentlichen Digital-Analog-Wandlers befinden sich weitere Stromsenken, die an die Verstärker des FADCs angebunden sind. Die türkisen Stromsenken bedienen den Verstärker für den Restwert. Die gelben Stromsenken sind an den Verstärker angebunden, der die Referenz darstellt.

Ganz rechts befindet sich ein Block mit zweimal zwei Stromsenken. Die festen Stromsenken Ib dienen anscheinend nur als einfache Arbeitspunkteinstellung. Die schaltbaren Stromsenken 22 und 22A ermöglichen die Umschaltung der Verstärkungsfaktoren der FADC-Verstärker.

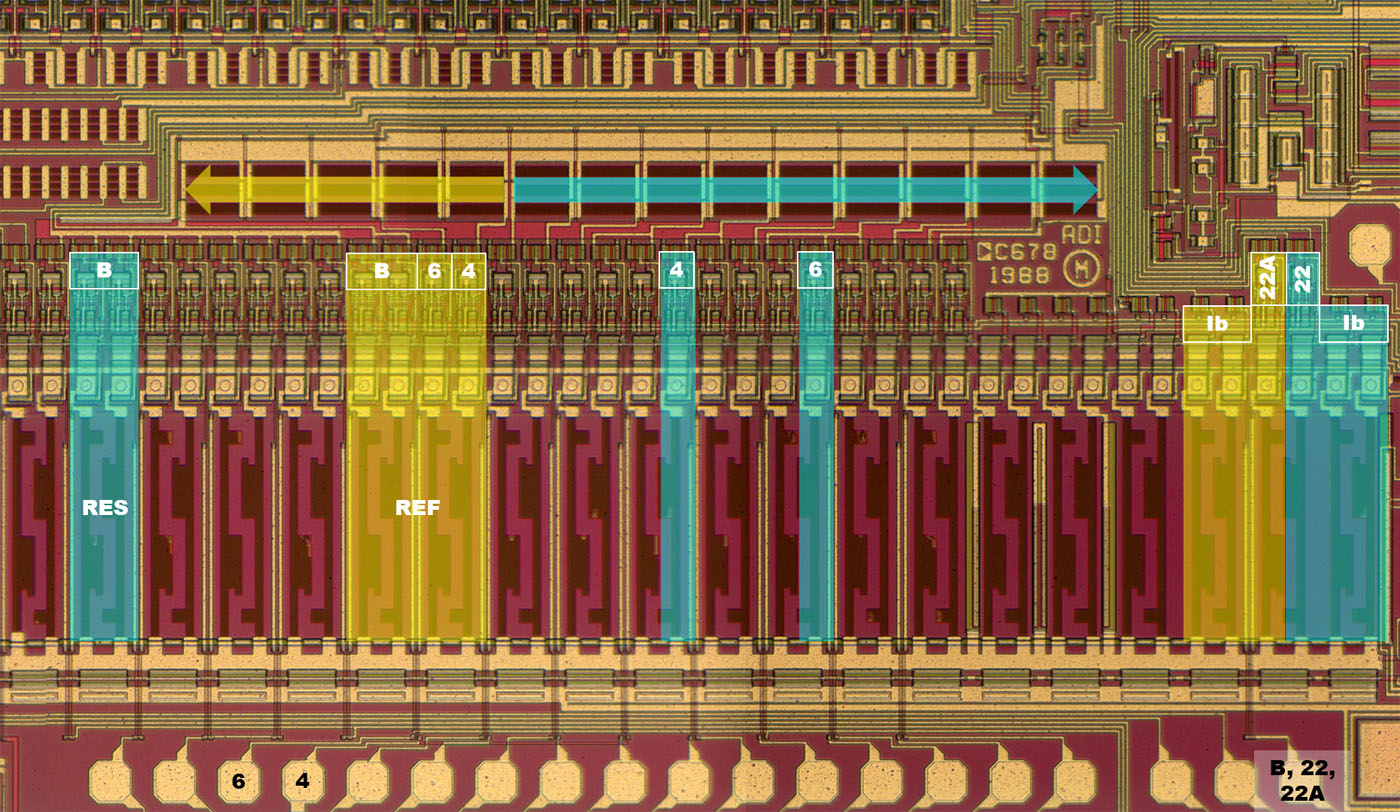

In den R2R-Stromteiler des Digital-Analog-Wandlers werden zusätzlich die drei türkisen schaltbaren Stromsenken 4, 6 und B eingespeist. Die Stromwerte sind die gleichen, wie bei den gleich benannten Stromsenken des Digital-Analog-Wandlers. Diese drei Stromsenken dienen allerdings als variable Arbeitspunkteinstellung des Verstärkers, die im Übersichtsbild mit der Zahl 36 bezeichnet ist. Für den Referenz-Verstärker stehen Stromsenken mit denselben Stromwerten zur Verfügung (gelb), um auch dort den Arbeitspunkt entsprechend umschalten zu können. Extra für diesen Zweck wurde links des bereits beschriebenen R2R-Stromteilers ein weiterer R2R-Stromteiler integriert (gelber Pfeil).

Die Stromsenken der beiden Verstärker werden über gemeinsame Steuerleitungen geschaltet. Für die Stromsenken 4 und 6 steht jeweils ein eigens Testpad zur Verfügung. Die Stromsenken mit den Bezeichnungen B, 22 und 22A werden miteinander geschaltet und besitzen daher auch nur ein Testpad. Das ist sinnvoll, da der höchste Ruhestrom durch die Stromsenken 36 beziehungsweise 36A einhergeht mit der Umschaltung der Verstärkerstufen, die über die Stromsenken 22 beziehungsweise 22A gesteuert werden.

Die Stromsenken bauen auf dem Vee Potential auf. An den Fußpunkten sind gemeinsam angesteuerte MOSFETs integriert, die von der Ansteuerung der Stromsenken kontrolliert werden. Das darüber liegende Potential wird ebenfalls zur Ansteuerung geführt. Es könnte sein, dass diese Transistoren ein stabiles Bezugspotential auf einem sinnvollen Niveau einregeln. Das wäre so weit plausibel, da das Vee-Potential einen sehr weiten Weg von den Stromsenken bis zum Vee-Bondpad zurücklegt.

Oberhalb des Transistors, der vermutlich das Bezugspotential regelt, befinden sich die mit einem Laser abgeglichenen Widerstände. Unterschiedlich breite Bereiche ermöglichen einen groben und einen feinen Abgleich. Die Fläche, in denen sich die Widerstände befinden, ist anscheinend über einen Streifen am Fußpunkt mit dem Vcc Potential verbunden. Diese Maßnahme hilft Leckströme zu reduzieren. Oberhalb der Widerstände befinden sich die Transistoren, die den gewünschten Strom einstellen und die Umschalter.

Der Transistor direkt oberhalb des Widerstands (gelb) stellt den gewünschten Strom ein. Gesteuert wird der Transistor über eine horizontal verlaufende Leitung, deren Potential über die Schaltung der Referenzstromerzeugung eingestellt wird. Üblicherweise reicht ein Transistor, um eine Stromsenke darzustellen. Dies ist zum Beispiel beim DAC709 zu sehen. Beim AD679 wurden über den Bipolartransistoren zusätzliche MOSFETs integriert (grün). Sie werden ebenfalls aus der Schaltung der Referenzstromerzeugung gesteuert und bilden eine Kaskodenschaltung. Die Kaskodenschaltung verhindert, dass sich Potentialänderungen am Ausgang auf den Stromwert auswirken.

Der blaue Bereich ist mit der Steuerleitung verbunden, die neben dem abgeglichenen Widerstand nach oben geführt wird. Die Schaltung erzeugt ein differentielles Steuersignal und dient als Pufferstufe für die darüber befindlichen Umschalter (türkis). An dieser Stelle wird die Stromsenke entweder mit dem Ausgang des Digital-Analog-Wandlers verbunden oder in der breiten lila Polysiliziumleitung neutralisiert. Die Polysiliziumleitung führt das weiter oben beschriebene geregelte Bezugspotential. Diese alternative Last sorgt dafür, dass sich im Bereich der Stromsenken unabhängig vom Zustand des Digital-Analog-Wandlers immer gleiche Ströme und Potentiale einstellen.

Die vier Stromsenken, die zur Erzeugung des Referenzstroms herangezogen werden, besitzen seitlich der abgleichbaren Widerstände zusätzliche Flächen. Es scheint sich um eine Abschirmung zu handeln. Das ist aber zumindest nicht der einzige Zweck. Die beiden äußeren Flächen sind sowohl mit dem Fußpunkt der Widerstände als auch mit dem Ausgang der jeweiligen Stromsenke verbunden. Es könnte sein, dass die Flächen hochohmige Widerstände darstellen, die notwendig sind, damit die Schaltung sicher anläuft. Die innere Fläche könnte dann einen Vorhalt darstellen, über den sich der Wert des Anlaufwiderstands variieren lässt.

Die Referenzspannungsquelle ist leicht zu erkennen, da sie die verhältnismäßig auffälligen Strukturen einer Bandpag-Referenz enthält. Die genaue Funktion einer Bandgap-Referenzspannungsquelle ist unter anderem im Rahmen des Spannungswächters TL7705 und der Referenzspannungsquelle AD1403 zu finden. Im linken Bereich des Bildes sind die zwei Transistoren integriert, an denen die Referenzspannung abgegriffen wird (rot). Das Größenverhältnis der Transistoren beträgt 8:1. Der größere Transistor ist um den Kleineren herum angeordnet, damit beide möglichst gleiche Eigenschaften und Temperaturen aufweisen.

Rechts unterhalb der Transistoren befindet sich ein Testpunkt und nach rechts folgend sind die typischen zwei in Reihe geschaltete Widerstände integriert, über die sich der Temperaturkoeffizient der Spannung einstellen lässt (gelb). Die Widerstände sind passend dazu abgeglichen. Interessant ist, dass sich zwischen den zwei Widerständen und dem von rechts zugeführten Massepotential ein weiterer Widerstand befindet (orange). Der Wert des dritten Widerstands kann über die Metalllage eingestellt werden und der Spannungsabfall daran wird auf ein Testpad an der oberen Kante des Dies geführt. Darüber lässt sich der Strom durch die Bandgap-Referenz vermessen.

Zwei weitere abgleichbare Widerstände (rosa) bilden den Spannungsteiler, über den sich die Ausgangsspannung der Referenz einstellen lässt. Von diesem Spannungsteiler führt eine Leitung zu einem weiteren Testpunkt an der oberen Kante des Dies. Zum REFout Bondpad führen zwei Leitungen. Die eine Leitung ist der Ausgang der Referenzspannungsquelle (blau), der über einem Ausgangstreiber mit drei Transistoren versorgt wird (türkis). Die andere Leitung (grün) ist die Rückkopplung, die mit dem Spannungsteiler verbunden ist.

Unter den restlichen Strukturen finden sich noch einige Schaltungsteile, die typisch sind für eine Bandgap-Referenz. Darunter ist zum Beispiel der Stromspiegel (weiß), der die beiden Bandgap-Transistoren versorgt. Am rechten Rand des Bildausschnitts beginnt eine größere Kapazität (schwarz).

Die Kapazität der Bandgap-Referenz musste auf zwei Bereiche aufgeteilt werden. Der zweite Teil ist unterhalb der Steuerschaltung zur Referenzstromerzeugung integriert.

Die Leitung, die die Stromsenken steuert, wird zuerst fast in die Mitte der Stromsenken geführt, bevor sie die Stromsenken kontaktiert. Diese Maßnahme reduziert den Spannungsabfall bis zur äußersten Stromsenke.

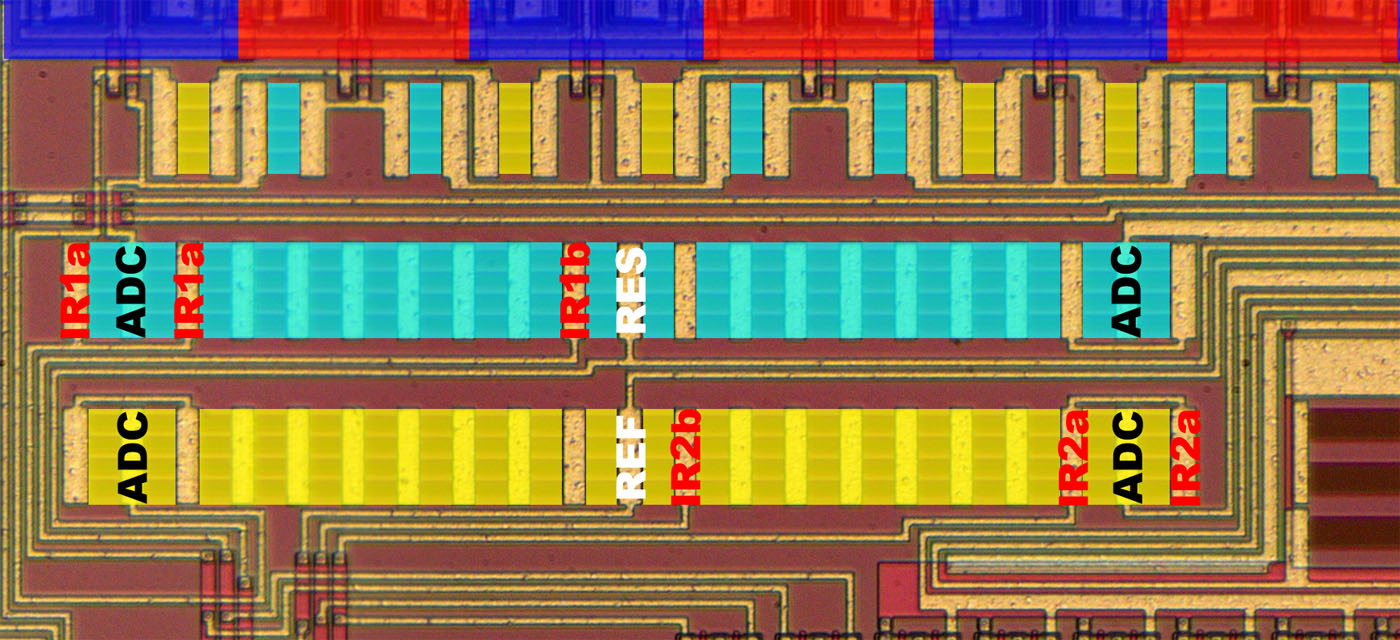

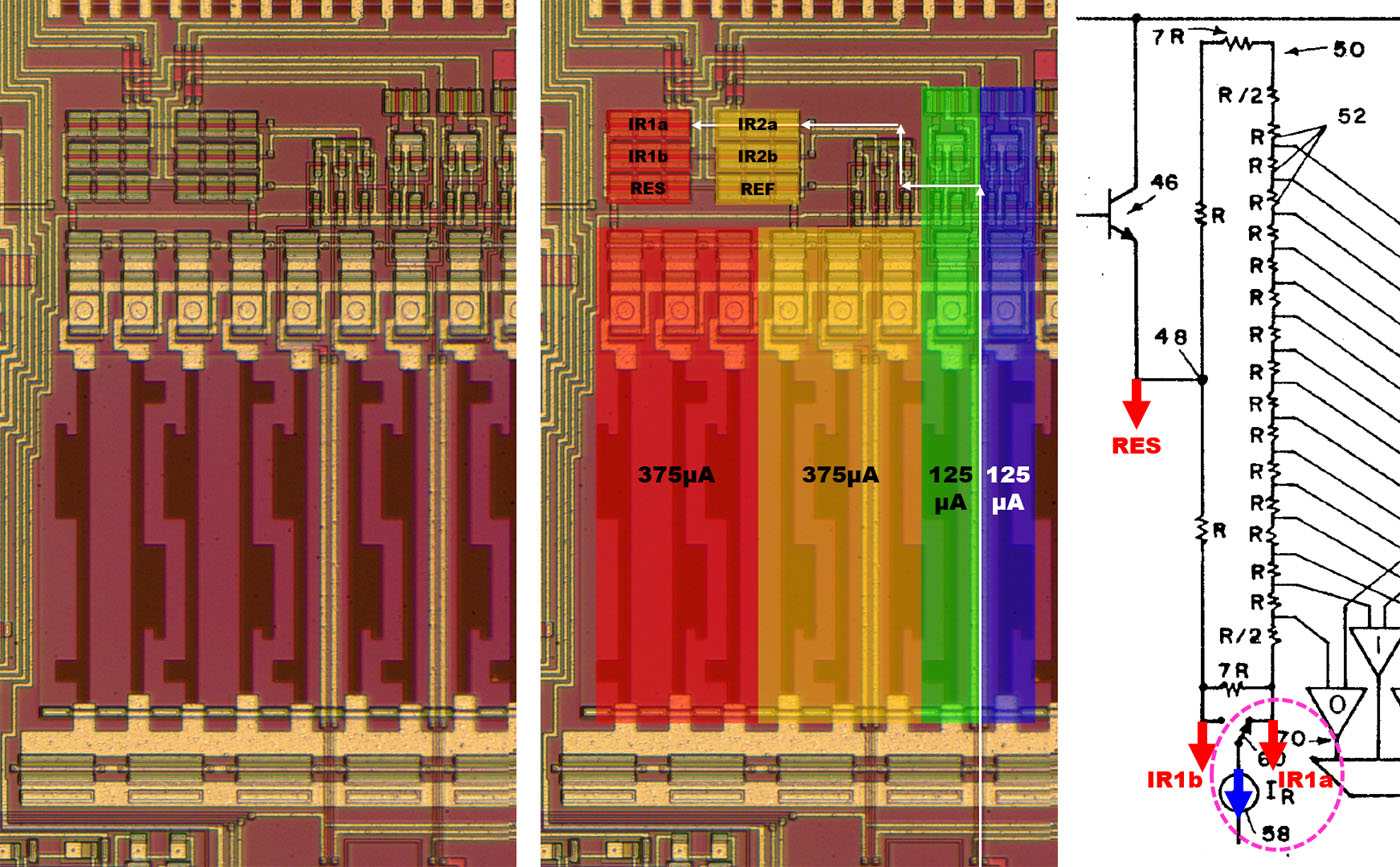

Der 4Bit-Flash-ADC nimmt eine verhältnismäßig große Fläche ein. Er besteht aus 15 Komparatoren, mehreren Widerstandsketten und einigen Stromsenken. Zwei Testpads an der linken Kante ermöglicht es die Eingangsspannung des FADCs zu vermessen.

Die Ausgänge der beiden Verstärker kontaktieren die Mitten zweier Widerstandsketten (RES und REF). Die Kontaktpunkte sind im Schaltbild des Patents US4804960 mit 48 und 48A bezeichnet. Die Widerstandsketten bieten von der Mitte nach außen jeweils die Widerstandswerte R, 7R und 1/2R. Das entspricht genau den Werten, die auch im Schaltbild des Patents aufgeführt sind.

Die Stromsenken, die in der Patentschrift als 58 und 58A bezeichnet sind, stellen sich etwas komplexer dar, wie sich gleich noch zeigen wird. Sie können zwischen den Anschlüssen IR1a, IR1b und RES beziehungsweise IR2a, IR2b und REF umgeschaltet werden. Von den äußeren Enden der beiden Widerstandsketten führen jeweils zwei Leitungen zu den zwei Spannungsteilern der Komparatoren, die sich darüber befinden und miteinander verwoben sind.

Die Stromsenken 58 und 58A bestehen aus insgesamt acht Stromsenken. Die rechten zwei Stromsenken sind aufgebaut wie die Stromsenken des Digital-Analog-Wandlers. Sie besitzen die bekannten Umschalter. Von den restlichen sechs Stromsenken sind jeweils drei zusammengefasst. Über jeder Dreier-Gruppen sind jeweils drei Schalter integriert. Hierbei handelt es sich nicht um Umschalter, sondern lediglich um einfache Schalter. Angesteuert werden die Schalter über einen kleinen Treiberblock.

Die rechten beiden Stromsenken nehmen jeweils 125µA auf. Die linken beiden Stromsenken nehmen insgesamt jeweils 375µA auf. Die grüne und die blaue Stromsenke werden mit einer Steuerleitung angesteuert (weiß), die über den Treiberblock gleichzeitig das oberste Schalterpaar IR1a und IR2a kontrolliert. Die Schalterpaare IR1a und IR2a verbinden die großen Stromsenken mit den Knoten IR1a und IR2a. Die unteren beiden Schalterpaare können über zwei eigene Steuerleitungen paarweise betätigt werden und verbinden die Stromsenken mit den Knoten IR1b und IR2b beziehungsweise RES und REF.

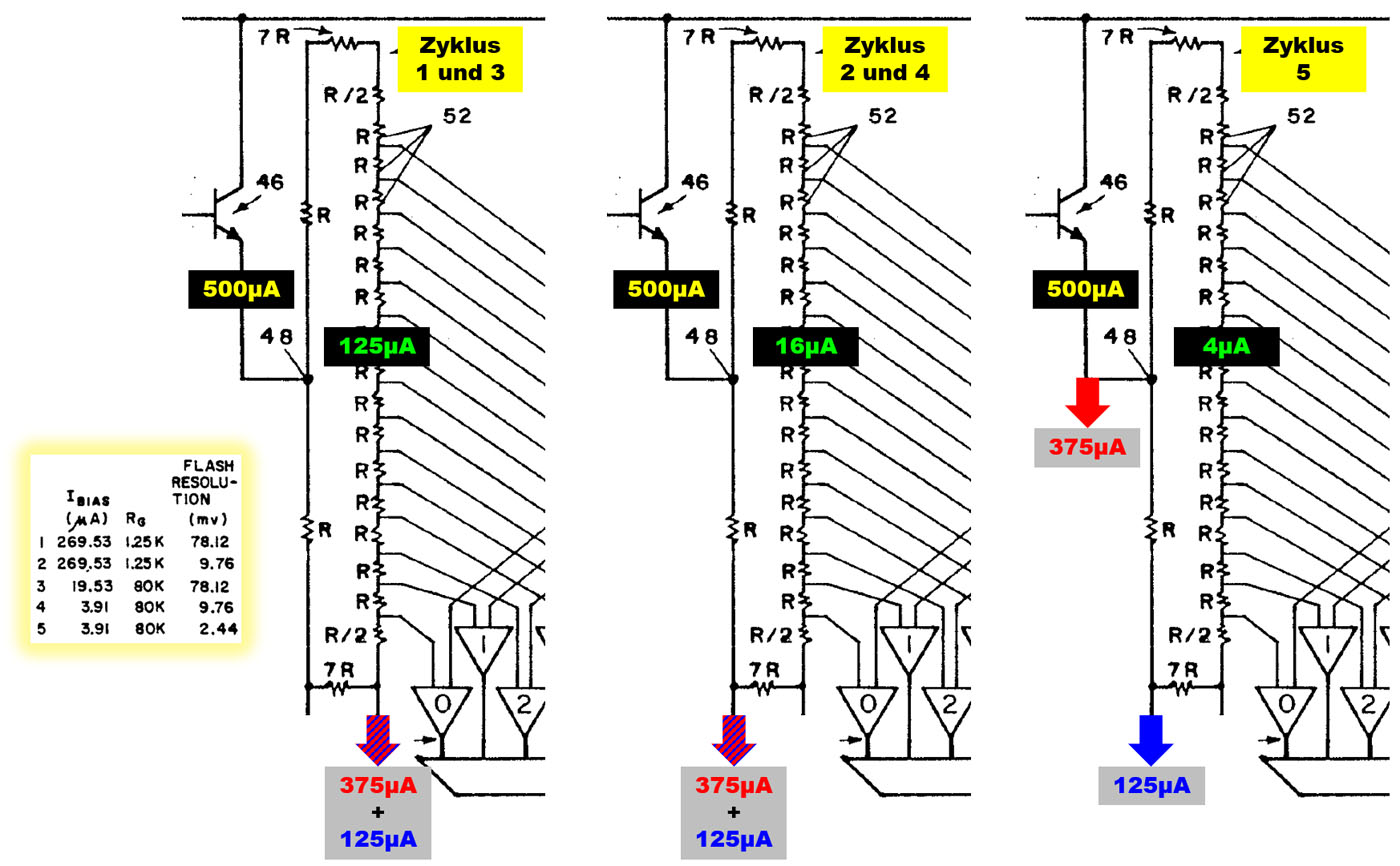

Die Schaltmimik ermöglicht es die Empfindlichkeit des FADCs in drei Stufen zu erhöhen, ohne den Arbeitspunkt des Transistors 46 zu verschieben, der das zu bestimmende Signal einspeist. Im ersten und im dritten Zyklus sind sowohl die 375µA Stromsenke als auch die 125µA Stromsenke an der rechten Seite des 7R-Widerstands angebunden. In der Widerstandskette des FADCs stellt sich entsprechend des Stromteilers ein Strom von 125µA ein. Der Transistor 46 muss den kompletten Strom in Höhe von 500µA liefern.

Im zweiten und vierten Zyklus werden die 375µA- und die 125µA-Stromsenke auf die linke Seite des 7R-Widerstands geschaltet. Durch die Widerstandskette des FADCs fließen dann nur noch 16µA, was einer Erhöhung der Auflösung um einen Faktor 8 entspricht. Durch den Transistor 46 fließt weiterhin ein Strom von 500µA.

Im fünften Zyklus befindet sich nur noch die 125µA-Stromsenke links des Widerstands 7R. Durch die Widerstandskette des FADCs fließt in diesem Zustand ein Strom von 4µA, was einer weiteren Erhöhung der Auflösung um einen Faktor 4 entspricht. Damit sich der Arbeitspunkt des Transistors 46 nicht verschiebt, ist die 375µA-Stromsenke mit dem Knoten 48 verbunden, wo sie den FADC nicht mehr beeinflusst aber den Stromfluss durch den Transistor 46 wieder auf 500µA erhöht.

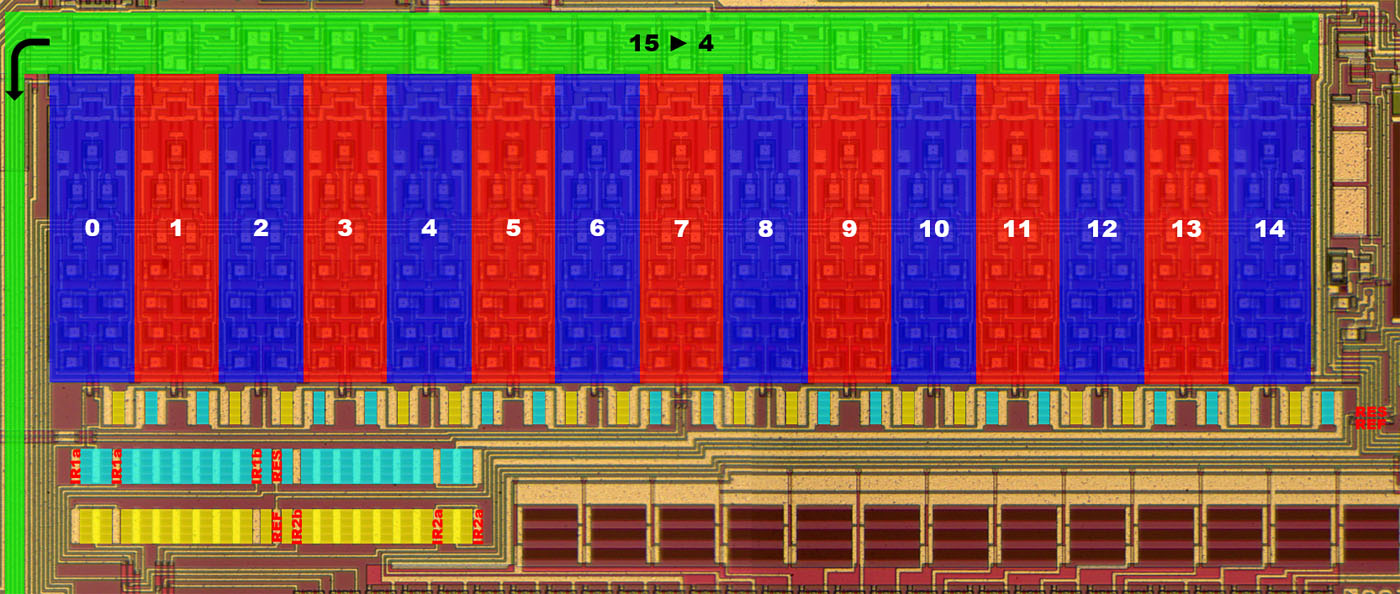

Die zwei Spannungsteiler, die den Komparatoren zugeordnet sind, befinden sich direkt unter den 15 Komparatoren und sind ineinander verwoben, was für die Verschaltung auf dem Die vorteilhaft ist, aber auch dafür sorgt, dass sich die zueinander gehörenden Widerstände der RES- und der REF-Spalte möglichst gleich verhalten. Die Ausgänge der 15 Komparatoren werden in einen 4Bit-Wert umgewandelt und in den Digitalteil übertragen.

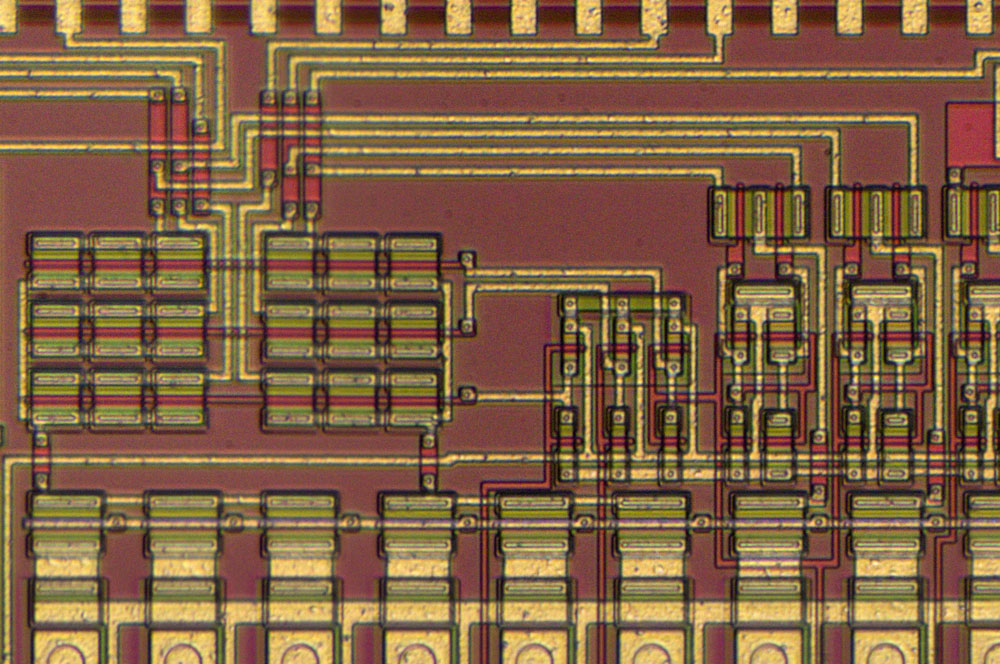

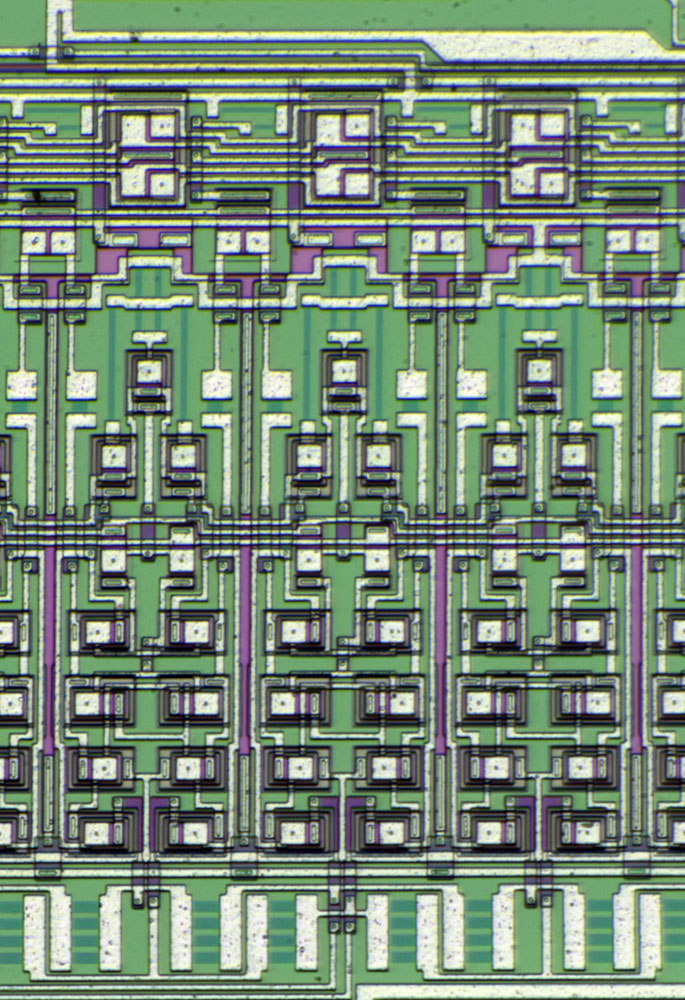

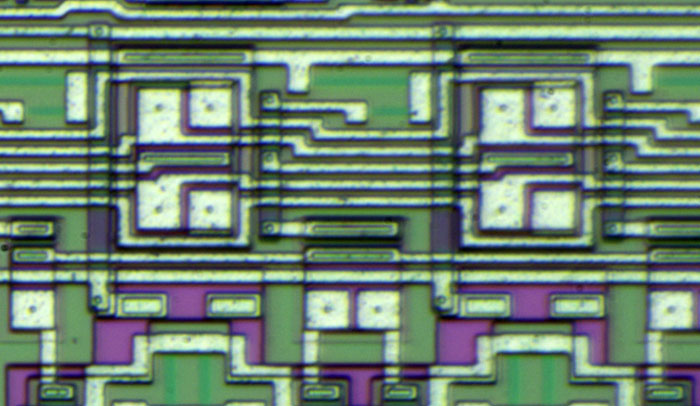

Dieser Bildausschnitt zeigt die Mitte des Komparatorenbereichs, wo die zu wandelnde Spannung eingespeist wird. Zwischen jedem Widerstandspaar kontaktiert der darüber liegende Komparator die dort abfallende Spannung.

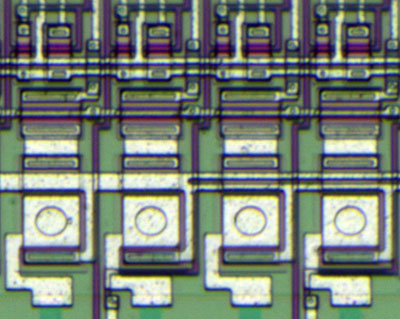

Die Komparatoren sind äußerst symmetrisch aufgebaut und von Isolationsgräben umgeben.

Die differentiellen Ausgänge der Komparatoren sind miteinander verknüpft. Es steuern immer zwei Komparatoren gemeinsam eine der kleinen Schaltungen auf dem 4 Bit breiten Datenbus an.

Die Verknüpfung ist notwendig, damit immer nur die Schaltung auf dem Datenbus aktiv wird, die sich zwischen den Komparatoren mit unterschiedlichen Ausgangspegeln befindet. Durch die Verknüpfung der Ausgänge ergibt sich genau an einer Stelle ein doppelter Low-Pegel, der die darüber liegende Schaltung aktiviert, die wiederum den gewünschten 4Bit-Wert auf den Bus legt.

Die vier Datenleitungen durchlaufen in allen 15 Schaltungen vier Emitterflächen, die die jeweilige Datenleitung auf einen High-Pegel ziehen können. Im Detail ist zu erkennen, dass nicht jedes Metallquadrat mit dem darunter liegenden Emitter verbunden ist. Durch den Wechsel der Durchkontaktierungen ergibt sich der für die jeweilige Schaltung gewünschte 4Bit-Wert.

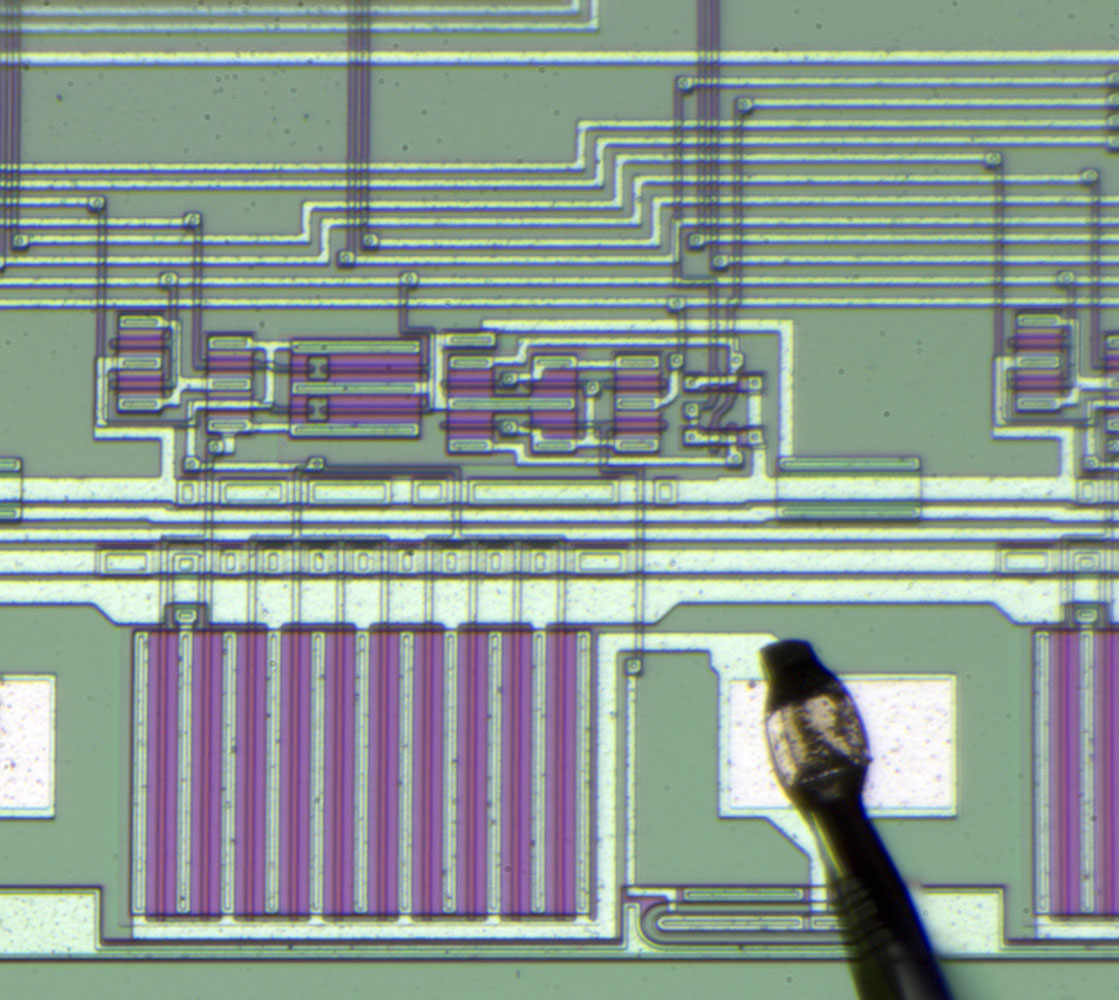

Der Digitalteil des AD679 nimmt eine etwas größere Fläche auf dem Die ein als der Analogteil. Die Strukturen sind groß genug, damit man alle logischen Funktionen analysieren könnte. Im Vergleich zum möglichen Erkenntnisgewinn ist der Aufwand allerdings relativ hoch.

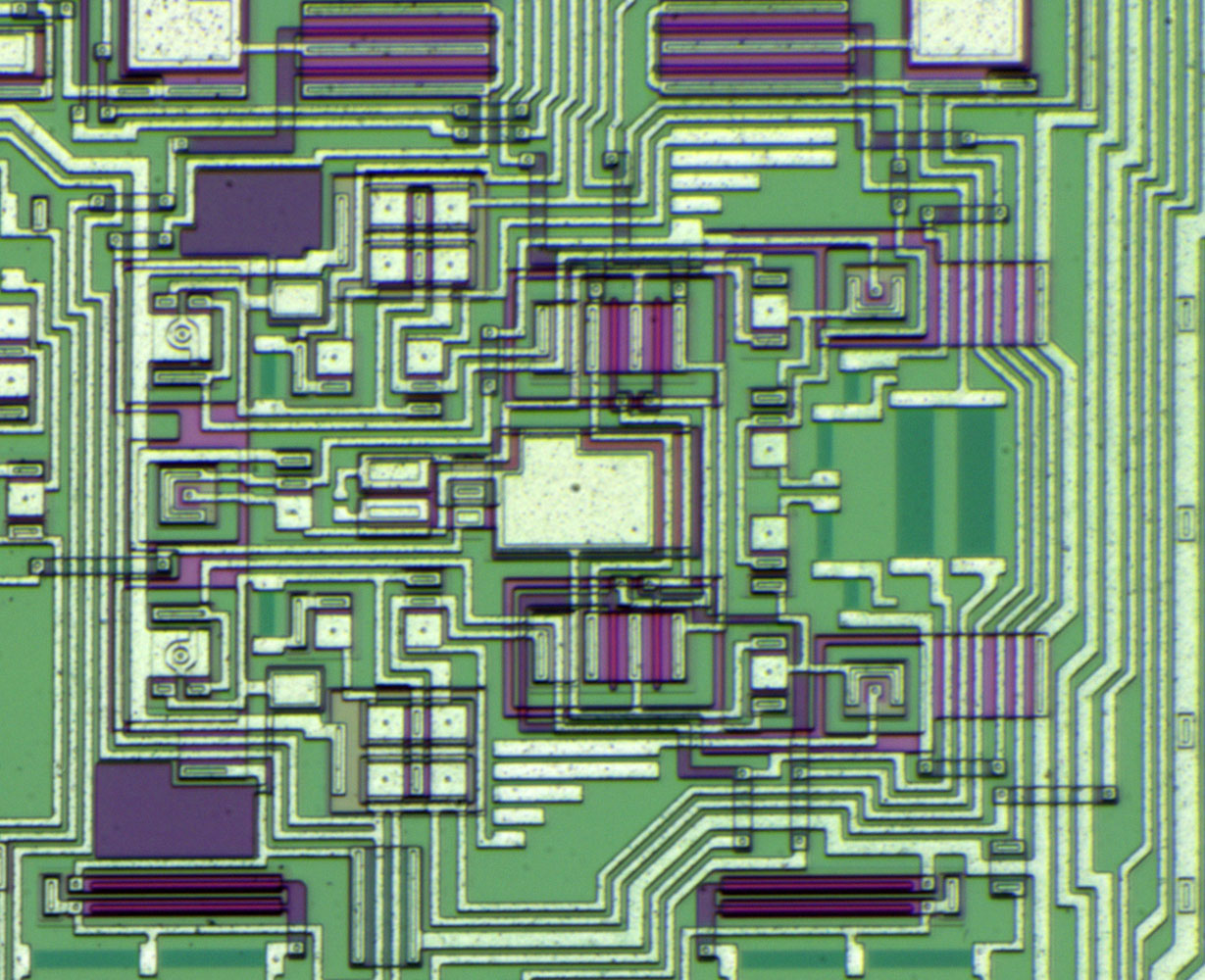

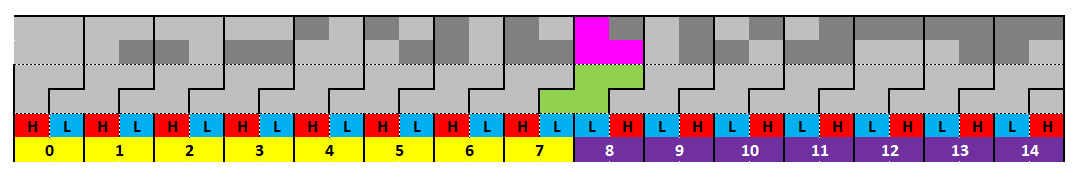

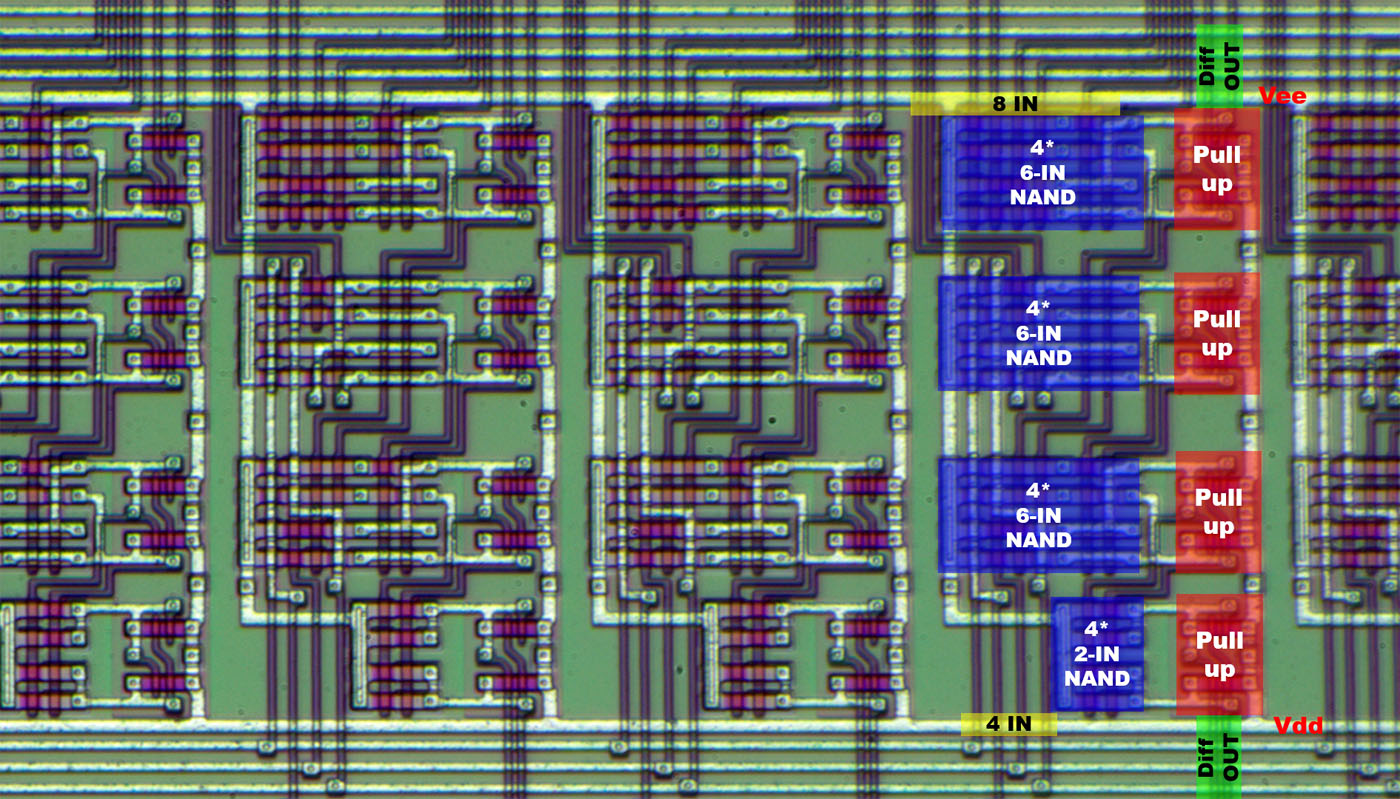

Die Logik besteht aus einzelnen Modulen, die sich zum Großteil stark ähneln. Hier ist ein Teil des unteren Bereichs zu sehen. Es wurde nicht auf den klassischen, zeilenförmigen Gatearray-Aufbau zurückgegriffen, wie man ihn zum Beispiel im DAC709 findet. Stattdessen hat man Blöcke mit mehreren großen NAND-Gattern gebildet. Da man nicht auf eine universelle Architektur angewiesen war, konnte man die in diesem Fall idealen Grundbausteine wählen.

Der hier herausgearbeitete Block besitzt an der Oberseite acht und an der Unterseite vier Eingänge. Dazu kommt ein differentieller Ausgang an der Oberseite und ein weiterer auf der Unterseite. Innerhalb des Schaltungsblocks sind insgesamt zwölf NAND-Gatter mit sechs Eingängen und vier NAND-Gatter mit zwei Eingängen integriert. Es können allerdings nicht alle Gatter beliebig genutzt werden, da sich die NAND-Gruppen die Gateelektroden teilen und sie jeweils nur eine Pull-Up-Strukturen besitzen. Effektiv enthält jeder Block folglich drei NAND-Gatter mit sechs Eingängen und ein NAND-Gatter mit zwei Eingängen. Die logischen Verknüpfungen der Blöcke lassen sich über die Verdrahtung in der Polysilizium- und der Metalllage bestimmen.

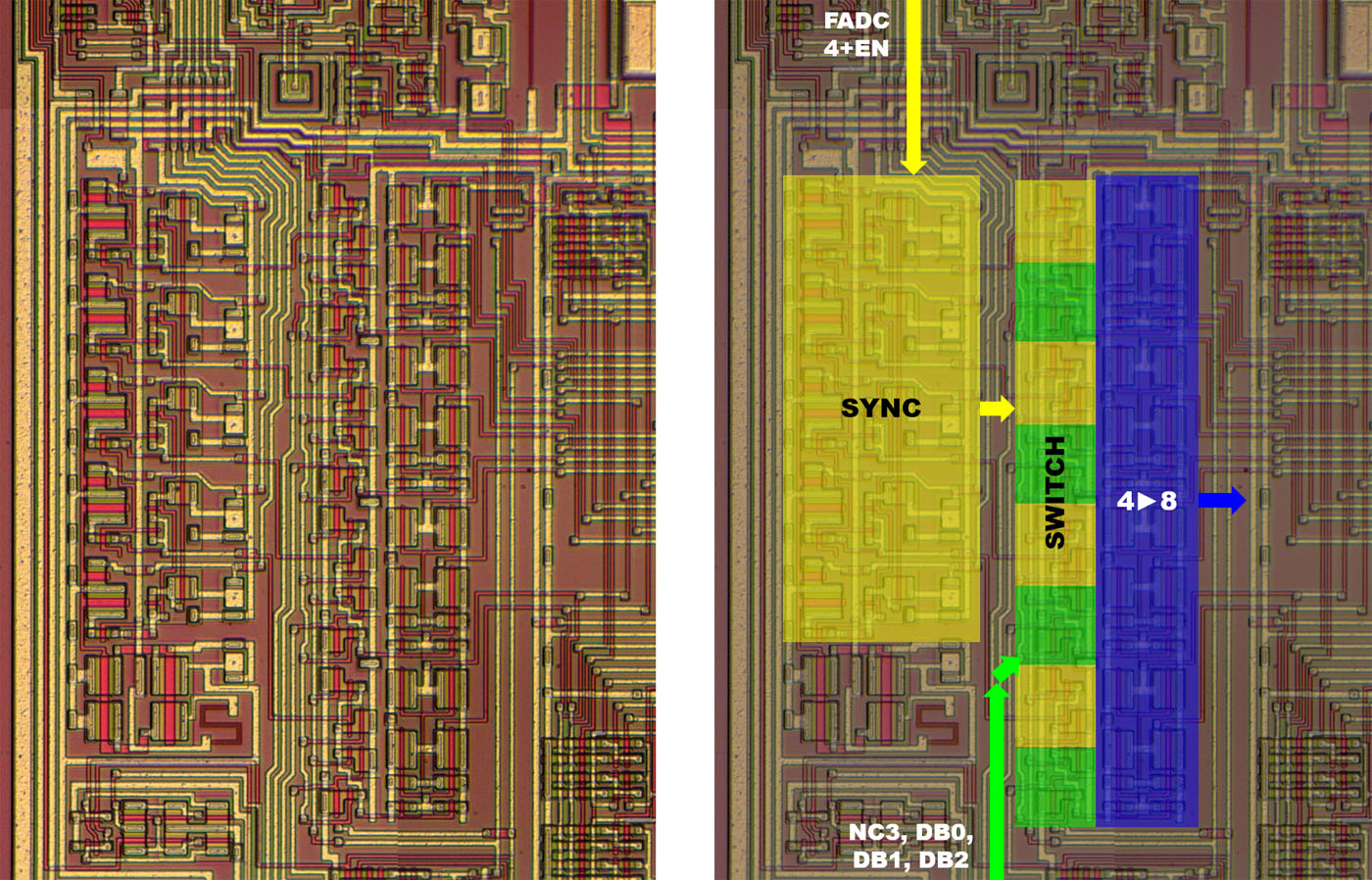

Ein auffälliger Bereich ist die Zuführung des FADC-Ausgangs. Der 4Bit breite Bus wird zuerst auf irgendeine Art synchronisiert beziehungsweise freigegeben (gelb), durchläuft dann einen Umschalter (gelb/grün) und wird dann in differentielle Signale gewandelt (blau). Interessant ist dabei, dass der Umschalter es ermöglicht statt der Signale des FADCs die Potentiale der Bondpads NC3, DB0, DB1 und DB2 in die Logik einzuspeisen. Für die grundsätzliche Funktion des ADCs scheint diese Umschaltung nicht notwendig zu sein. Vielleicht handelt es sich um eine integrierte Testfunktion, die während der Produktion genutzt wird.

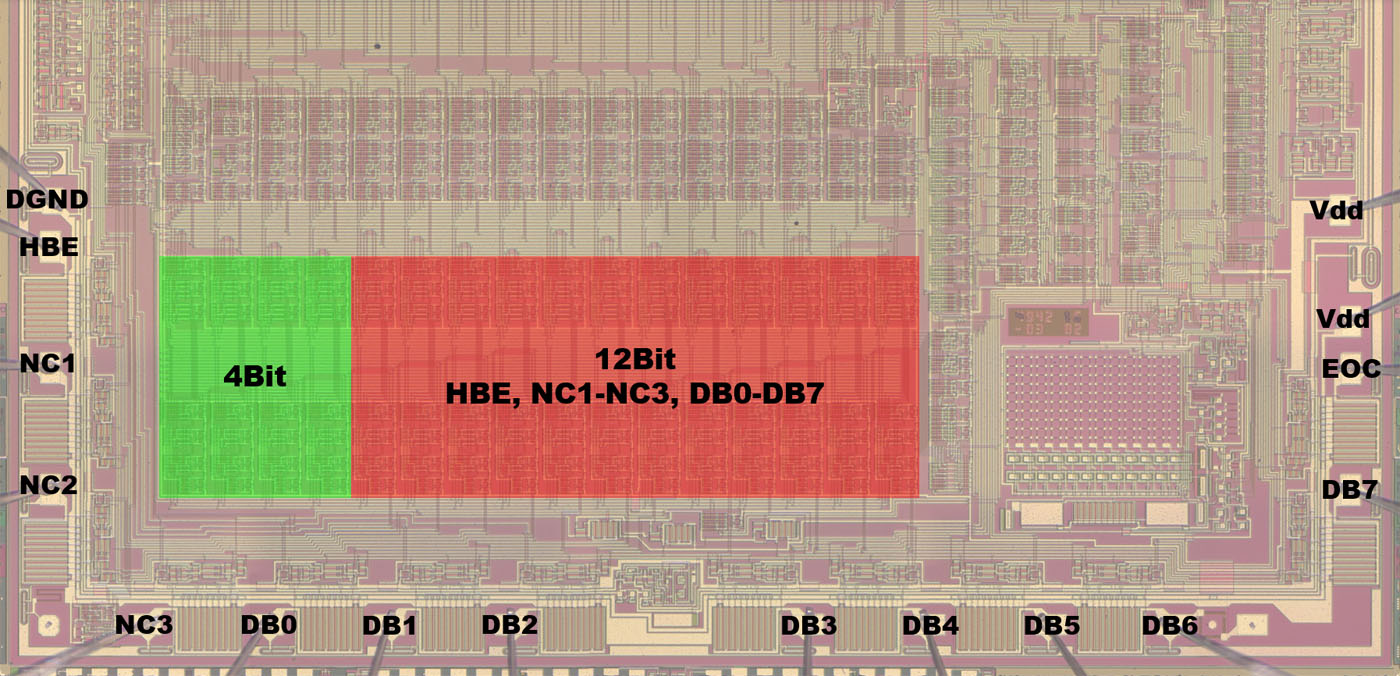

Im unteren Bereich sind 16 gleiche Bereiche zu erkennen. Die rechten 12 Elemente (rot) sind an die Bondpads HBE, NC1-NC3 und DB0-DB7 angebunden. Links der 12 Elemente befinden sich 4 gleich aufgebaute Bereiche (grün) ohne eine Verbindung zu einem Bondpad. Man kann davon ausgehen, dass im roten Bereich die 12Bit der ersten vier Wandlungszyklen abgespeichert werden und im grünen Bereich dann noch die letzten vom FADC gelieferten 4Bit landen. Es muss sich hier um Speicherzellen mit einer Schieberegisterfunktion handeln, damit der 14Bit breite Digitalwert über die 8Bit breite Datenschnittstelle ausgegeben werden kann. Im AD678 können dann die oberen 12Bit direkt zu den jeweiligen Pins geleitet werden.

Wie die Unterscheidung zwischen AD678 und AD679 erfolgt, ist nicht zu erkennen. Wahrscheinlich müssen beim Abgleichprozess lediglich ein paar Verbindungen aufgetrennt werden. Schließlich muss man die Logik nur dazu bringen den fünften Zyklus nicht auszuführen und die 12Bit (abhängig vom Status des 12/8-Pins) direkt über die vorhandenen Pins auszugeben. So hätte man außerdem die Möglichkeit während des Abgleichs qualitativ schlechtere Dies in AD678 umzuwandeln und entsprechend die Ausbeute zu erhöhen.

In der rechten unteren Ecke des Dies befindet sich ein ungewöhnlicher Schaltungsteil. Obwohl man davon ausgehen kann, dass der Bereich zum Digitalteil zählt, befindet sich hier ein großes, abgeglichenes Array aus Widerständen. Dem Aufbau und den umgebenden Strukturen nach scheint es sich um den internen Oszillator zu handeln. Die Taktfrequenz derartiger RC-Oszillatoren unterliegt großen Toleranzen. Gleichzeitig laufen im AD679 bei einer Digitalwandlung verhältnismäßig viele Funktionen ab. Die Taktfrequenz muss niedrig genug sein, damit die Einschwingzeiten der verschiedenen Schaltungsteile eingehalten werden. Die Taktfrequenz muss aber gleichzeitig möglichst hoch sein, damit die Digitalwandlung ausreichend schnell abläuft. Mit diesem Hintergrund ist eine Feineinstellung der Taktfrequenz durchaus sinnvoll.