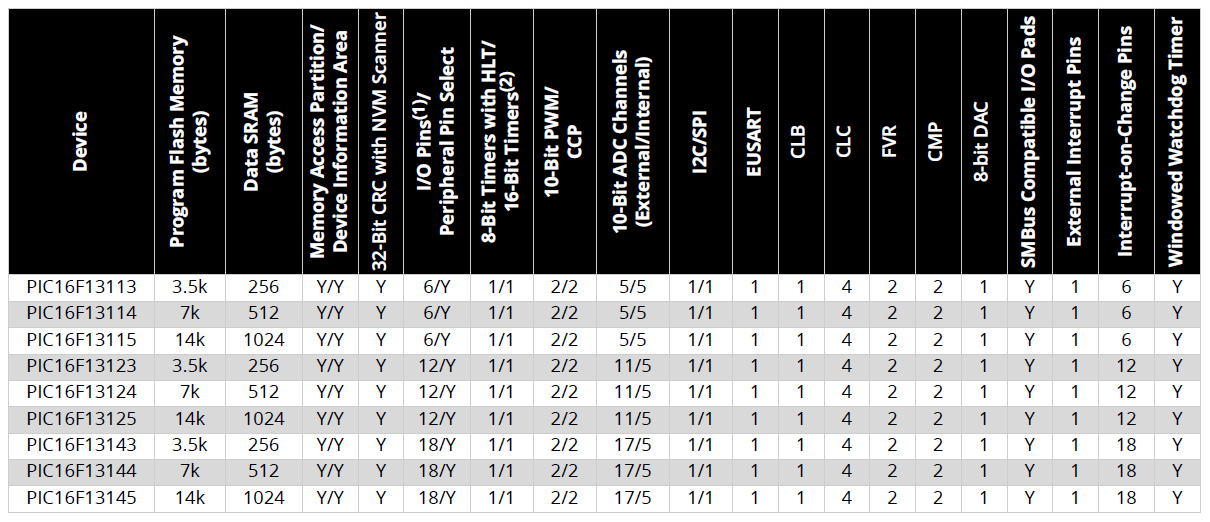

Der Microchip PIC16F13145 gehört zu einer Familie von Mikrocontrollern, die mit einem Arbeitstakt von 32MHz arbeiten, bis zu 14kB Flash-EEPROM und bis zu 1024B SRAM enthalten.

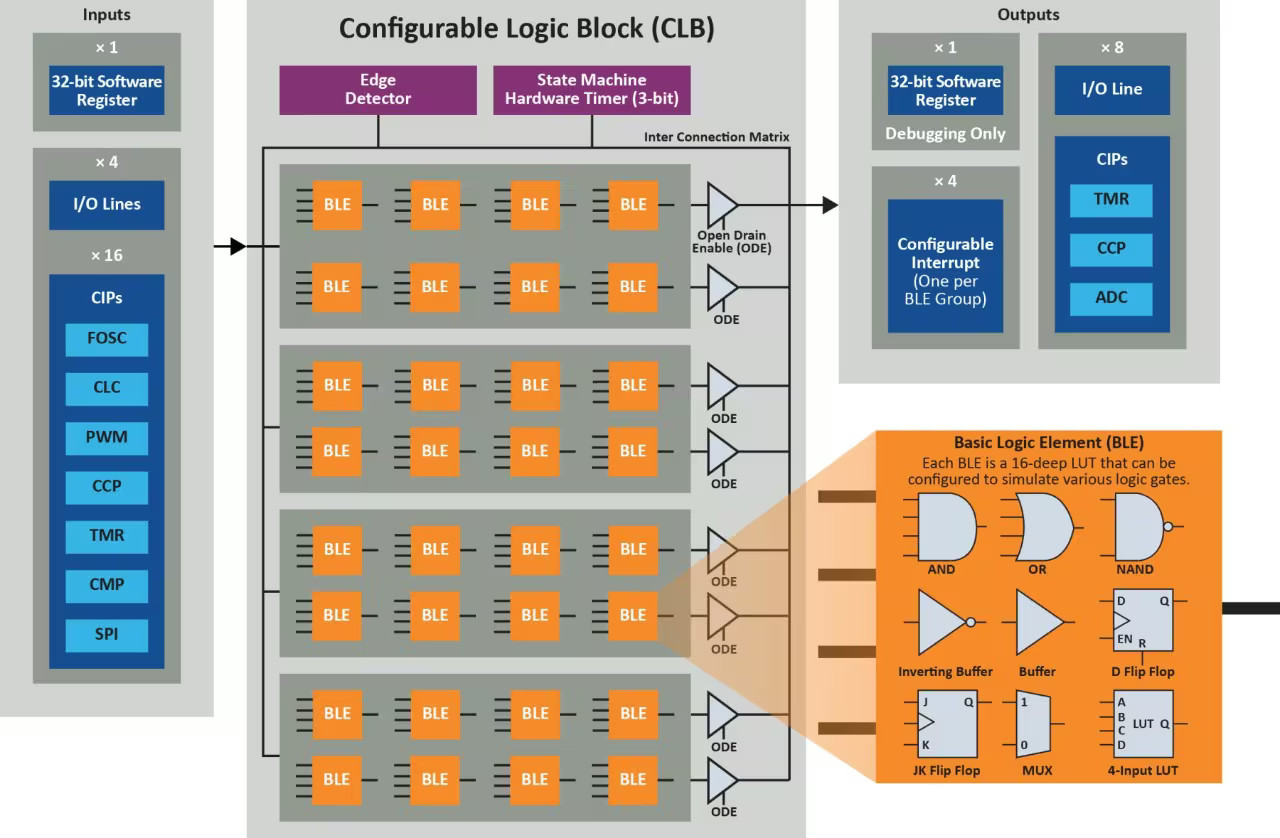

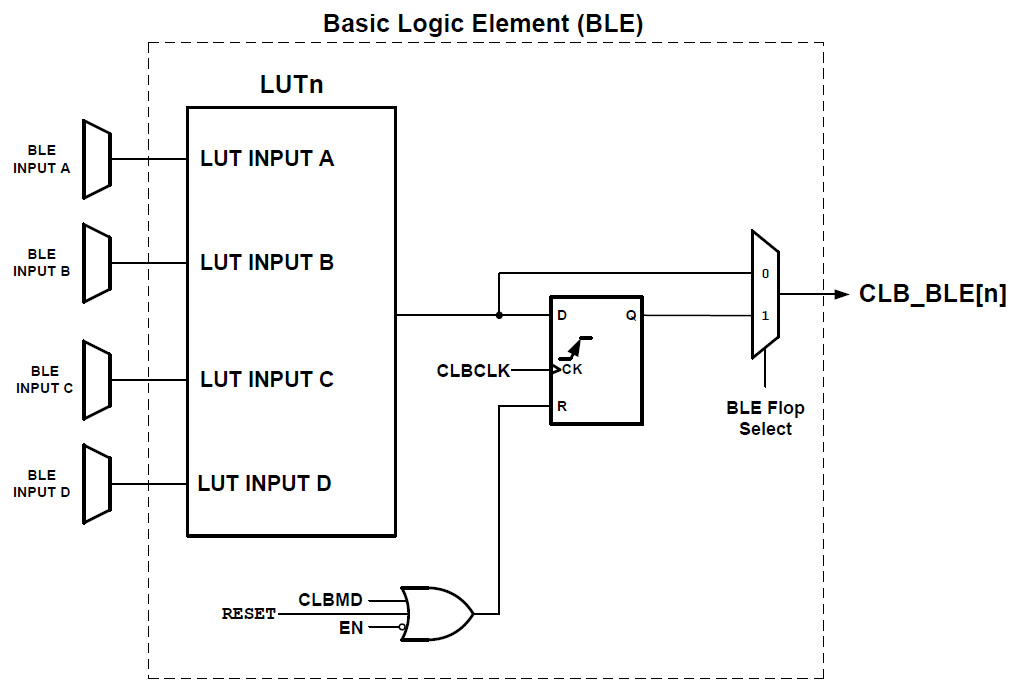

Als Besonderheit bietet der PIC16F13145 konfigurierbare Logikblöcke, ähnlich einem CPLD. Dort kann der Anwender zeitkritische Funktionen implementieren. Ein sogenannter "Configurable Logic Block" (CLB) besteht aus 32 "Basic Logic Elements" (BLE).

Jedes BLE besitzt vier Eingänge, eine Lookup-Tabelle, die die logische Funktion dieses Elements definiert und ein Flip-Flop.

Im Gehäuse findet sich ein Die mit den Abmessungen 2,1mm x 1,9mm.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 20MB

Neben dem Microchip Copyright sind die Maskenrevisionen der Metalllagen abgebildet. 59F07 scheint eine interne Projektbezeichnung zu sein.

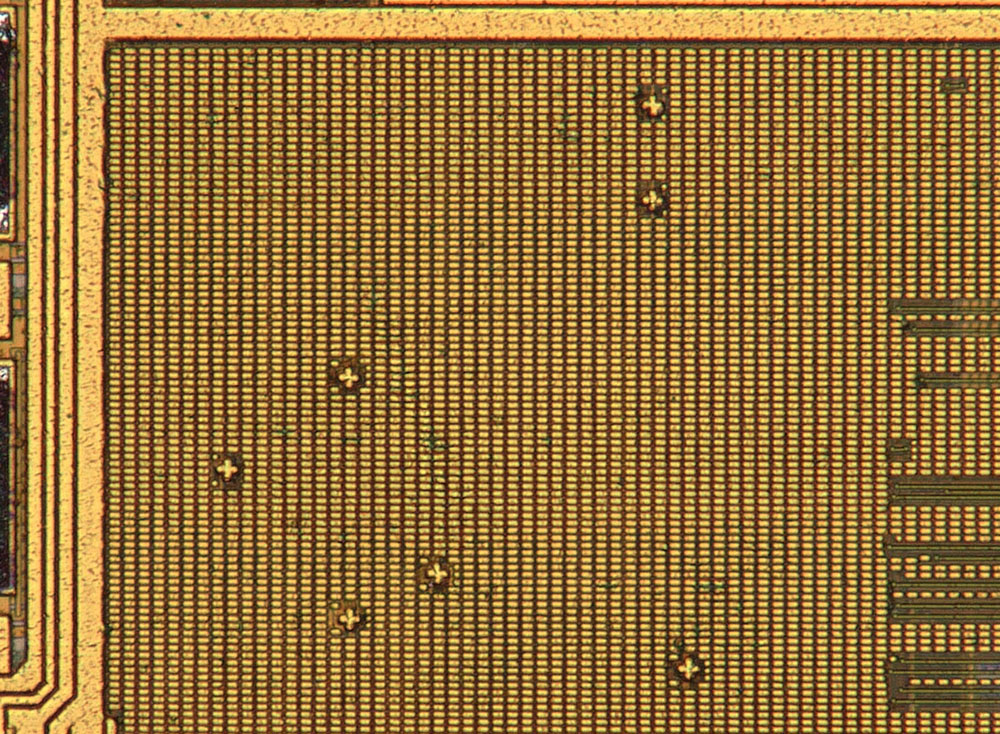

Die kleinen Kreuze innerhalb der Dummystrukturen sind höchstwahrscheinlich Kontakte, die selbstverständlich nicht ohne Weiteres kontaktiert werden können. Sie erleichtern es aber bei einer Fehlersuche tiefer liegende Potentiale zu erreichen. Man muss dann lediglich die Passivierungsschicht öffnen und evtl. mit einem FIB ein Testpad aufbauen. Wie so etwas aussehen kann, ist im Rahmen des Philips QU2AGC1 dokumentiert. Ohne die vorbereiteten Kontakte müsste man nicht nur die Passivierungsschicht entfernen, sondern zusätzlich auch noch eine oder mehrere Metalllagen kontrolliert öffnen. Eventuell durchtrennte Leitungen müsste man dann neben dem Freischnitt wieder verbinden. Danach kann man das benötigte, tief liegende Potential kontaktieren und isoliert nach oben führen.

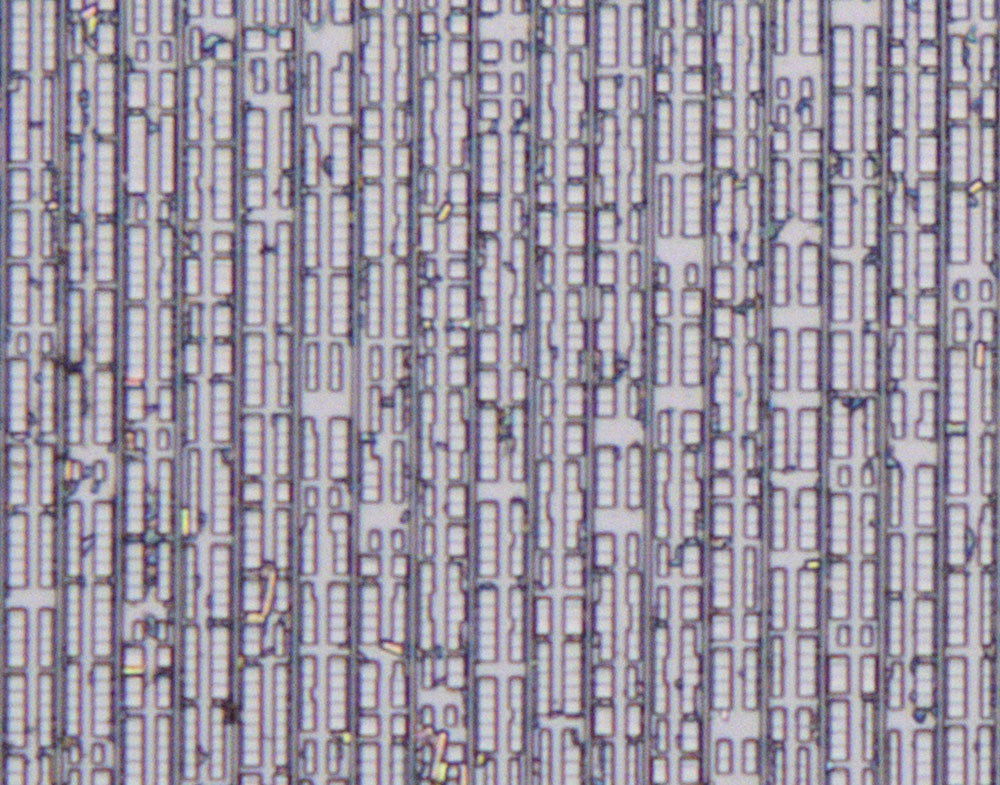

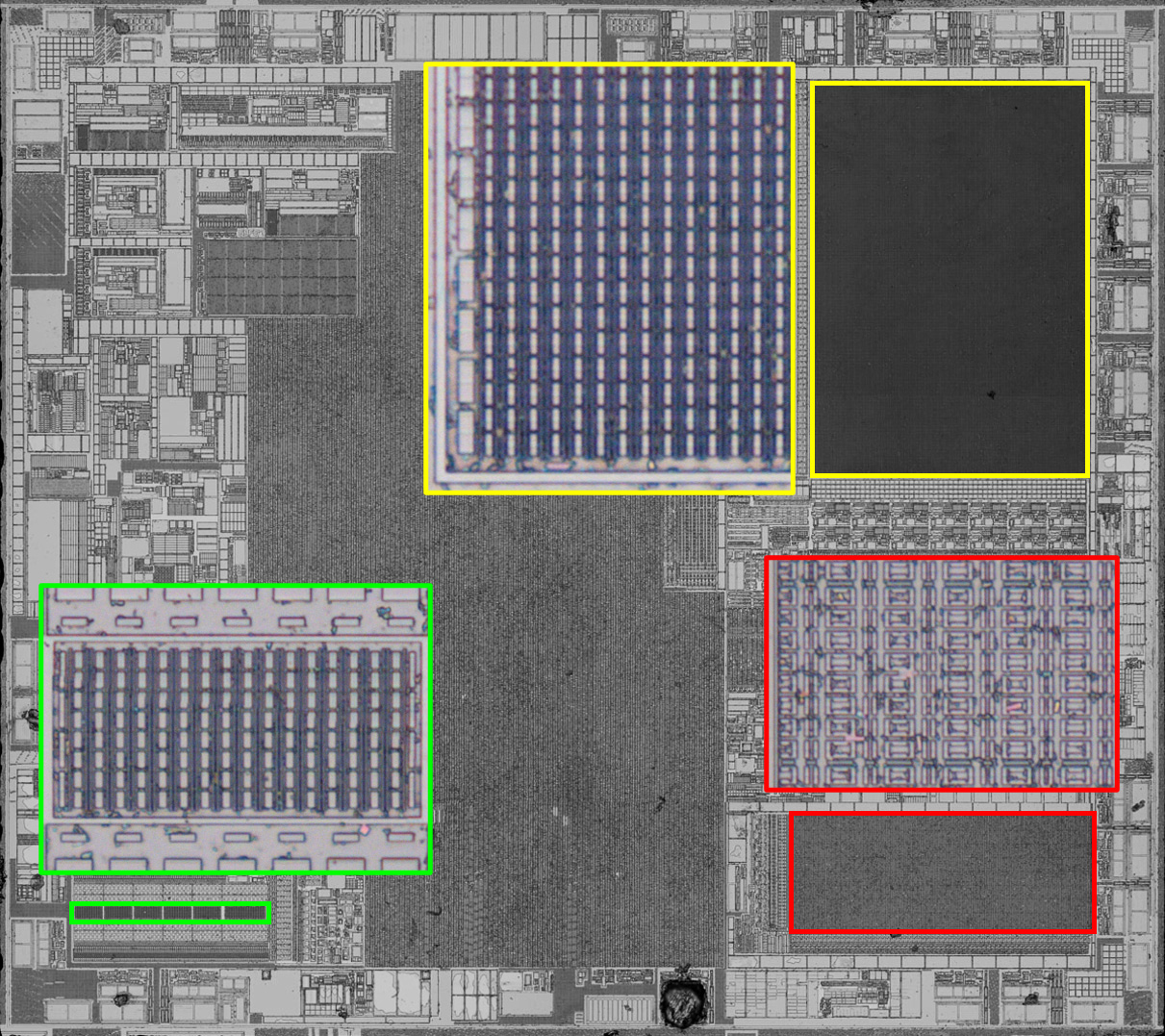

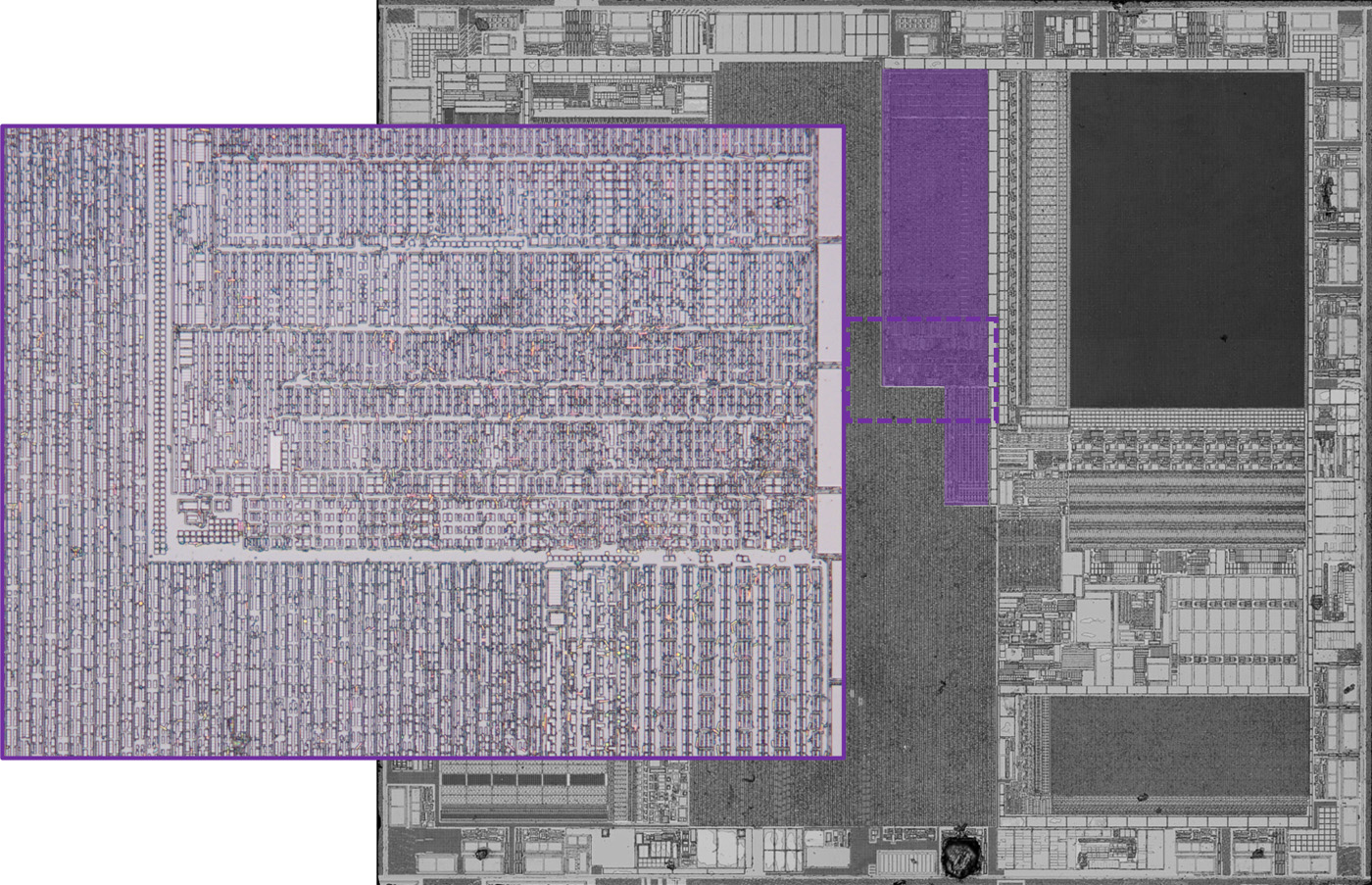

Entfernt man die oberen Lagen, so kann man einige Bereiche ihrer Funktionen zuordnen.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 60MB

Die große, oberflächlich gleichmäßige Fläche in der Mitte des Dies enthält die Steuerungslogik. Im Detail sind die typischen, unterschiedlich großen Transistorbereiche zu erkennen, die die Grundlage für die einzelnen Logikgatter darstellen.

Insgesamt finden sich drei größere Speicherbereiche. Der Block in der rechten unteren Ecke enthält typische SRAM-Strukturen (rot). Der sehr große Block in der oberen rechten Ecke stellt den Flash-EEPROM dar (gelb). Interessant ist der Block in der linken unteren Ecke (grün). Hierbei scheint es sich um einen zweiten, kleineren EEPROM zu handeln. Wahrscheinlich haben diese Speicherzellen spezielle Eigenschaften.

Die konfigurierbaren Logikblöcke kann man nicht eindeutig identifizieren. Auf Grund der Größe kommt eigentlich nur ein Bereich dafür in Betracht. Dort sind die Strukturen deutlich gleichmäßiger als in der Steuerungslogik, was zu einem konfigurierbaren Logikarray passen würde.