Das Batteriemanagementsystem BQ41Z50 ist eine Weiterentwicklung des BQ40Z50.

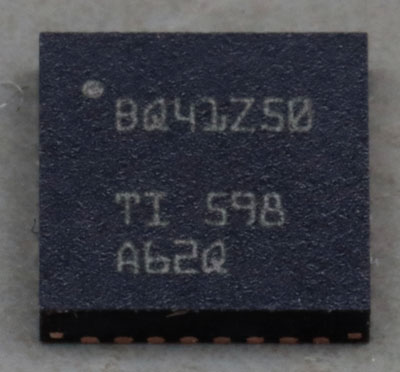

Das Datenblatt enthält ein Blockschaltbild, das dem Blockschaltbild des BQ40Z50 sehr ähnlich ist.

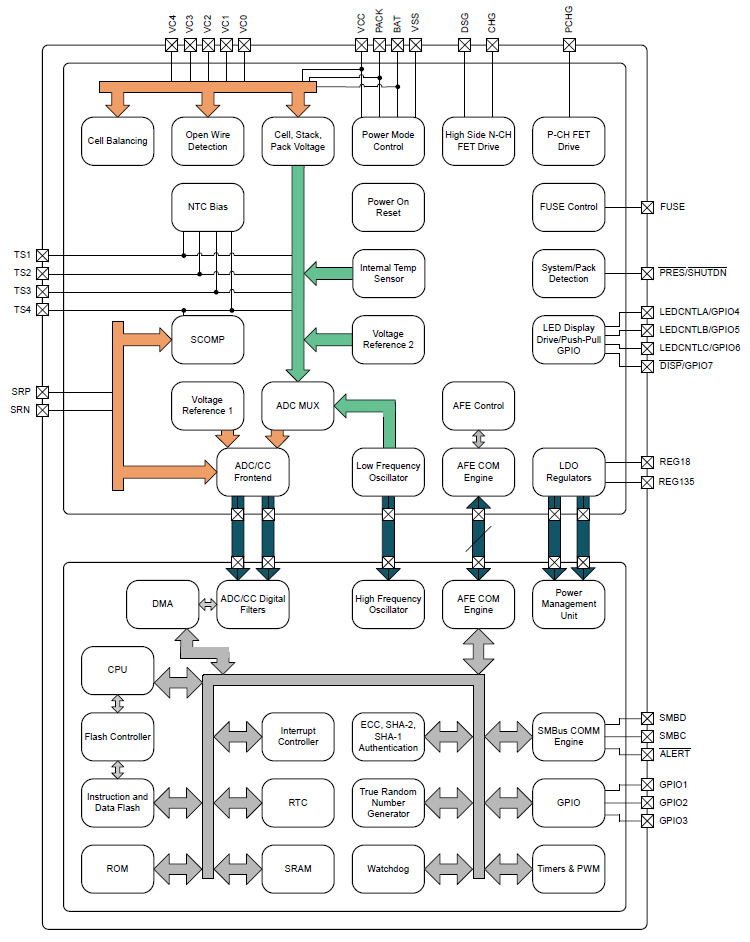

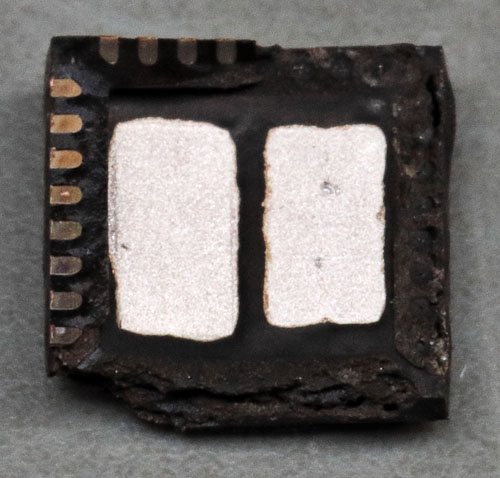

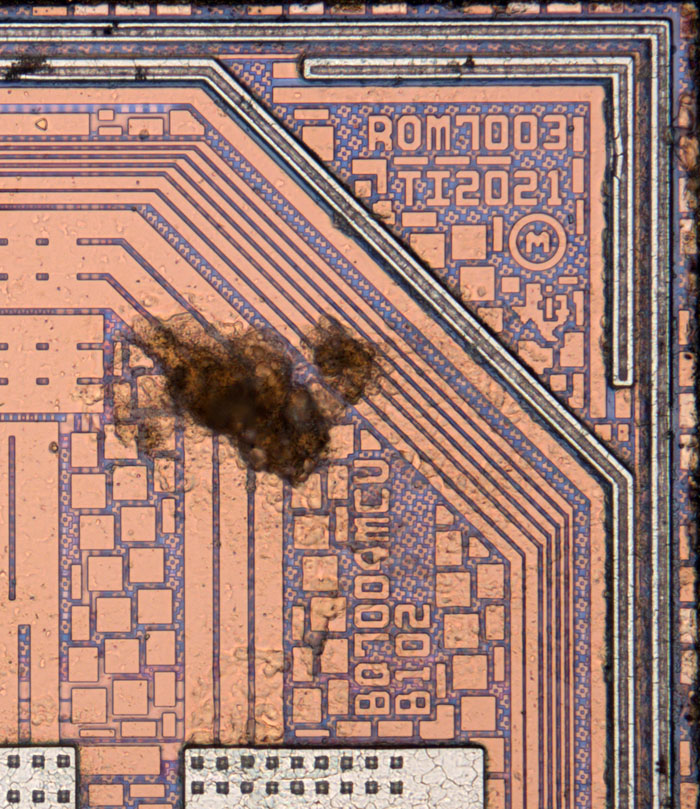

Im Gehäuse befinden sich zwei nebeneinander platzierte Dies.

Das Die, welches das analoge Frontend darstellt, ist 2,30mm x 1,15mm groß. Im rechten Bereich ist ein großer Logikblock zu erkennen. An der unteren Kante scheinen Treibertransistoren für die externen MOSFETs integriert zu sein.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 31MB

Das Design stammt aus dem Jahr 2021. Sowohl das Texas Instruments Logo als auch das Benchmarq Microelectronics Logo wurde auf dem Die abgebildet. Die interne Bezeichnung lautet BQ7004AFEA1. Rechts oben sind die Revisionen von drei Metalllagen abgebildet.

Hier ist das Substrat des analogen Frontends zu sehen. Die Strukturen zeigen nichts Überraschendes.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 40MB

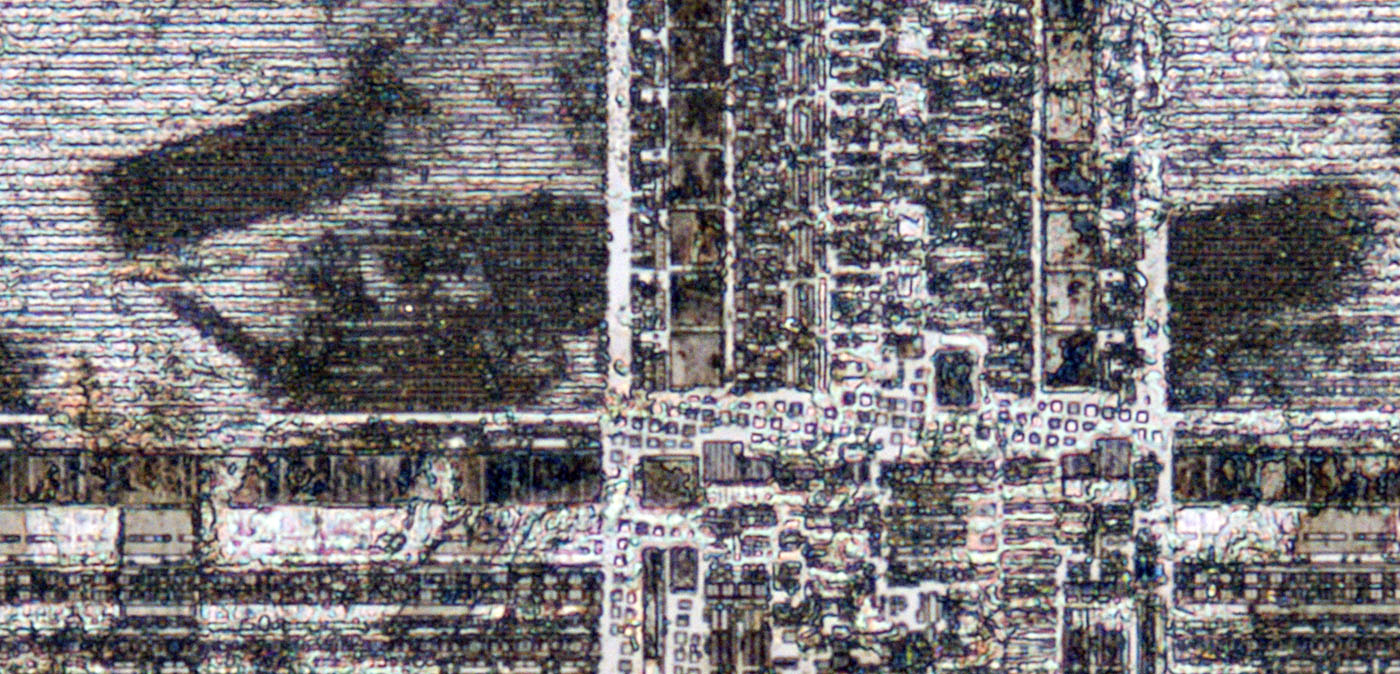

Das zweite Die enthält den Prozessor, die Speicherbereiche und diverse zusätzliche Schaltungsteile. Die Abmessungen betragen 2,16mm x 1,07mm. Die oberste Metalllage dient offenbar hauptsächlich der Spannungsversorgung.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 27MB

Dieser integrierte Schaltkreis wurde 2021 entwickelt. Hier ist nur noch das Texas Instruments Logo abgebildet. Die interne Bezeichnung lautet BQ7004MCUB102. Die Zeichenfolge ROM7003 lässt vermuten, dass zumindest ein Teil des Programms in Hardware abgebildet ist.

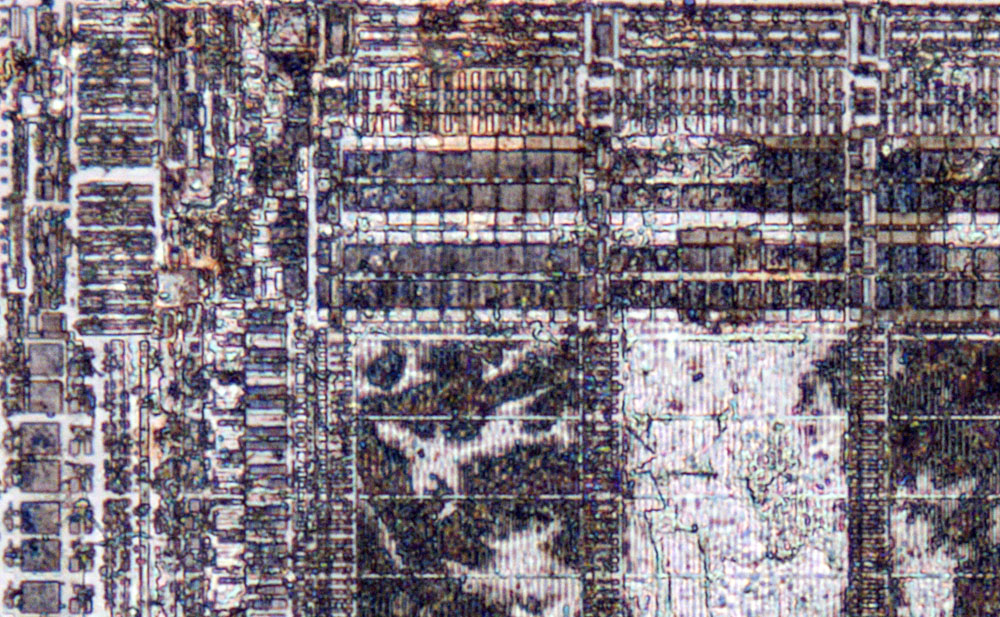

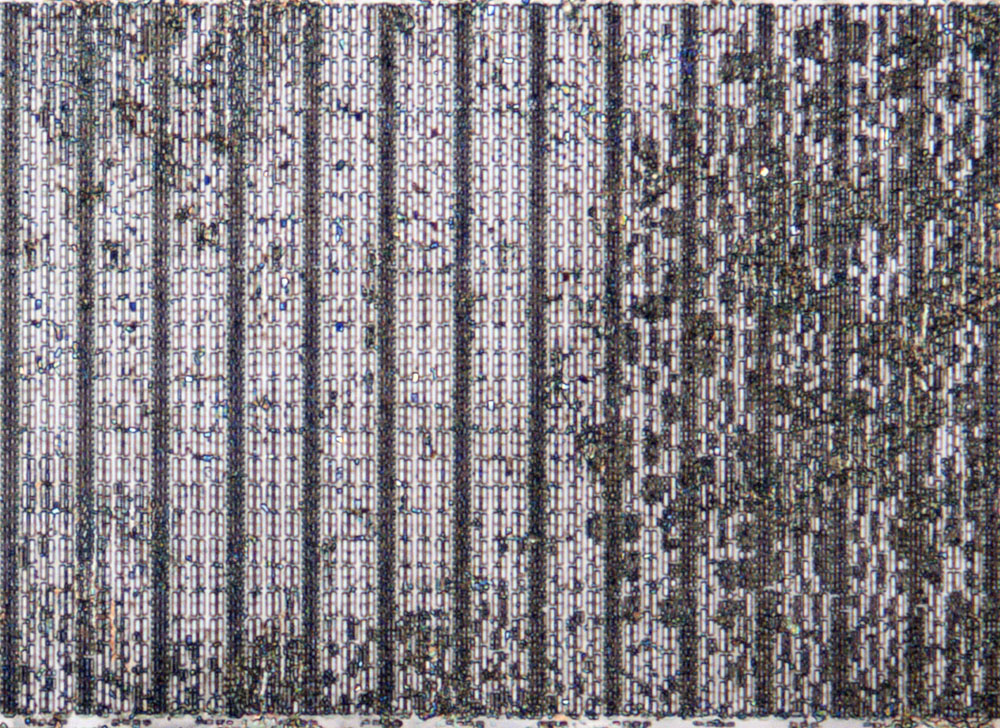

Das Substrat des digitalen Schaltkreises lässt sich nicht ganz sauber freilegen. Oft sind es spezielle Barrierelagen, die sich nicht ohne Weiteres auflösen.

Auf dem Substrat stechen vor allem drei Speicherblöcke ins Auge. Ein Großteil der umgebenden Fläche ist mit Logikschaltungen aufgefüllt. Die Strukturen im linken Bereich sind unregelmäßiger. An der unteren Kante liegen die Ein- und Ausgangsbeschaltungen der Bondpads nebeneinander.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 38MB

Der große Speicherblock links der Mitte scheint ein EEPROM zu sein.

Der Speicher rechts der Mitte besteht aus vier Blöcken. Die einzelnen Speicherzellen sind nicht zu erkennen. Die Architektur lässt vermuten, dass es sich um einen SRAM handelt.

Der rechte, kleinere Speicherblock könnte ein weiterer EEPROM sein. Die Strukturen unterscheiden sich aber etwas von dem EEPROM links der Mitte.

Der Logikbereich besitzt einige Flächen, in denen keine Schaltungen integriert wurden. Die restlichen Flächen erscheinen wie üblich für derartige Logik chaotisch.