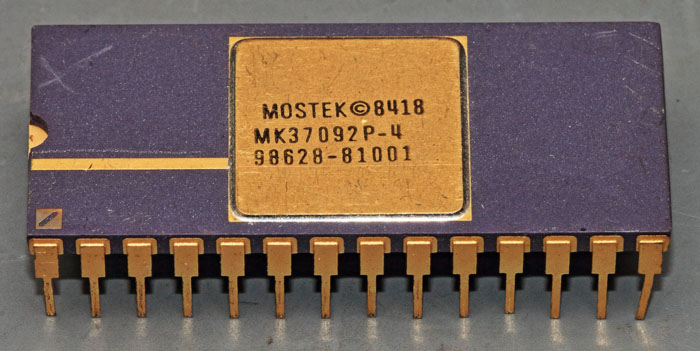

Der MOSTEK MK37092 ist ein maskenprogrammiertes NMOS-ROM. MK steht für die Standard-Bauteile von MOSTEK, MKB und MKI sind Bauteile, die für einen erweiterten Temperaturbereich spezifiziert sind. Die Zahl 3 steht für die Kategorie ROM und EPROM. Die Zahl 7 tragen die Varianten mit einer Speichertiefe von 8kB und ein Package mit 28 Pins. Das keramische DIL-Gehäuse ist mit dem Buchstaben P spezifiziert. Der Index 4 markiert die schnellere Variante des Bausteins. Die Bedeutung der Zahlen 092 erklärt das Datenblatt nicht. Wie sich noch zeigen wird, stehen die Zahlen höchstwahrscheinlich für den programmierten Inhalt, also die spezifische Maske.

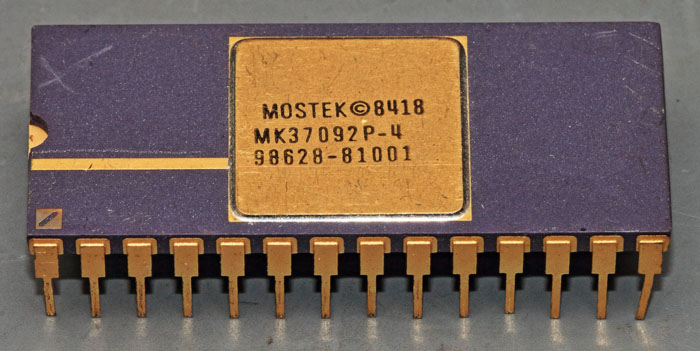

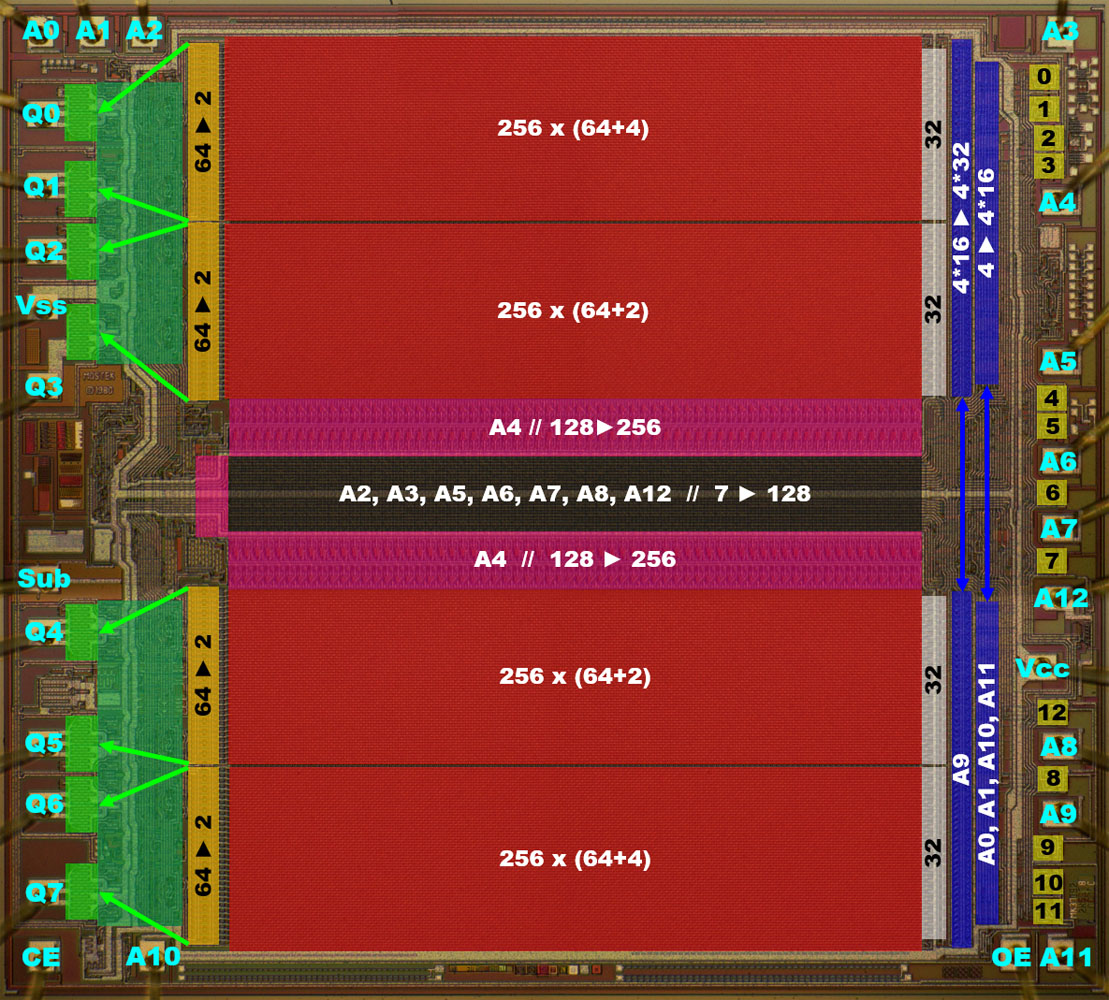

Das Datenblatt zeigt die Funktionsweise des ROMs. Der Kern ist eine 65.536Bit große Speichermatrix. Acht Leitungen des 12Bit breiten Adressbus wählen eine von 256 Spalten aus. Ausgegeben werden 32 Datenleitungen, die mit den restlichen vier Adressleitungen auf einen 8Bit breiten Datenbus reduziert werden. Der Eingang OE ermöglicht es die Ausgangstreiber zu deaktivieren. Über den Eingang CE lässt sich das ROM in einen stromsparenden Standby-Modus schalten.

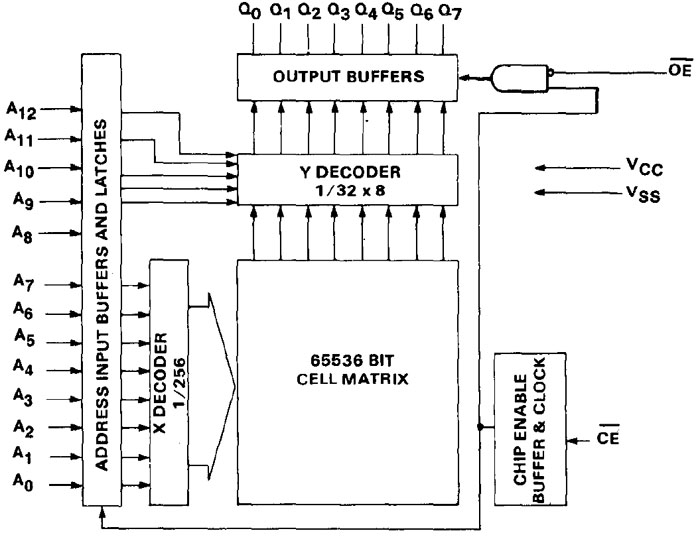

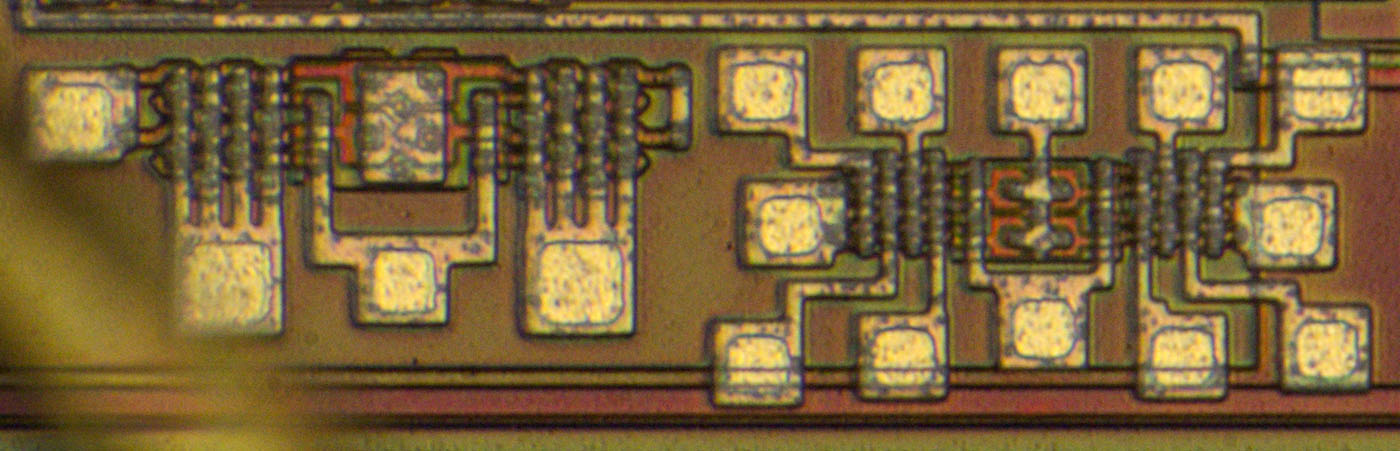

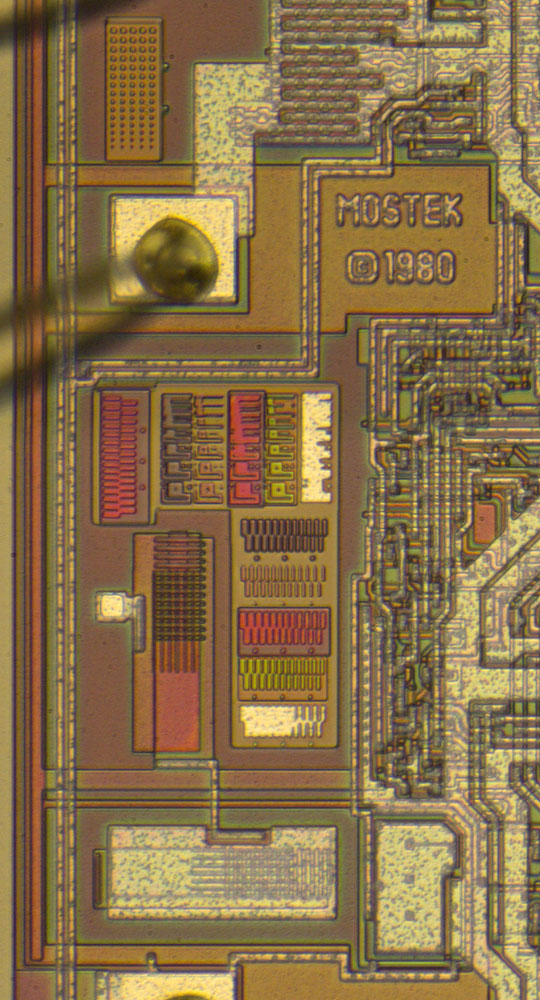

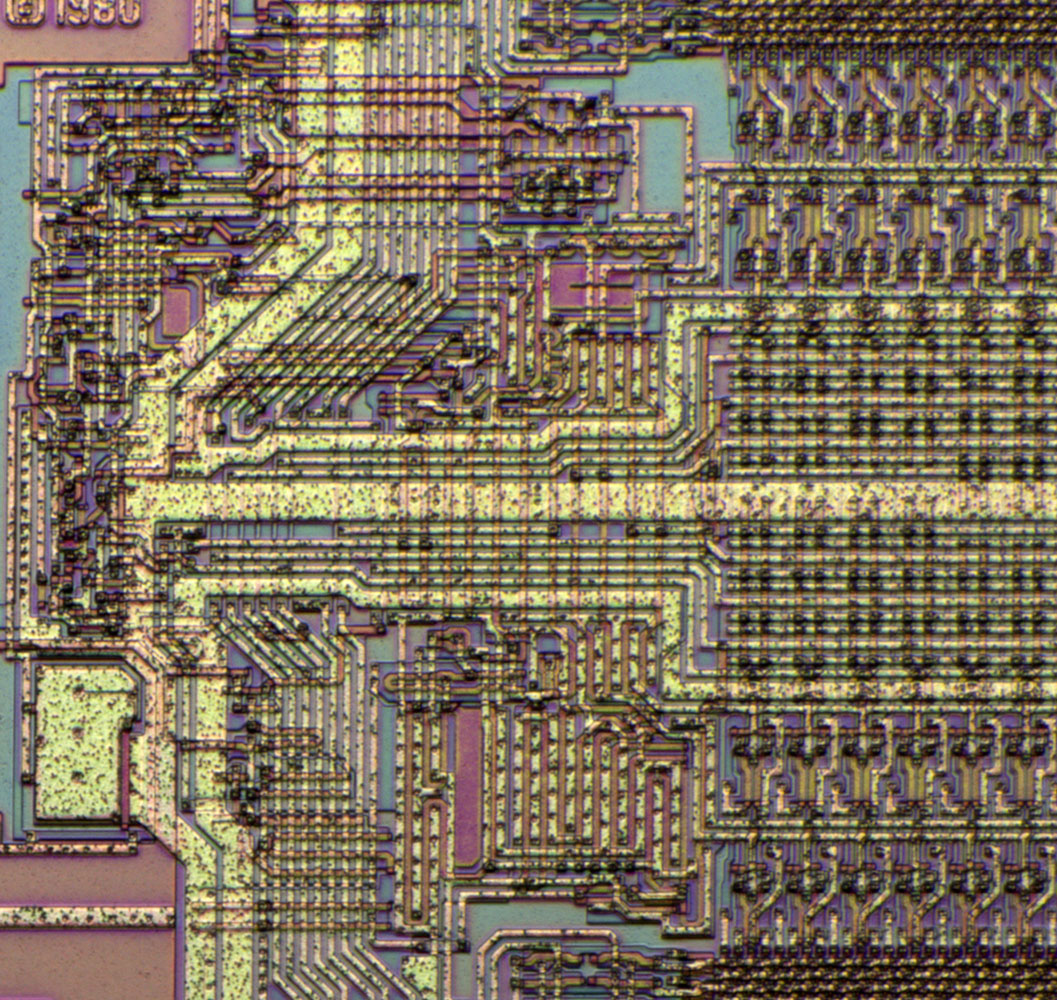

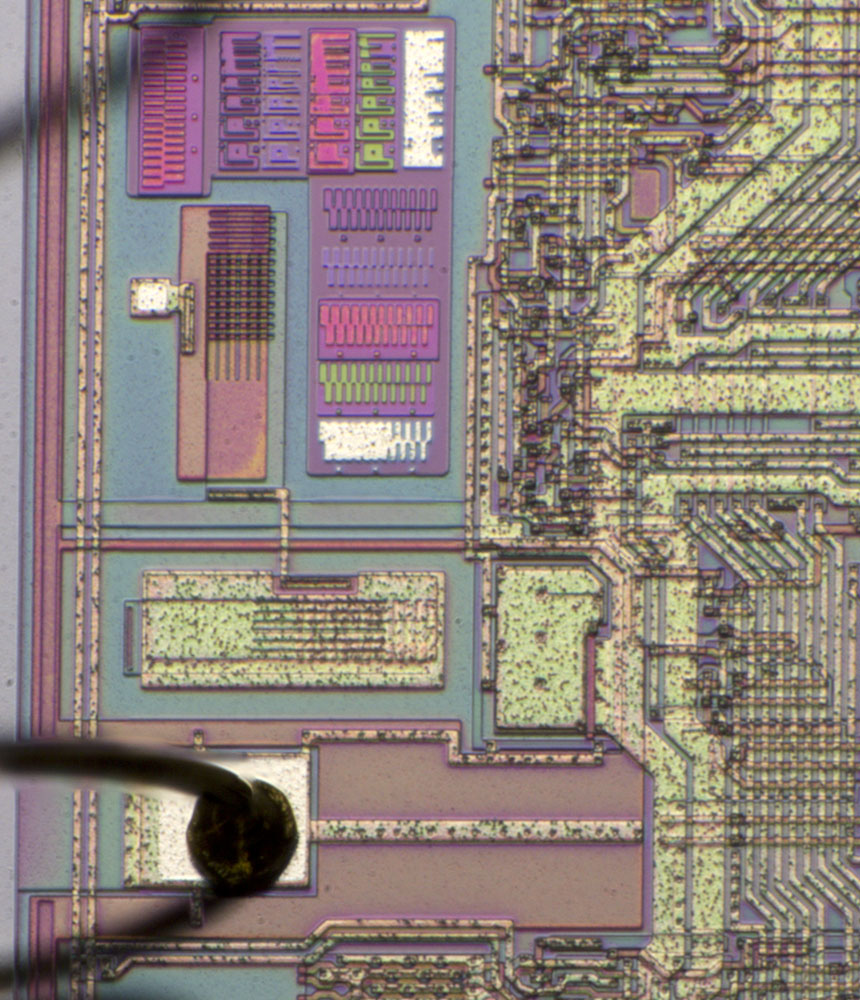

Die Anordnung der Kontaktflächen im Gehäuse ist offensichtlich für derartige Dies optimiert.

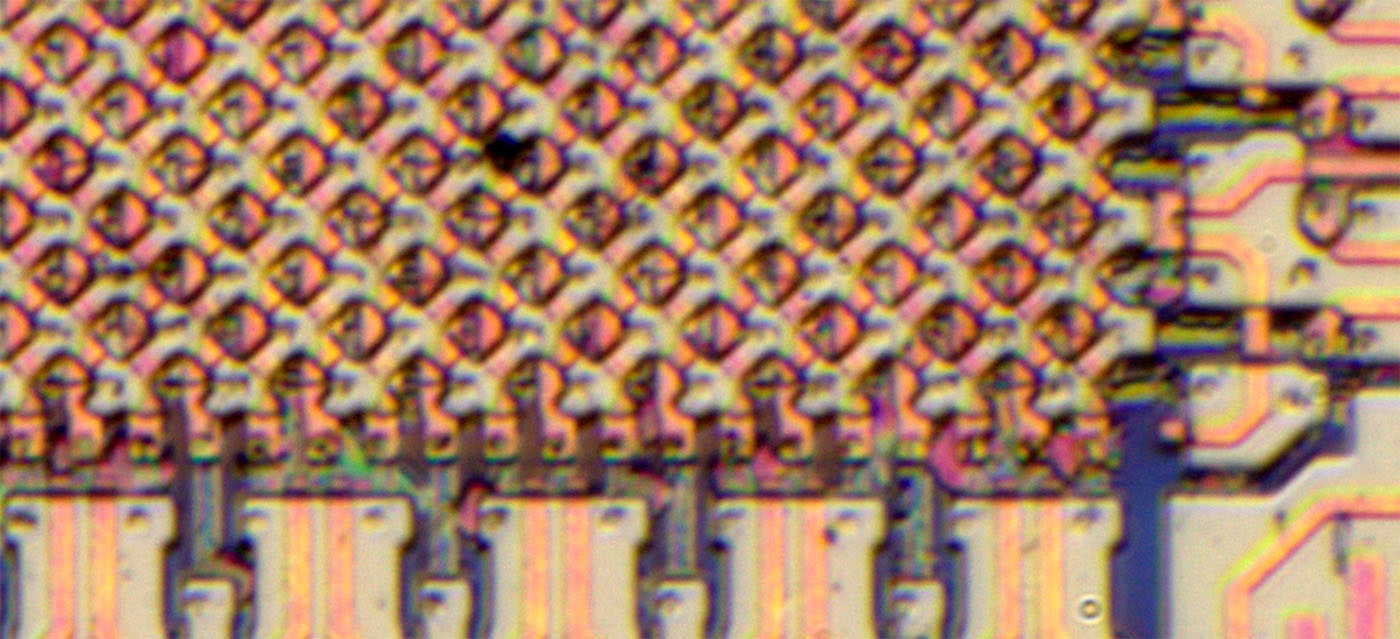

Das Heraustrennen des Dies aus dem Wafer erfolgte zweistufig. Die obere Kante wurde geschnitten. Die untere Kante entstand dann höchstwahrscheinlich beim Herausbrechen des Dies aus dem Wafer. Das war eine gängige Methode, um Dies zu vereinzeln.

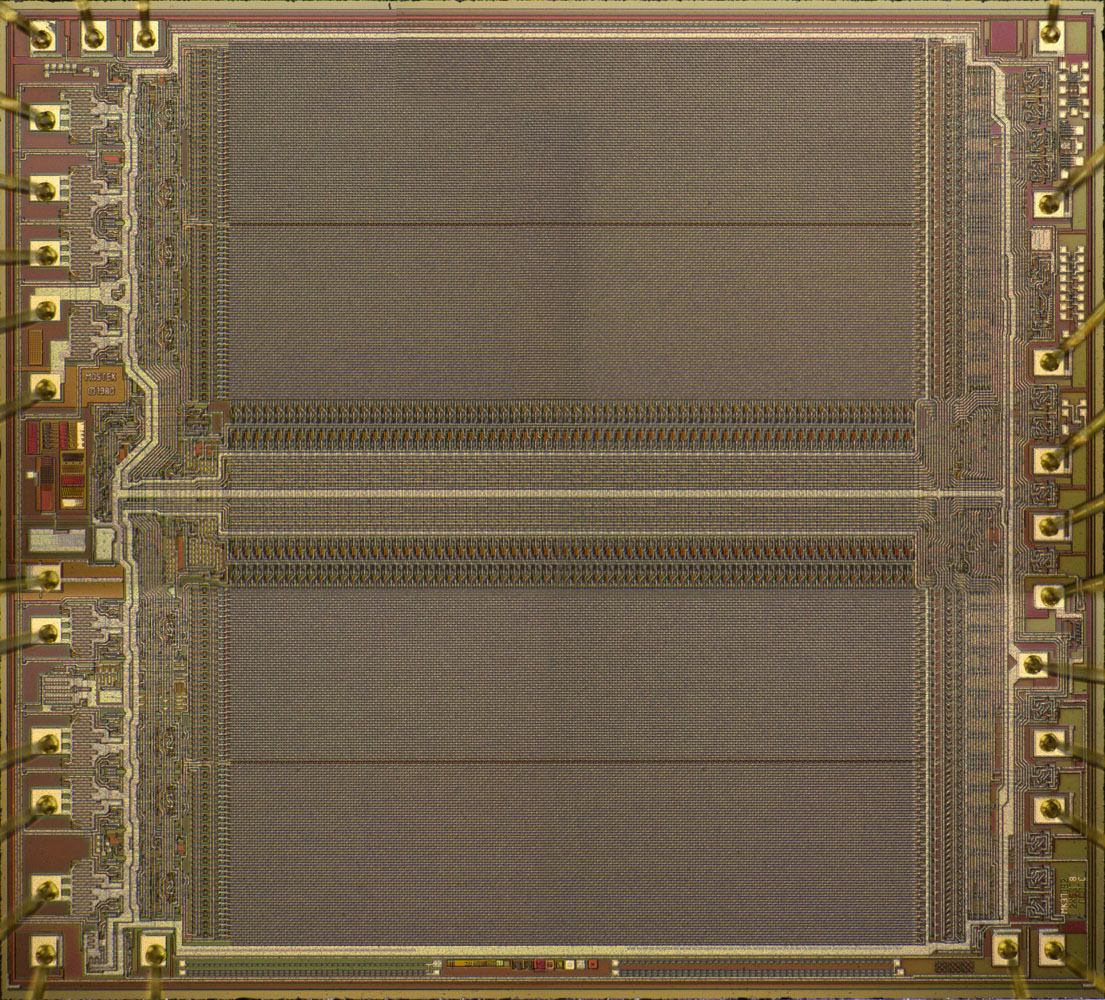

Die Abmessungen des Dies betragen 5,3mm x 4,8mm.

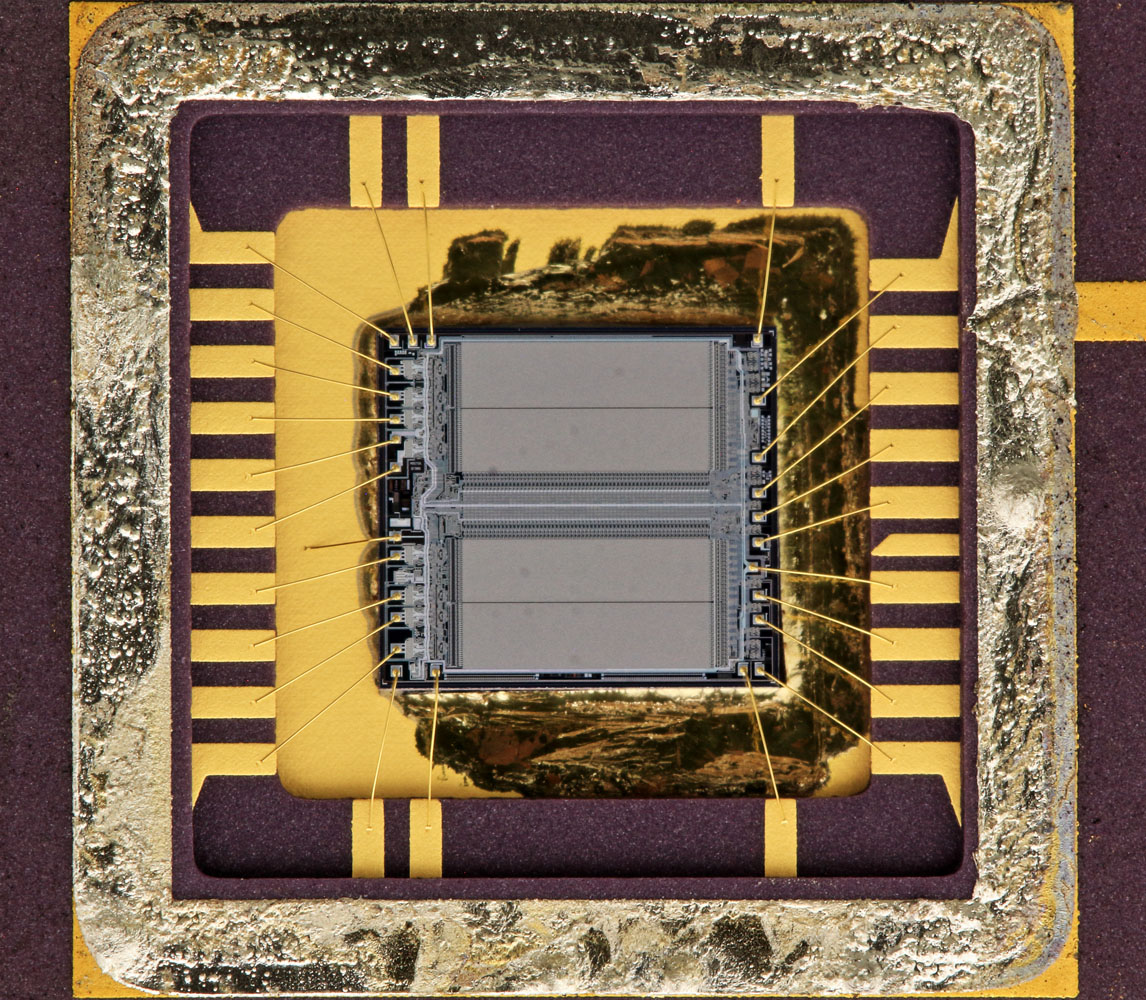

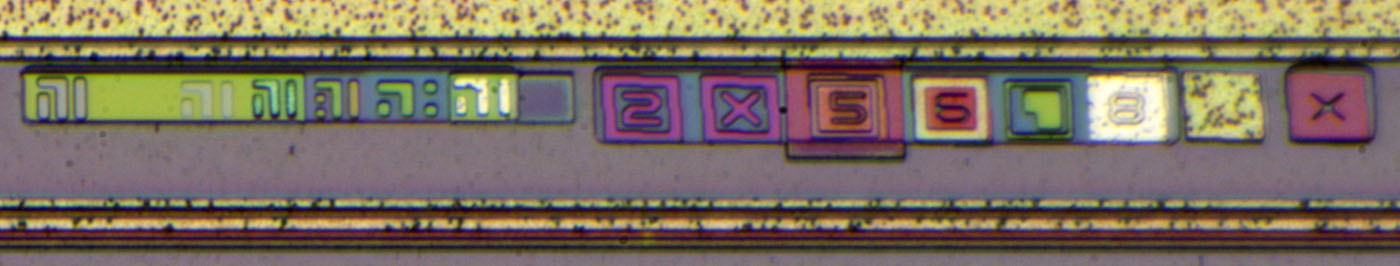

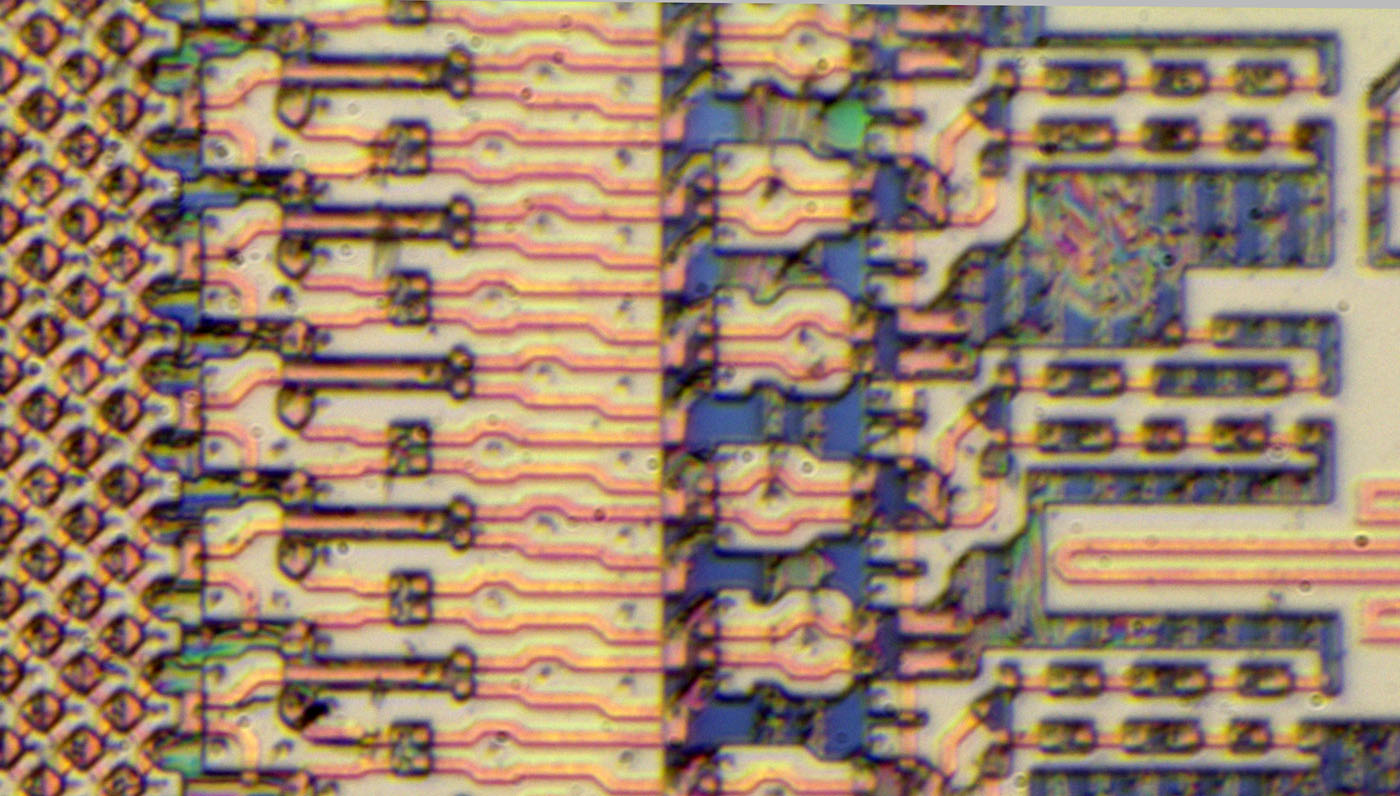

An der unteren Kante sind einige der verwendeten Masken abgebildet.

An der linken Kante findet sich eine weitere Auflistung der verwendeten Masken und die Bezeichnung des Bausteins. Der Rahmen stellt eine Aussparung in der obersten Siliziumoxidschicht dar. Im oberen Bild ist das gut zu erkennen, da die Metalllage dort innerhalb des Fensters weiß erscheint im Gegensatz zu der Leitung in der linken oberen Ecke.

Die Maske 1 definiert anfänglich die aktiven Bereiche. Die Maske 2X strukturiert eine Dotierung, über die die gewünschten Informationen in den Speicher geschrieben werden können. Dafür spricht, dass die Zahlen 092 in der Bezeichnung des Bausteins mit dieser Maske abgebildet wurden. Auch der Aufbau des Speichers zeigt, dass die Programmierung über eine Dotierung erfolgt sein muss. Die Dotierung wird unter dem Gate eines Transistors eingebracht und verschiebt dessen Thresholdspannung. Fraglich bleibt, ob es sich um eine Maske mit der Bezeichnung 2X handelt oder um zwei Masken mit den Bezeichnungen 2 und X. Die oben abgebildeten Quadrate lassen Letzteres vermuten, da dort eine 2 und ein X einzeln dargestellt werden. Es ist durchaus denkbar, dass die Maske 2 für die Grundfunktionalität benötigt wird und die Maske X lediglich den Speicherbereich konfiguriert.

Nach der partiellen Dotierung erfolgt die Strukturierung der Polysiliziumlage mit der Maske 5. Die Maske 8 formt die Metalllage. Die Maske 7 erzeugt der optischen Erscheinung nach Durchkontaktierungen. Welchen Zweck die Maske 6 hat, lässt sich nicht mit Sicherheit sagen. Vielleicht gab es zwei Masken für die unterschiedlich tiefen Durchkontaktierungen zu den aktiven Flächen und zum Polysilizium. Der Buchstabe C steht vermutlich für eine dritte Revision des Maskensatzes.

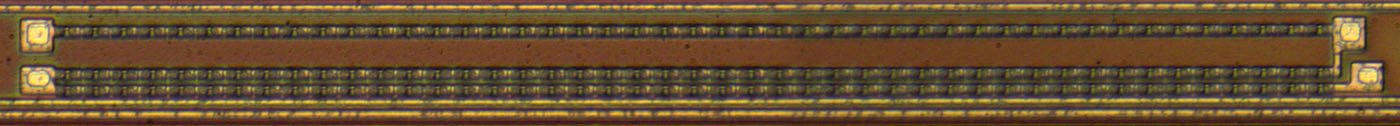

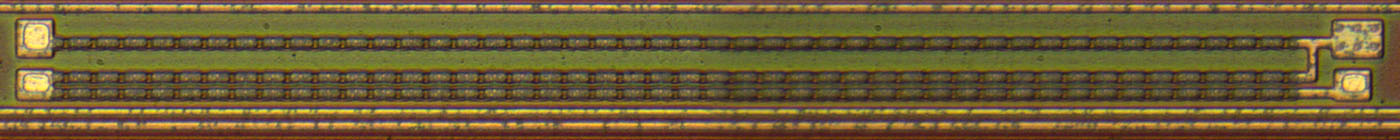

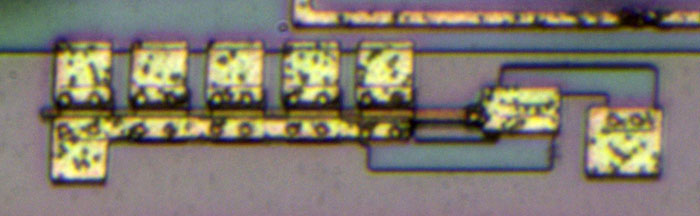

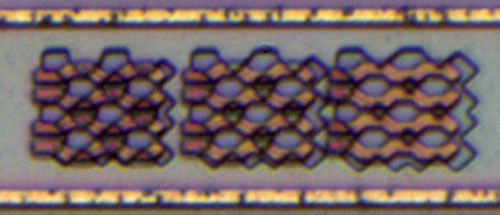

Das Die ist mit sehr vielen Teststrukturen ausgestattet. An der unteren Kante sind zweimal drei in Reihe geschaltete Ketten integriert, in denen sehr viele kurze Stücke aus Polysilizium über die Metalllage miteinander verbunden sind. Mit einer solchen Struktur kann man die Widerstände der Durchkontaktierungen bestimmt. Die Anordnung über einen Großteil der unteren Kante und die unterschiedlichen Abstände wurden wahrscheinlich gewählt, um inhomogene Prozesse erkennen zu können.

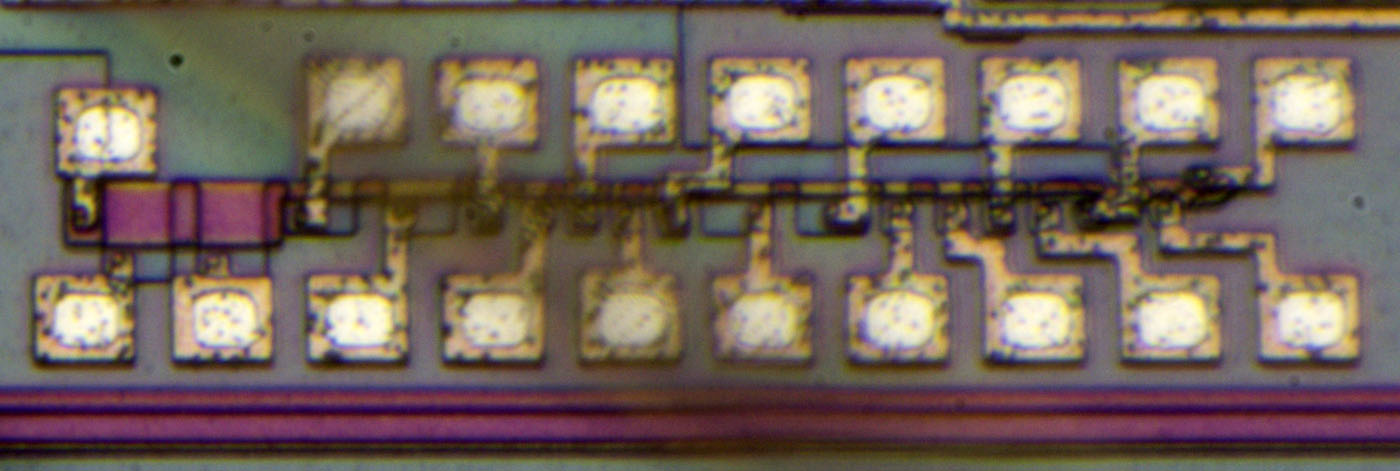

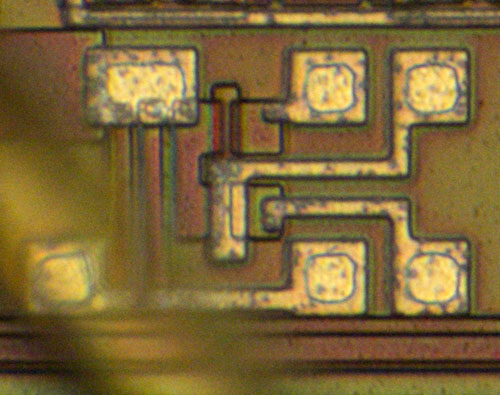

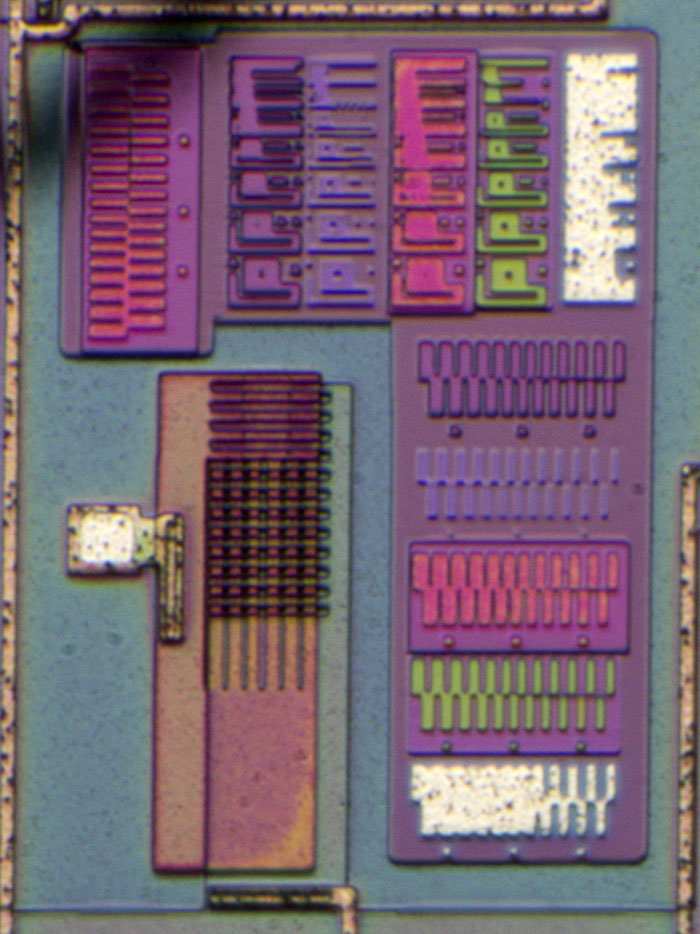

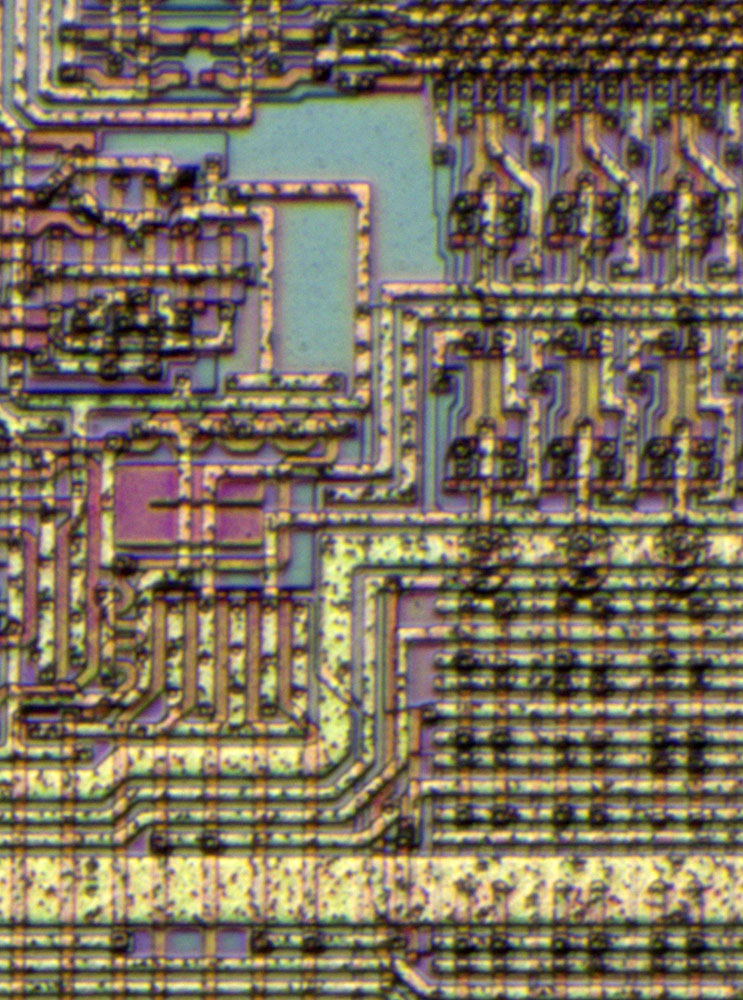

Die hier dargestellte Teststruktur enthält einige Transistoren, bei denen die Gateelektroden unterschiedliche Breite/Länge-Verhältnisse und entsprechend unterschiedliche Eigenschaften aufweisen.

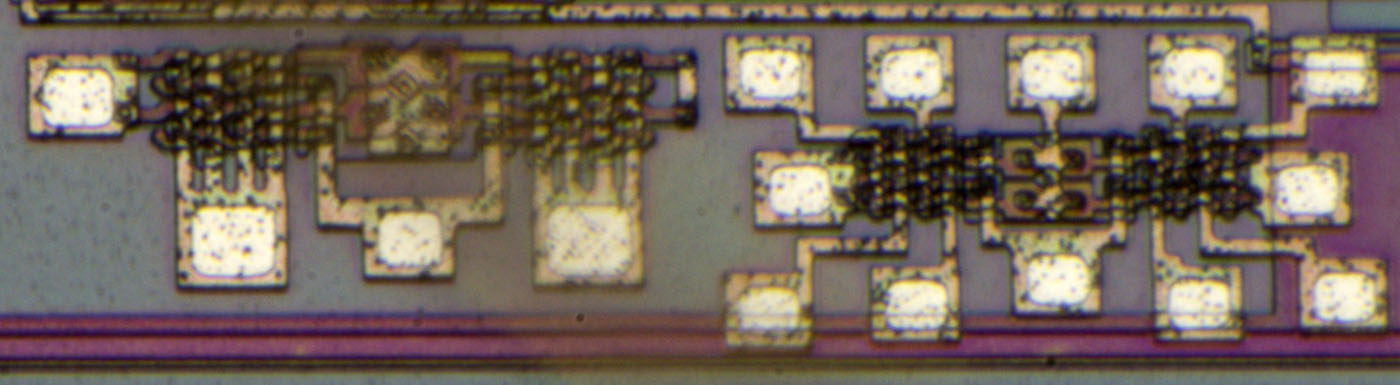

Zwei weitere Teststrukturen scheinen kleine Speicherbereiche darzustellen.

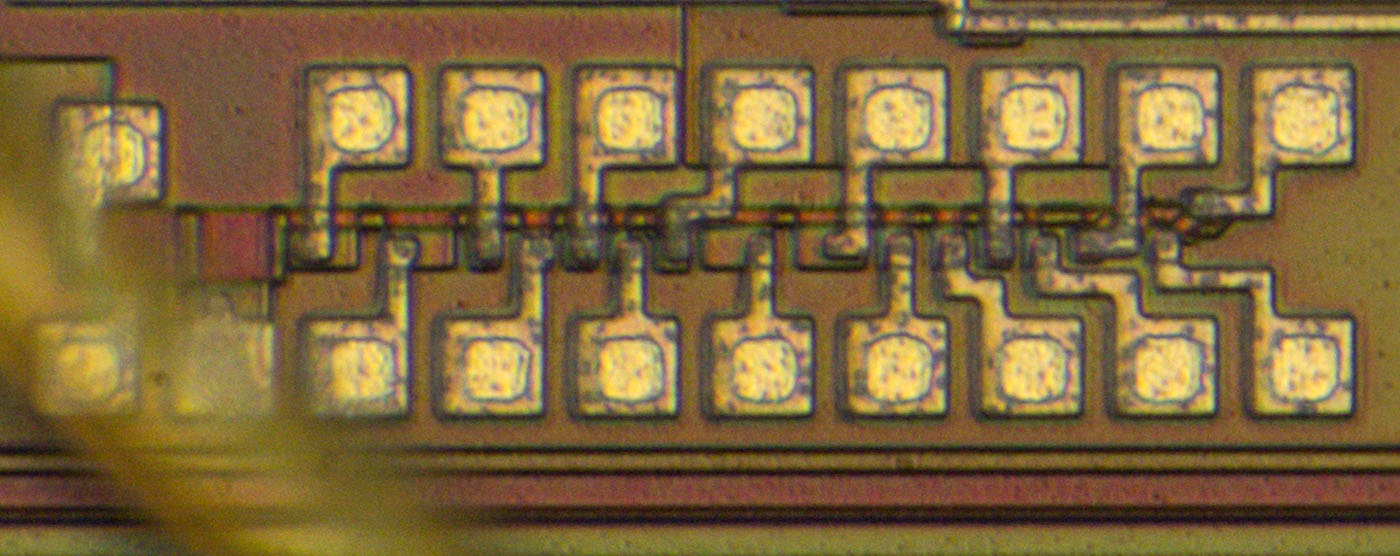

Hier lassen sich links zwei Streifen vermessen. Einer besteht aus Polysilizium, einer ist mit aktiven Bereich aufgebaut. Nach rechts folgt ein MOSFET mit einem Polysilizium-Gate und ein weiterer MOSFET mit einem Metall-Gate.

Diese Teststruktur beinhaltet mehrere Transistoren. Interessant ist, dass hier die Passivierungsschicht über den Kontaktflächen keine Aussparungen besitzt.

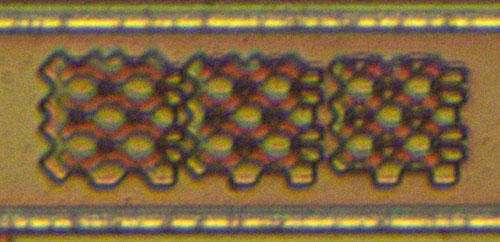

Wie sich später noch zeigen wird, handelt es sich hier um die Strukturen, die sich im Speicherbereich unter der Metalllage befinden. Streifen des Polysiliziums verlaufen geschwungen über ein Gitter. In den drei Bereichen ist das Gitter unterschiedlich dick ausgeführt.

Das Design stammt aus dem Jahr 1980. Die hier abgebildeten Teststrukturen zeigen die Abbildungsleistung des Herstellungsprozesses. Die Metalllage wird deutlich gröber abgebildet als die anderen Strukturen.

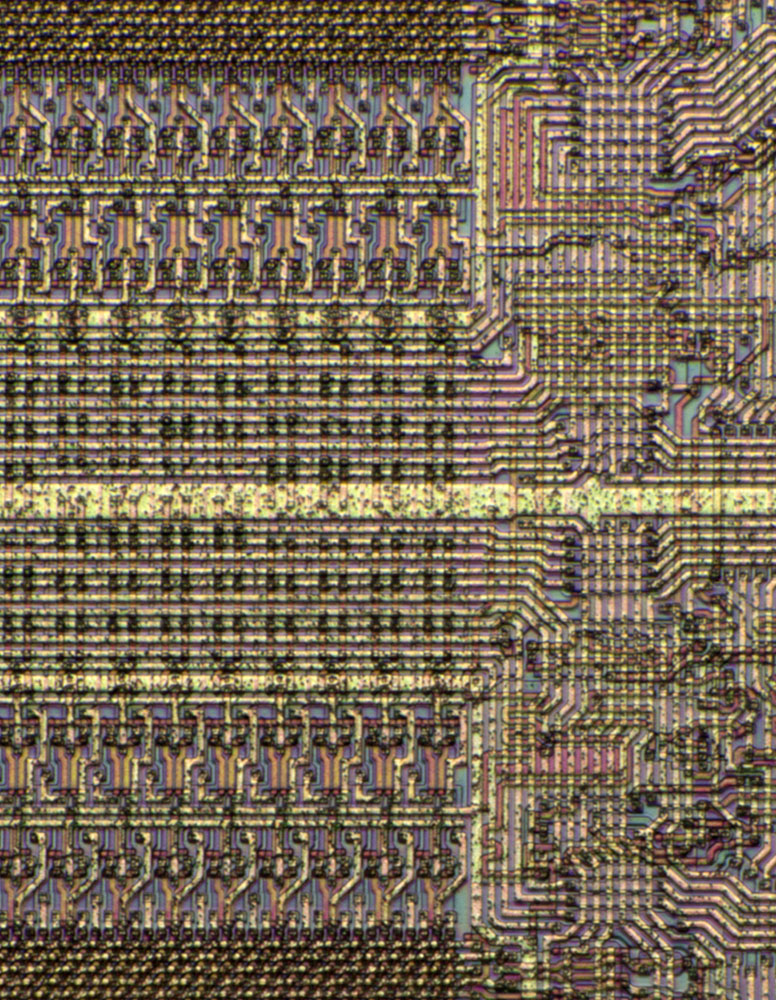

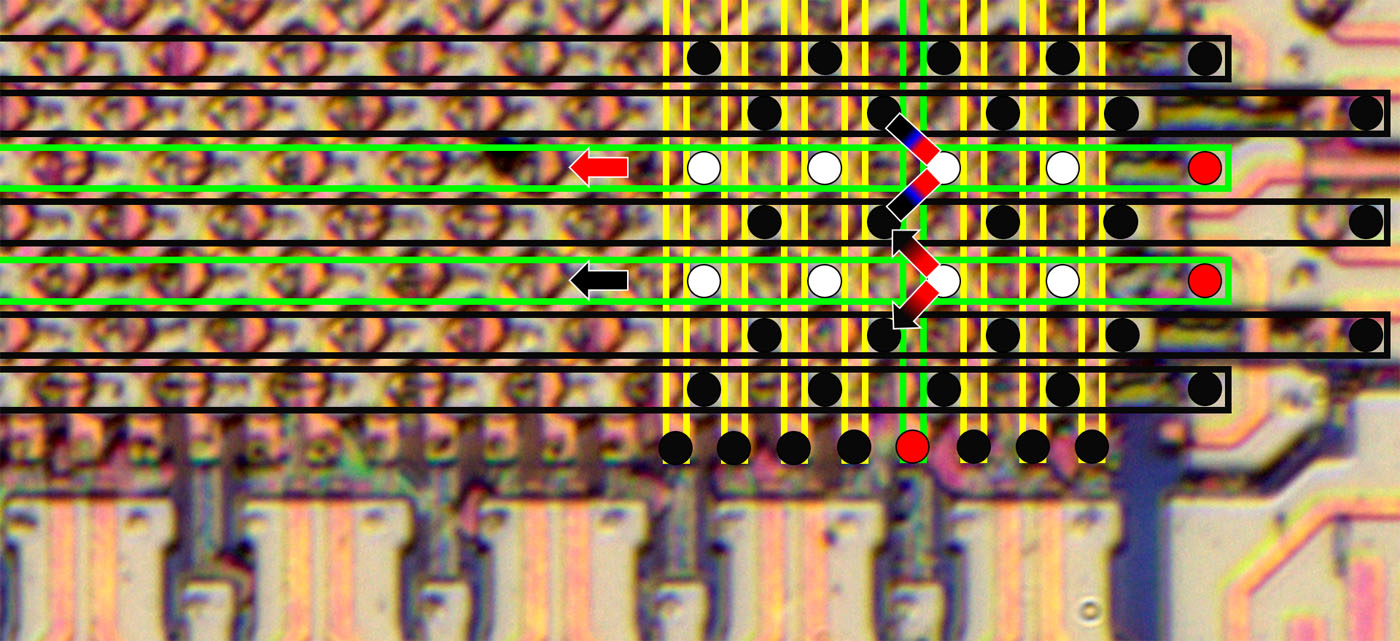

Der Speicher besteht aus vier Blöcken (rot), die jeweils 256x64 Speicherzellen enthalten. Die inneren Blöcke besitzen zwei, die äußeren vier zusätzliche Zeilen, die nicht zur Speichergröße beitragen. Es handelt sich aber nicht nur um klassische Dummystrukturen, die nur einen funktionalen Kern sicherzustellen sollen. Sie dienen teilweise der Funktion benachbarter Speicherzeilen.

Die meisten Adressleitungen treffen von rechts ein, wo sich auch die 12 Eingangspuffer befinden (gelb). Die Adressleitungen A0, A1, A10 und A11 steuern eine erste Multiplexspalte (blau), die daraus für jeden Speicherblock 16 Steuersignale erzeugt. Die Adressleitung A9 verdoppelt in einer zweiten Spalte die Steuersignale, so dass letztlich in jedem Speicherblock 32 Zeilen ausgewählt werden können (weiß). Das bedeutet, dass in jedem Speicherblock immer zwei Zeilen aktiv sind.

Zur Auswahl einer einzelnen Spalte werden im ersten Schritt die Adressleitungen A2, A3, A5, A6, A7, A8 und A12 in der Mitte des Dies in 128 Steuersignale umgewandelt (schwarz). Die Adressleitung A4 steuert zwei kleine Endstufen am linken Ende des Speicherbereichs. Die zwei Ausgangssignale dieser Schaltung sind mit den zwei Doppelzeilen verbunden, die wiederum die Spaltenauswahl realisieren (rosa). Die Adressleitung A4 doppelt so die 128 Steuersignale auf und es wird nur eine der 256 Spalten des Speichers aktiviert.

Am linken Ausgang jedes Speicherblocks werden die 64 Zeilen ohne Weiteres auf zwei Ausgänge zusammengefasst (orange). Diese Zusammenfassung ist möglich, da von den 64 Zeilen immer nur zwei aktiv sind. Eine Vermischung der Informationen kann bei richtiger Verschaltung nicht vorkommen.

Die Ausgangssignale der vier Speicherblöcke werden jeweils zwei Endstufen zugeführt (hellgrün). Die Signale durchlaufen dabei einen weiteren Schaltungsteil (dunkelgrün), der den Treiber für die Endstufen enthält und die Funktion übernimmt die Ausgänge global zu deaktivieren (OE).

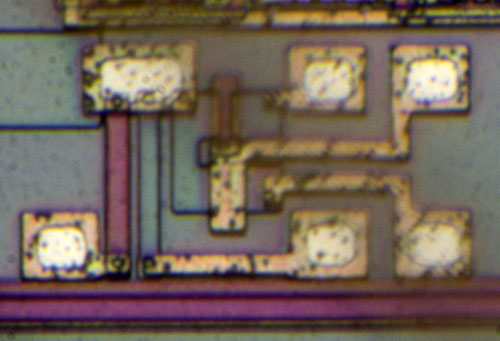

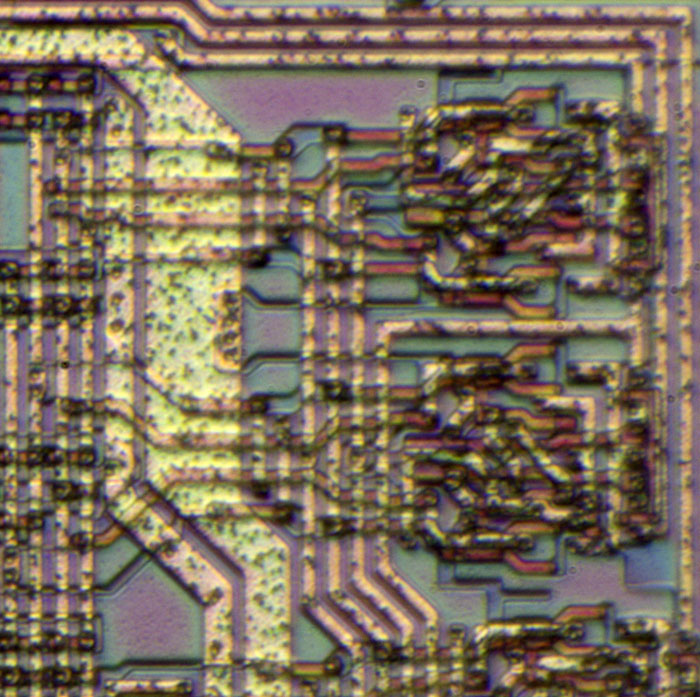

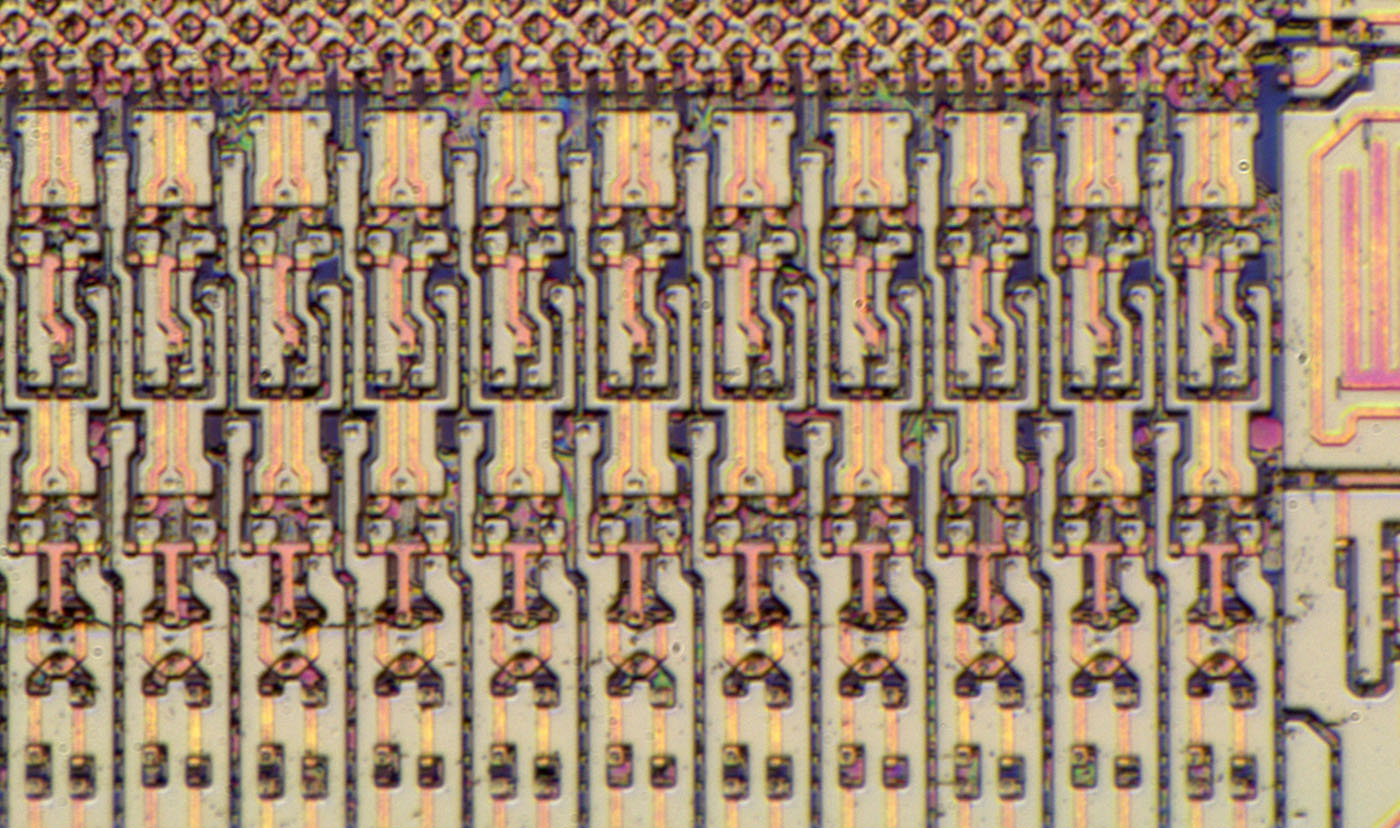

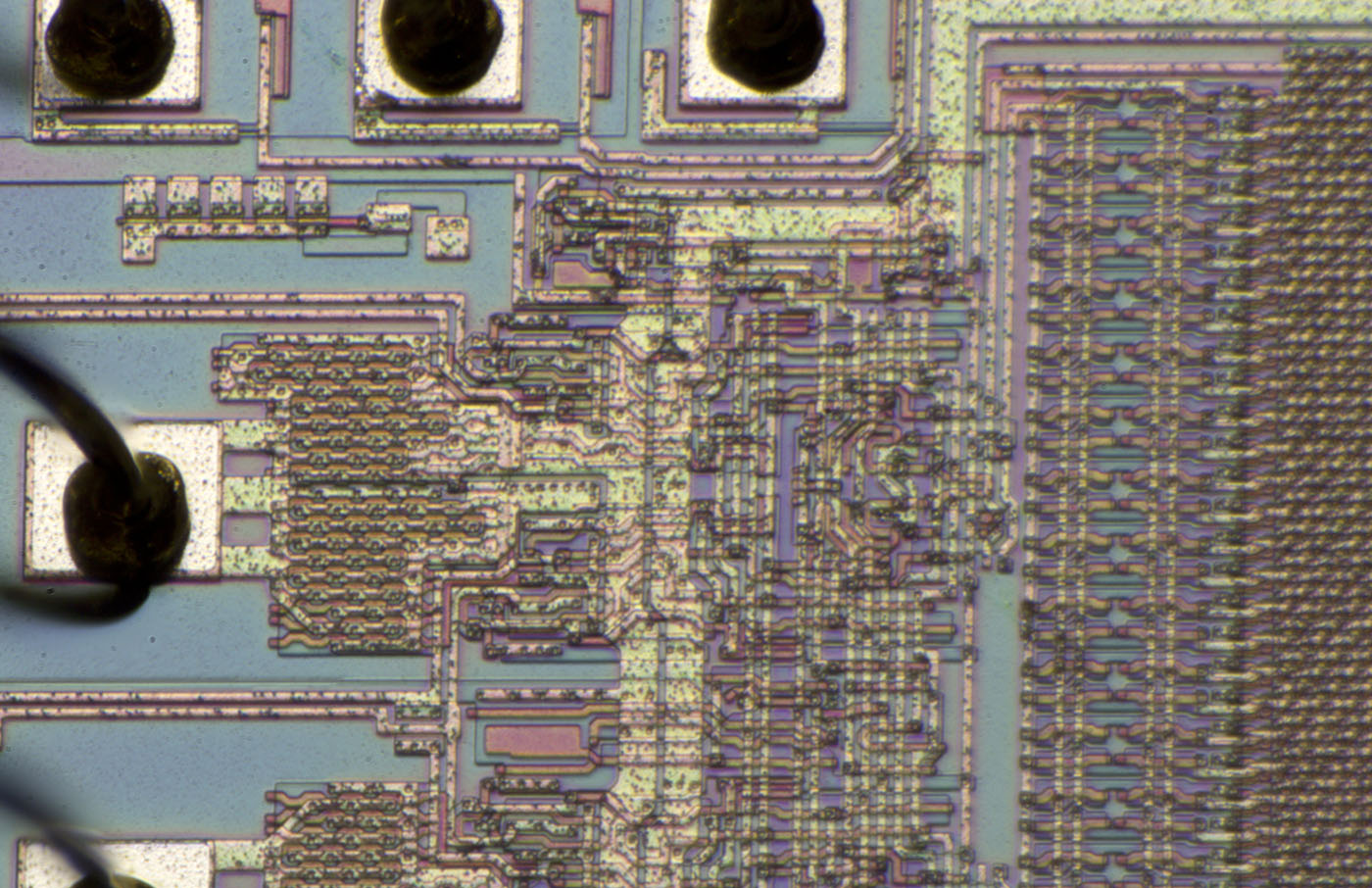

Hier sind zwei Zwischenspeicher des Adressbus abgebildet, deren differentiellen Ausgänge direkt zur ersten Stufe der Zeilenauswahl geführt werden (links im Bild). Das Eingangssignal der zugehörigen Bondpads trifft von oben ein und kontaktiert die Zwischenspeicher rechts. Vertikal verlaufen vier gemeinsame Steuerleitungen durch alle Zwischenspeicher.

Die differentiellen Signale der Adressleitungen A0, A1, A10 und A11 führen zu acht vertikal verlaufenden Leitungen, die bei jedem der vier Speicherblöcke acht aktive Bereiche durchlaufen und teilweise kontaktieren (rot). In diesen aktiven Bereichen befinden sich zwei Reihen Polysilizium-Gateelektroden, die mehrere Transistoren darstellen. Die Gateelektroden sind so aufgebaut und werden so kontaktiert, dass abhängig von der anliegenden Adresse in jedem Speicherblock nur einer der 16 Ausgänge aktiv wird. Über den ganzen Speicher betrachtet, sind in dieser Ebene immer vier Steuersignale aktiv.

Nach links folgt der Umschalter, der dafür sorgt, dass mit den 16 Steuersignalen 32 Zeilenpaare ausgewählt werden können (grün). Die abwechselnde Kontaktierung der zwei vertikal verlaufenden Steuerleitungen ist gut zu erkennen. Genau genommen handelt es sich nicht um einen Umschalter. Die aktiven Bereiche enthalten zwei Schalter, die von den zwei vertikalen Leitungen versorgt werden. Durch eine Umschaltung der zwei Versorgungsleitungen sorgt man dafür, dass nur jeder zweite aktive Bereich das gewünschte Signal durchschalten kann.

Hinter dem Block mit den Umschaltern folgt ein weiterer Schaltungsteil. Wahrscheinlich befinden sich dort unterstützende Schaltungsteile, wie Pull-Up- oder Pull-Down-Strukturen.

Die Unterbrechung zwischen dem inneren und dem äußeren Speicherblock ist durch die Verschaltung am linken Ende des Speichers verursacht. Die Ansteuerung auf der rechten Seite ist für eine optimale Signalführung gespiegelt aufgebaut.

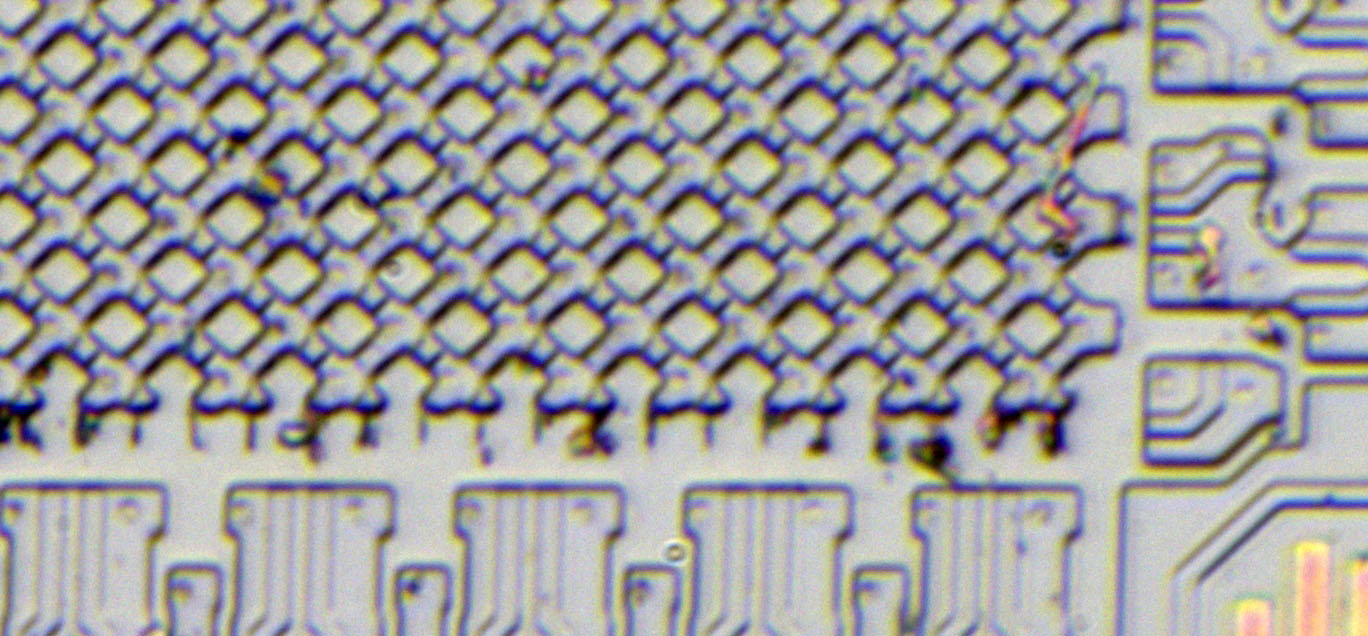

Entfernt man die Metalllage, so wird die Funktionsweise der Zeilenauswahl etwas klarer. Auch ohne eine vollständige Analyse kann man im linken Bereich erkennen, dass im Speicher zwischen zwei aktiven Zeilen immer eine Zeile inaktiv bleibt.

Im rechten Bereich zeigt sich, wie die einzelnen Transistoren aus den acht differentiellen Adressleitungen Steuersignale für die Zeilenauswahl generieren. Es handelt sich um einen NOR-Verschaltung. Der Ausgang ist aktiv, wenn keiner der Transistoren angesteuert wird.

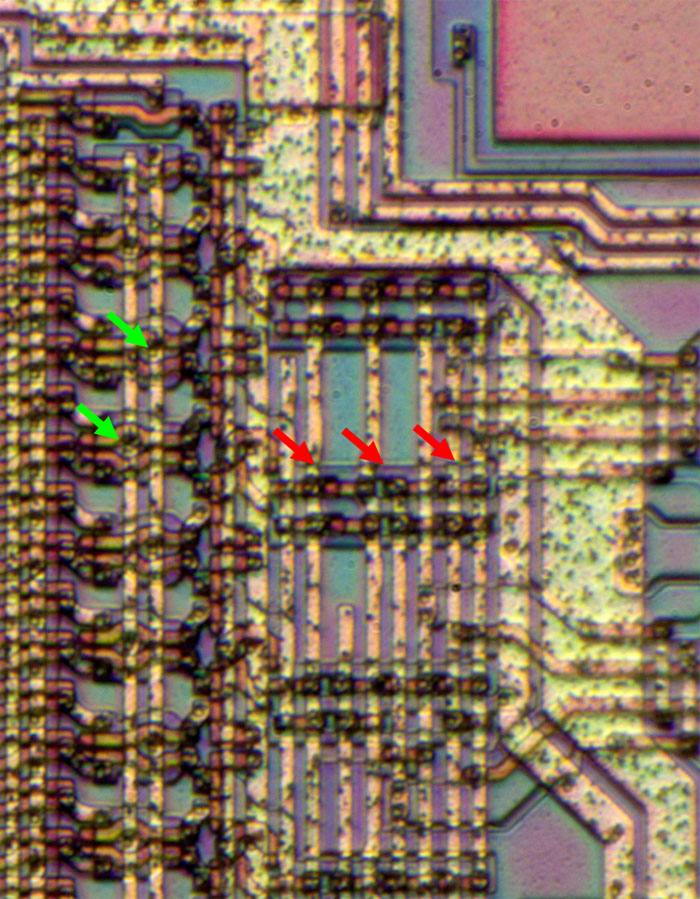

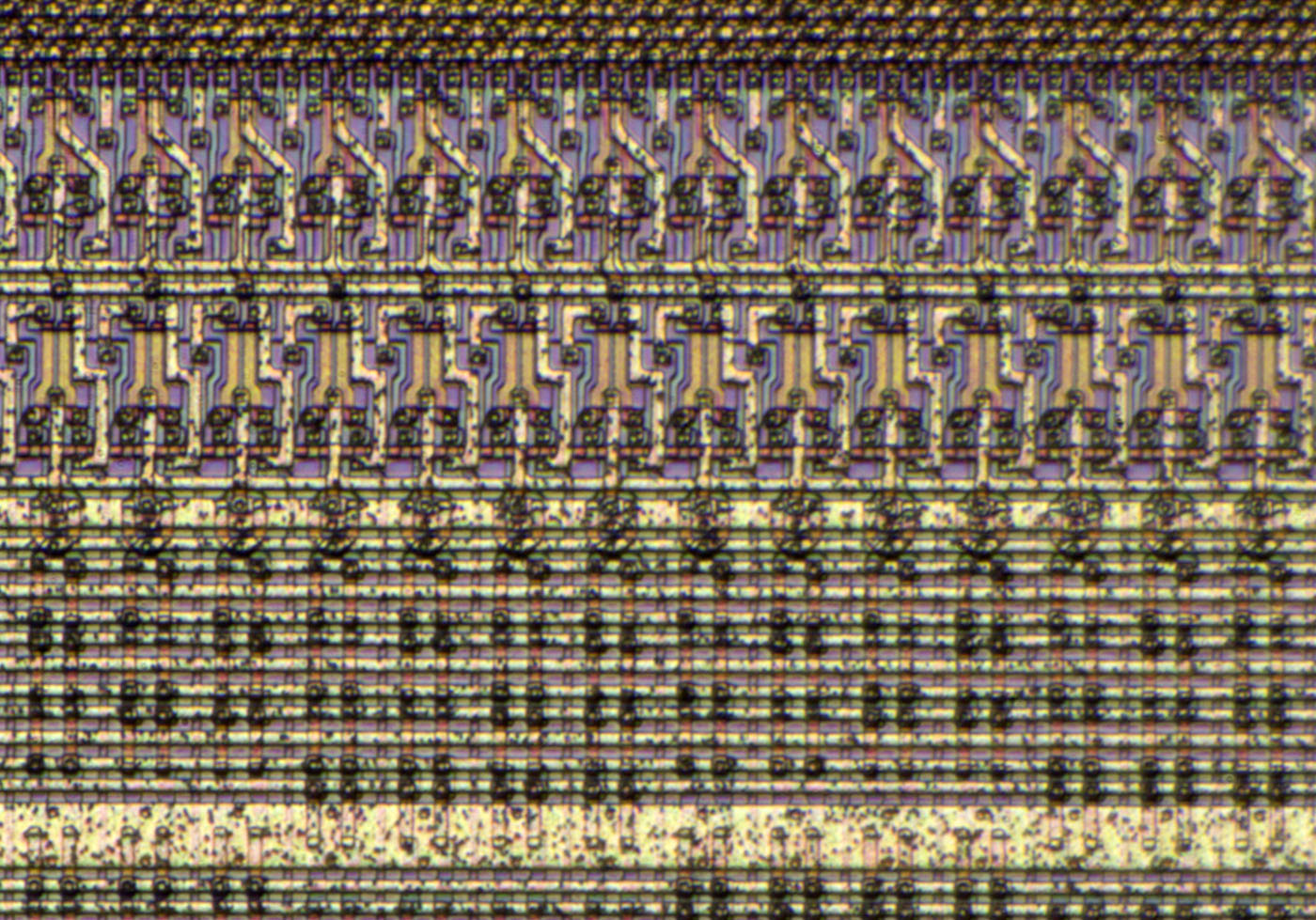

Die Spaltenauswahl erfolgt über einige in der Mitte des Dies horizontal verlaufende differentielle Adressleitungen. Ähnlich wie bei der Zeilenauswahl kontaktieren die Leitungen vertikal angeordnete Polysiliziumstreifen. Die Hälfte der insgesamt 14 Adressleitungen befinden sich oberhalb der breiteren Vss-Leitung in der Mitte, die andere Hälfte befindet sich darunter. Abhängig von der Kontaktierung der Polysiliziumstreifen und der Struktur des darunter liegenden aktiven Bereichs wird genau eine der 128 Steuerleitungen aktiv geschaltet.

Zwischen den Adressleitungen und den Speicherbereichen befinden sich jeweils zwei Zeilen, die die Spalten treiben können. Abhängig vom Status der Adressleitung 4 wird eine der zwei Zeilen aktiv und es kann so mit den 128 Steuerleitungen eine von 256 Spalten ausgewählt werden. In den unteren und den oberen Speicherblöcken ist immer die gleiche Spalte aktiv.

Auch bei genauerer Betrachtung erschließt sich die Funktionsweise der Spaltenauswahl nicht sofort. Es sind zwar teilweise Unterschiede im Aufbau und bei der Kontaktierung erkennbar, der Großteil der Strukturen erscheint aber gleich.

Entfernt man die Metalllage, so wird die Funktionsweise der Spaltenauswahl etwas klarer. An der unteren Kante des Bilds ist noch ein kleiner Teil der Schaltung abgebildet. Es handelt sich um kleine, vertikale Polysiliziumstreifen, die teilweise am oberen, teilweise am unteren Ende mit einer der Adressleitungen verbunden sind. Die sich ausbildenden Transistoren verbinden die Spalten so lange mit dem Vss-Potential, das sich zwischen den Adressleitungen befindet, bis die Adresse der Spalte ausgewählt wird und so alle Transistoren sperren. Oberhalb der Adressleitungen befindet sich eine Pull-Up-Struktur, die in diesem Fall für einen sauberen High-Pegel sorgt.

Die zwei Zeilen der Spaltenansteuerungen sind grundsätzlich gleich aufgebaut. Der untere Bereich der oberen Zeile und der obere Bereich der unteren Zeile wurden lediglich etwas verlängert, damit die notwendigen Kontakte hergestellt werden konnten.

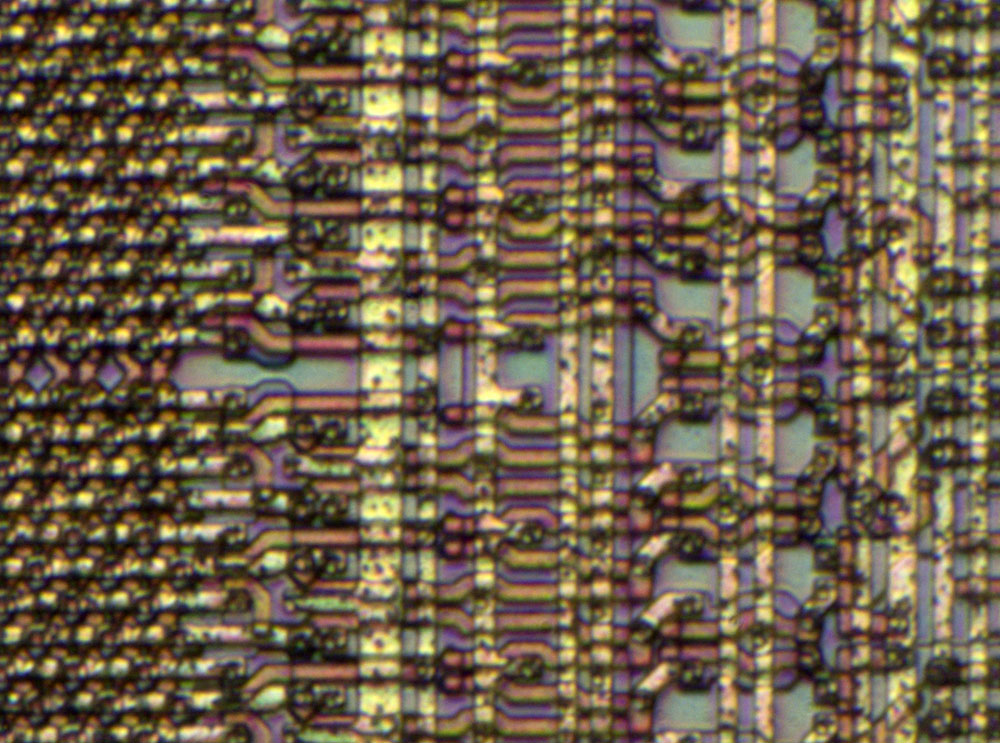

Die Strukturen im Speicherbereich lassen nichts von der Programmierung erkennen. Die Metalllage ist in regelmäßigen Abständen mit dem aktiven Bereich verbunden. Zwischen den Durchkontaktierungen verlaufen jeweils zwei Polysiliziumleitungen der Spaltenauswahl.

Die Funktionsweise wird klarer, wenn man die Metalllage entfernt. Der Speicher basiert auf einem diagonalen Gitter des aktiven Bereichs. Die Polysiliziumleitungen verlaufen oberhalb dieses Gitters. Im unteren Bild sind sie mit geraden Streifen markiert. Tatsächlich verlaufen sie geschwungen, wie es bei den Teststrukturen deutlich zu sehen ist. Die Polysiliziumstreifen bilden Transistoren in den diagonalen Verbindungen zwischen den Kreuzungspunkten. In den Kreuzungspunkten kontaktiert die Metalllage den aktiven Bereich.

Wie bereits beschrieben, werden immer zwei Zeilen mit einer Zeile Abstand aktiviert (grün). Am unteren Ende des Speicherbereichs sind es genau genommen einmal drei Zeilen, was hier allerdings zum besseren Verständnis ignoriert wurde. Jede Speicherzeile benötigt anscheinend immer zwei benachbarte Zeilen, um ordnungsgemäß zu funktionieren. Das erklärt einen Großteil der Dummy-Zeilen. Sie tragen nicht direkt zum nutzbaren Speicher bei. Parallel zu den zwei aktiven Zeilen wird eine der Spalten aktiviert (grün). Die aktive Polysiliziumleitung kann bei jeder Speicherzelle zwei der diagonalen Transistoren leitend schalten. Ein aktiver Transistor führt dazu, dass das Potential der aktiven Zeile auf das Potential der benachbarten, inaktiven Zeilen gezogen wird (untere Zeile). Die gewünschten Informationen sind in Form einer zusätzlichen Dotierung in den Speicherbereich eingebracht. Ändert man die Dotierung in den diagonalen Transistoren (blau), so werden diese niemals leitend, die ausgewählte Zeile wird nicht beeinflusst und liefert einen High-Pegel zum Ausgang (obere Zeile).

Trägt man auch noch die Polysiliziumleitungen ab, so bleiben nur noch die Umrisse der aktiven Bereiche zurück. Optisch ist die Dotierung, die die Programmierung darstellt, nicht zu erkennen. Sie würde sich auch in einer schärferen Darstellung nicht absetzen. Es existieren aber anscheinend spezielle Chemikalien, mit denen sich unterschiedliche Dotierungen sichtbar machen lassen.

Am linken Ende der Spaltenauswahl kann man die Endstufen erkennen, die für den oberen und den unteren Speicherbereich die Umschaltung der beiden Spaltentreiberzeilen realisieren.

An der linken Kante des Speicherbereichs münden die Zeilen in eine Auswerteschaltung, die sich auf zwei Spalten aufteilt. Dieser Aufbau erzeugt aus jedem der vier Speicherblöcke zwei differentielle Ausgangssignale. Da in jedem Speicherblock nur zwei Zeilen aktiv sind, benötigt die Schaltung keine zusätzliche Steuerung, die Zeilen müssen lediglich abwechselnd an einen der Ausgänge angebunden werden.

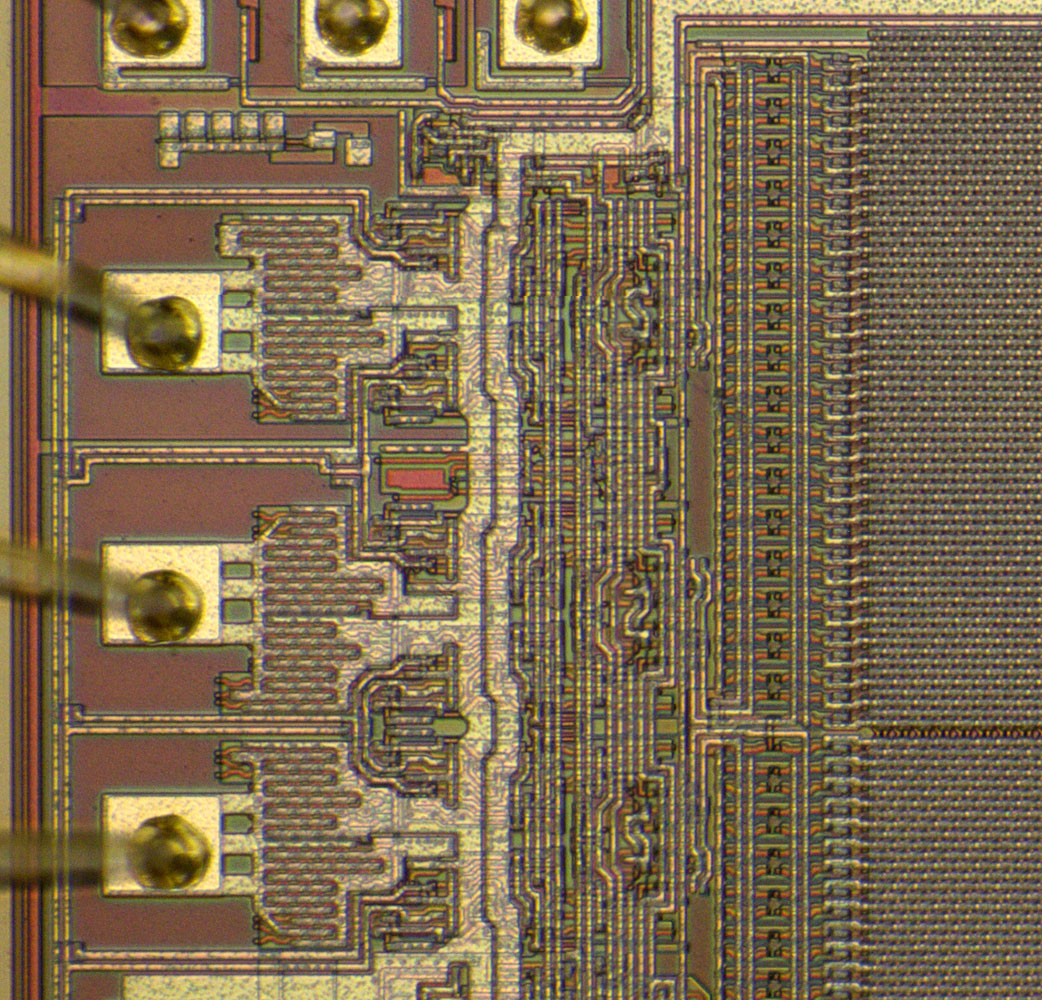

Links der Auswerteschaltung befindet sich ein Schaltungsteil, der höchstwahrscheinlich das Ausgangssignal aufbereitet, für eine Schaltbarkeit über das OE-Signal sorgt und die Ausgangsendstufe treibt. Jeder Ausgang besitzt einen großen Lowside- und einen großen Highsidetransistor direkt am Bondpad.

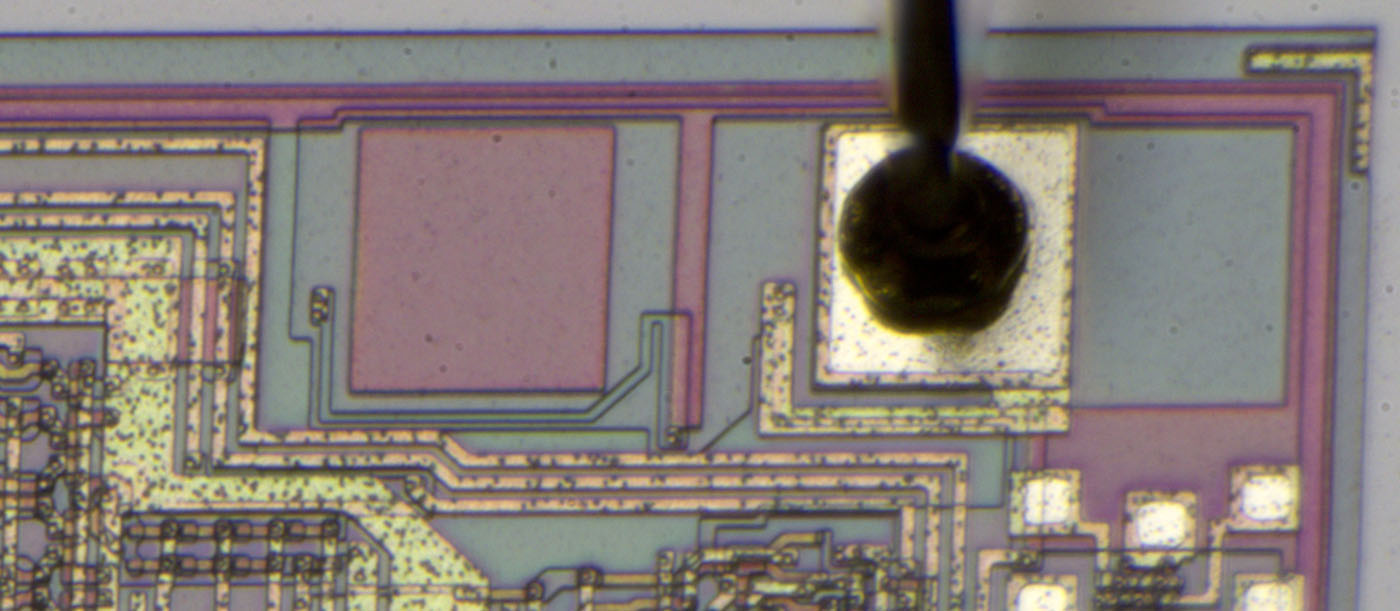

Der Bonddraht, der zum Boden des Keramikgehäuses führt, ist auf dem Die an das Substrat, an eine Rahmenstruktur und an eine Schaltung angebunden. Es könnte sein, dass auf dem Die eine negative Spannung generiert und dem Substrat zugeführt wird, was die Eigenschaften der integrierten Transistoren optimiert. Auf dem Die des Grafikprozessors NEC µPD7220 ist eine solche Schaltung deutlicher abgebildet.

In der oberen linken Ecke des Dies befindet sich die Vorbereitung für ein zusätzliches Bondpad, das in der Metalllage allerdings nicht dargestellt wurde. Wahrscheinlich kann man das Die auch in einer anderen Konfiguration nutzen.

An dieser Stelle ist die Schutzbeschaltung der Eingänge gut zu erkennen. Das Potential der Bondpads wird zuerst zu einem Widerstandsstreifen geführt. Das Ende des Widerstandstreifens überlappt ein Streifen des rötlichen Rahmens. Der Rahmen führt das vermutlich negative Substratpotential. Die sich überlappende Bereiche bilden höchstwahrscheinlich eine Diode aus, die negative Eingangsspannungen auf das Substratpotential begrenzt.

Die scheinbar unnötig lange und breite Zuleitung vom Bondpad zum Widerstandsstreifen stellt mit den Strukturen darunter einen Transistor dar. Beim nicht ausgebildeten Bondpad sieht man, dass der Widerstandsstreifen parallel zu einem aktiven Bereich verläuft. Im Fall einer Überspannung ist die Gate-Source-Spannung des Transistors hoch genug, um trotz der dicken Oxidschicht unter der Metallelektrode einen leitfähigen Kanal zwischen dem Widerstand und dem aktiven Bereich zu etablieren. Überspannungen können darüber abgeleitet werden.