Der Intel D2164 ist ein 64kBit-DRAM. Die Variante "20" bietet eine maximale Zugriffzeit von 200ns. Für die Variante "15" ist eine maximale Zugriffszeit von 150ns spezifiziert.

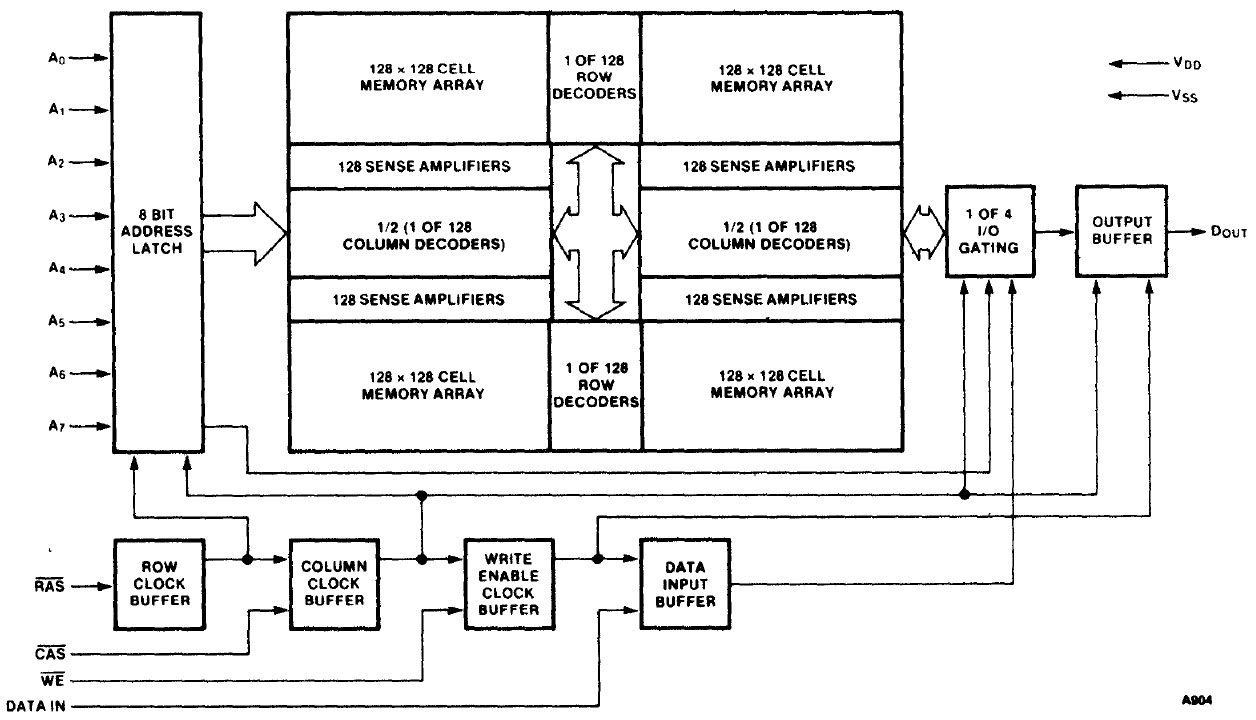

Die Application Note AP-131 von Intel enthält viele Informationen zum D2164. Die 64kBit sind in vier Bereiche mit 128 x 128 Speicherzellen aufgeteilt. Adressiert werden die Zellen mit zweimal acht Adressbits. Die ersten sieben Adressbits aktivieren in den oberen und in den unteren Bereichen jeweils eine Zeile. Die zweiten sieben Adressbits wählen im linken und im rechten Block jeweils eine Spalte aus. So liefert der D2164 im ersten Moment den Inhalt von vier Speicherzellen. Das achte Adressbit, das ebenfalls doppelt eingelesen wurde, realisiert die Auswahl einer Speicherzelle, die dann ausgegeben wird. Das Schreiben von Daten erfolgt auf dem gleichen Weg.

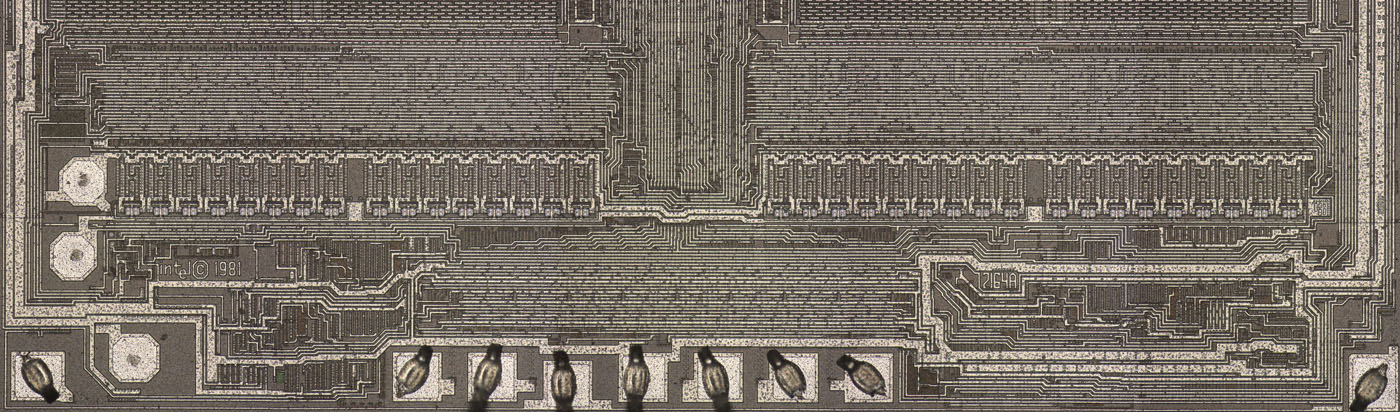

Die Abmessungen des Dies betragen 6,9mm x 3,7mm. Der D2164 basiert auf dem NMOS-Prozess HMOS-D III. Die Vierteilung der Speicherfläche ist deutlich zu erkennen.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 37MB

Das Design stammt aus dem Jahr 1981. Das A am Ende der Bezeichnung 2164A könnte für eine erste Revision stehen.

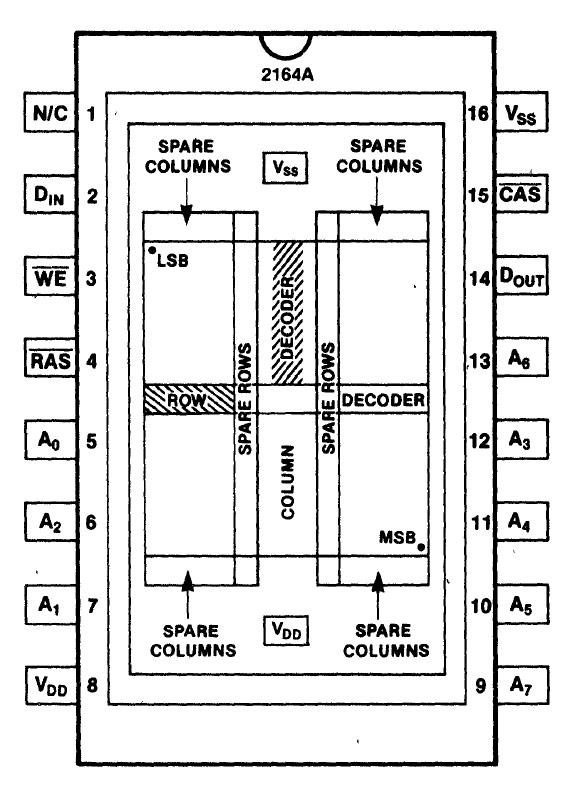

Die Applikation Note AP-131 behauptet, dass der D2164 der erste kommerziell produzierte RAM war, in den Reservezellen integriert wurden. In jedem der vier Bereiche sind zwei zusätzliche Spalten und zwei zusätzliche Reihen enthalten, die fehlerhafte Speicherzellen ersetzen können und so die Ausbeute deutlich erhöhen.

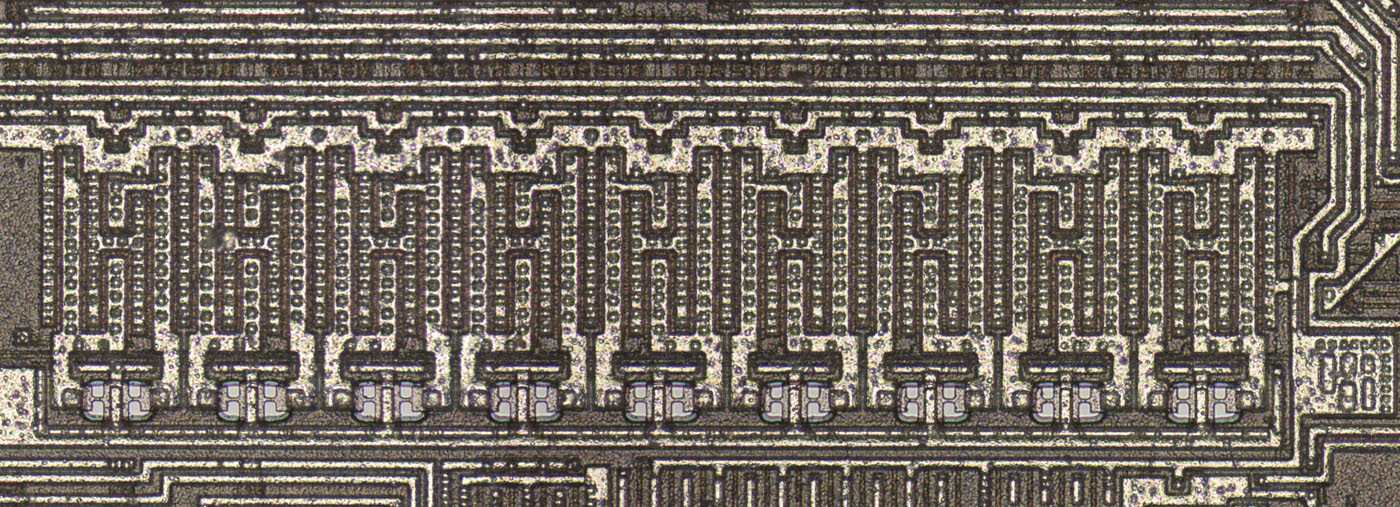

Die Zuordnung der Reservezellen erfolgt im rechten Bereich des Dies. Dazu sind dort drei Testpads integriert. Diese Schaltung findet sich sehr ähnlich im U2164.

Über den Fuses befinden sich Aussparungen. Bei diesem D2164 wurde keine Fuse ausgelöst.

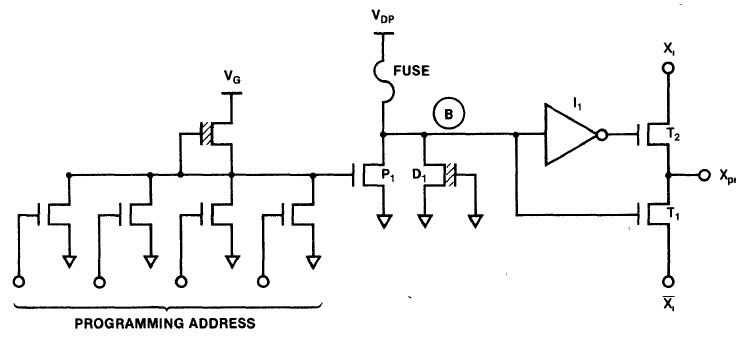

Die Application Note beschreibt die Schaltung zur Auswahl der Reservezeilen und Reservespalten genauer. Jede Fuse befindet sich in einem sogenannten "Programming Element", das am Ausgang zwei Transistoren besitzt. Bei intakter Fuse ist der untere Transistor aktiv. Durchtrennt man die Fuse, dann wird der obere Transistor aktiv. Vg und Vdp müssen über die Testpads zugeführt werden. Das dritte Testpad wird in der Application Note nicht näher beschrieben. Auf dem Die sieht man, dass darüber der Strom, mit dem die Fuse ausgelöst wird, abfließen kann. Wie die einzelnen Fuses ausgewählt werden hat Intel nicht offengelegt. Dem Schaltbild nach erfolgt die Adressierung mit vier Leitungen. Auf dem Die meint man erkennen zu können, dass die normalen Adressleitungen für die Auswahl der Fuses genutzt werden. Das erscheint zumindest logisch.

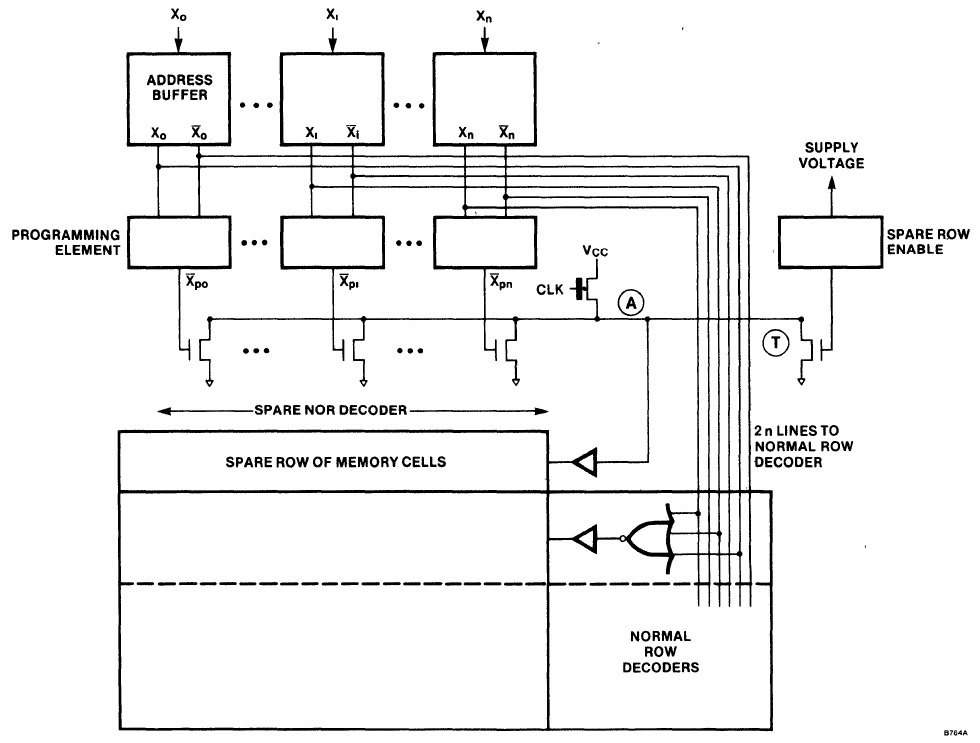

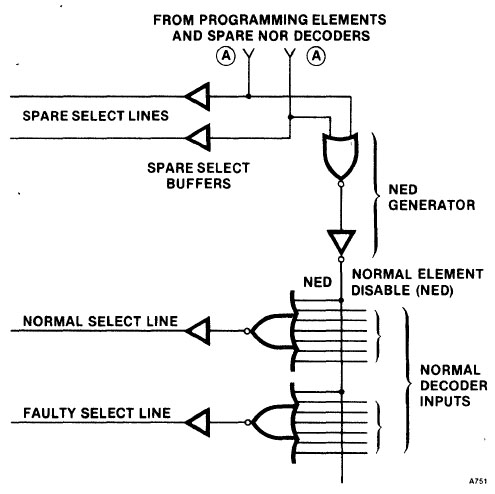

Das obige Bild zeigt, wie Reservezeilen in den Adressbereich eingebunden werden. Zuerst muss man die Fuse "Spare Row Enable" auslösen. Die zugehörige Reservezeile wird dann bei einer Zeilenadresse aktiv. Die Konfiguration der Fuses bestimmt welche Adresse der Reservezeile zugeordnet wird. Dazu leitet jedes programmierbare Element entweder sein Adressbit oder das invertierte Adressbit weiter.

Damit erklärt sich die Anzahl der Fuses. Im linken Bereich befinden sich 32, im rechten Bereich 36 Fuses. 4 Fuses aktivieren bei Bedarf die zwei Reservezeilen und die zwei Reservespalten. Mit viermal 8 Fuses kann man dann den Reservezeilen und den Reservespalten jeweils eine Adresse zuordnen.

Parallel zur beschriebenen Schaltung sorgt eine Logik dafür, dass die normale Zeilenauswahl inaktiv bleibt, solange die Reservezeile aktiv ist.