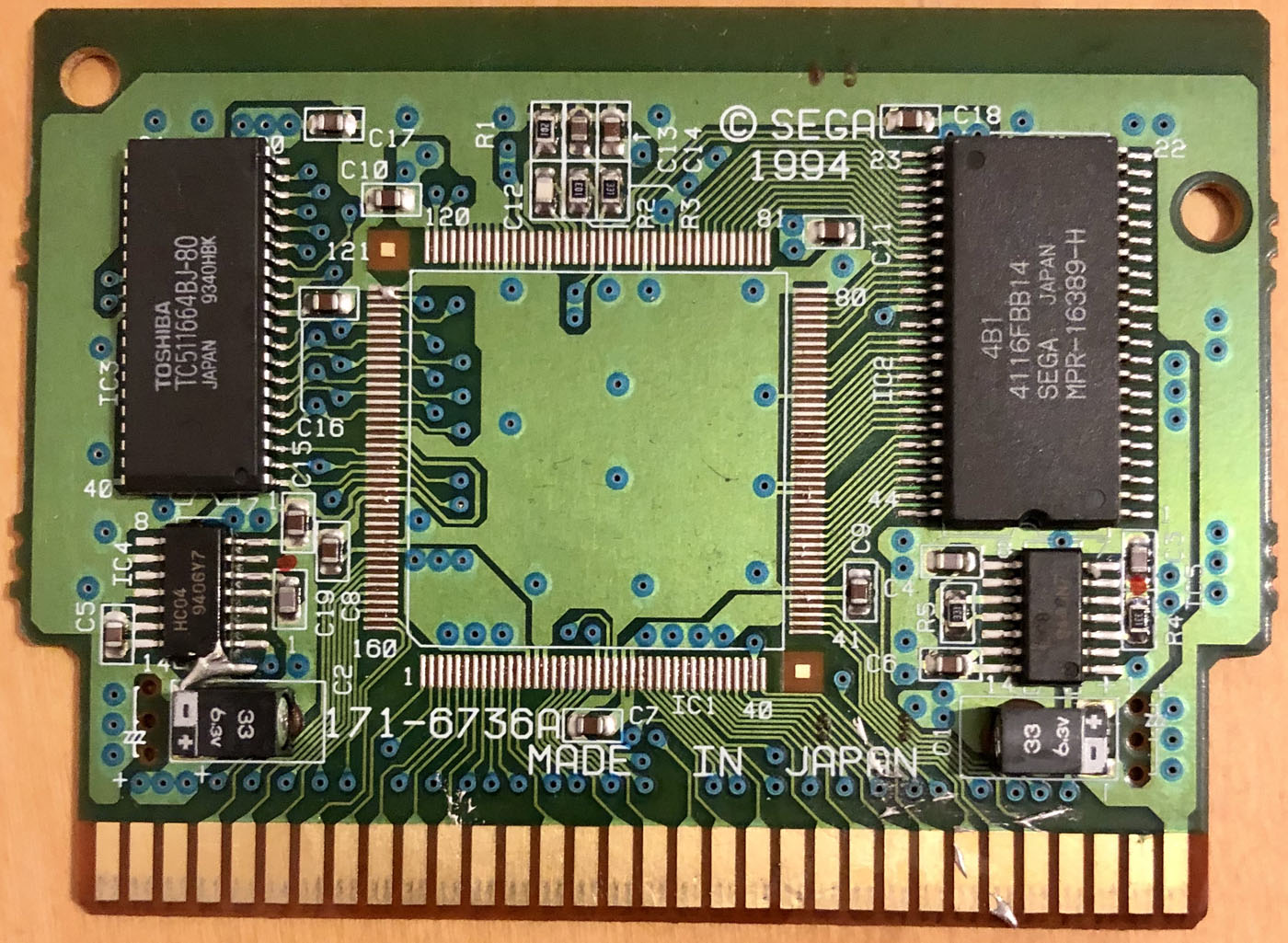

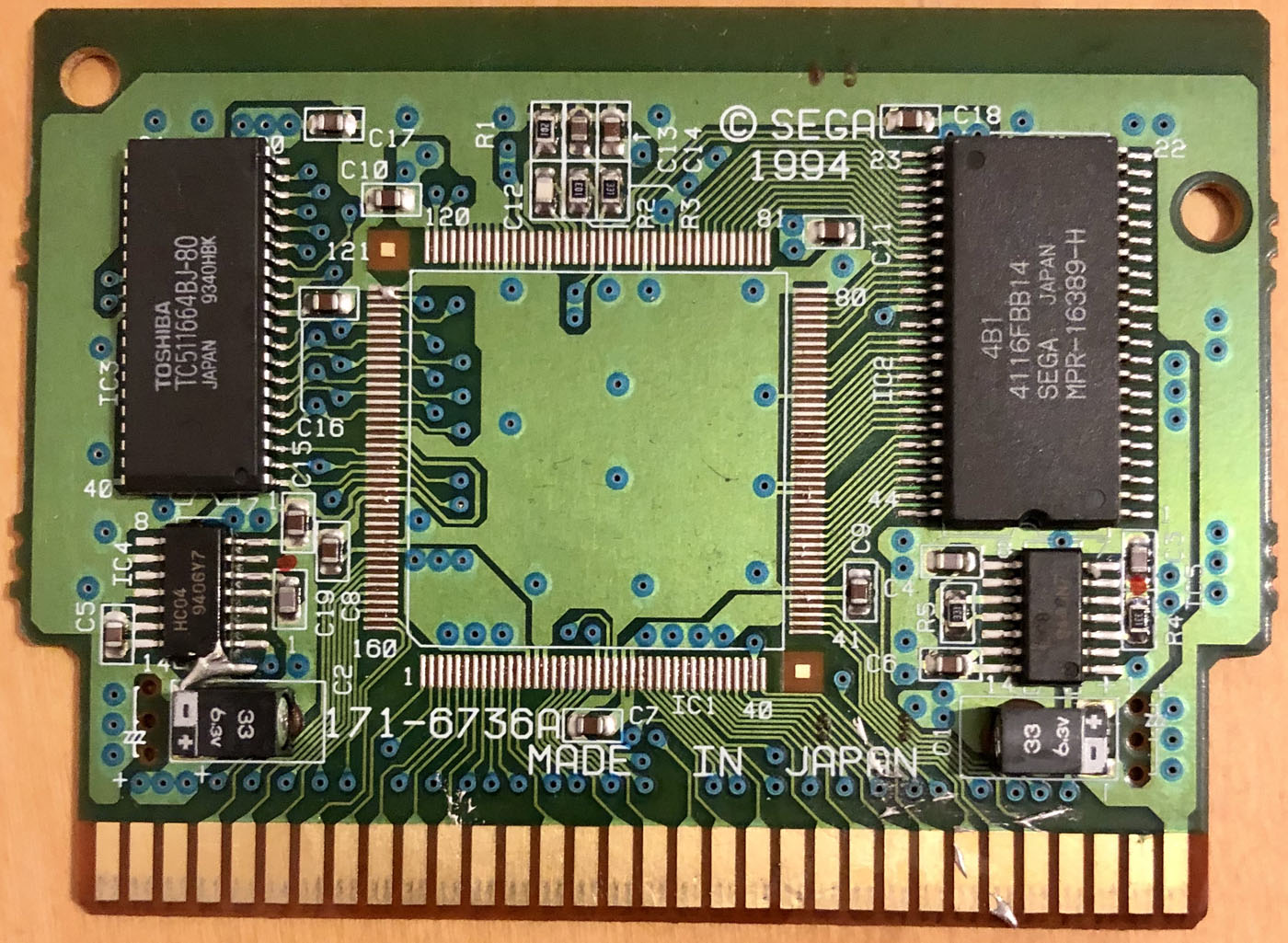

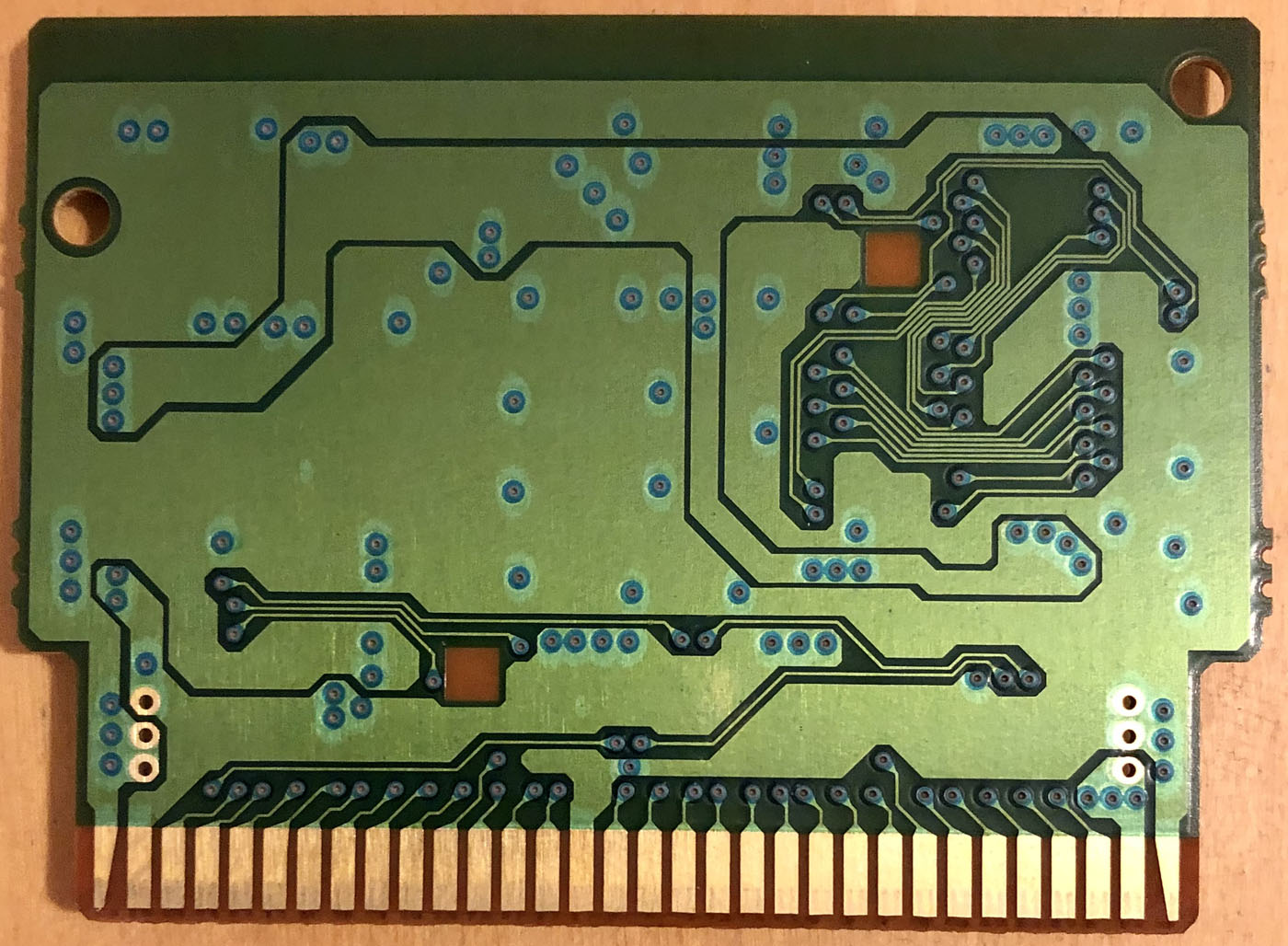

Spiele für die Spielkonsole Sega Mega Drive bestehen üblicherweise aus einer Einsteckkarte, auf der sich lediglich ein ROM befindet. Beim hier zu sehenden Spiel Virtua Racing hat Sega zusätzlich eine Art Grafikbeschleunigung integriert. Neben dem ROM mit den Spieledaten (IC2, rechts) enthält die Platine zusätzlich 128kB RAM (IC3, links) und den hier bereits entstückten SVP, den Sega Virtua Processor (IC1, Mitte). Der SVP ist ein DSP, ein digitaler Signalprozessor, der sehr effektiv spezielle Berechnungen durchführen kann. Er entlastet die Hardware der Spielekonsole, indem er Polygone rendert, also die Farbverteilung auf Flächen im dreidimensionalen Raum des Spiels berechnet.

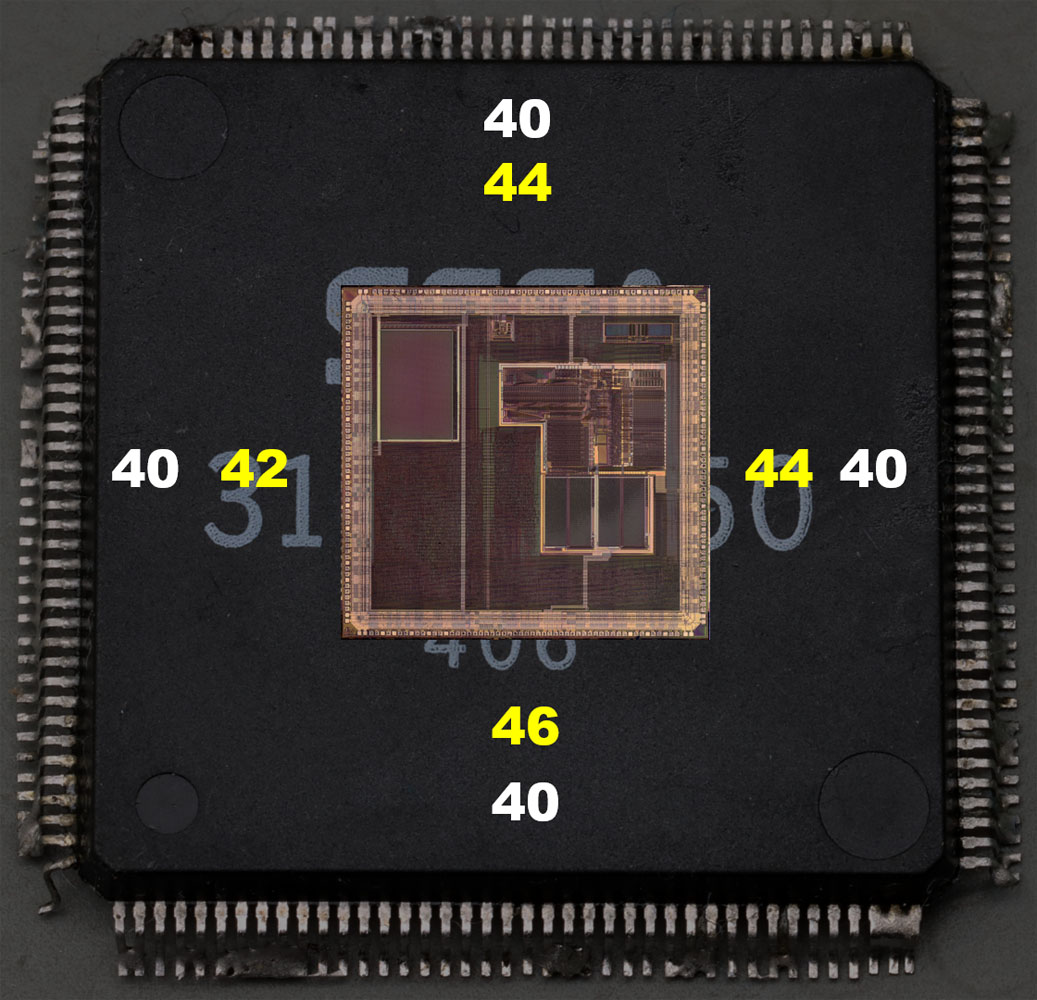

Der SVP trägt das Sega-Logo und die Bezeichnung 315-5750. Es handelt sich um ein TQFP-Gehäuse mit 160 Pins.

Eine recht ausführliche Analyse der Funktionalität des SVPs findet sich auf Github.

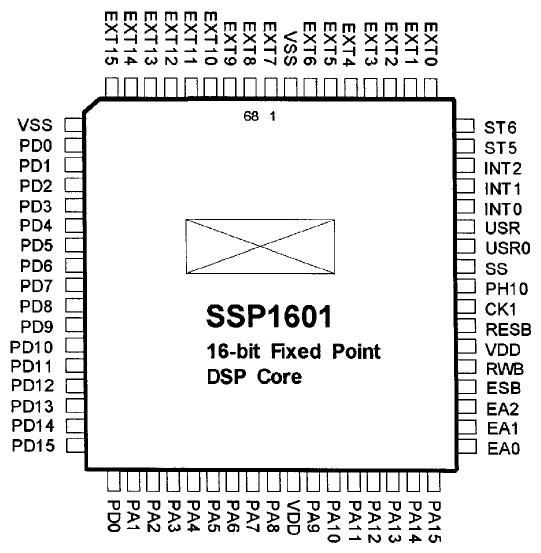

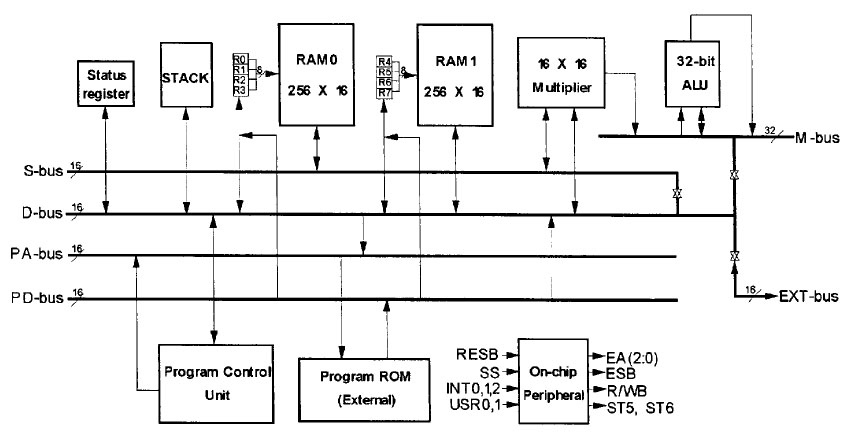

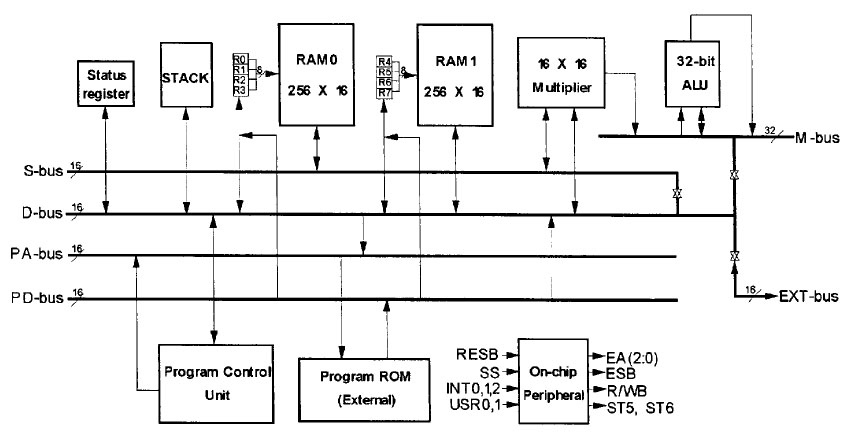

Online findet sich vielfach die Aussage, dass der SVP ein Samsung SSP1601 mit einer Sega-Beschriftung ist. Der SSP1601 ist ein DSP, der laut Datenblatt auf einem 0,8µm CMOS-Prozess basiert. Die maximale Taktfrequenz beträgt 25MHz. Neben zwei Bänken mit jeweils 256x16Bit RAM bietet der SSP1601 einen 16x16 Multiplikator und eine 32Bit ALU.

Es mag sein, dass der SVP auf einem SSP1601 basiert. Das sehr viel größere Gehäuse zeigt allerdings, dass es sich nicht nur um einen anders beschrifteten SSP1601 handelt.

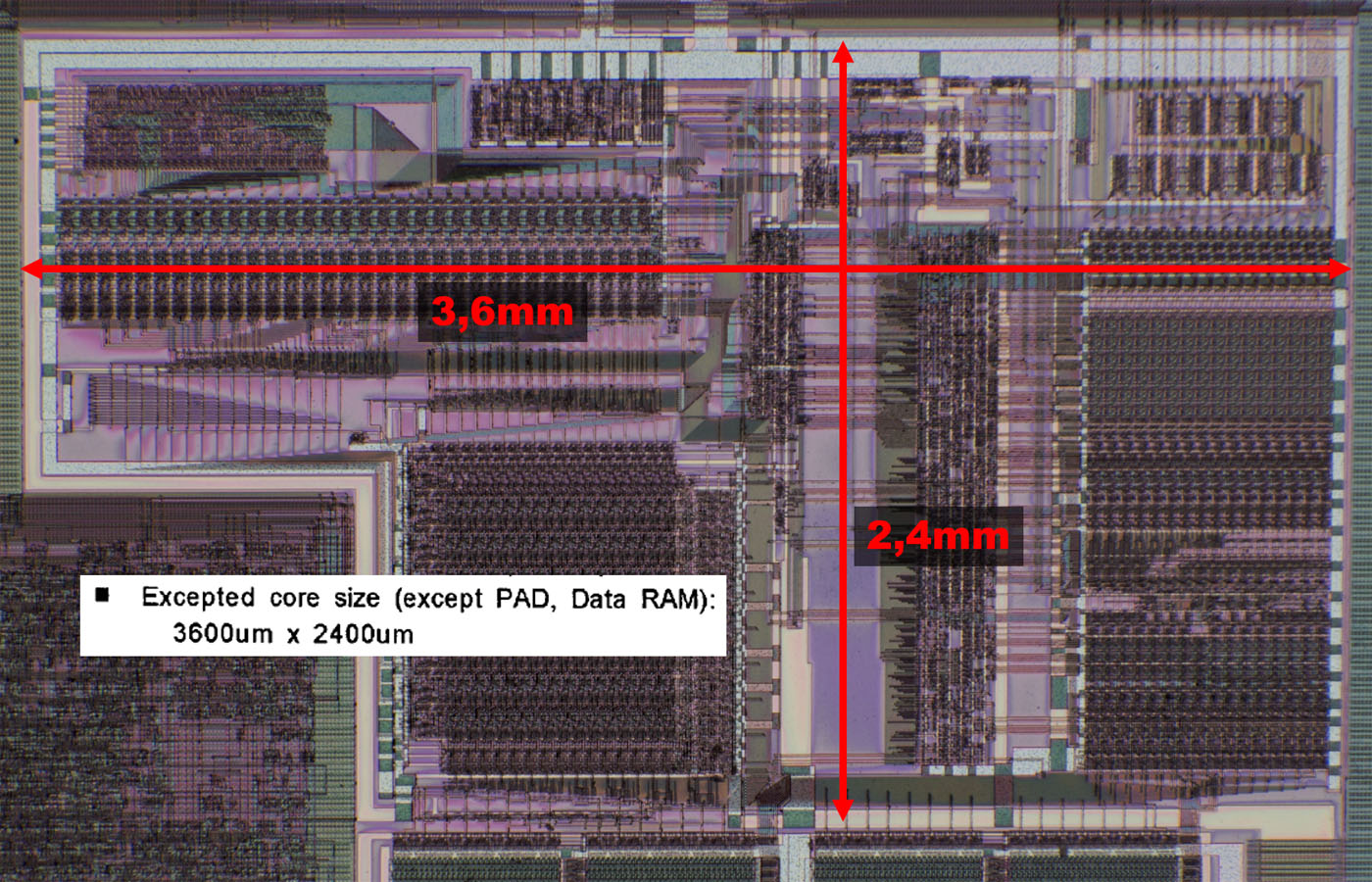

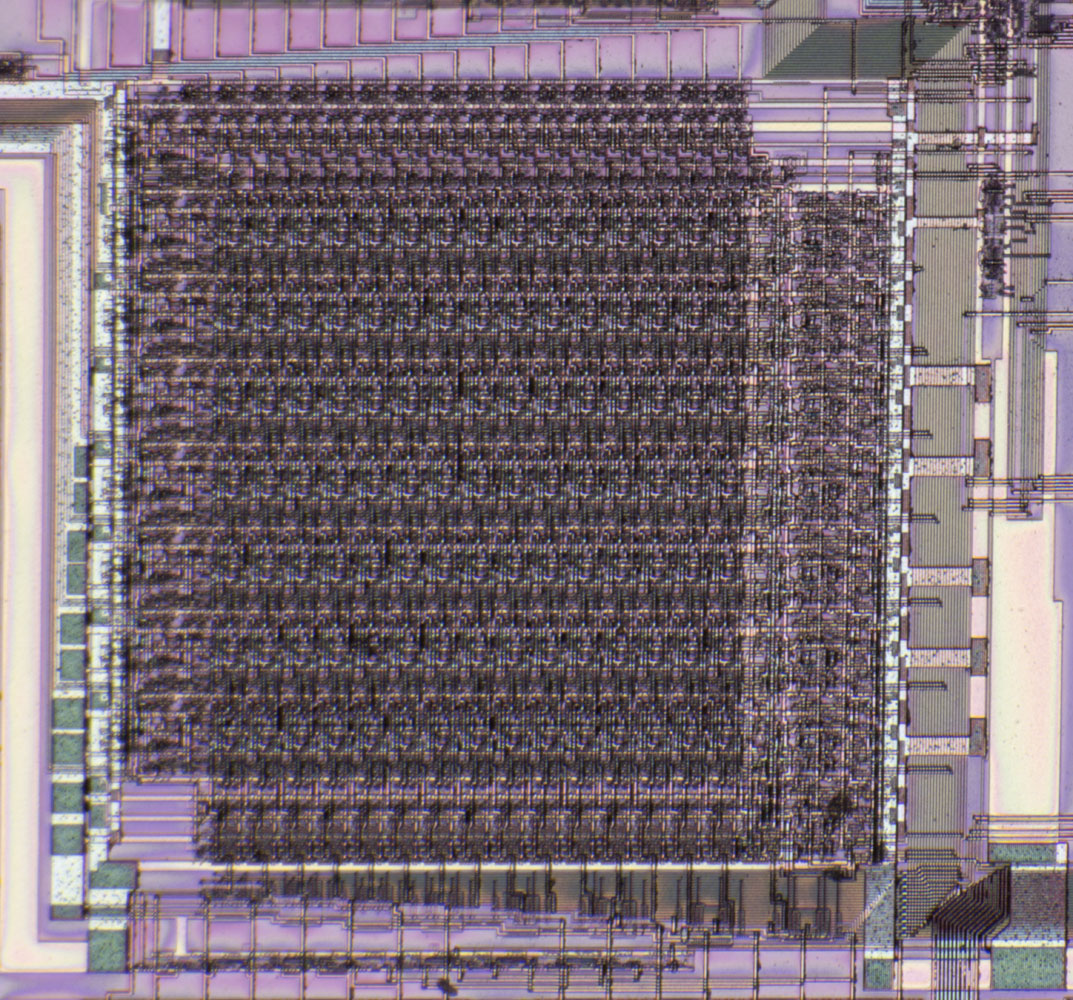

Die Abmessungen des Dies betragen 8,0mm x 7,6mm.

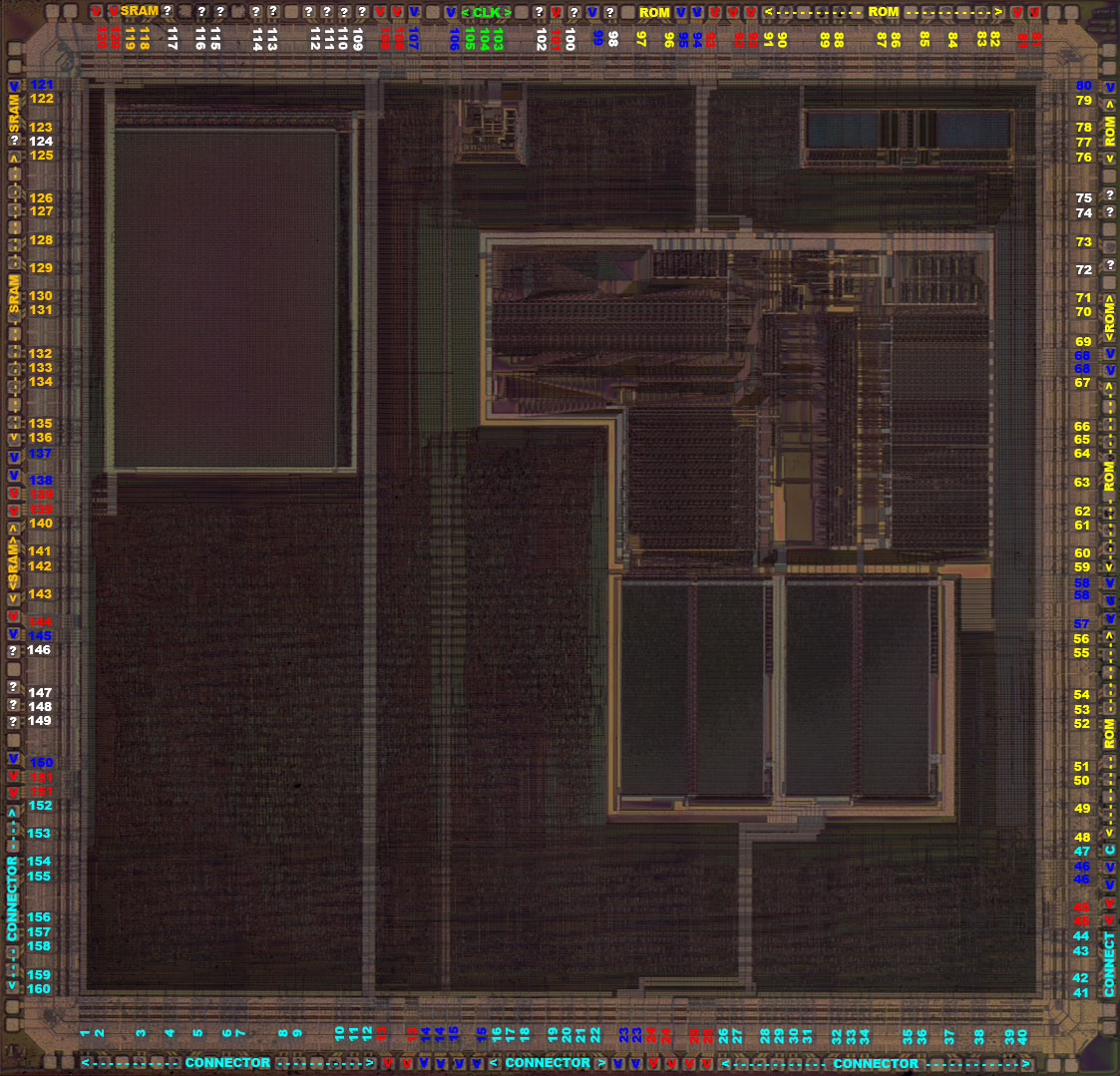

Das obige Bild ist auch in einer höheren Auflösung verfügbar: 16.312 x 15.632, 55MB.

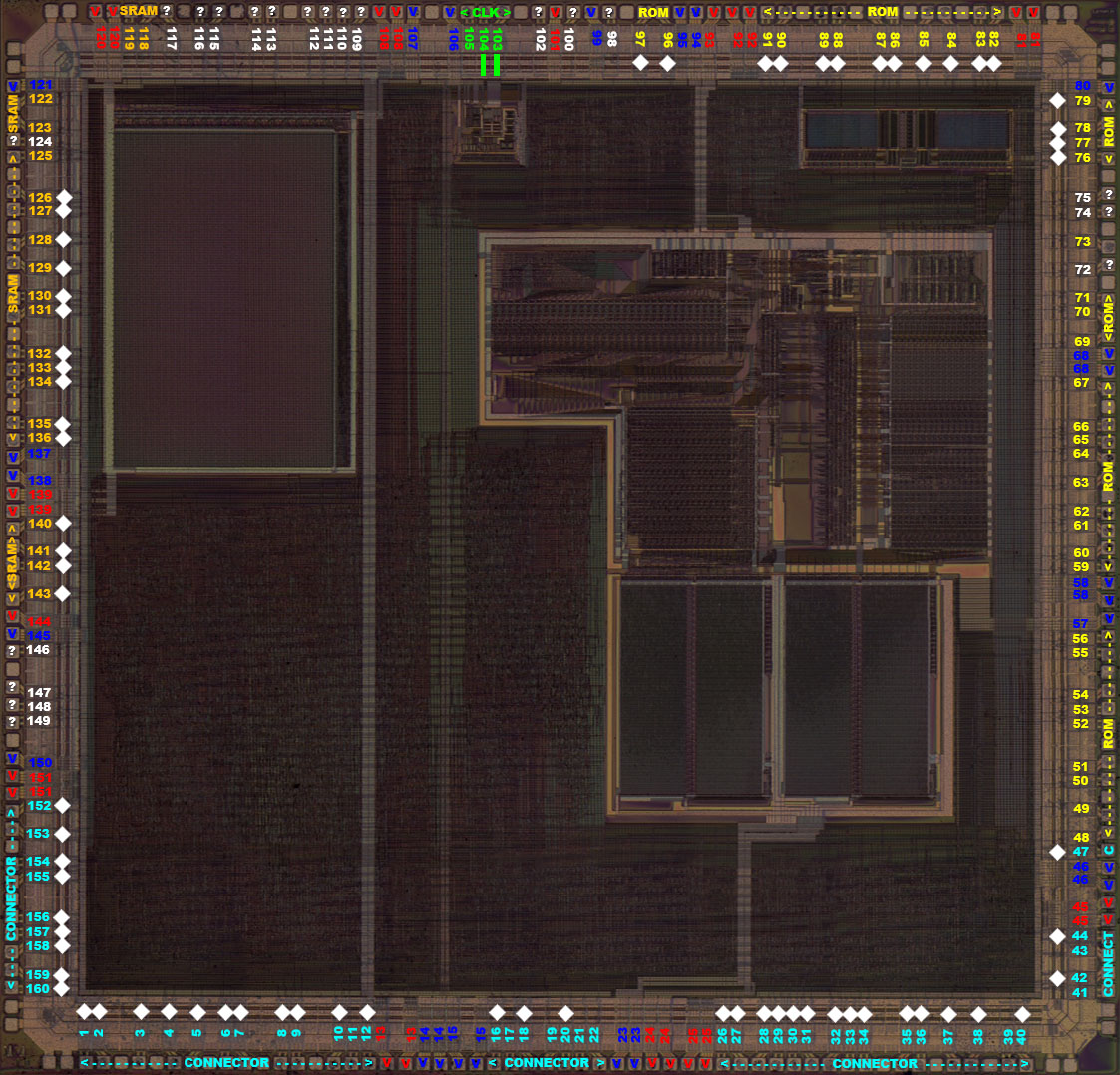

In der oberen rechten Ecke des Dies findet sich ein Copyright von Samsung. Das Design stammt aus dem Jahr 1993. Die interne Bezeichnung lautete anscheinend SEGA160FS. Die Zahlen 160 könnten auf den SSP1601 verweisen.

Die beiden SEGA160FS Schriftzüge befinden sich entweder in zwei Metalllagen oder in einer Metalllage und in einer Maske für Durchkontaktierungen. Es ist gut möglich, dass der SVP auf einem universellen System basiert, das lediglich über die Metalllagen für SEGA angepasst wurde.

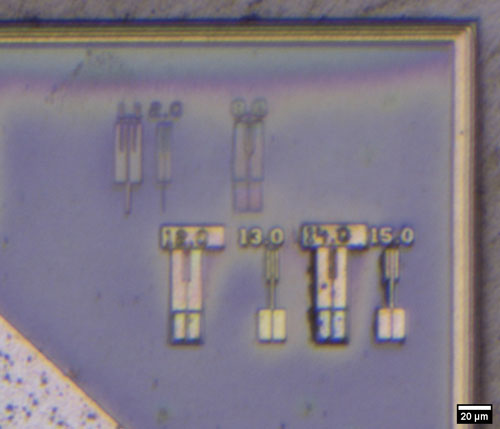

In der unteren linken Ecke befinden sich Teststrukturen für einige Masken.

Das Gehäuse des SVP bietet auf jeder Seite 40 Pins. Das Die besitzt oben und unten 58 Bondpads, links und rechts sind es 56 Bondpads. Kontaktiert wurden 42, 44, 44 und 46 Bondpads. Versorgungspins sind teilweise mit mehreren Bondpads verbunden.

Die meisten Bondpads lassen sich über das Layout der Platine ihrer Funktion zuordnen.

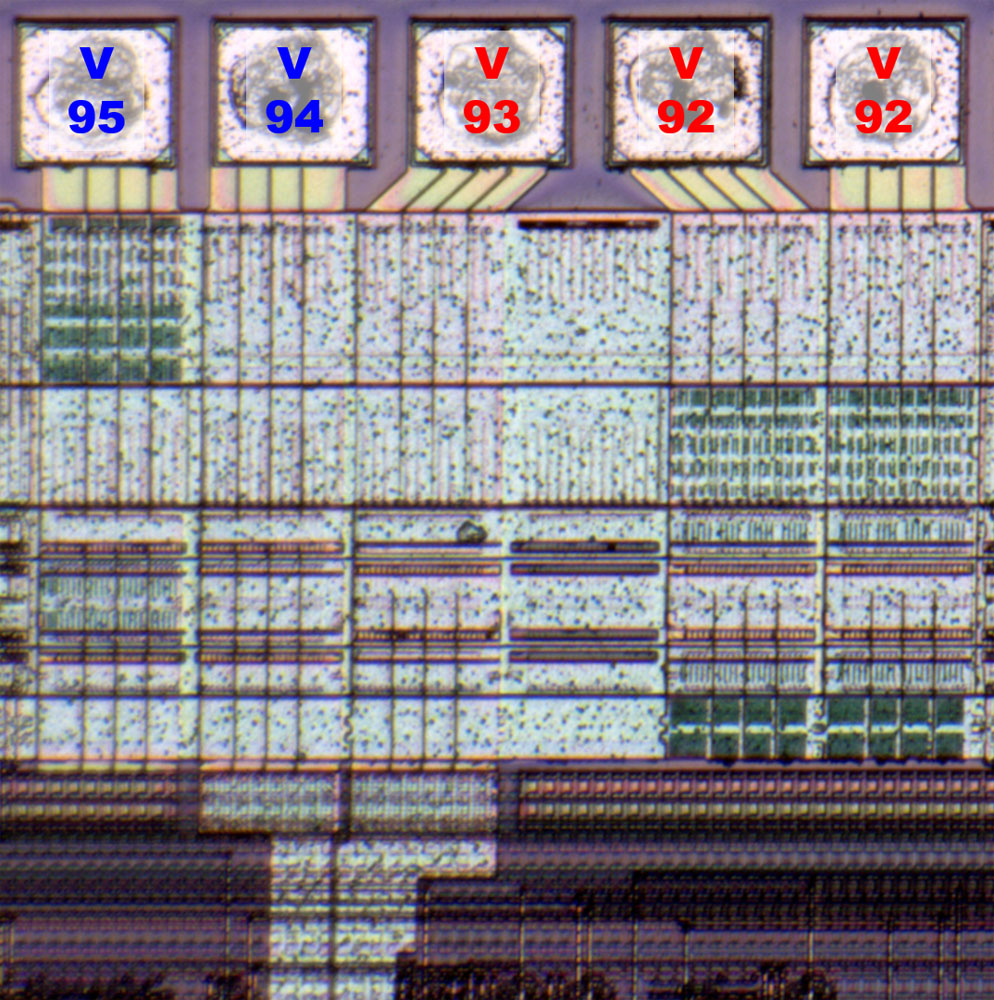

Die Bondpads zur Versorgung des Chips sind massiver angebunden als die Ein- und Ausgänge. Je nach Potential kontaktieren sie unterschiedliche Bereiche der Rahmenstruktur (95 und 92). Einige Versorgungen führen außerdem ins Innere der Schaltung (94 und 93).

An den Rändern des Dies befinden sich auch nicht kontaktierte Bondpads. Im Detail zeigt sich, dass die meisten dieser Bondpads gar nicht in die Schaltung eingebunden sind. Genauso finden sich auch ungenutzte I/O-Strukturen. Das spricht dafür, dass es sich um einen eher universellen Baustein handelt.

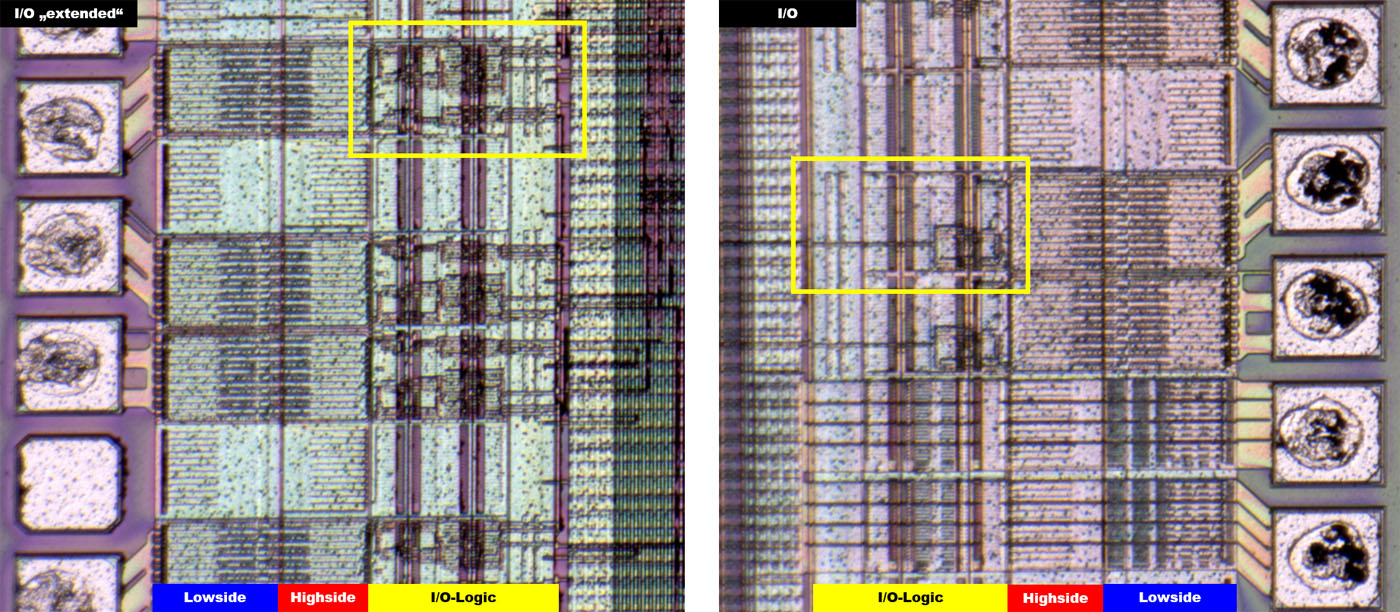

Bei den verwendeten Bondpads führen zwei breite Leitungen und eine schmale Leitung in die Rahmenstruktur. In den beiden breiten, äußeren Rahmen befinden sich die Ausgangstreiber. Höchstwahrscheinlich dienen diese Bereiche bei Eingängen gleichzeitig als Schutzstrukturen. Weiter im Inneren des Chips verlaufen zusätzliche Versorgungsleitungen, innerhalb derer zwei Logikzeilen integriert sind. Es fällt auf, dass es bei diesen Logik-Strukturen nur zwei Varianten gibt. Die rechte Variante ist sehr einfach gehalten und besitzt gut erkennbar nur eine Zuleitung. Die linke Logik ist komplexer und wird von mehreren Leitungen angefahren. Mit dem Hintergrund der Verwendung der einzelnen Ein-/Ausgänge kann man spekulieren, dass die größere Variante eine Art Latch-Funktion darstellt, die ein synchronisiertes Einlesen und ein Zwischenspeichern des Eingangspegels ermöglicht.

Bei der RAM- und der ROM-Schnittstelle (orange/gelb) werden zum Beispiel die Adressleitungen von einfachen Ausgängen bedient. Die Pins, die Datenleitungen einlesen müssen, sind dagegen mit den erweiterten Logikstrukturen bestückt (weiße Rauten).

Abweichende Strukturen finden sich abgesehen von den Versorgungsleitungen nur im Bereich der Taktaufbereitung. Dort führen zwei Leitungen aus der Schaltung direkt zu zwei Bondpads (grün).

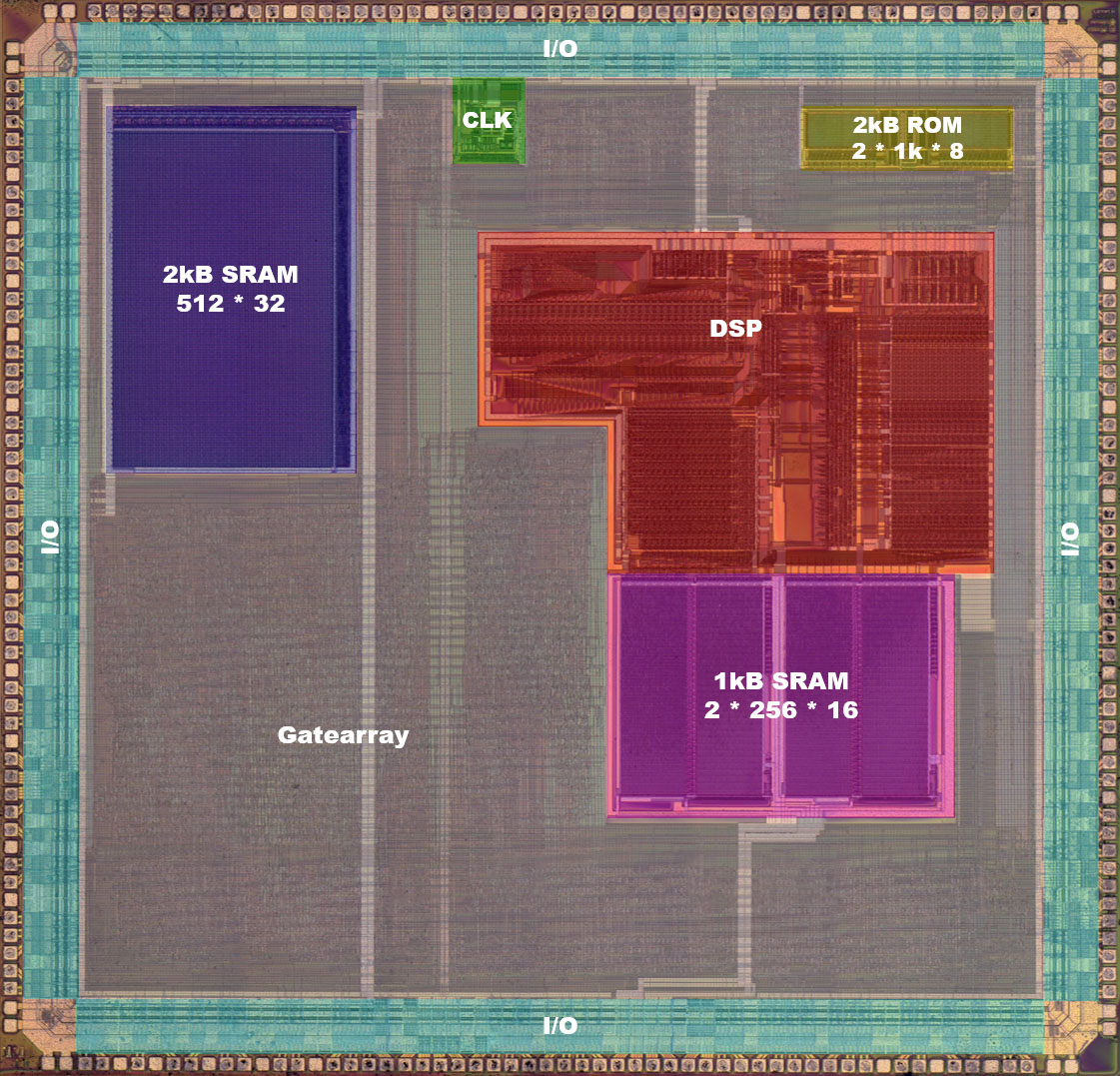

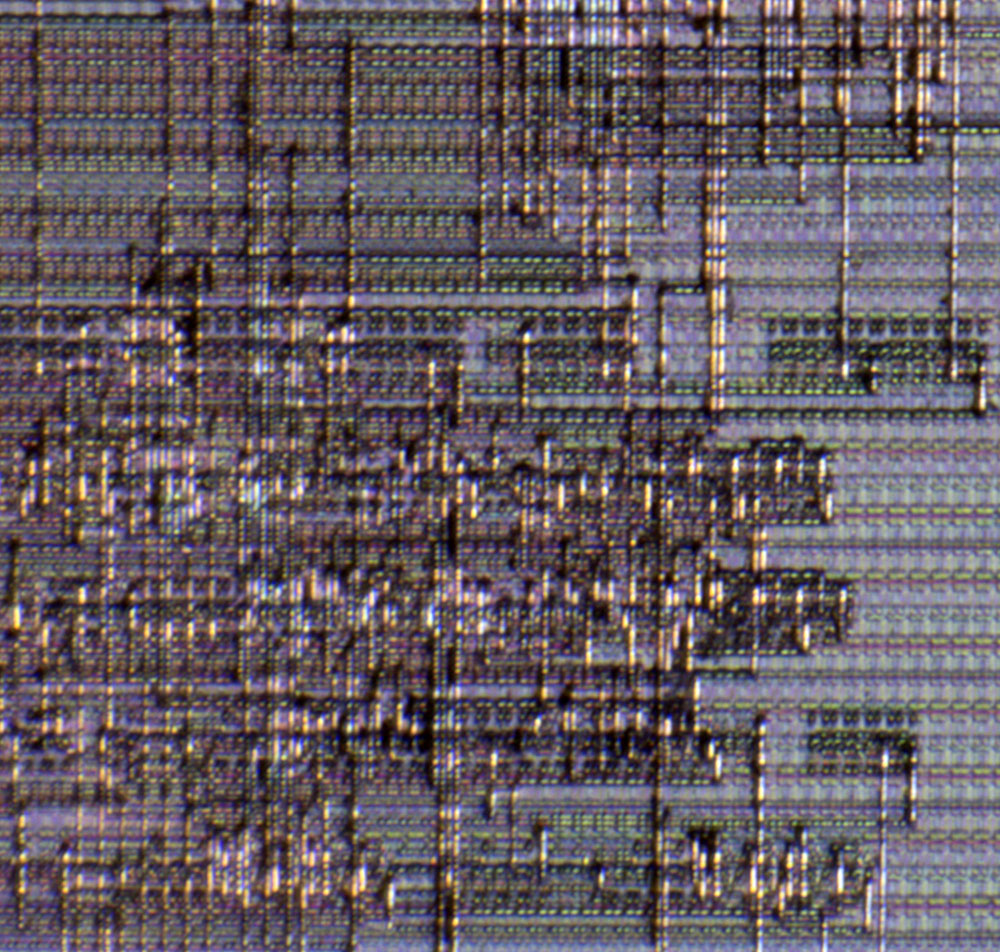

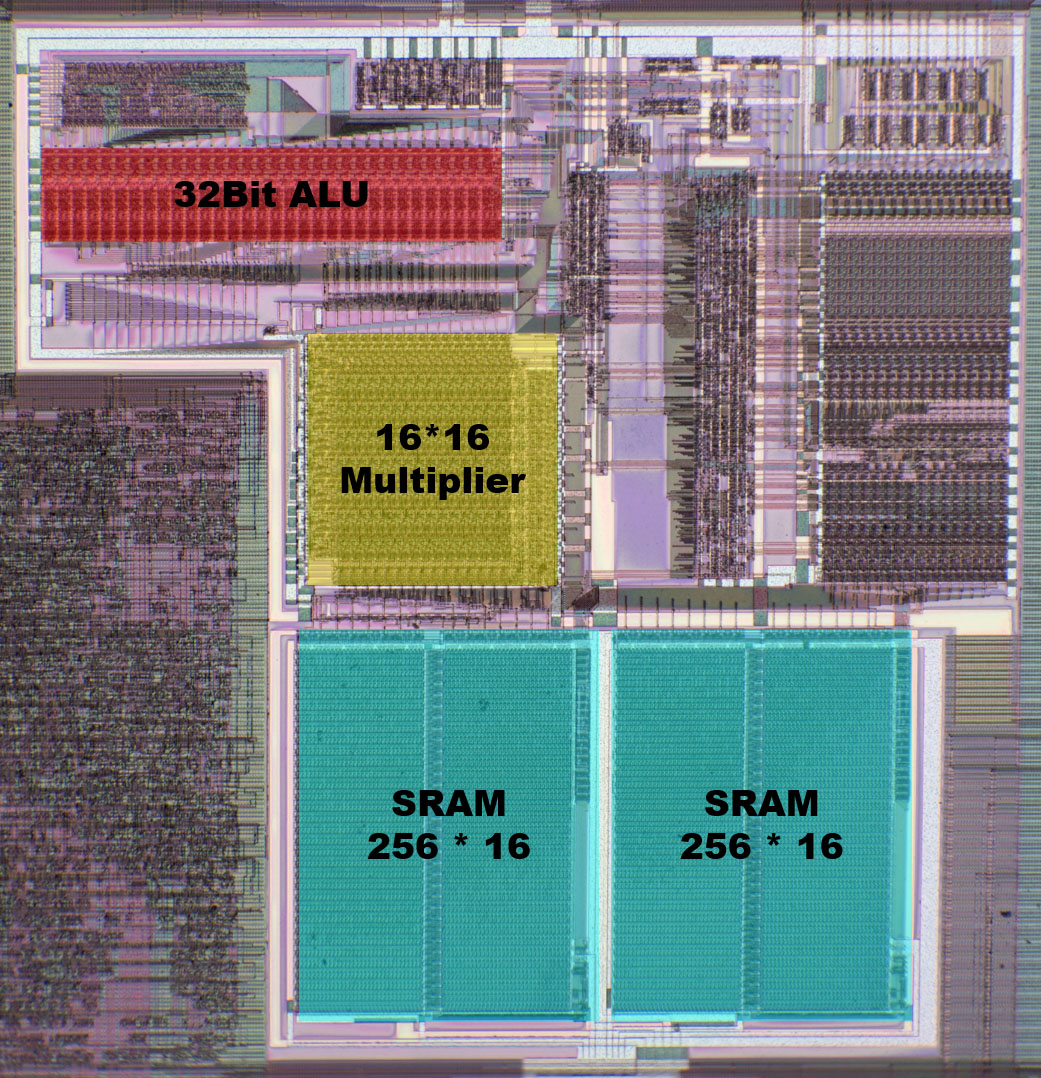

Die unterschiedlichen Strukturen der verschiedenen Funktionsblöcke geben schnell einen groben Überblick über den Aufbau des SVPs. Die Ein- und Ausgänge erstrecken sich über alle vier Kanten (türkis). An der oberen Kante befindet sich ein kleiner Schaltungsteil (grün), in dem der Baustein wahrscheinlich seinen Arbeitstakt erzeugt.

Der DSP selbst fällt durch seine unterschiedlichen, aber in sich wieder regelmäßigen Strukturen auf (rot). Direkt angebunden an den DSP ist ein großer Speicher mit der dafür typischen sehr gleichmäßigen Struktur (rosa). Wie sich noch zeigen wird, handelt es sich um zwei SRAM-Bereiche mit jeweils 256*16Bit.

In der oberen rechten Ecke des Dies ist ein ROM integriert (gelb). Es besteht aus zwei Bereichen mit jeweils 1kB. Höchstwahrscheinlich befinden sich dort einige Grundfunktionen des SVPs. In der linken oberen Ecke befindet sich ein weiteres SRAM mit einer Kapazität von 2kB (blau). In diesen Speicher kann der Anwender wahrscheinlich Code ablegen, der besonders schnell ausgeführt werden soll.

In den freien Bereichen zwischen den großen Funktionsblöcken ist ein Gatearray integriert (weiß). Darin befindet sich die Logik, die die einzelnen Funktionsblöcke miteinander, mit den externen Komponenten und der Spielekonsole verbindet. Die große Fläche lässt vermuten, dass der dort abgebildete Funktionsumfang nicht unerheblich ist.

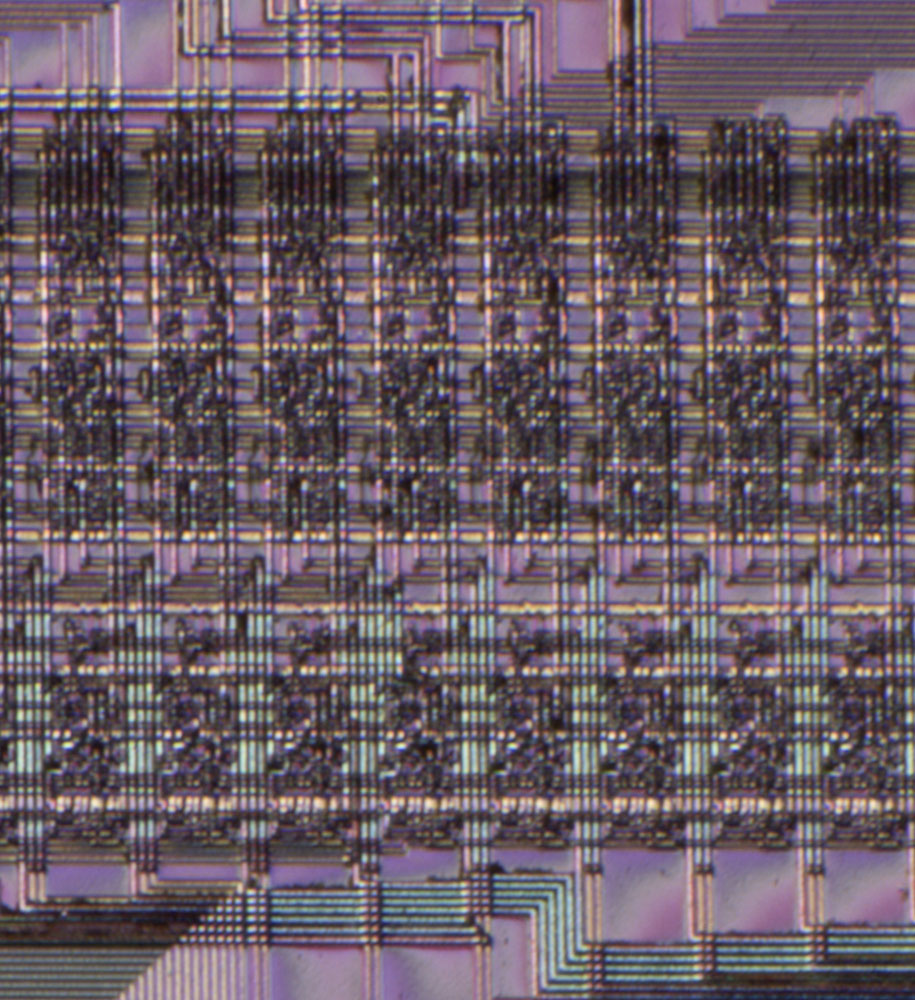

In der Gatearray-Fläche sind an einigen Stellen die Zeilen zu erkennen, die die Standardzellen enthalten. Diese Zellen werden über mindestens zwei Metalllagen zu den gewünschten Schaltungen zusammengefügt.

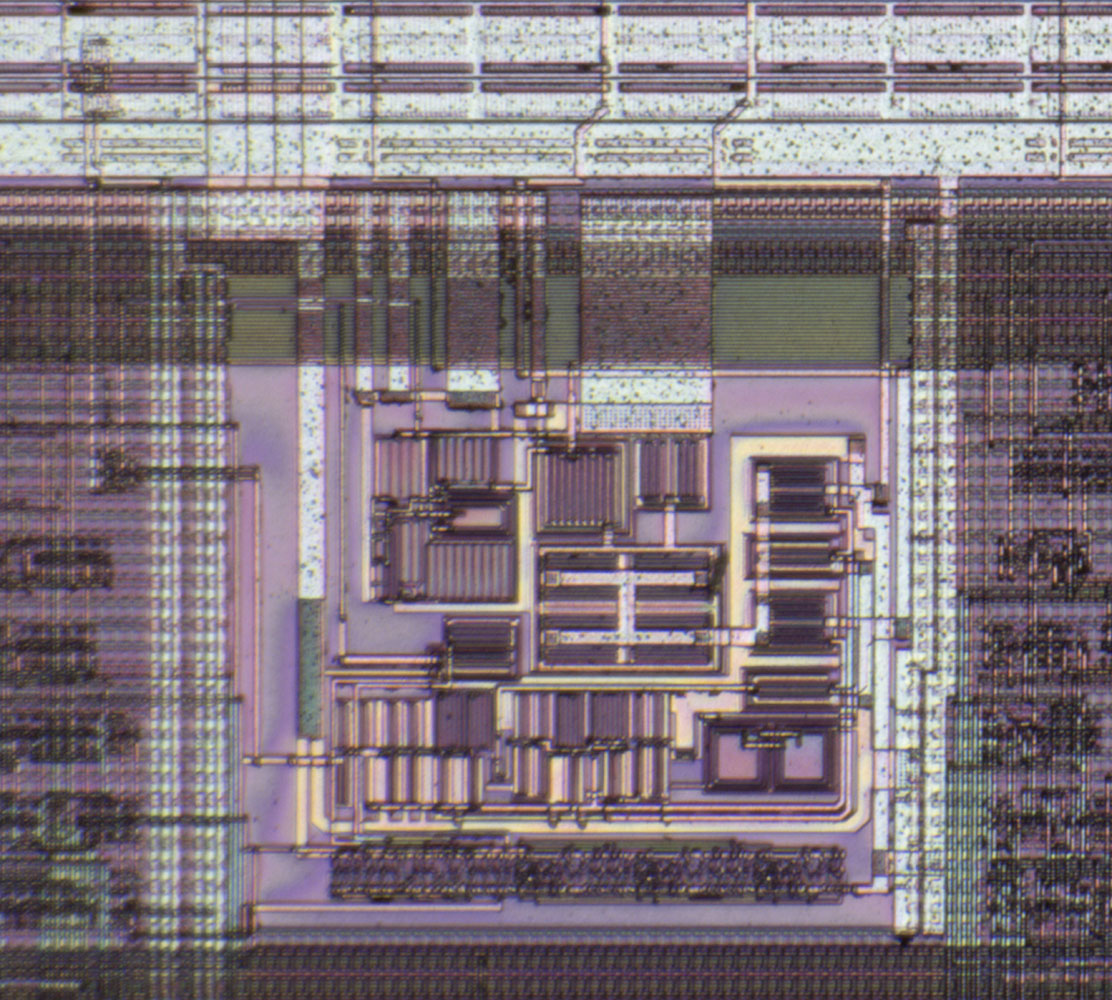

Der Bereich an der oberen Kante, der wahrscheinlich den Arbeitstakt des Bausteins bereitstellt, beinhaltet relativ große Elemente. Die Schaltung ist über zwei Pins direkt und exklusiv mit einem externen Kondensator verbunden. Eine spezielle Taktzuführung aus der Spielekonsole lässt sich nicht erkennen. Es ist gut denkbar, dass es sich hier um einen Oszillator handelt, über den der SVP sich seinen eigenen Arbeitstakt erzeugt. Vielleicht könnte man den DSP sogar übertakten, indem man den Wert der externen Kapazität oder der umgebenden Bausteine ändert.

Der ROM in der oberen rechten Ecke des Dies ist bezogen auf den Flächenverbrauch sehr viel kleiner als der im SVP integrierte RAM. Das liegt daran, dass in einem maskenprogrammierten ROM eine Speicherzelle üblicherweise nur aus einem Transistor besteht und entsprechend wenig Fläche benötigt. Eine SRAM-Zelle benötigt dagegen üblicherweise sechs Transistoren.

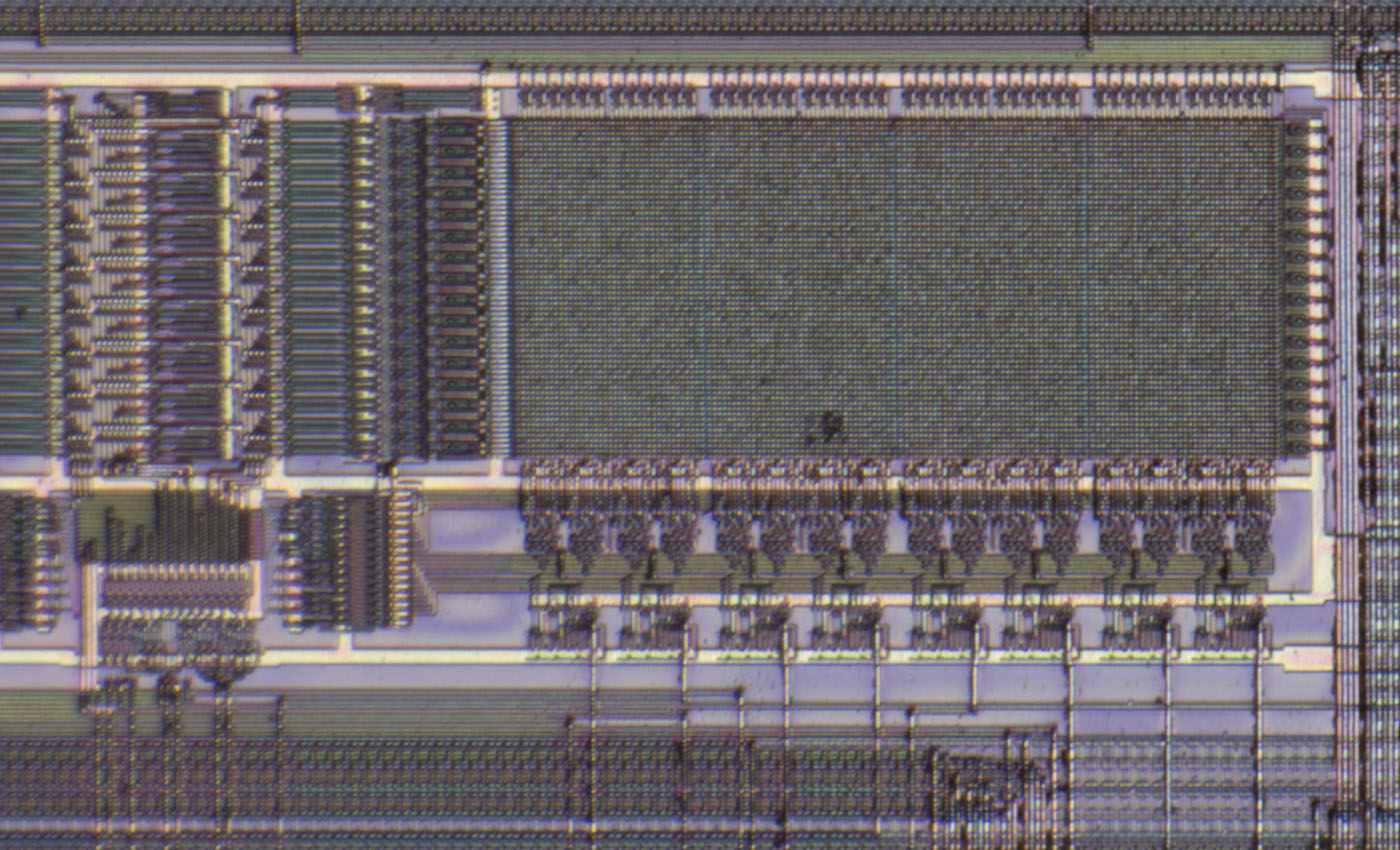

Die Strukturen sind sehr klein, man kann aber trotzdem die Speichergröße abschätzen. Der Aufbau erinnert an den Masken-ROM MK37092 von Mostek, wobei hier anscheinend die Ansteuerung seitlich erfolgt und die Daten nach unten ausgegeben werden.

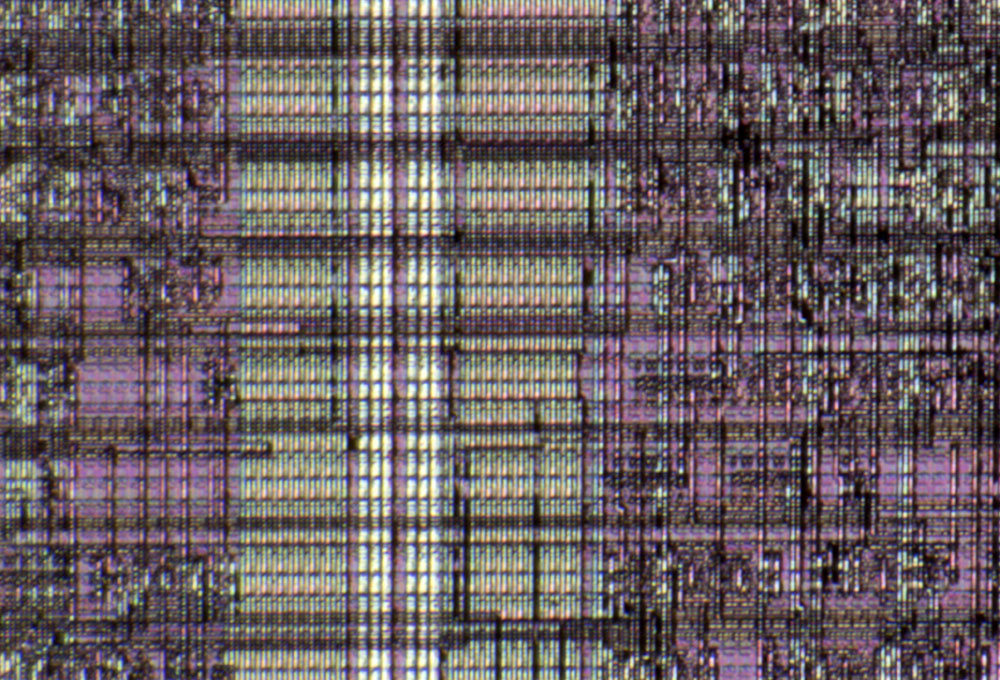

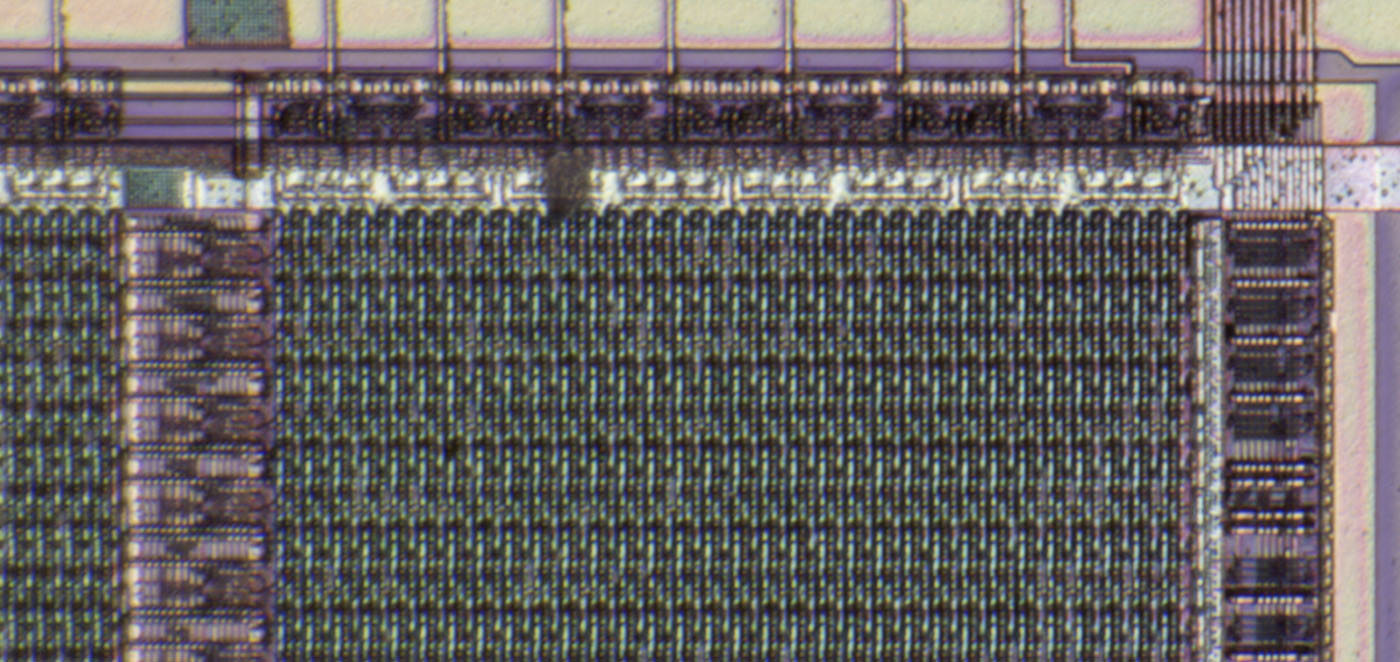

Zwischen den beiden Speicherblöcken werden von unten mehrere Steuersignal zugeführt und aufbereitet (weiß). Von dort aus führen nach rechts und nach links jeweils 4+2 Steuersignale (rot). Auf der Innenseite eines jeden Speicherblocks werden daraus 64 Steuersignale erzeugt und darüber eine einzelne Zeile aktiviert (rot). Jeder der zwei Speicherblöcke speist unabhängig vom anderen Bereich an der Unterseite acht Datenleitungen (gelb). 12 Steuersignale (grün) ermöglichen es eine von 18 Spalten auf jede der Datenleitungen zu schalten. Insgesamt ergibt sich so ein 2kB großer Speicher.

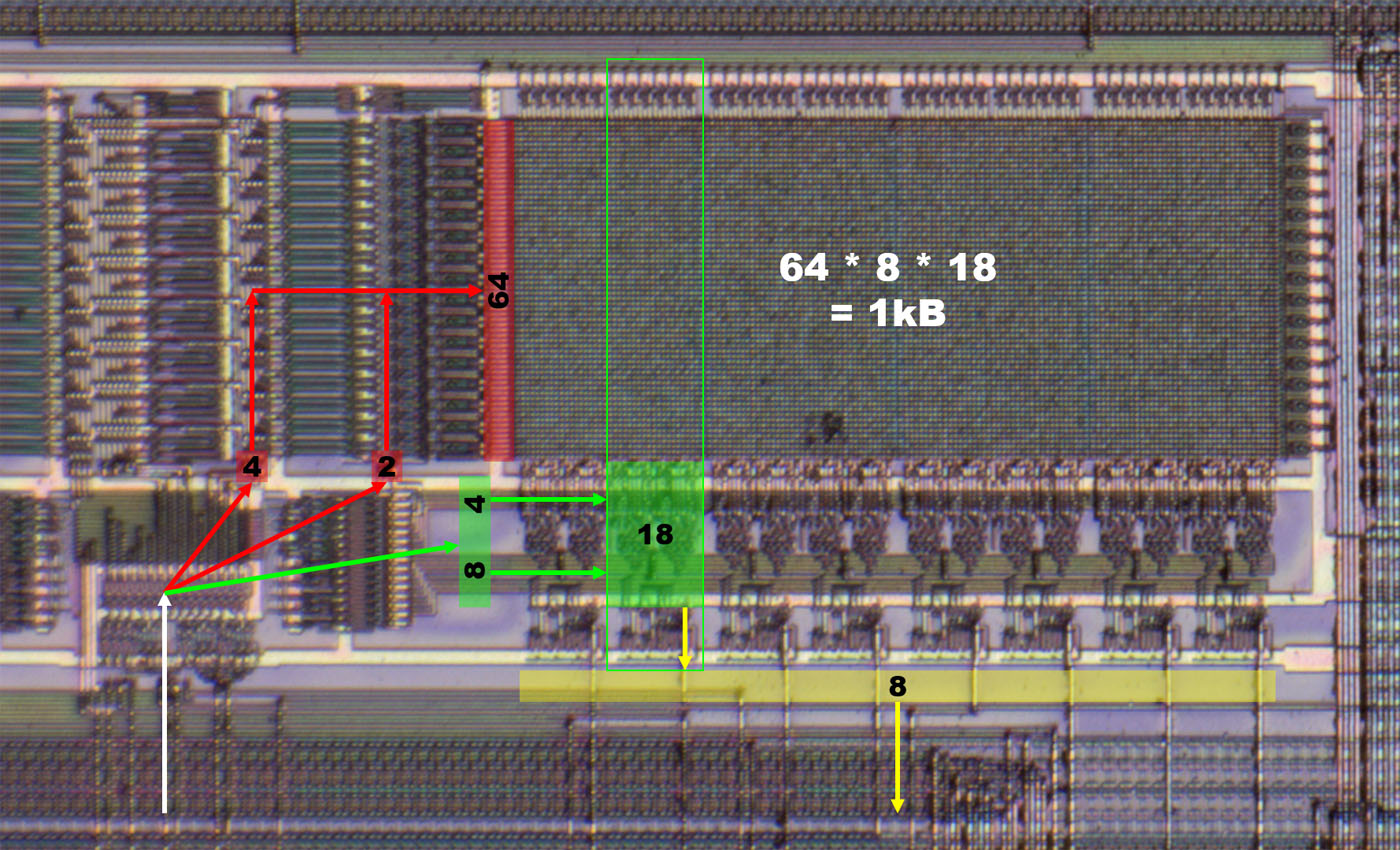

Der SRAM in der oberen linken Ecke des Dies nimmt im Vergleich zum ROM wieder sehr viel mehr Fläche ein. An der oberen Kante des Speicherbereichs befindet sich eine 32Bit breite Datenschnittstelle (grün). Vier Steuerleitungen verbinden jede Datenleitung mit einer von acht Spalten des Speicherbereichs (blau/türkis). Von rechts treffen sieben Steuerleitungen ein. An dieser Kante befindet sich die Schaltung, die eine der 64 Zeilen auswählt. Insgesamt ergibt sich so eine Speichergröße von 2kB.

In der Zeilenauswahl kann man gerade so die unterschiedlich platzierten Durchkontaktierungen erkennen, die die Adressierung einer einzelnen Zeile ermöglichen. Die einzelnen Speicherzellen lassen sich nur noch erahnen. Es fällt auf, dass für die Auswahl von 64 Zeilen sechs Steuersignale ausreichend gewesen wären. Es wurden aber tatsächlich alle sieben Steuerleitungen für die Zeilenauswahl herangezogen.

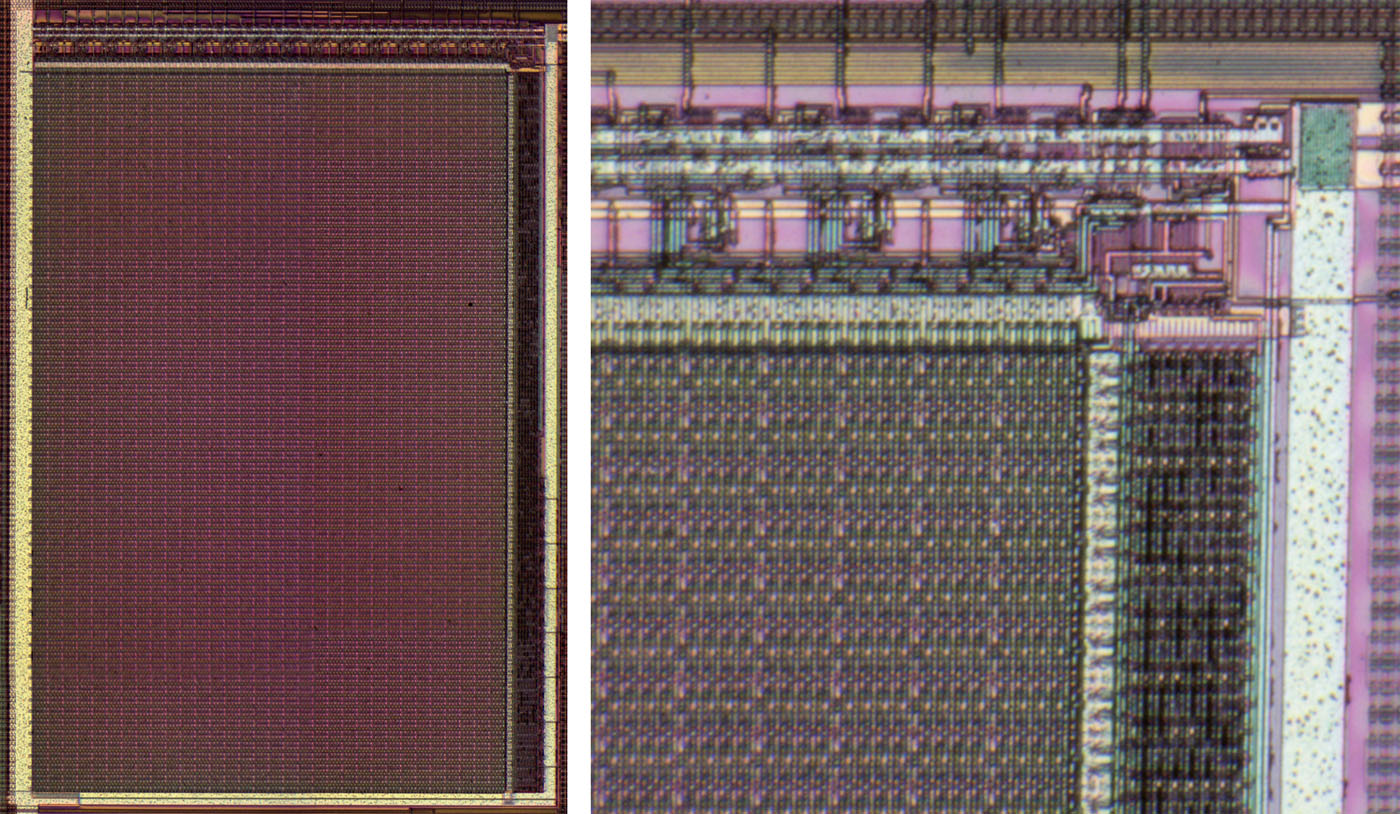

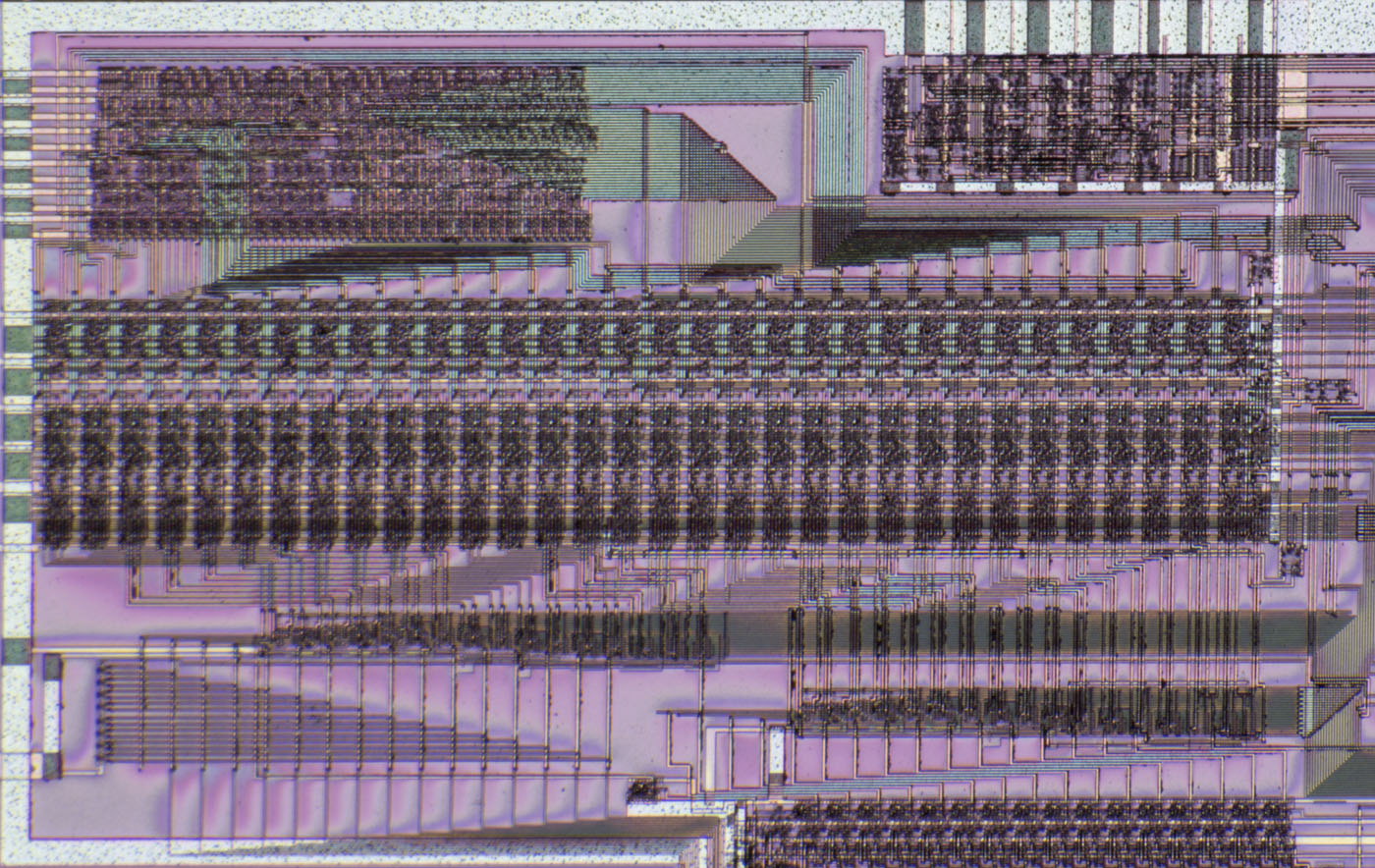

Der DSP-Bereich setzt sich durch seine speziellen Strukturen deutlich ab. Der hier zu sehende Ausschnitt ist auch in einem größeren Format verfügbar: 4.416 x 4.572, 4MB.

Das Datenblatt des SSP1601 enthält einen Hinweis, dass die Abmessungen des DSPs selbst 3,6mm x 2,4mm betragen. Das passt genau zu der Fläche, die der hier integrierte DSP-Kern einnimmt.

Das Datenblatt des SSP1601 enthält auch ein Blockschaltbild. Der 32Bit-ALU und den 16*16-Multiplizierer lassen sich relativ gut erkennen. Die Größe des SRAM (2*512B) scheint zu den Angaben im Datenblatt des SSP1601 zu passen.

Die nicht zugeordneten Strukturen sind groß genug, dass sie den Rest des Blockschaltbilds enthalten könnten. Wirklich identifizieren lassen sich diese Funktionsblöcke aber nicht.

Die ALU (arithmetisch-logische Einheit) besteht aus 32 Einzelelementen.

Der 16*16-Multiplizierer ist durch seine symmetrische, quadratische Struktur zu erkennen.

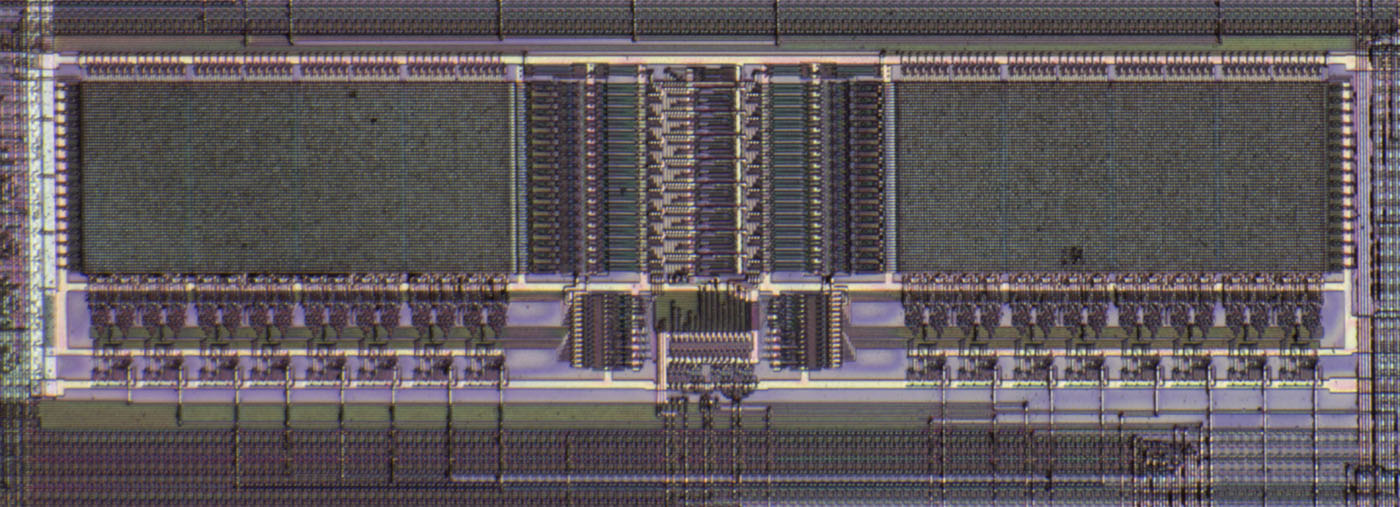

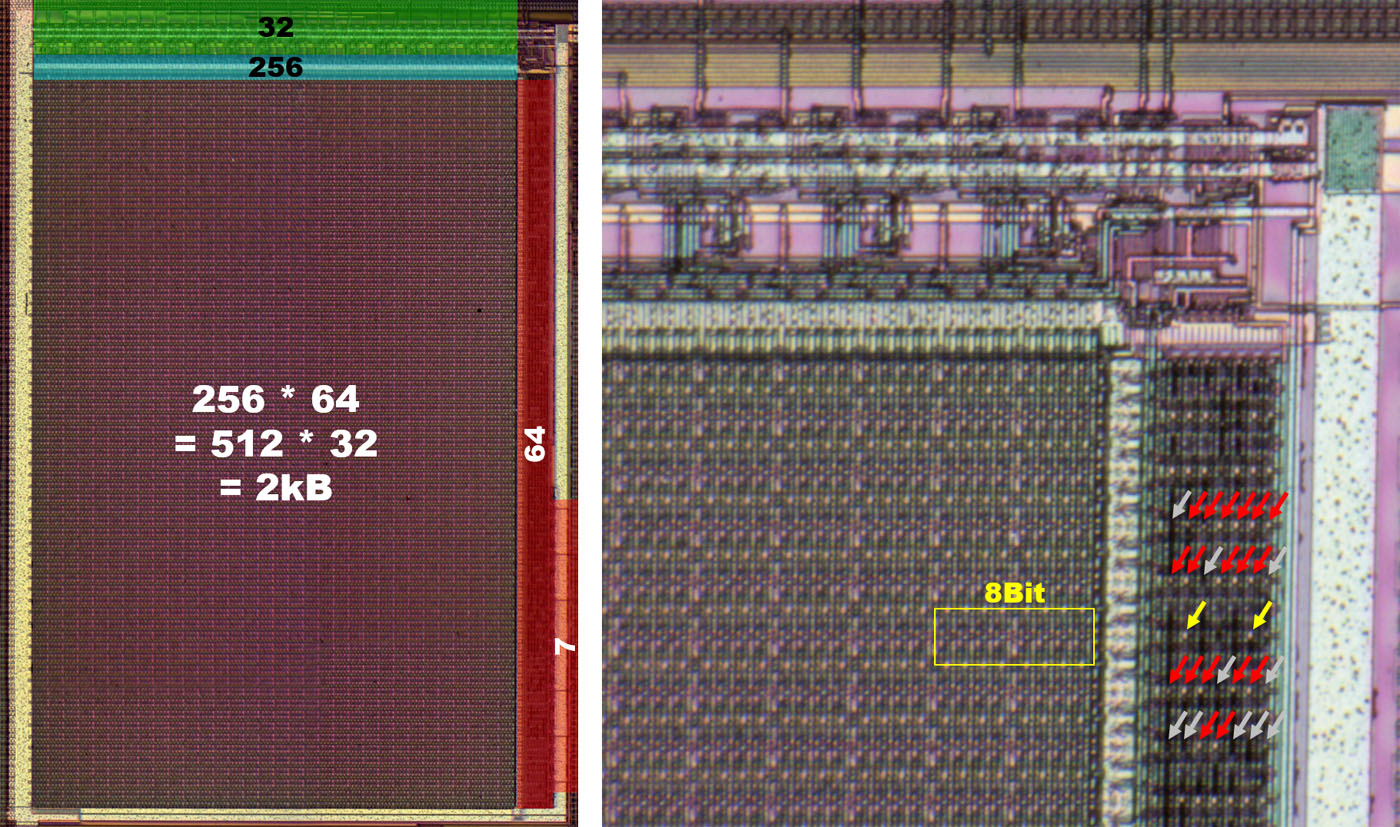

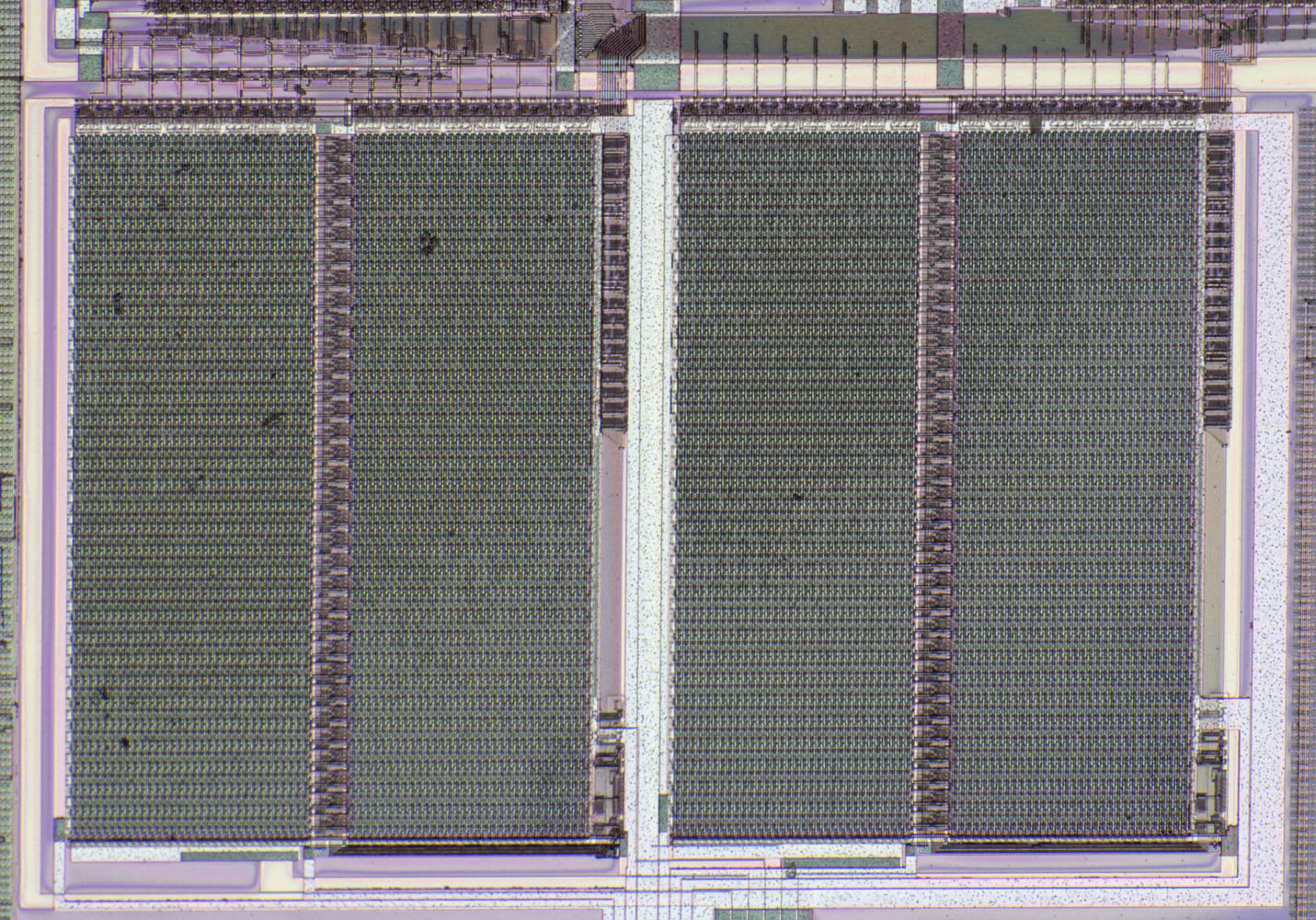

Wie beim SRAM in der oberen linken Ecke des Dies sind auch beim SRAM des DSPs die Strukturen nur noch schwer zu erkennen. Die Speicher scheinen grundsätzlich ähnlich aufgebaut zu sein, was nicht verwunderlich ist.

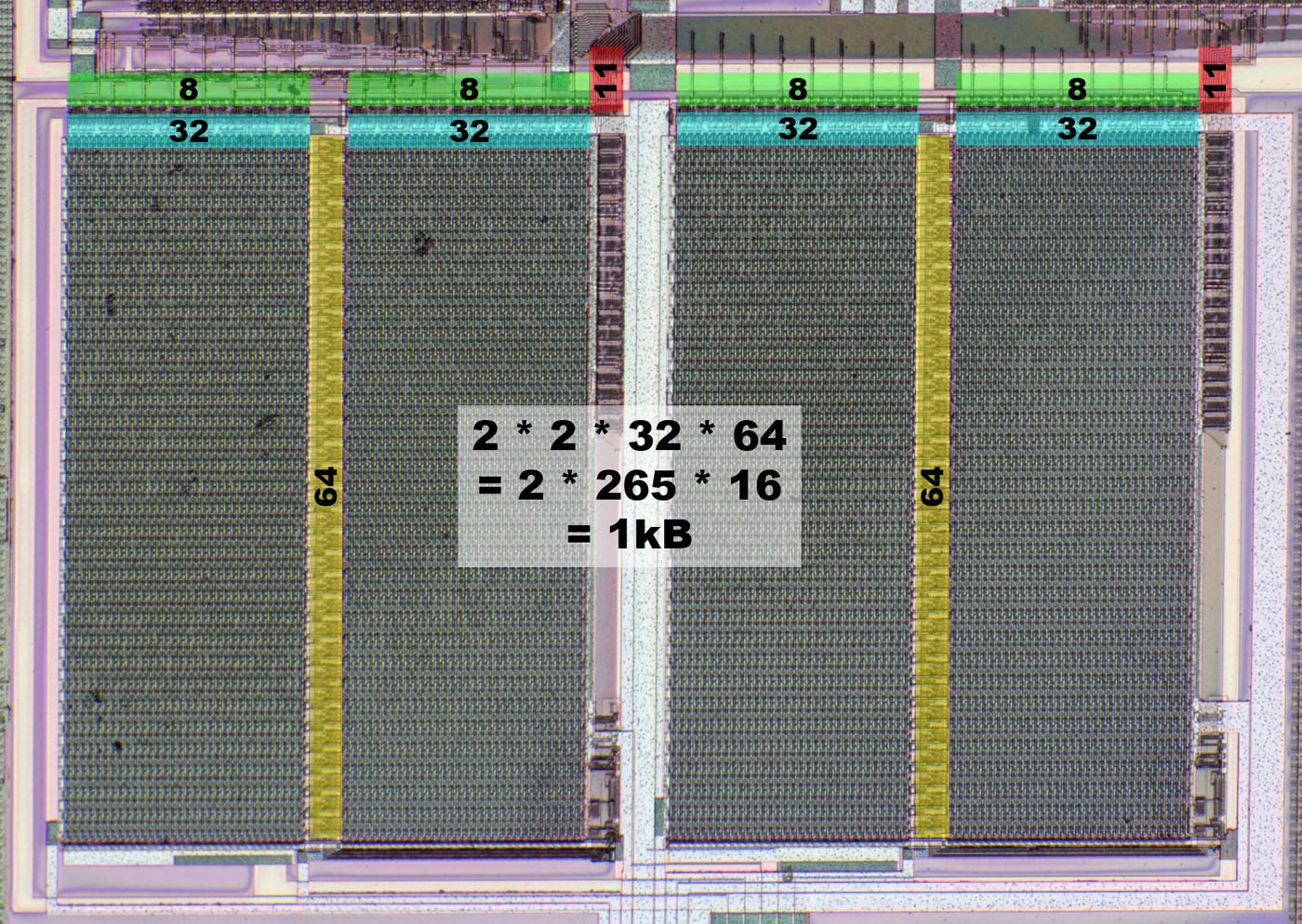

Jeder der zwei SRAM-Blöcke ist in zwei weitere Bereiche aufgeteilt. Zwischen den Bereichen befindet sich die Schaltung der Zeilenauswahl (gelb). Es sind 32 gleichförmige Schaltungen zu erkennen. Mit dem Wissen um die Struktur des 2kB SRAM in der oberen linken Ecke des Dies kann man folgern, dass jede dieser Schaltungen zwei Zeilen ansteuert. Die Steuerleitungen für die Zeilenauswahl verlaufen von der oberen rechten Ecke des Speichers an der rechten Kante entlang nach unten und zur Zeilenauswahl. Jeder der vier Speicherbereiche enthält 32 Spalten (türkis), die auf viermal 8 Datenleitungen zusammengeführt werden (grün). Insgesamt ergibt sich so ein Speicherplatz von 1kB. In der oberen rechten Ecke der beiden Speicherhälften sind 11 Steuerleitungen erkennbar (rot).