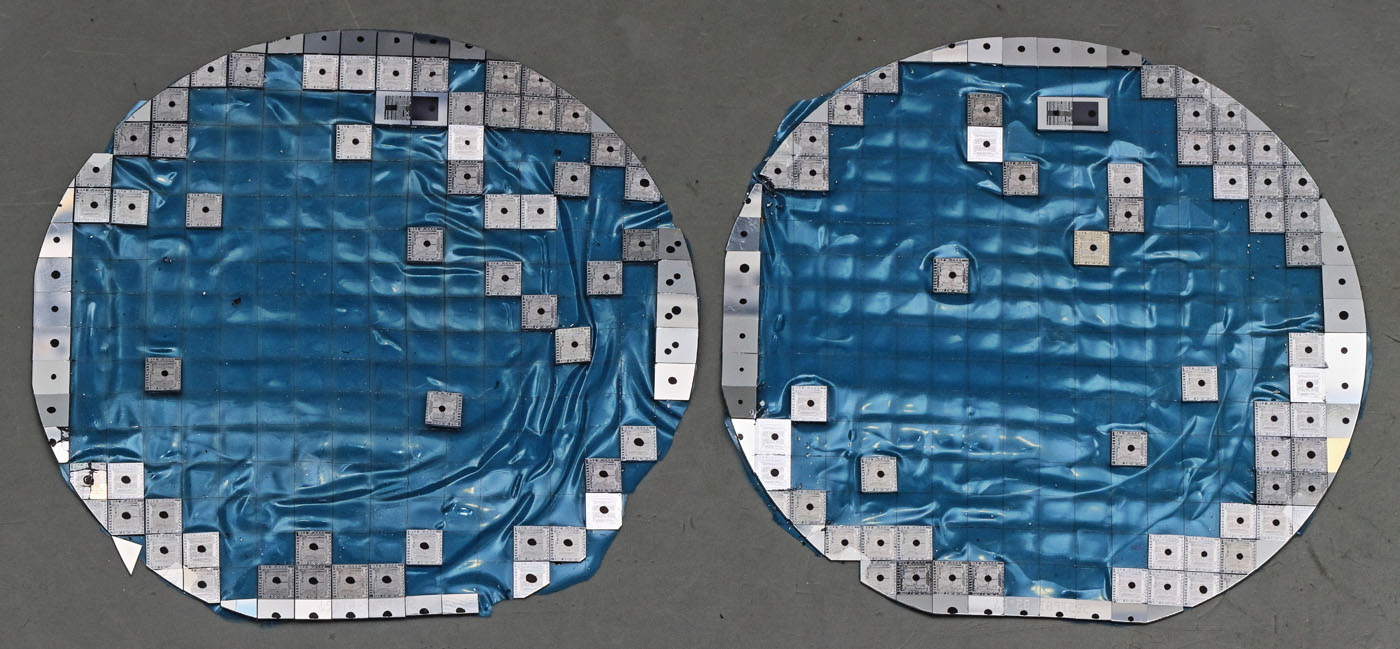

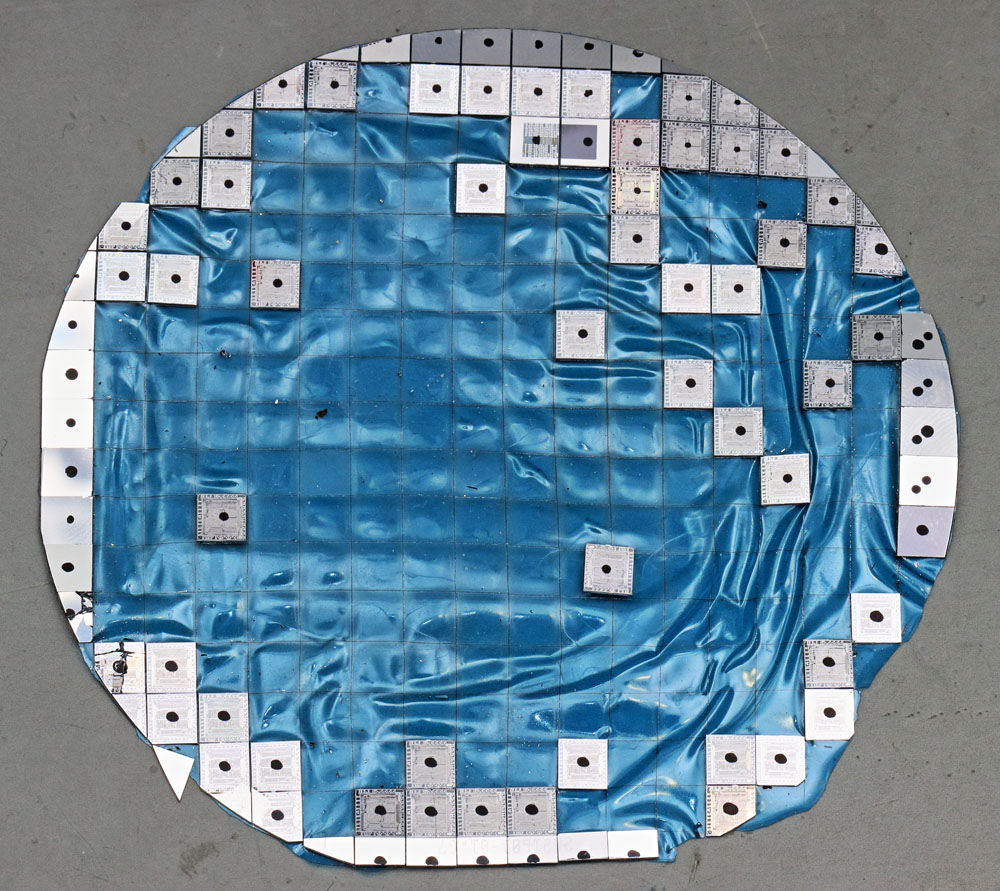

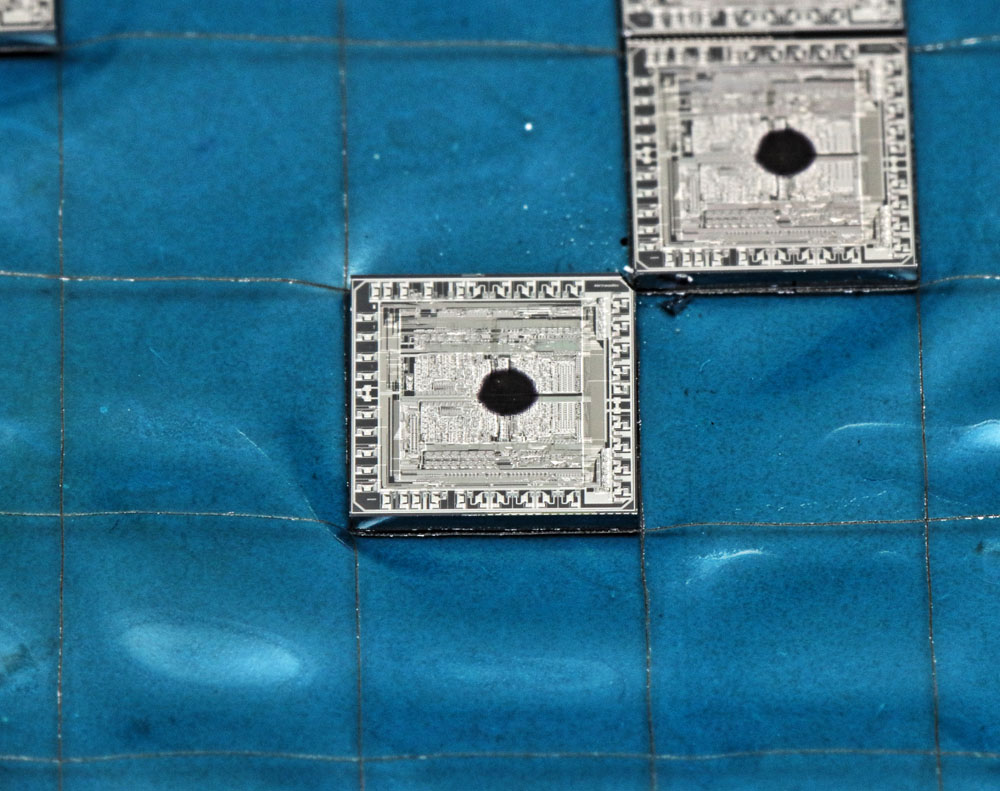

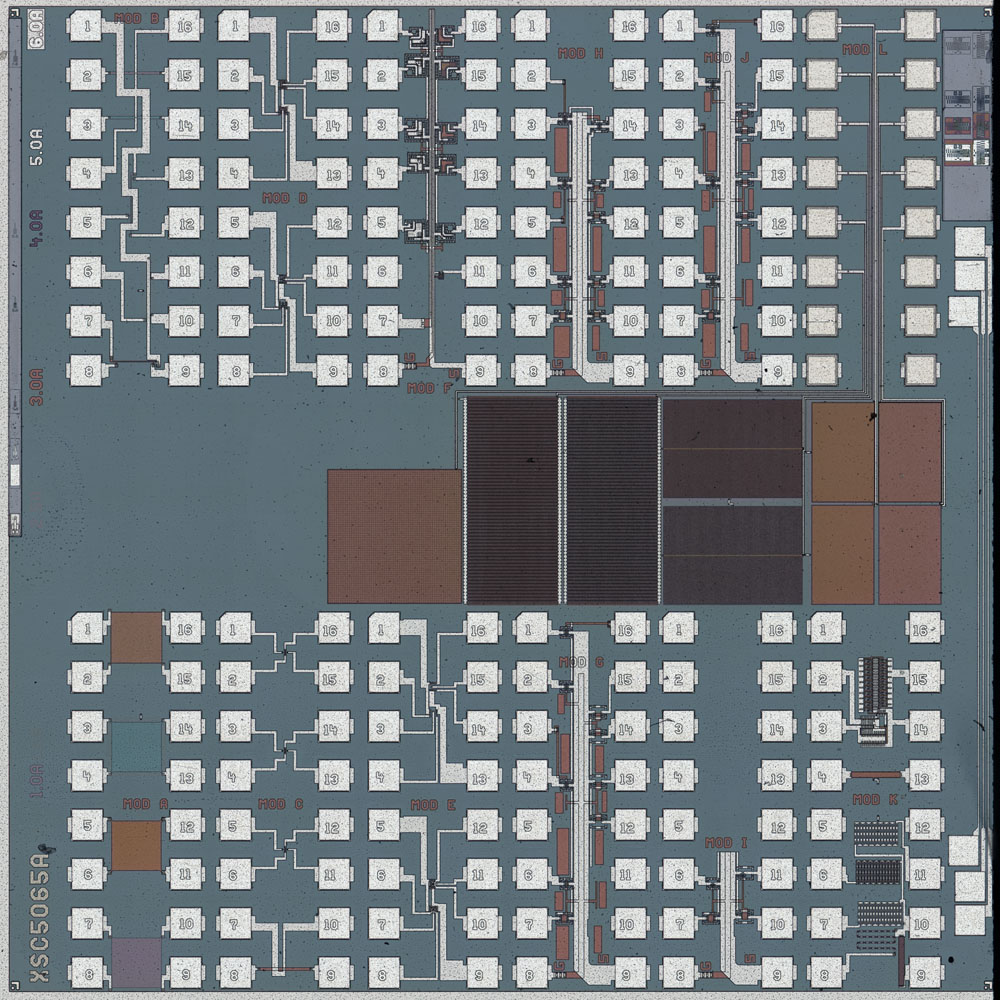

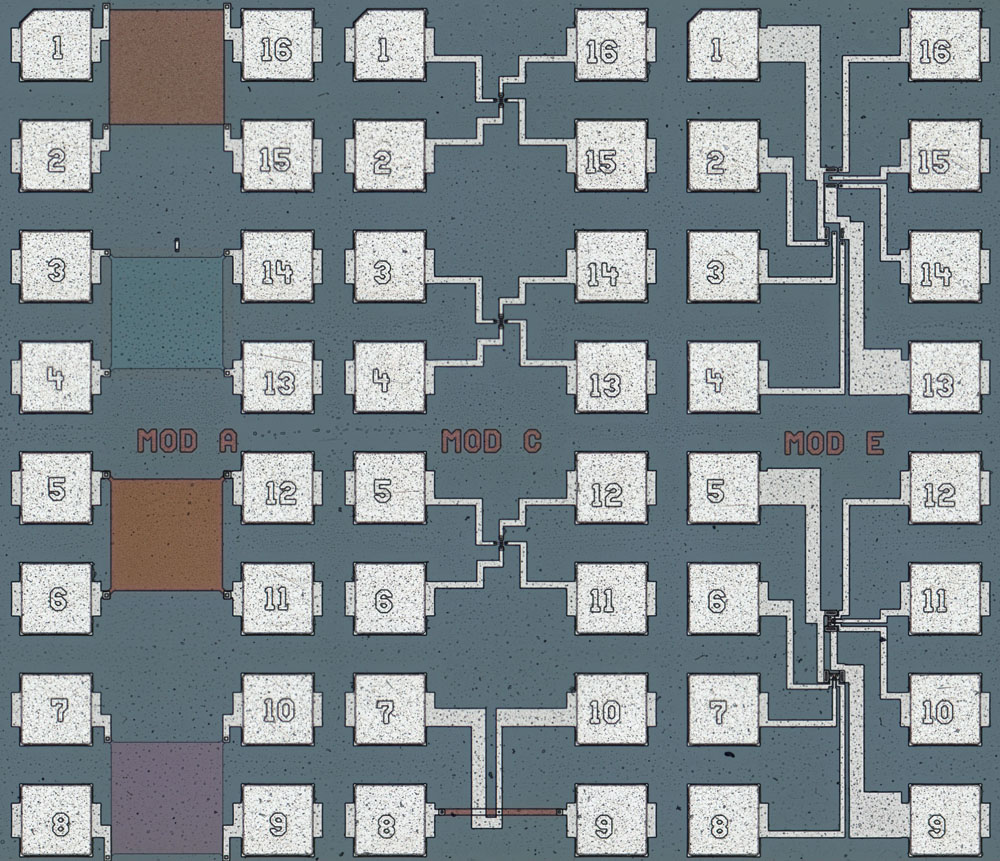

Hier sind die Überreste von zwei 4"-Wafern zu sehen. Bevor man einen Wafer in einzelne Dies schneidet, bringt man ihn auf eine Kunststofffolie auf, die zu diesem Zeitpunkt noch in eine Halterung eingespannt ist. Die Folie hat eine gewisse Klebewirkung und sorgt so dafür, dass die einzelnen Dies beim Sägen an Ort und Stelle bleiben. Nach dem Sägen kann man die Folie etwas auseinanderziehen, wodurch sich der Abstand zwischen den Dies vergrößert und sie beim Entnehmen nicht aneinander stoßen. Teilweise lässt sich die Klebewirkung durch UV-Licht oder Wärmeeinwirkung schwächen, was das Ablösen erleichtert.

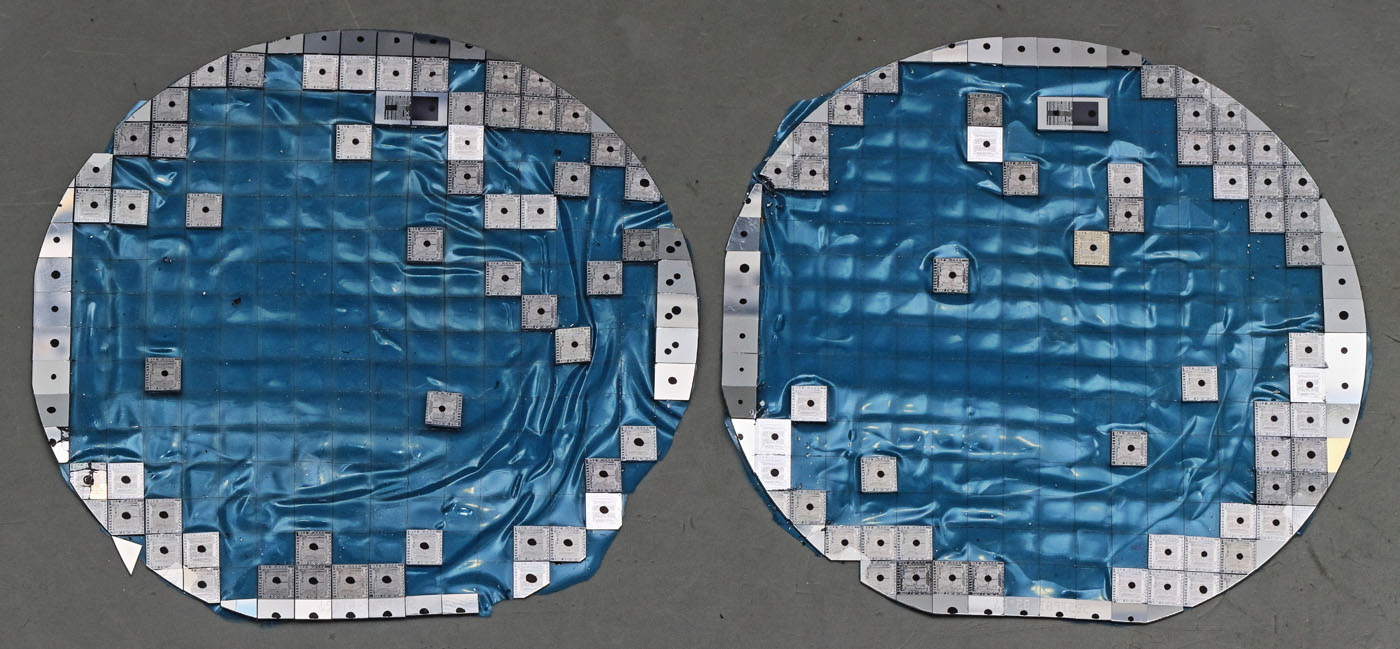

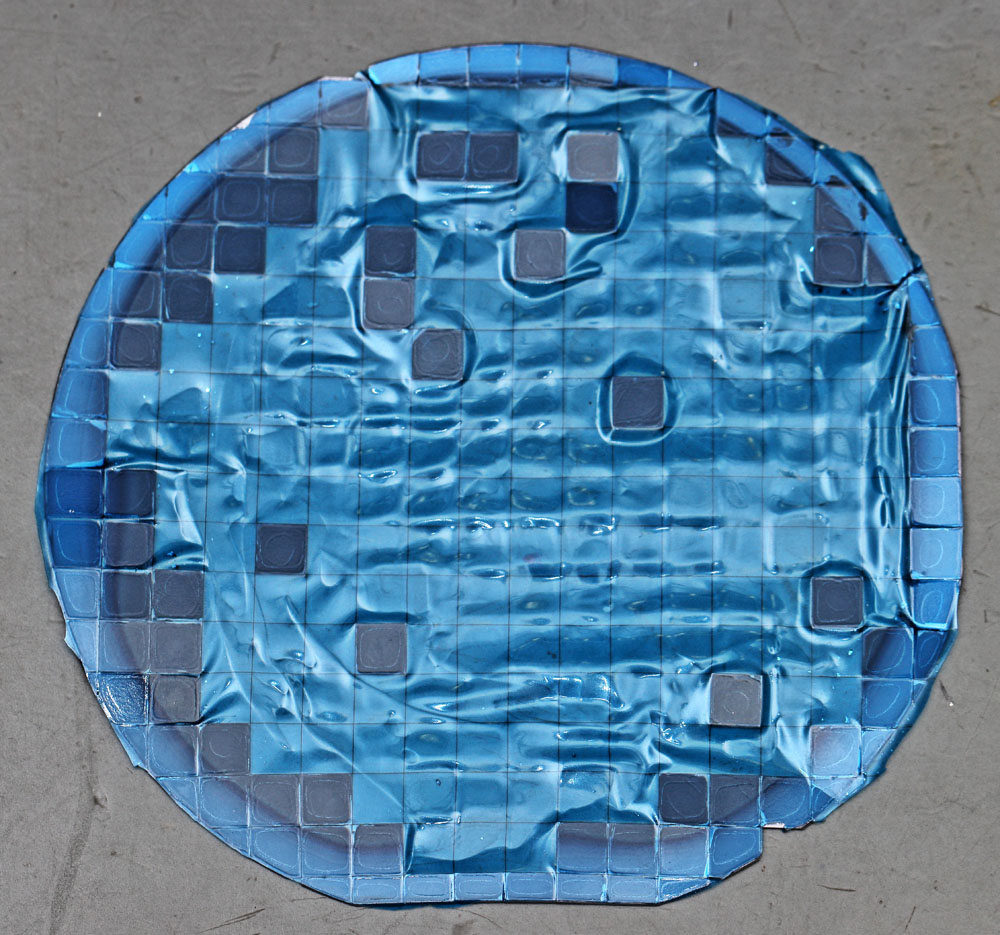

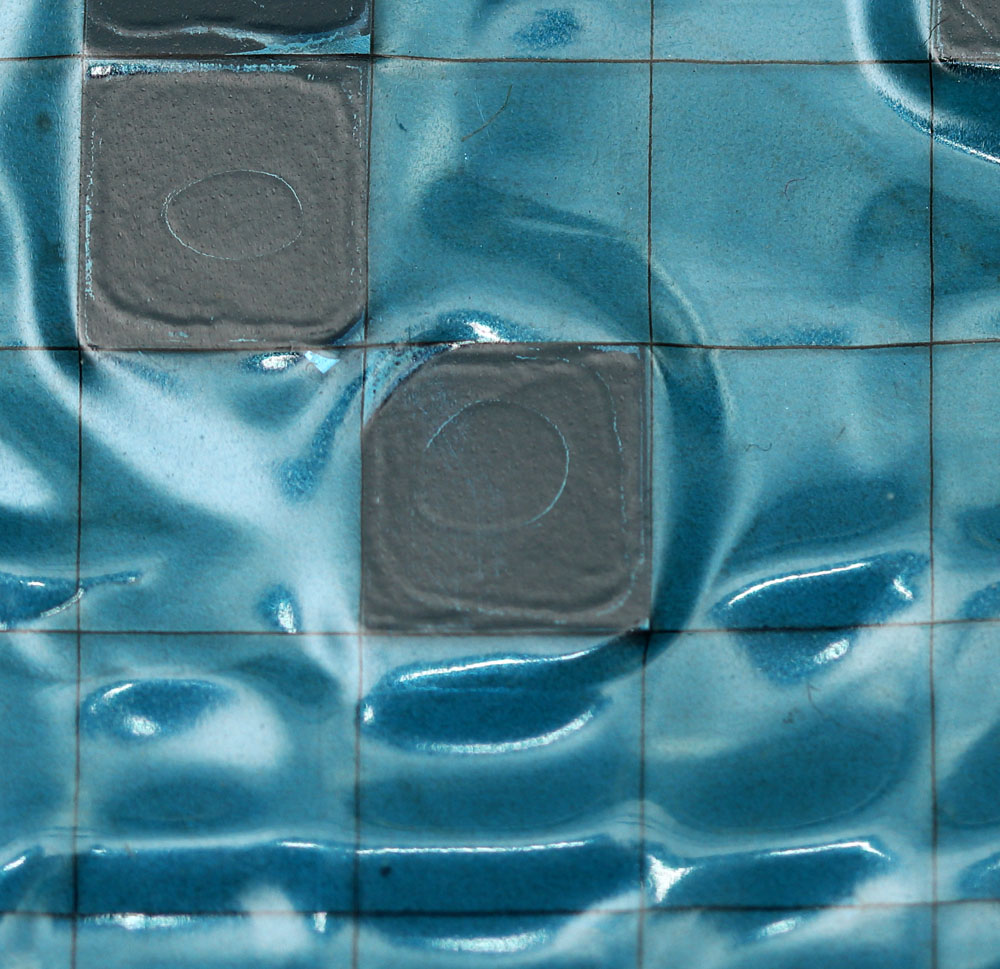

Die Folie hat man aus der Halterung herausgeschnitten. Die nicht nutzbaren Elemente, die bei der Fertigung des Wafers mit einem Punkt markiert wurden, hat man auf der Folie zurückgelassen. Dabei handelt es sich vor allem um geometrisch unvollständige Teile und um Bereiche, auf denen keine Strukturen aufgebracht wurden, außerdem ein Testbereich. Diese Anteile sind prozessbedingt und lassen sich nicht ohne Weiteres optimieren. Die vollständigen Elemente, die auch mit Strukturen versehen wurden, aber trotzdem nicht nutzbar waren, reduzieren dagegen die Ausbeute und müssen daher auf ein Minimum optimiert werden. Hier befindet sich der Ausschuss vor allem im Randbereich, wo wahrscheinlich manche Prozessschritte inhomogener wirken.

Die Kantenlänge eines Dies beträgt 5,5mm. Auf einen Wafer könnte man 216 dieser Chips integrieren. Links waren 179 Elemente nutzbar, rechts waren es 178. Das entspricht einer Ausbeute von 83% beziehungsweise 82%.

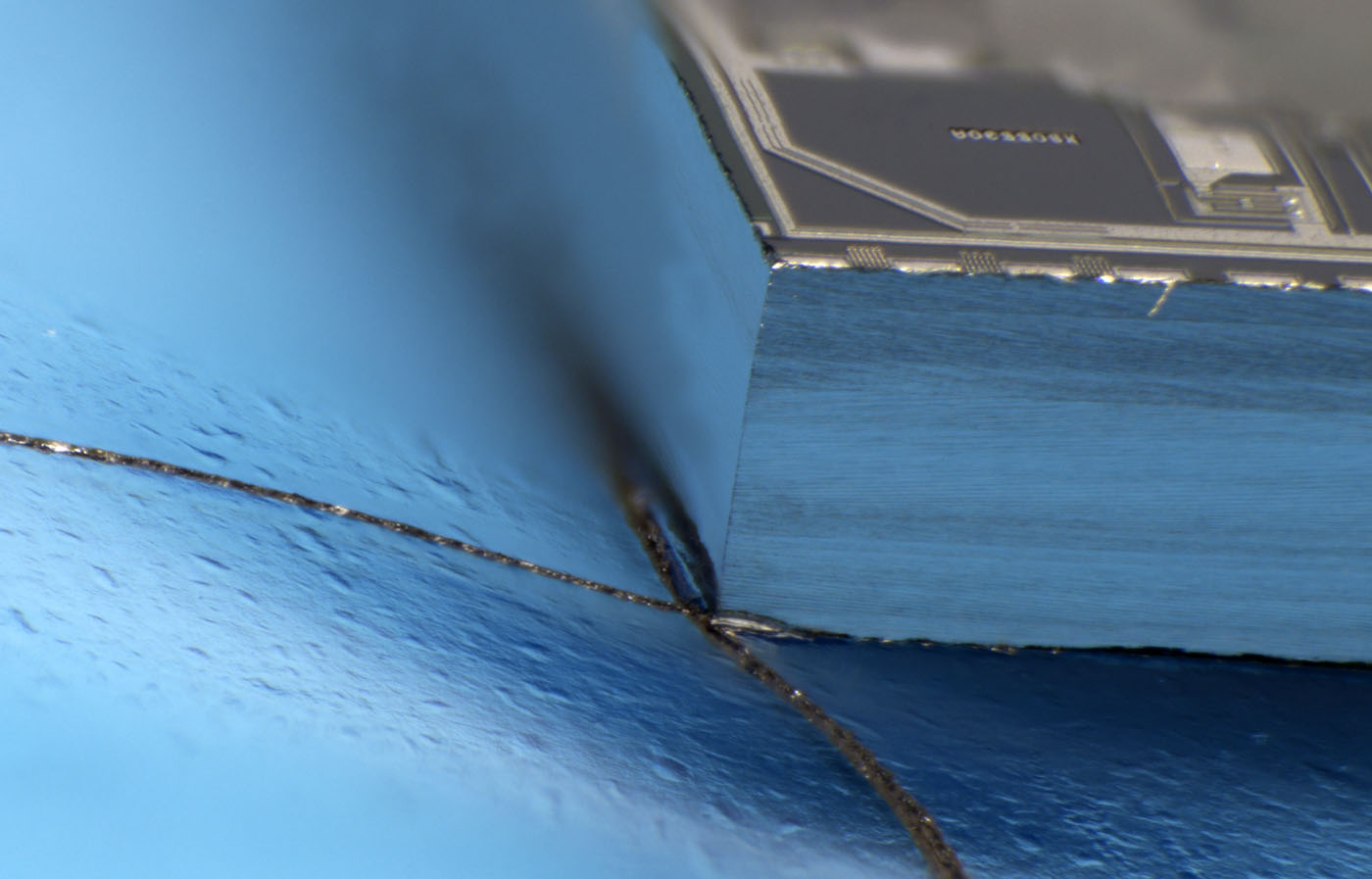

Das Vereinzeln der integrierten Schaltkreise hat auf der Folie dunkle Spuren hinterlassen.

Die seitlichen Kanten der Dies sind sehr glatt. Das lässt vermuten, dass der Wafer in einem Schritt vollständig geschnitten wurde. Dazu gibt es mehrere Alternativen. Man kann den Wafer nur oberflächlich einschneiden und den unteren Bereich brechen, indem man die Folie nach oben bewegt. Teilweise wurde der obere Bereich mit einem dickeren Sägeblatt und der untere Bereich mit einem dünneren Sägeblatt geschnitten. Dieses Vorgehen reduziert die Gefahr von Beschädigungen an den Kanten. Modernere Prozesse nutzen Laser zum Schneiden der Wafer.

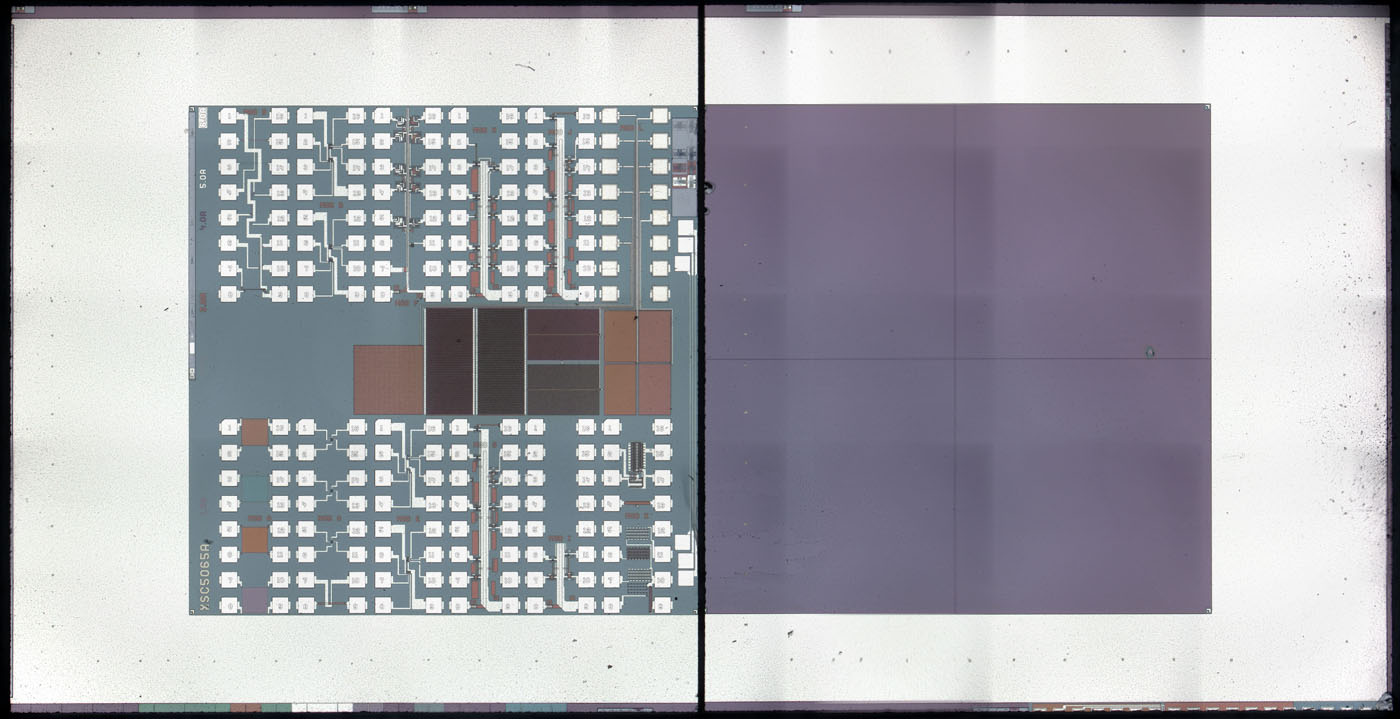

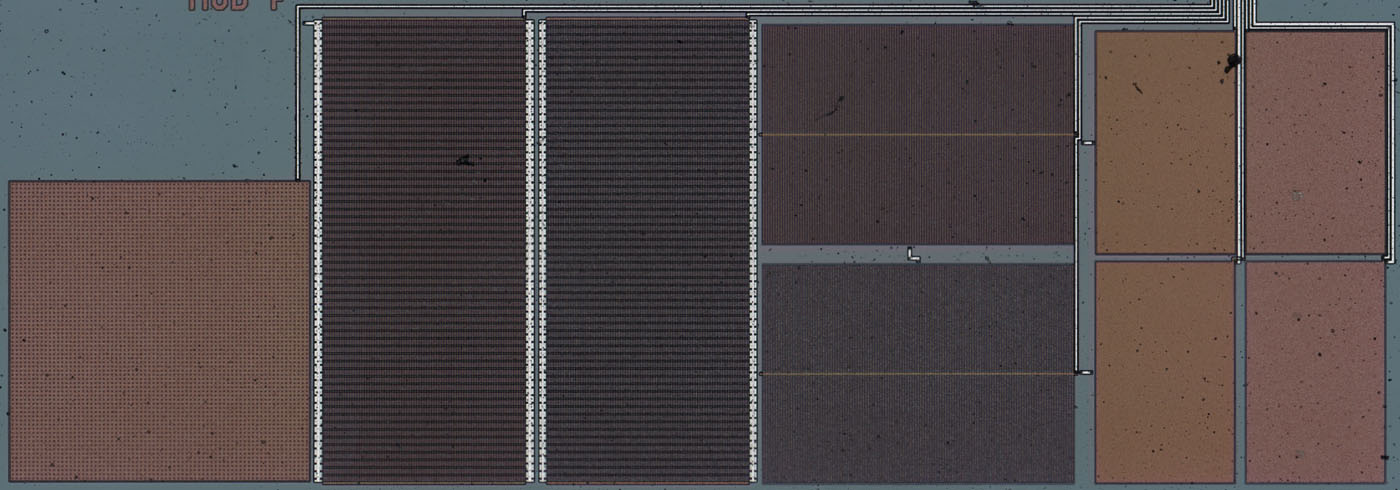

Die Form des Testbereichs ist etwas verwunderlich. Obwohl der Bereich der Teststrukturen problemlos in die Geometrie eines Dies gepasst hätte, hat man zwei Elemente dafür freigehalten. Der rechte Teil ist leer. Anscheinend hat man derart große leere Bereiche zum automatischen Ausrichten der Masken verwendet. Dafür würde sprechen, dass die Fläche nicht wirklich ganz leer ist. Die Farbe zeigt, dass Prozesse vollflächig auf den Bereich eingewirkt haben.

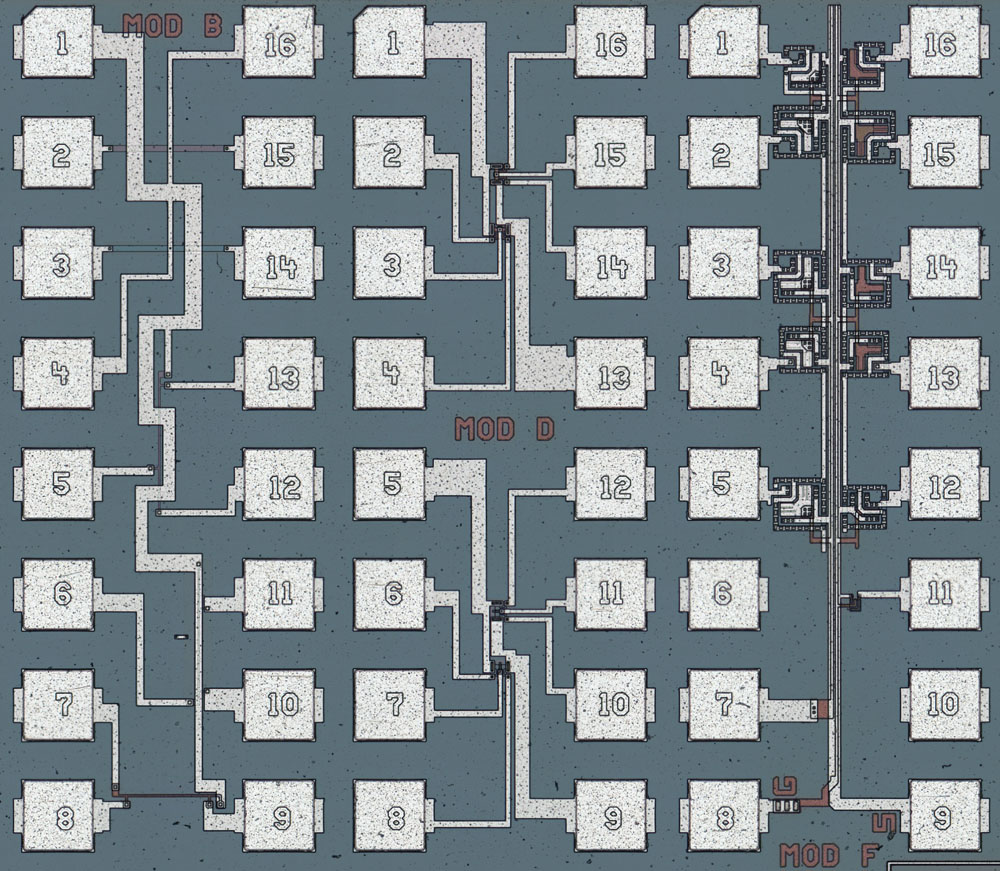

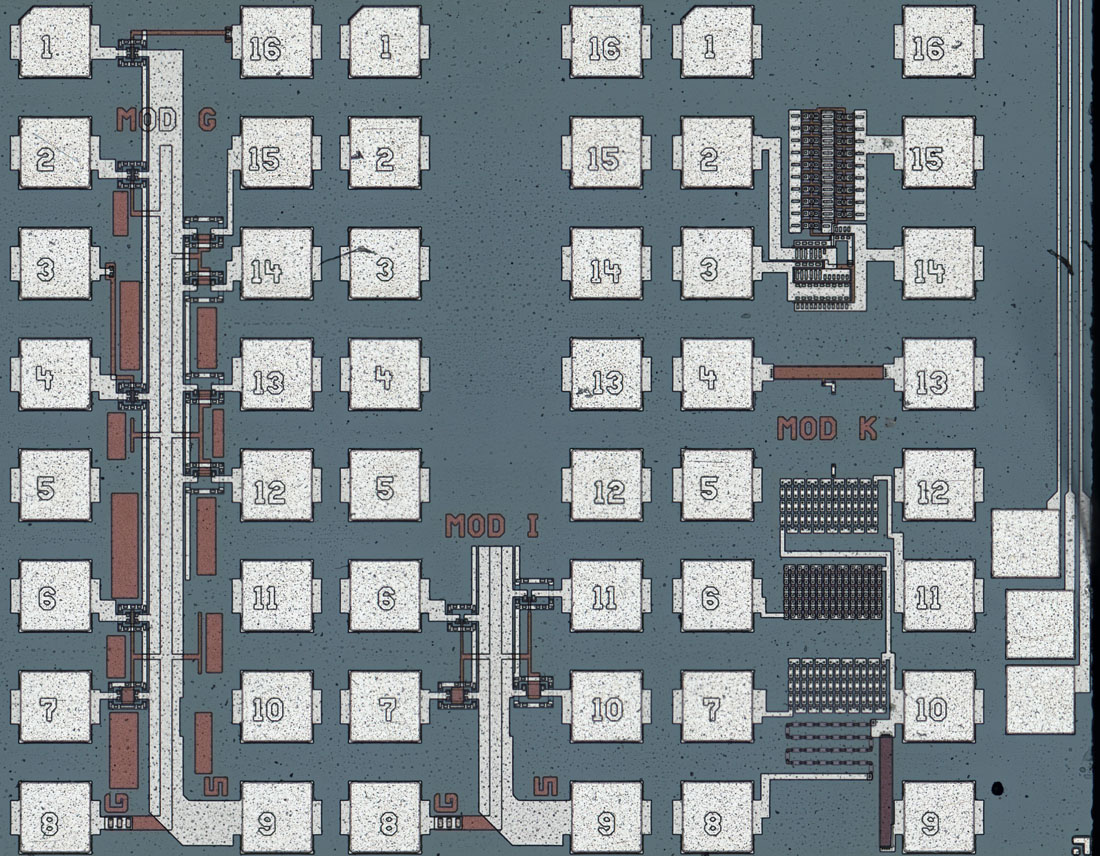

Der Testbereich enthält viele unterschiedliche Strukturen, die elektrisch vermessen werden können. Die Strukturen sind in 12 Gruppen zusammengefasst.

In der Gruppe B befinden sich einige Leitungen und Durchkontaktierungen, die mit Kelvin-Verbindungen angebunden sind, so dass sich die Widerstände dieser Elemente genau bestimmen lassen.

In der Gruppe D kann man vier Transistoren erkennen.

Die Gruppe F enthält mehrere sehr massiv erscheinende Elemente. Es ist gut möglich, dass es sich hier um Schutzstrukturen für Eingänge handelt.

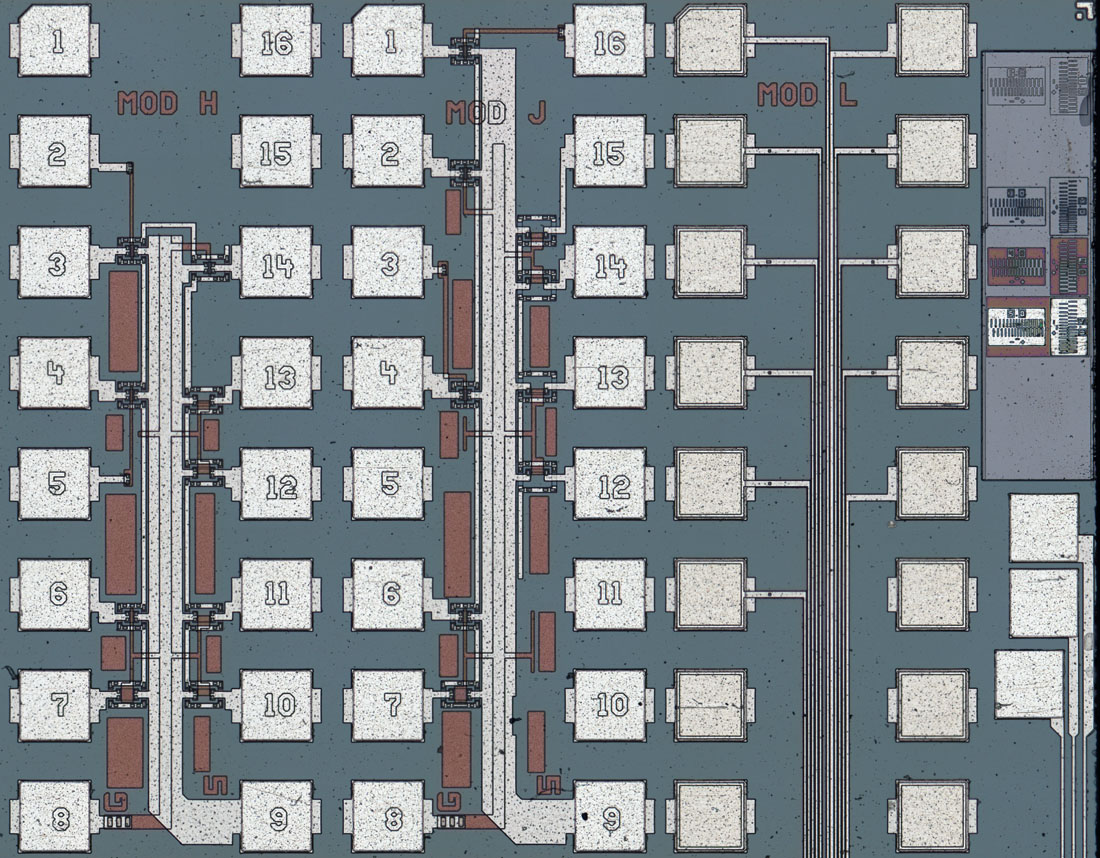

Die Gruppen H und J enthalten Transistoren mit verschiedenen Länge/Breite-Verhältnissen.

Die Potentiale der Gruppe L werden nach unten geführt. Dies zeigt deutlich, dass für alle Teststrukturen der gleiche Nadeladapter verwendet wurde. Es handelt sich immer um zwei Reihen mit jeweils acht Testpunkten im gleichen Abstand. Die einzige Ausnahme stellen die zweimal drei Testpunkte an der rechten Kante dar, die allerdings lediglich drei längere Leitungen der Metalllage kontaktieren.

Im oberen rechten Bereich kann man die Abbildungsleistung von vier Masken bewerten. Interessant ist hierbei, dass man jeweils Teststrukturen im 90°-Winkel zueinander angeordnet hat, um eventuelle Abhängigkeiten von der Ausrichtung sichtbar zu machen.

Die Testpunkte der Gruppe L kontaktieren sehr große Flächen. Die einzelnen Flächen scheinen lediglich mit einer Leitung verbunden zu sein. Das spricht dafür, dass in diesem Bereich Leckströme zum Substrat bestimmt werden. Es könnte auch sein, dass damit die parasitäre Kapazität zum Substrat hin vermessen wurde.

In der Gruppe A sind drei Quadrate in verschiedenen Ebenen dargestellt. Vier Testpunkte kontaktieren jeweils eine Ecke. Mit diesen Strukturen werden die Widerstände der verschiedenen Schichten bestimmt.

Das unterste Element in der Gruppe C enthält lediglich einen Kontakt. Die oberen Elemente könnten demnach auch verschiedene Kontakte sein. Die Strukturen sind zu klein, um sie auflösen zu können. Wahrscheinlich werden auch hier die Eigenschaften, vor allem der Widerstand der Kontakte vermessen.

Im oberen Bereich der Gruppe E kann man unter den Kontakten der Metalllage keine Elemente erkennen. Es könnte sein, dass man darüber die Eigenschaften des Substrats bestimmt hat. Es ist aber auch möglich, dass es sich um einen Vorhalt handelt, um Elemente zu vermessen, die in diesem Prozess nicht vorhanden sind.

Die Gruppen G und I enthalten weitere Transistorvarianten.

In der Gruppe K befinden sich im unteren Bereich Ketten von verschiedenen Durchkontaktierungen, die es ermöglichen die Qualität dieser Durchkontaktierungen zu bestimmen. Im oberen Bereich ist eine komplexere Struktur integriert, die an einen Ringoszillator erinnert. Ringoszillatoren dienen dazu ohne größeren Aufwand die maximale Schaltgeschwindigkeit der integrierten Transistoren bewerten zu können.

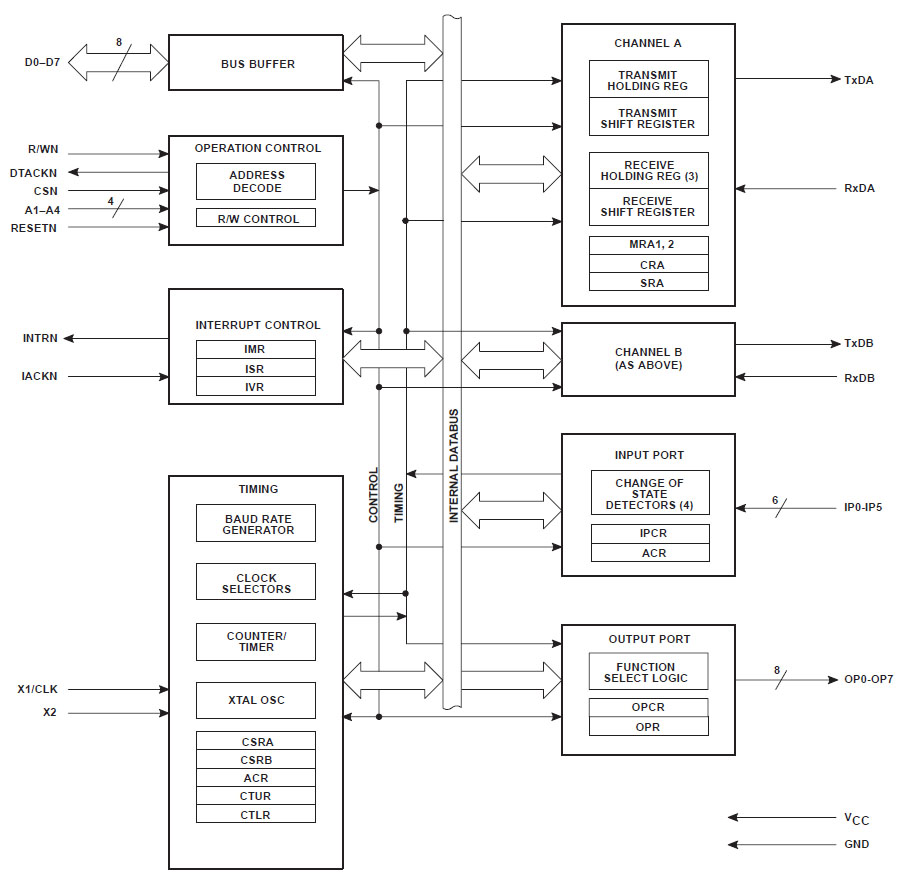

Die Verpackung zeigt, dass der Wafer bei Rood Technology, heute RoodMicrotec, verarbeitet wurde. RoodMicrotec ist ein Dienstleister im Bereich der Halbleiter Lieferkette. Die Typbezeichnung SCC68692 verrät, dass es sich um einen DUART-Transmitter von Signetics handelt. Die Zeichenfolge in der untersten Zeile könnte einen Datecode darstellen. Die Wafer würden dann aus dem Jahr 1998 stammen.

Der Datecode könnte ein Hinweis dafür sein, warum der SCC68692 von Rood Technology verarbeitet wurde, während der Baustein noch bis Ende 2015 direkt von NXP bezogen werden konnte. Im Jahr 1998 wurde das Datenblatt aktualisiert. Als signifikante Änderung wird zwar nur der Entfall eines Keramikgehäuses angegeben, vielleicht gab es aber dennoch Änderungen, die es erforderlich machten Wafer einzulagern und über einen Dienstleister weiter zu verarbeiten.

Der SCC68692 besitzt mit seinen zwei UART-Schnittstellen durchaus eine gewisse Komplexität.

Durch das Handling der Wafer sind mittlerweile einige Kanten der Dies beschädigt. In der Sägestraße erkennt man noch die Überreste weiterer Teststrukturen. Darüber kann man mit etwas mehr Aufwand die Eigenschaften der einzelnen Elemente im jeweiligen Bereich des Wafers bestimmen. Das ist wichtig, wenn man immer an den gleichen Stellen mit erhöhten Ausfallraten zu kämpfen hat.

Die Kantenlänge des Dies beträgt 5,5mm. Dieses Bild ist auch in einer höheren Auflösung verfügbar (123MB). In der unteren linken Ecke zeigt sich, dass das Design von Signetics aus dem Jahr 1988 stammt. Die interne Bezeichnung scheint XSC5530A zu lauten. Es ist deutlich eine Zweiteilung mit einer hohen Symmetrie zu erkennen.