Der Atmel ATtiny10 ist ein Mikrocontroller in einem sehr kleinen SOT-23 Gehäuse. Alternativ wird er auch im UDFN Gehäuse angeboten. Versorgt mit 5V arbeitet der ATtiny10 mit bis zu 12MHz. Er besitzt 1kB Flash und 32B SRAM. Bei 12MHz beträgt die Stromaufnahme 3,7mA. Bei 1,8V und 1MHz reichen 200µA zum Betrieb des Mikrocontrollers.

Der ATtiny10 bietet vier Ausgänge, einen 16Bit-Zähler, zwei PWM Kanäle, einen Komparator und einen 8Bit-ADC, der vier Kanäle bedienen kann.

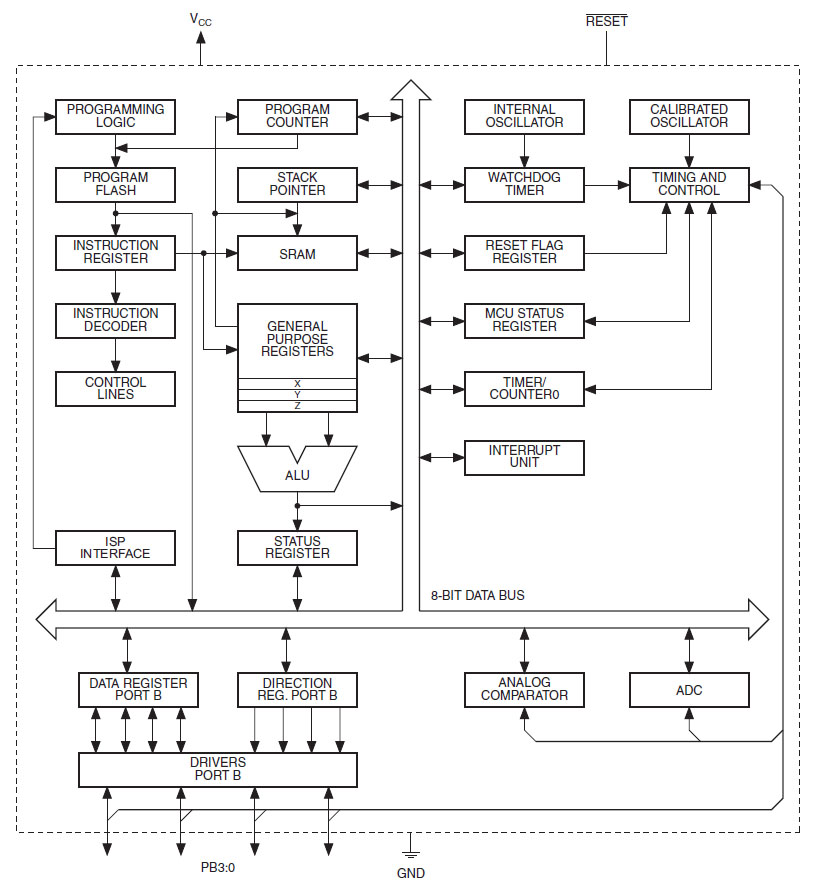

Neben dem ATtiny10 führt das Datenblatt außerdem den ATtiny5 mit nur halb so viel Flash-Speicher und die Varianten ATtiny9 und ATtiny4, denen der ADC fehlt. Anscheinend hat man für alle vier Varianten das gleiche Design verwendet und lediglich gewisse Bereiche deaktiviert. Zeptobars hat das Bild eines ATtiny4 veröffentlicht, das zeigt, dass dieser Mikrocontroller genauso aufgebaut ist wie der ATtiny10: https://zeptobars.com/en/read/atmel-tiny4-attiny4-microcontroller

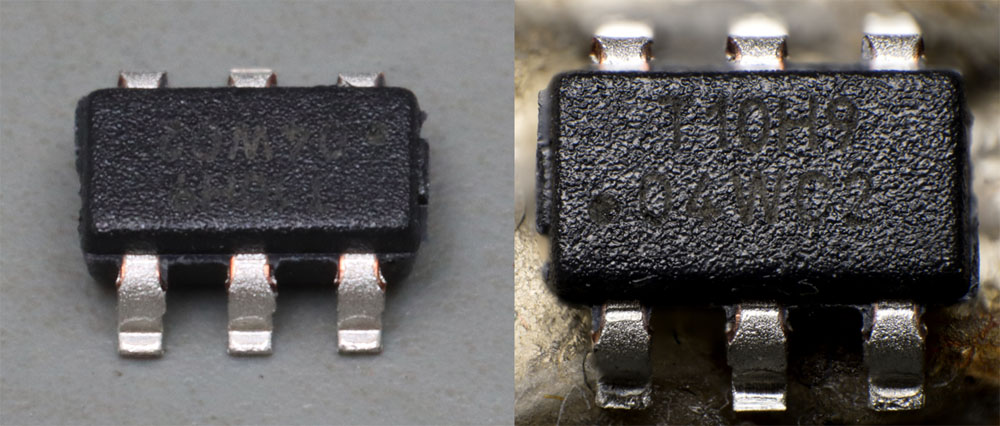

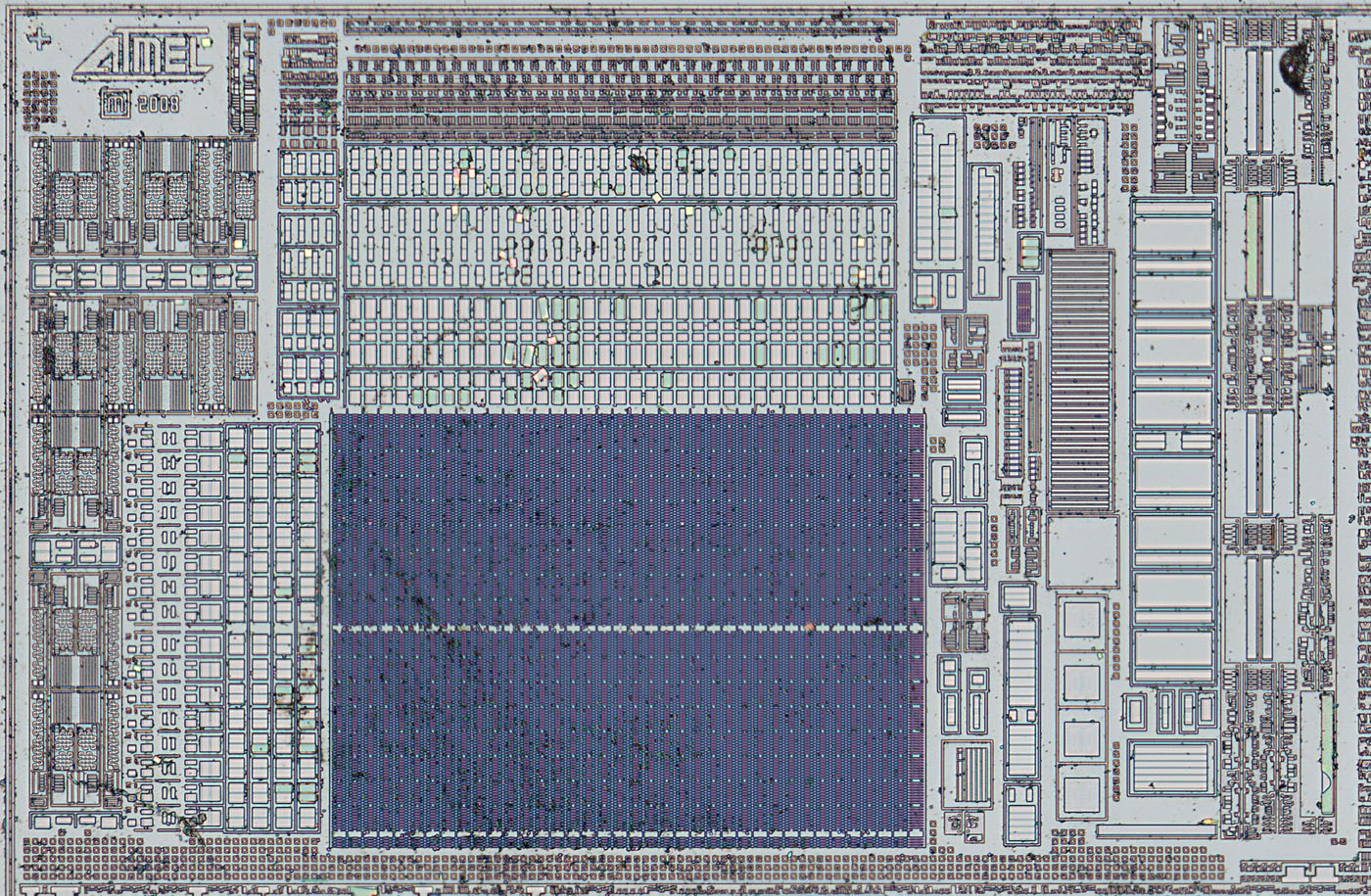

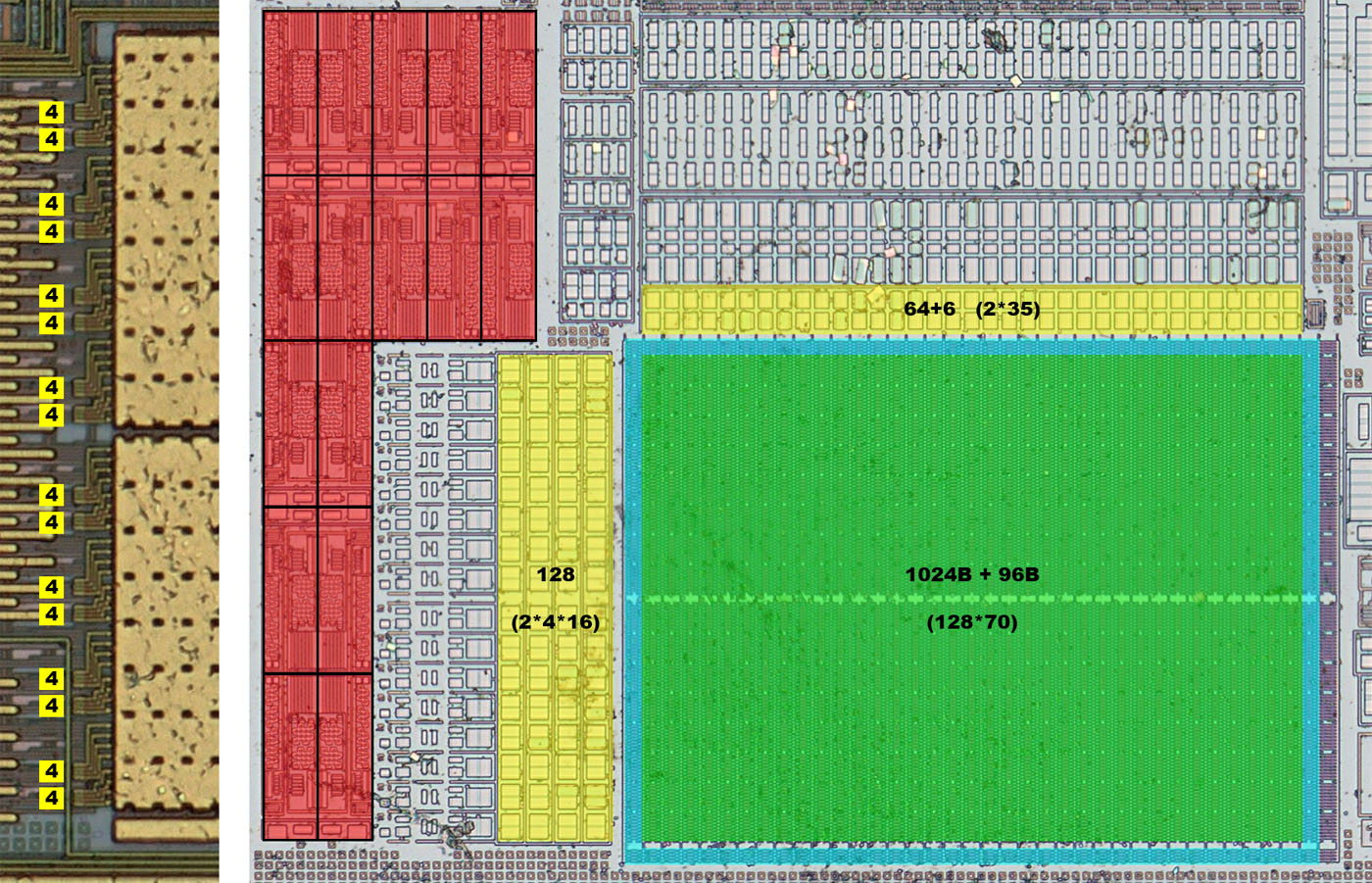

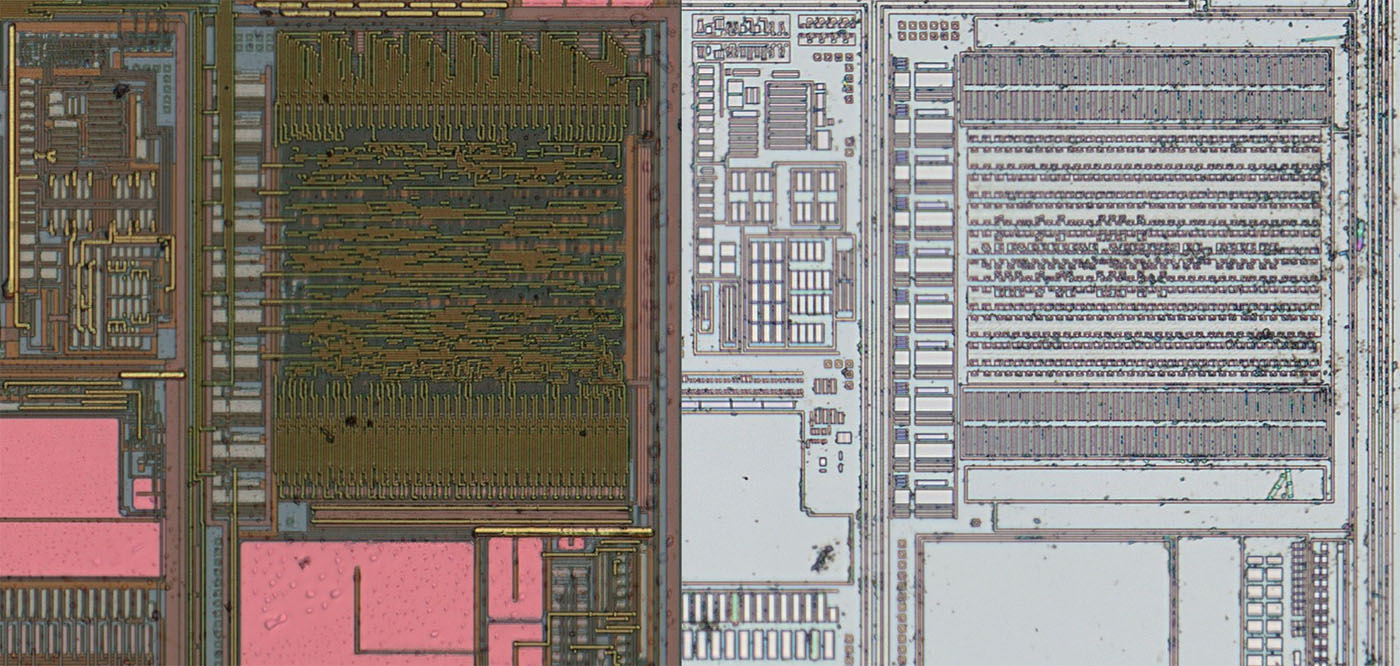

Die Abmessungen des Dies betragen 1,38mm x 0,93mm. In der oberen linken Ecke befindet sich der Flashspeicher. Eine massive Fläche der obersten Metalllage deckt den Speicherbereich selbst ab. Mit seiner Umgebungsbeschaltung nimmt der Speicher einen großen Teil des Dies ein. Der Streifen in der oberen rechten Ecke ist der SRAM. An der rechten Kante sind analoge Schaltungsteile und Funktionsblöcke wie ADC, Komparator und Zähler integriert. Was sich in dem abgegrenzten Bereich an der unteren Kante befindet bleibt unklar. Es könnte sein, dass dort die Oszillatoren platziert wurde.

Dieses Bild ist auch in höherer Auflösung verfügbar: 18MB

Das Design stammt offensichtlich aus dem Jahr 2008.

AT 35470 ist wahrscheinlich die interne Projektbezeichnung. Der ATtiny4, den Zeptobars dokumentiert hat, trägt die gleiche Bezeichnung.

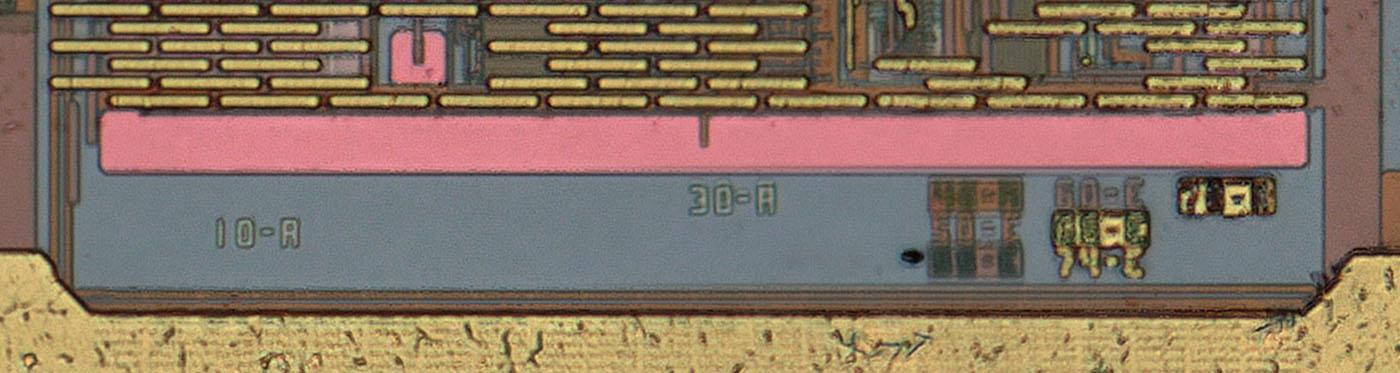

An der unteren Kante sind einige Masken abgebildet. Es scheinen vier Metalllagen zum Einsatz gekommen zu sein. Der Buchstabe am Ende jeder Maske ist wahrscheinlich die Revision. Das würde mit den Revisionen übereinstimmen, die das Datenblatt aufführt. Die Revision E wurde dort im Februar 2010 aufgenommen.

Offensichtlich hat man hier lediglich die BEOL-Masken dargestellt. Bei der Herstellung integrierter Schaltkreise durchfläuft der Wafer zuerst das FEOL, das Front-End-Of-Line. Dort werden die aktiven Strukturen im Silizium erzeugt. Auf das FEOL folgt das BEOL, das Back-End-Of-Line, wo die Metalllagen aufgebracht werden.

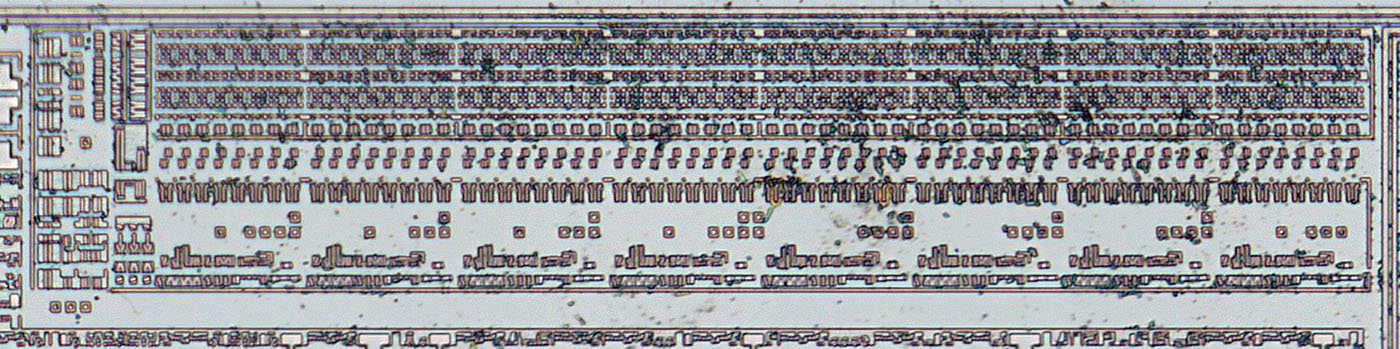

Nach vier Stunden in einer Glasätzpaste hat die daraus freigesetzte Flusssäure jegliches Siliziumoxid aufgelöst. Metalle, Polysilizium und das Substrat werden nur wenig angegriffen. Über die lange Einwirkzeit lösen sich aber neben der obersten Passivierungsschicht auch die Siliziumoxidschichten unter den folgenden Lagen auf. Das führt dazu, dass sich alle Schichten ablösen und man letztlich einen ungestörten Blick auf das Substrat werfen kann. Die Strukturierung der aktiven Bereiche hat auf dem Substrat Höhenunterschiede hinterlassen, die es oft erleichtern die integrierten Funktionsblöcke zu identifizieren.

Dieses Bild ist auch in höherer Auflösung verfügbar: 21MB

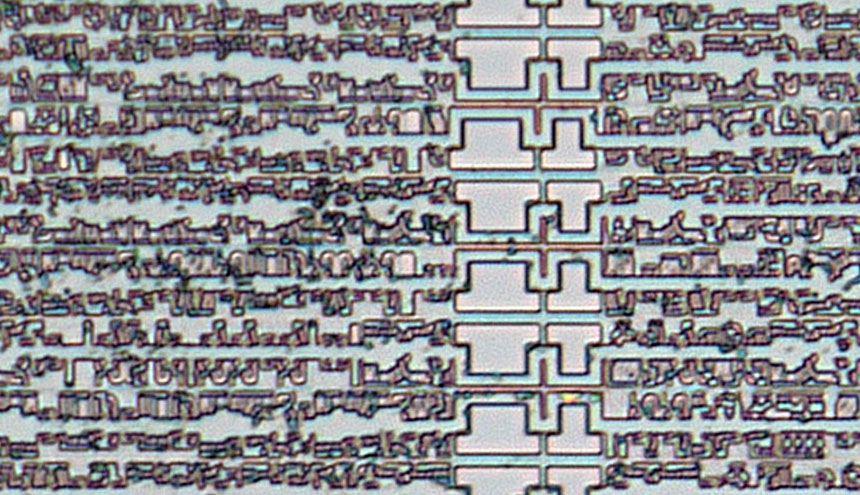

Der Aufbau des Flash-Speichers wird ohne Metalllage sehr viel deutlicher. Die Speicherzellen selbst sind die dichtesten Strukturen auf dem Die. Links und oberhalb der Fläche sind die sich wiederholenden Elemente der Zeilen- und Spaltenauswahl zu erkennen. Die größeren Strukturen rechts sind wahrscheinlich Hilfsschaltungen. Darunter könnte sich zum Beispiel eine Ladungspumpe befinden, die man üblicherweise zum Beschreiben von Flash- oder EEPROM-Zellen benötigt.

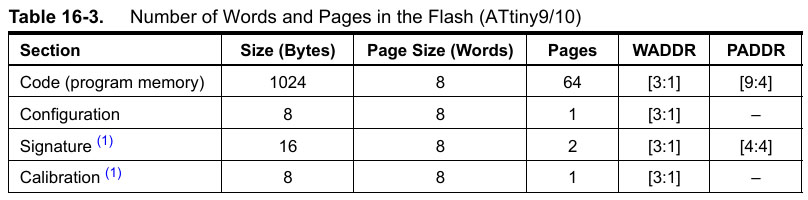

Die Speicherarchitektur gibt das Datenblatt mit 16x512 an. Links des Speichers kann man 16 größere, gleich aufgebaute Schaltungen erkennen (rot). Höchstwahrscheinlich erfolgt dort eine Signalaufbereitung zum Auslesen oder Beschreiben des Speichers. An der linken Kante des Speichers sind 4x16 gleiche Rechtecke zu erkennen (gelb). Bei genauerer Betrachtung sind die Rechtecke zweigeteilt. In der obersten Metalllage sind nur 16x4 Leitungen zu erkennen (Bild links). Darunter kann man aber weitere horizontale Leitungen erahnen. Innerhalb der Speicherfläche befinden sich 2x8 Blöcke mit jeweils 8 Elemente. Man kann folglich davon ausgehen, dass der Speicher 128 Zeilen besitzt. An der oberen Kante finden sich 2x35 Rechtecke, wodurch man auf 70 Spalten schließen kann. Für die nutzbaren 1024B würden 64 Spalten ausreichen. An allen Kanten des Speichers befinden sich Dummystrukturen (türkis). Die zusätzlichen 6 Spalten, insgesamt 96B, sind folglich funktionale Speicherzellen.

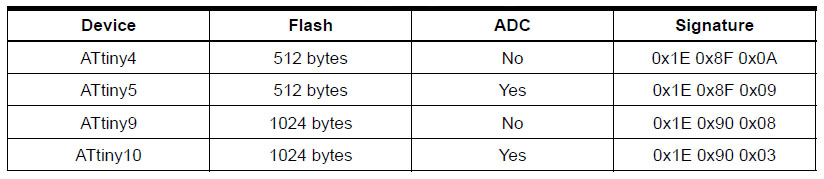

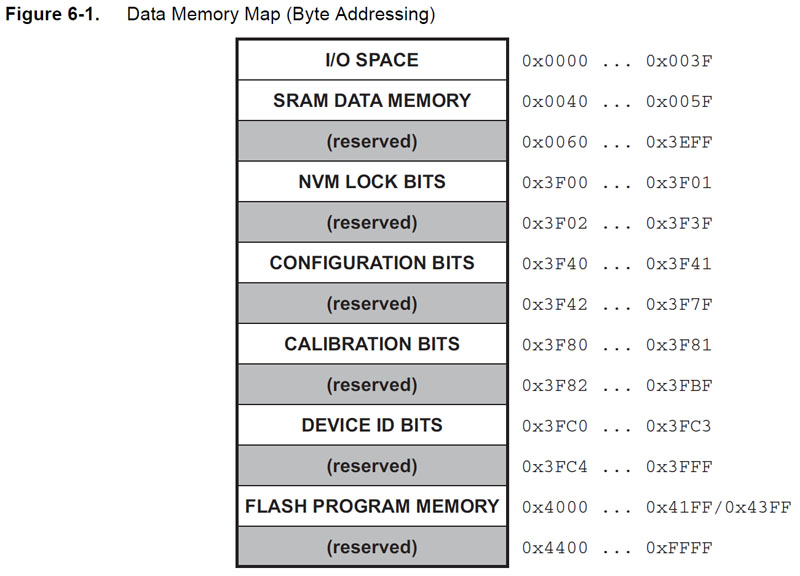

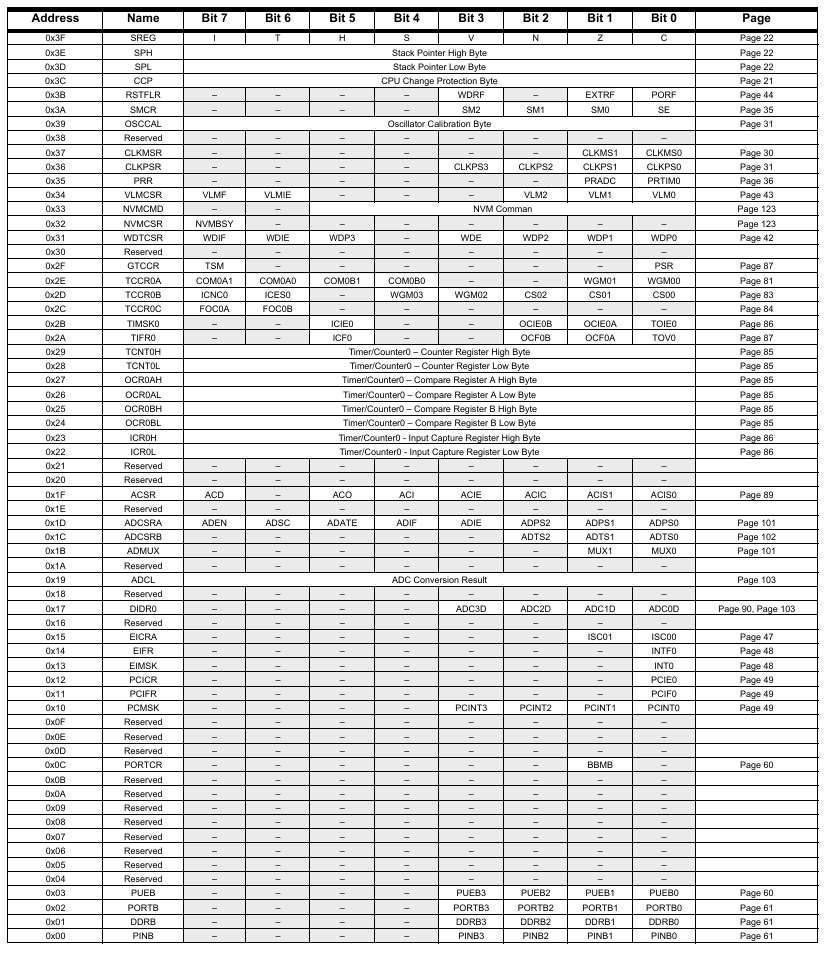

Ein Blick ins Datenblatt zeigt wie zumindest einige der zusätzlichen Speicherzellen zu erklären sind. Die Bereiche I/O Space und SRAM finden sich an anderen Stellen. Die darunter folgenden Speicherzellen befinden sich aber alle innerhalb des einen Flash-Speichers. Neben den Lock Bits befinden sich im Flash-Speicher noch die Configuration Bits, die Calibration Bits und die Device ID. Obwohl diese Funktionen nur wenige Speicherzellen benötigen, belegen sie verhältnismäßig große Bereiche. Vermutlich erleichtert das eine gewisse funktionale Abtrennung.

Die Platzierung der Lock Bits innerhalb des großen Flash-Speichers wird als besonders sicher beworben. Befinden sich die Lock Bits an einer anderen Stelle des Dies, so kann man versuchen diese selektiv mit UV-Licht löschen, um danach den Speicher auszulesen. Innerhalb des Programmspeichers ist es deutlich schwerer die Lock Bits zu beeinflussen ohne das Programm selbst zu löschen. Das gilt besonders dann, wenn die Speicherzellen von einer Metallschicht verdeckt sind. Solange man nicht die Möglichkeit hat ein Fenster in die Metallschicht zu schneiden, muss man die notwendige Lichtmenge über Reflektionen in die relevanten Speicherzellen lenken. In direkter Nähe des Programmspeichers ist das noch schwieriger.

Ohne Metalllage kann man nun auch den Aufbau des SRAM genauer erkennen.

Der Logikbereich erscheint chaotisch. Je nach gewünschter Funktion wurden hier Formen erzeugt, die mit der darüber liegenden Polysiliziumschicht an den notwendigen Stellen Transistoren erzeugen.

Im rechten Bereich des Dies befinden sich unterschiedliche Strukturen. Darin integriert sind analoge Schaltungsteile und Funktionen wie der Zähler. Außergewöhnlich erscheint in diesem Zusammenhang eine große und überraschend gleichmäßige Struktur, die an einen Speicher erinnert. Für einen Speicher sind die unregelmäßigen Kontakte in der Mitte des Bereichs aber untypisch.

Nach dem Abtragen der Metall- und Polysiliziumlagen zeigt sich darunter ebenfalls eine gleichmäßige Struktur mit Abweichungen. Bei genauerer Betrachtung zeigt sich, dass es sich um 8 Zeilen handelt, von oben und von unten führen jeweils 64 Leitungen in die Strukturen.

Man kann davon ausgehen, dass es sich hier um die Register handelt, die Funktionen wie Analog-Digital-Wandler, Komparatoren, Zähler und ähnliches konfigurieren. Der Registerblock besitzt 64x8 Speicherzellen, was zur optischen Erscheinung des obigen Blocks passt. Es ist absolut sinnvoll die Konfigurationsregister in dem Bereich zu platzieren, in dem sich auch die zu konfigurierenden Funktionen befinden. Wahrscheinlich sorgt die teilweise exklusive Kontaktierung innerhalb der Register dafür, dass gewisse Blöcke direkt und damit sehr schnell ausgelesen oder beschrieben werden können. Es könnte auch sein, dass in ungenutzten Bereichen zusätzliche Logikschaltungen integriert wurden.