Die ESP32-Familie wird von der chinesischen Firma Espressif Systems produziert. Die Bausteine vereinen einen Mikrocontroller mit einem oder mehreren Funkmodulen, üblicherweise WiFi und Bluetooth. Die ESP32 haben sich stark im Bereich Internet of Things verbreitet. Es existieren verschiedene Varianten des ESP32. Der ESP32-S3 enthält einen Dual-Core Prozessor, einen Xtensa LX7 von Cadence, der mit 240MHz arbeitet. Im Prozessor integriert sind 384kB ROM und 512kB SRAM. Ein Ultra Low Power Coprozessor ermöglicht eine sehr geringe Stromaufnahme im Standby.

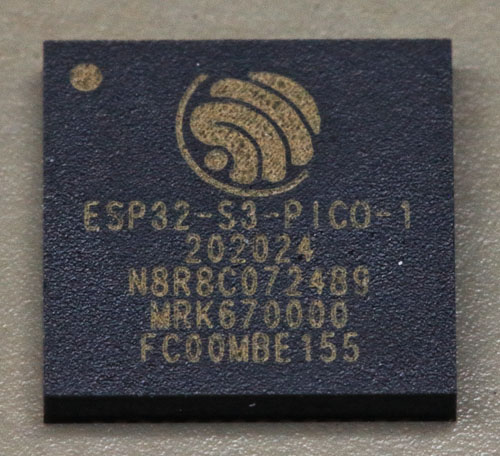

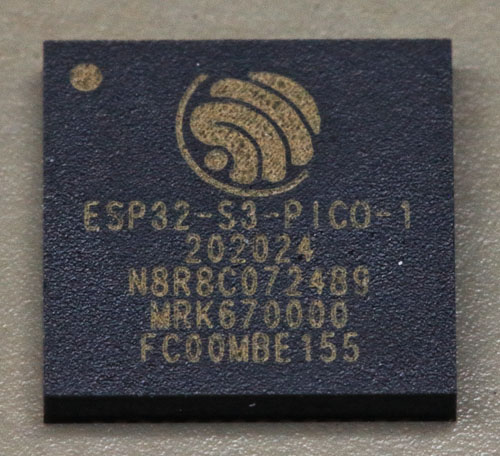

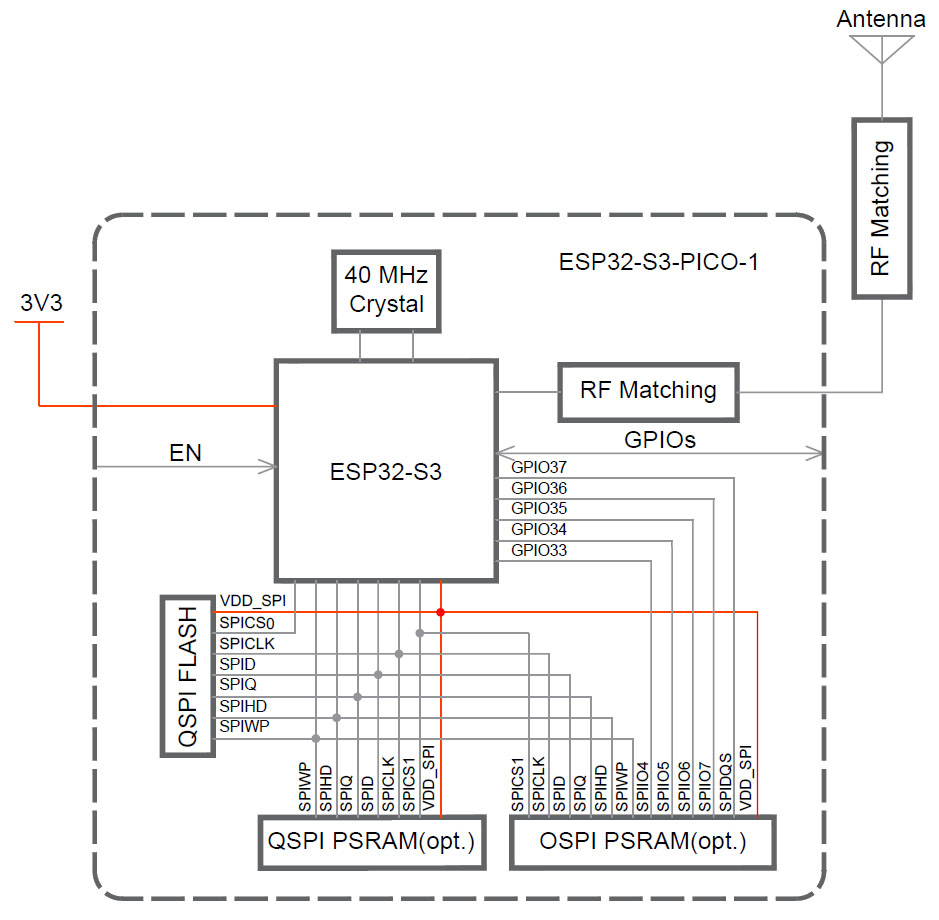

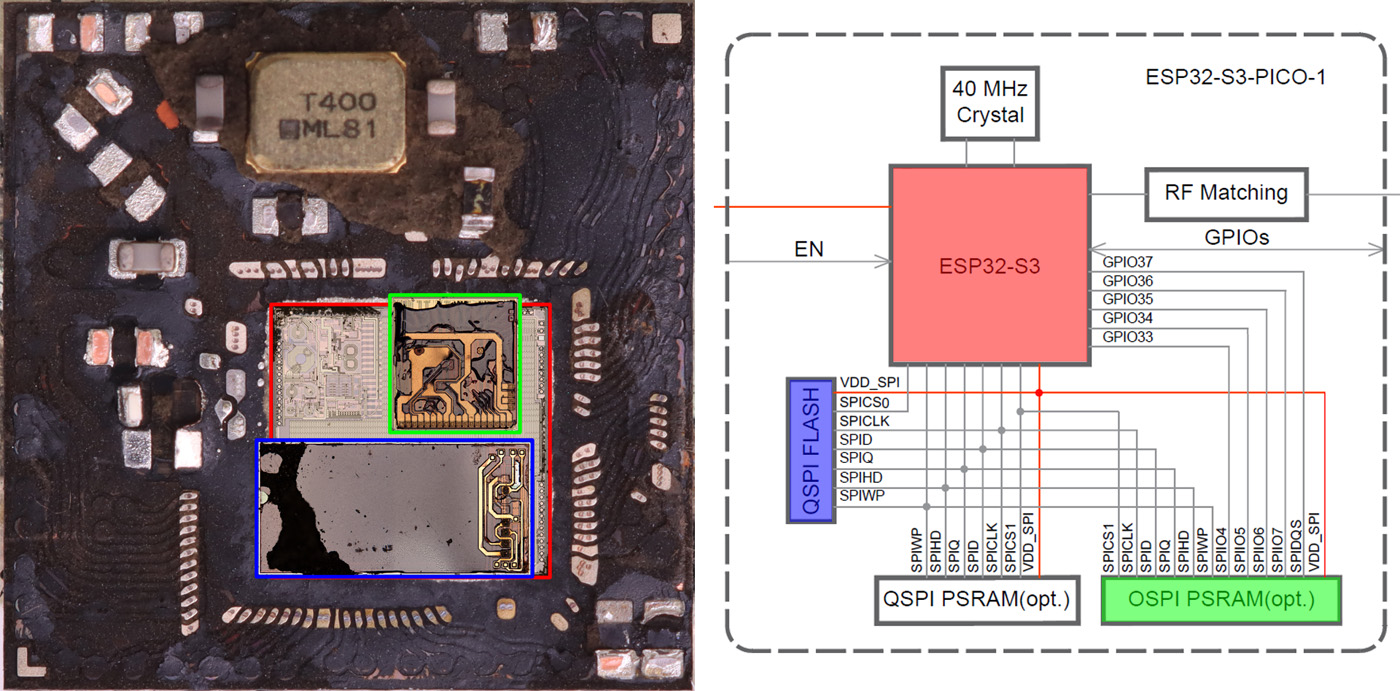

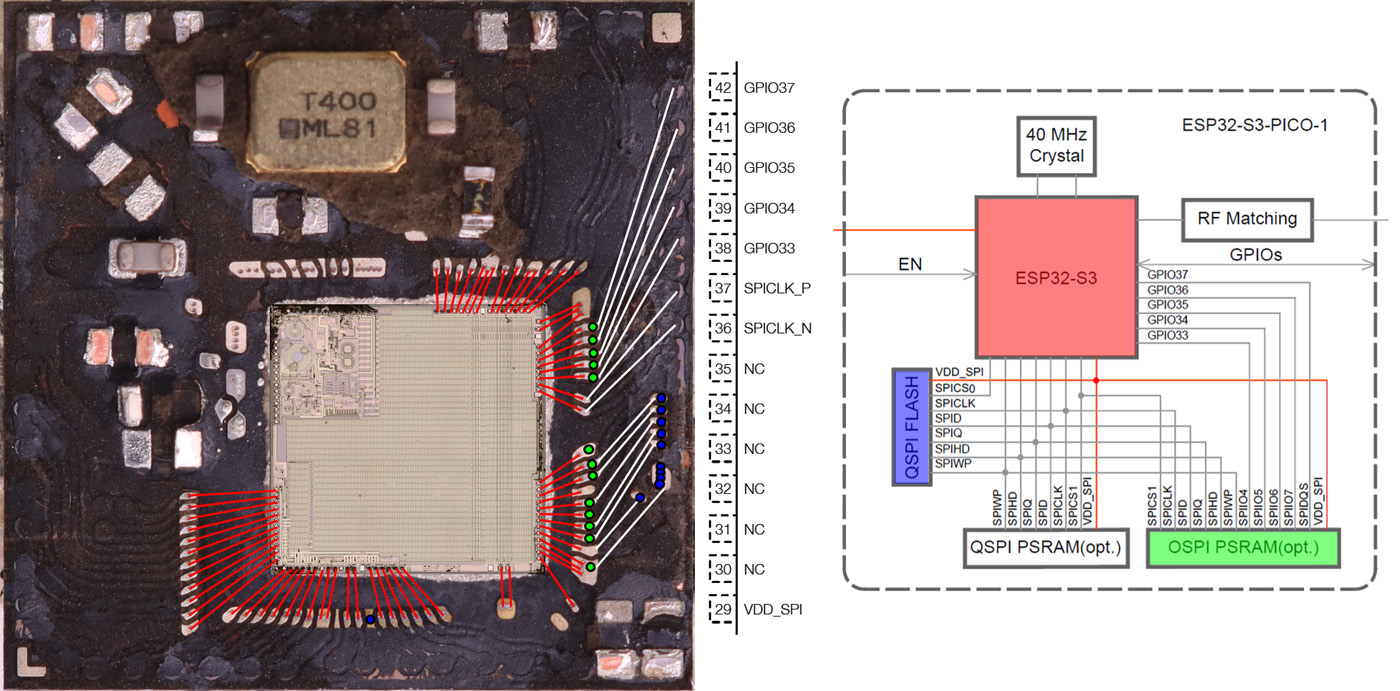

Der ESP32-S3-PICO1 ist ein sogenanntes SiP, ein "System in Package". In dem TFQFN-56 Gehäuse befindet sich der Mikrocontroller, der auch einen Großteil der HF-Schaltungsteile enthält. Außerdem hat die passiven Elemente der Antennenanpassung, den Quarzresonator und die Entkopplung der Spannungsversorgung integriert. Parallel zum internen Speicher kann der Mikrocontroller auf zusätzliche Speicherelemente zugreifen, die sich ebenfalls im Gehäuse befinden. Dazu zählt ein 8MB großer Flash-EEPROM und ein 2MB oder 8MB großes PSRAM. Beide Speicher sind über einen Quad-SPI Bus mit dem Controller verbunden. Für den 8MB-PSRAM hat man die Schnittstelle auf einen Octal-SPI Bus erweitert.

Die Variante mit 2MB PSRAM trägt die Zeichenfolge N8R2 in der Bezeichnung. Die Variante mit 8MB PSRAM, die hier vorliegt, hat man mit N8R8 markiert. Interessant ist in diesem Zusammenhang der zulässige Betriebstemperaturbereich. Mit 2MB PSRAM darf die Umgebungstemperatur 85°C erreichen. Bei der Variante mit 8MB PSRAM liegt die Grenze bei 65°C. Offenbar ist bei der Vollbestückung die Entwärmung duch das kleine Gehäuse bereits grenzwertig.

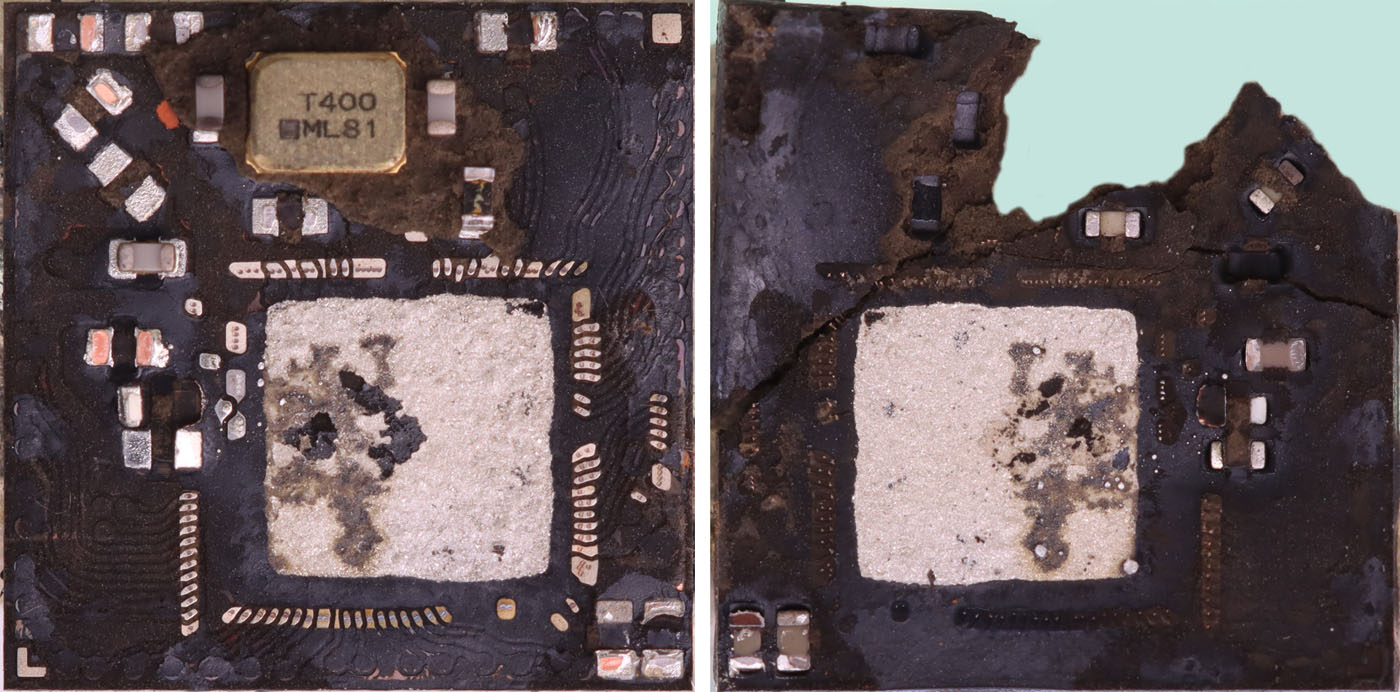

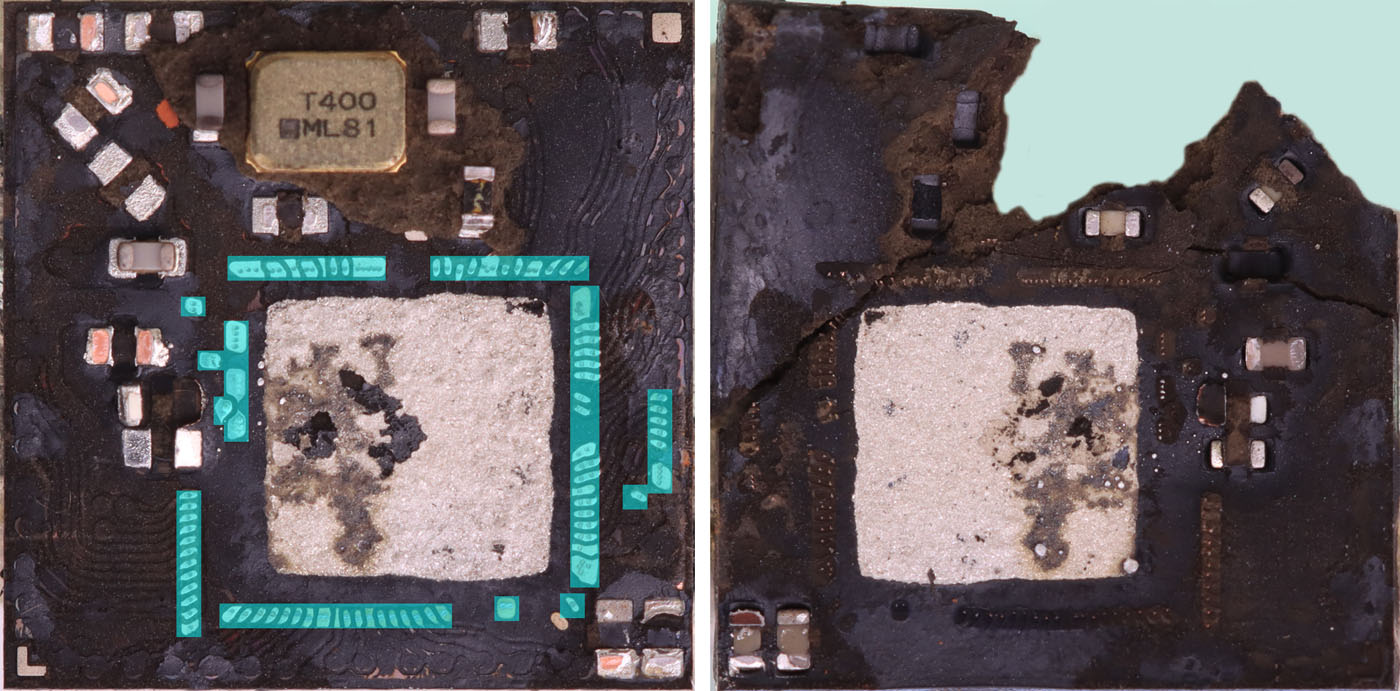

Verbrennt man den Epoxidanteil des Gehäuses, so kann man den Interposer ablösen, die kleine Platine, auf der alle Bauteile platziert sind. Der Controller befindet sich in den Überresten des Gehäusematerials. Der Quarz-Resonator ist deutlich zu erkennen. Über das Gehäuse verteilt hat man einige passive Bauteile platziert.

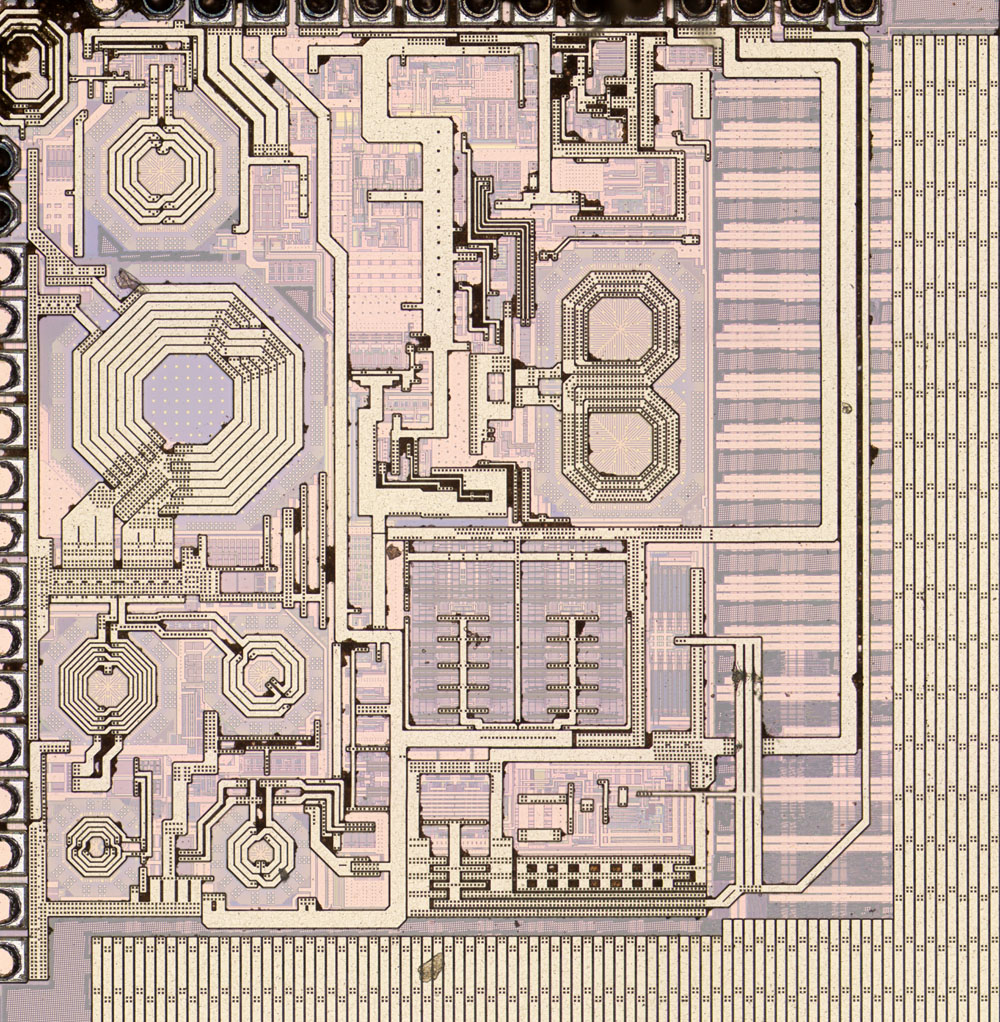

Die Abmessungen des Controllers betragen 2,81mm x 2,77mm. Man erkennt sofort wo sich die HF-Schaltungsteile befinden. Der Rest der Schaltung wird von der obersten Metalllage verdeckt. Sie sorgt für eine niederohmige Verteilung der Versorgungsspannung. Das Datenblatt verrät, dass der Controller auf einem 40nm-Prozess basiert und bei TSMC gefertigt wird.

Dieses Bild ist auch in höherer Auflösung verfügbar: 76MB

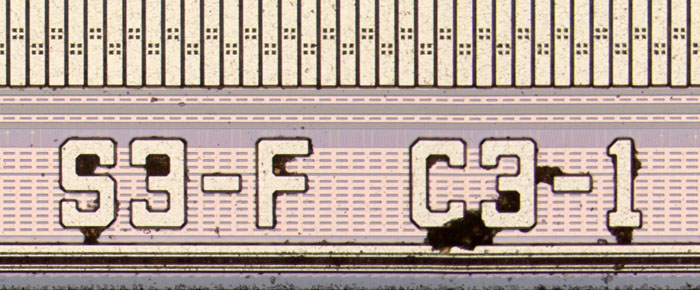

An der unteren Kante sind die Zeichenfolgen S3-F und C3-1 abgebildet. Sie könnten Varianten und Revisionen des ESP32 kennzeichnen.

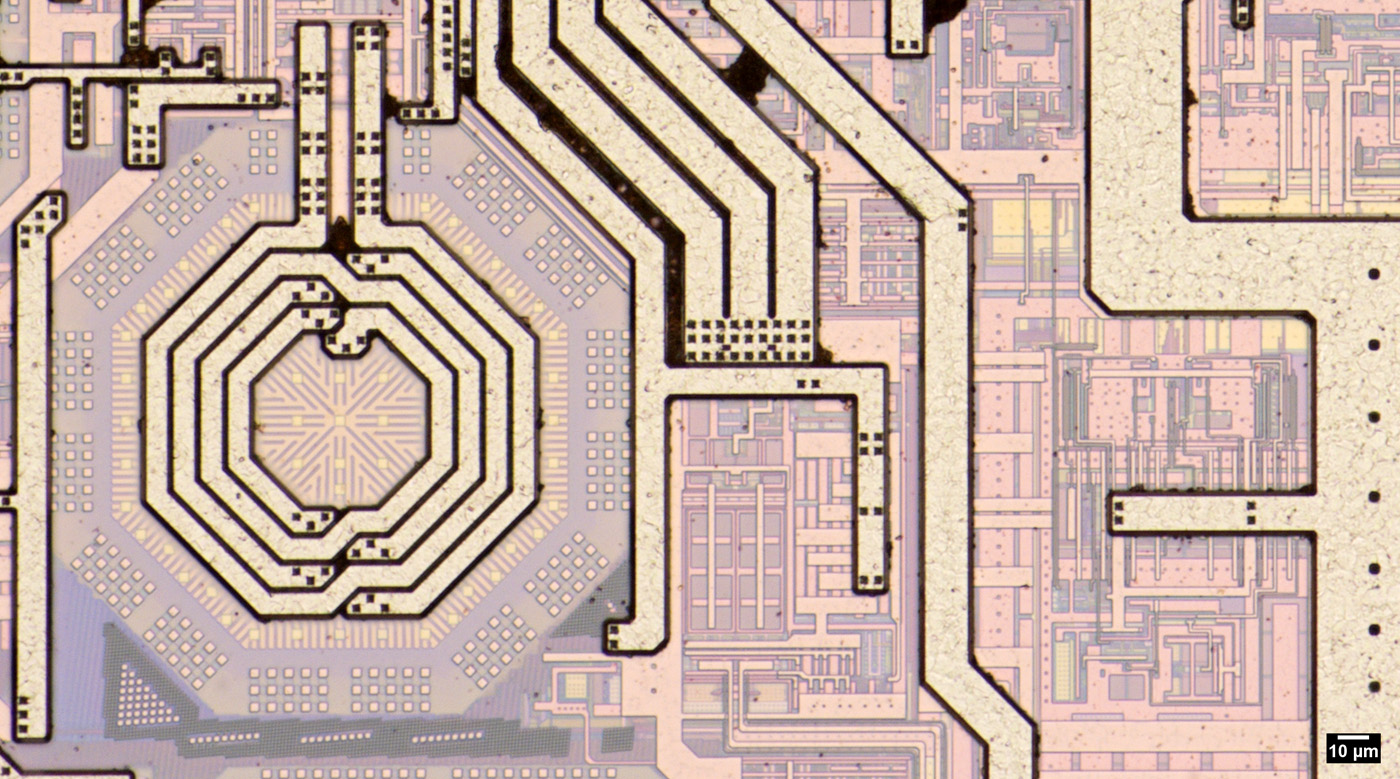

Im HF-Bereich bildet die oberste Metalllage die bekannten ringförmigen Strukturen, die Induktivitäten darstellen.

Im Detail kann man erahnen, dass die unteren Lagen deutlich komplexer sind.

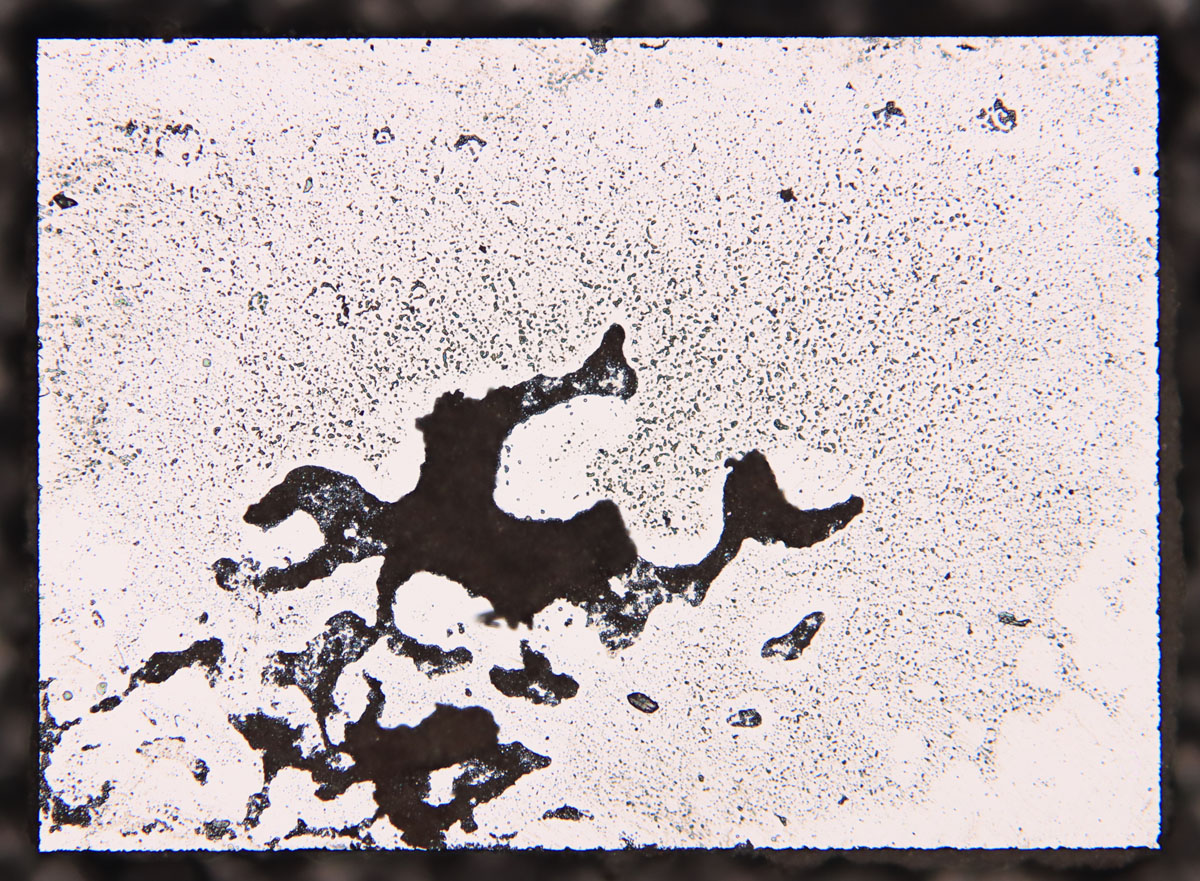

Lässt man eine Zeit lang Flusssäure auf das Die einwirken, so bekommt man einen Eindruck vom Aufbau des Digitalteils. Man kann einige Speicherblöcke mit den für Speicher typischen gleichmäßigen Strukturen erkennen.

Dieses Bild ist auch in höherer Auflösung verfügbar: 30MB

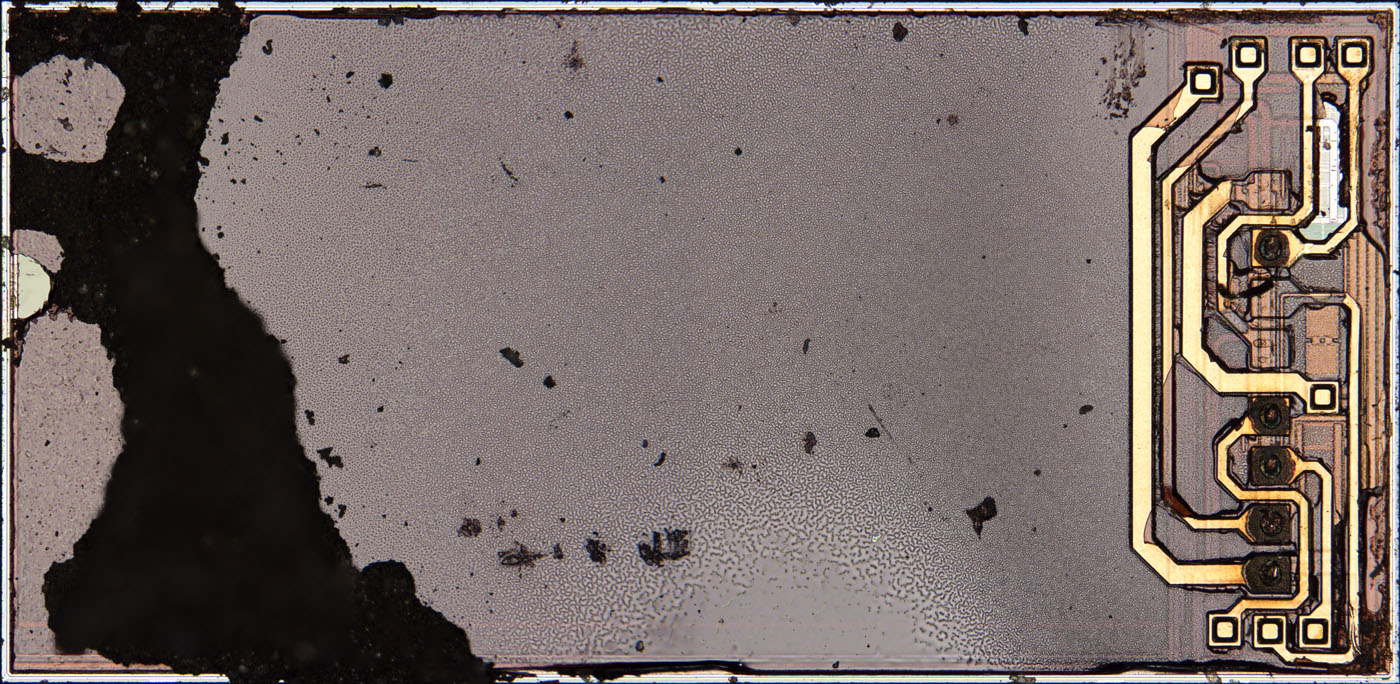

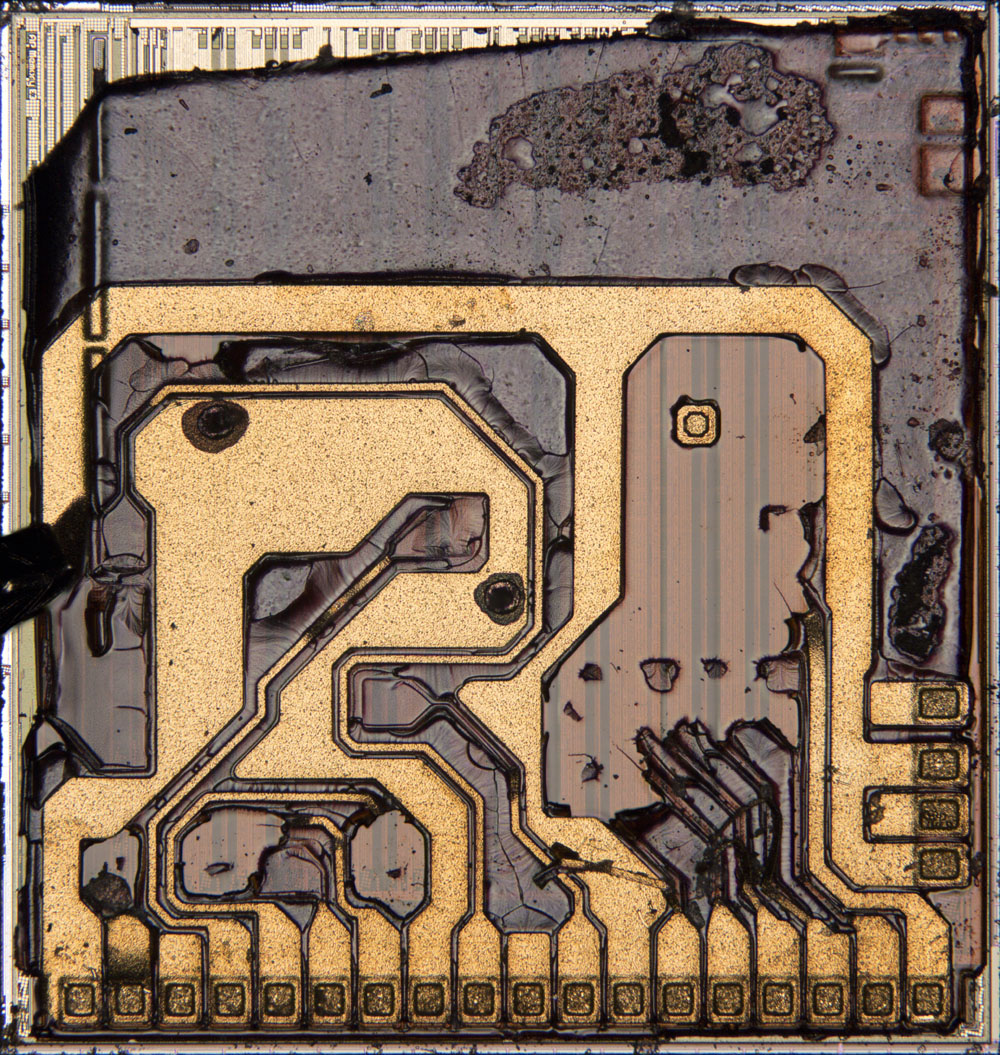

Oberhalb des Controllers findet sich in den Überresten des Vergussmaterials der Flash-EEPROM. Die Abmessungen des Dies betragen 2,80mm x 1,37mm. Auf einer Polyimidschicht befindet sich eine sogenannte RDL, eine Redistribution Layer. In dieser Lage werden die Schnittstellenpotentiale zu den für den Bondvorgang passenden Stellen geführt. Einige Leitungen haben sich hier schon gelöst.

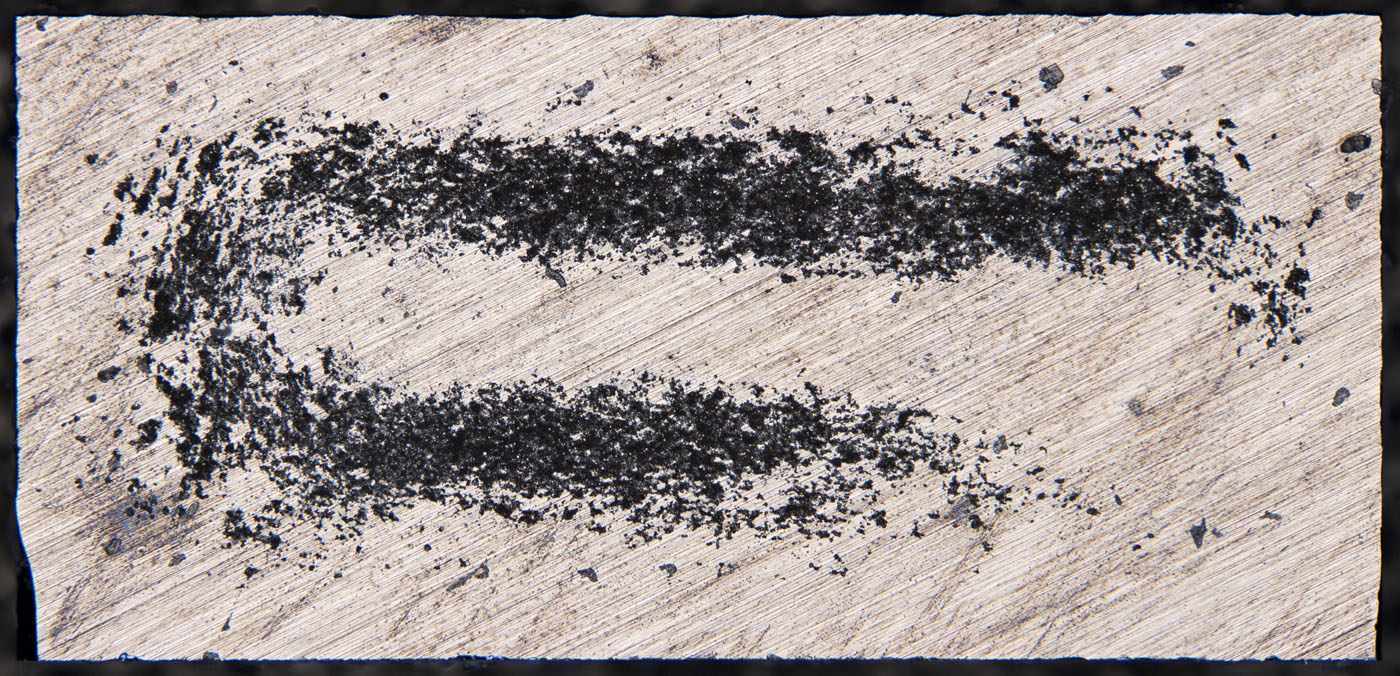

Mit erhöhten Temperaturen kann man auch die Polyimidschicht veraschen. Darunter werden die Blöcke des Speicherbereichs sichtbar. An der rechten Kante befindet sich die notwendige Steuerung.

Dieses Bild ist auch in höherer Auflösung verfügbar: 11MB

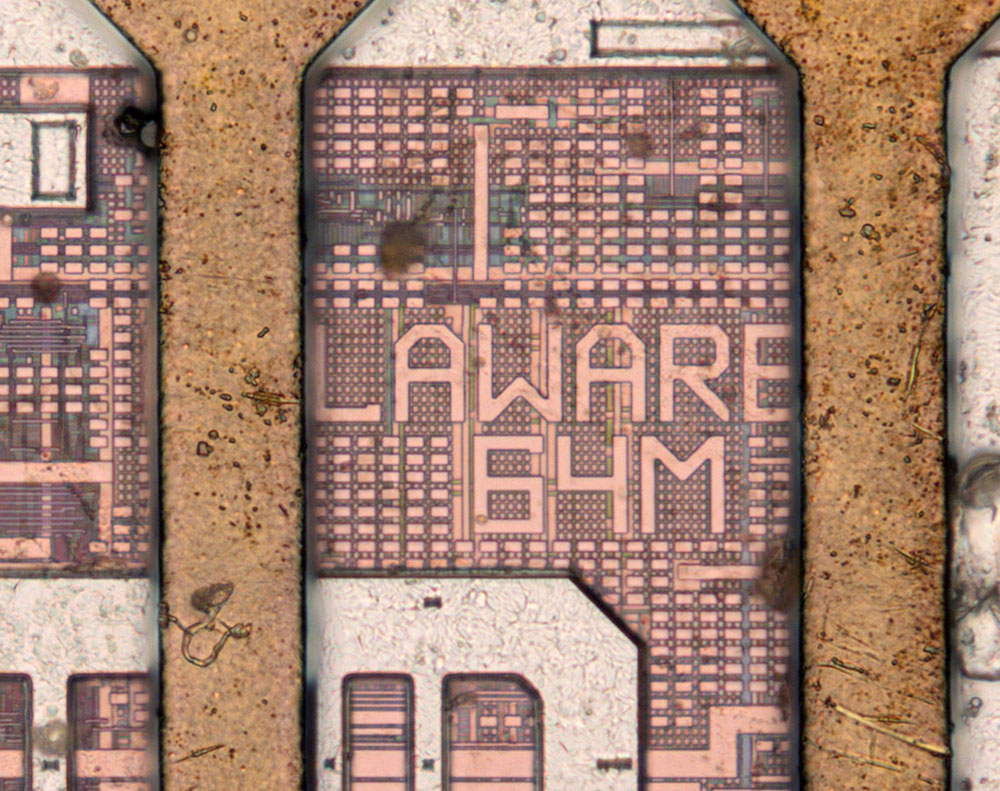

In einer Metalllage findet sich ein Hinweis auf das Speichervolument von 64MBit und die Zeichenfolge LAWARE. Wahrscheinlich steht dort das Wort Delaware.

Zwischen dem Controller und dem Flash-Speicher befindet sich ein Plättchen, das aus Silizium zu bestehen scheint. Auf keiner der beiden Seite sind funktionale Strukturen aufgebracht.

Oberhalb des Controllers ist auch der PSRAM platziert. Die Abkürzung PSRAM steht für Pseudostatischer RAM. Dabei handelt es sich um einen DRAM mit der für DRAM typischen hohe Speicherdichte. Auf dem Die ist allerdings zusätzlich eine Schaltung integriert, die das notwendige, regelmäßige Aktualisieren der Speicherzellen übernimmt. So verhält sich der PSRAM nach außen wie ein SRAM, der keine regelmäßige Aktualisierung benötigt.

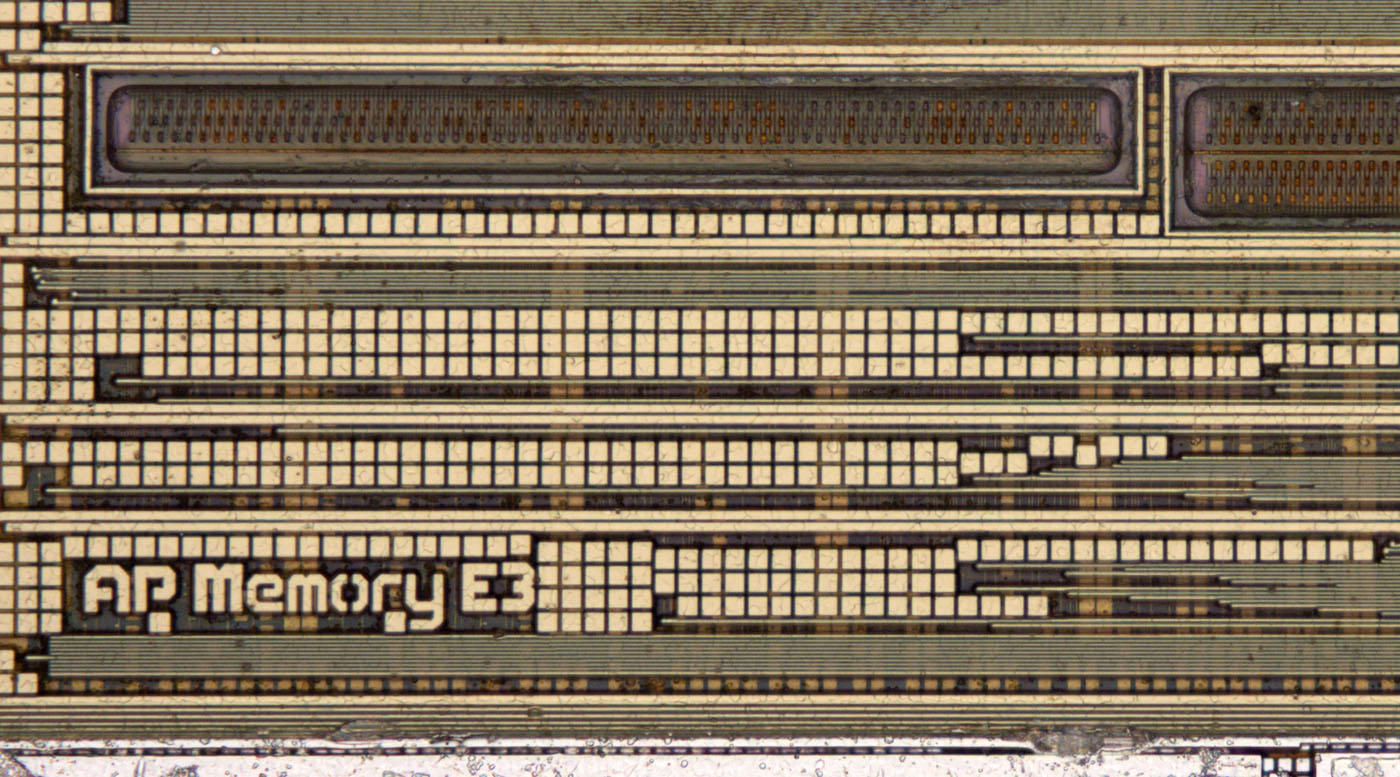

Die Abmessungen des Dies betragen 1,37mm x 1,31mm. Auch hier befindet sich auf dem Die eine Polyimidschicht, die eine Redistribution Layer trägt. Die Octal-SPI Schnittstelle benötigt deutlich mehr Signale, bietet aber auch eine größere Bandbreite.

Der eigentliche Speicherbereich befindet sich in der Mitte des Dies. Dort sind vier große, ähnliche Blöcke zu erkennen. Vor allem an der linken Kante, aber auch in den rechten Ecken wurden Fenster integriert, die eine gewisse Konfigurationsmöglichkeit bieten. Man kann davon ausgehen, dass darüber defekte Speicherzellen deaktiviert und Reservezellen in die Schaltung eingebunden werden können.

Dieses Bild ist auch in höherer Auflösung verfügbar: 25MB

Eine Zeichenfolge verrät, dass der PSRAM von AP Memory entwickelt wurde. E3 könnte eine interne Projektbezeichnung oder eine Revision sein. Im oberen Bereich sieht man die Fenster und die darin enthaltenen Schaltelemente. Höchstwahrscheinlich handelt es sich um Verbindungen, die mit einem Laser unterbrochen werden können.

Auch unter dem PSRAM befindet sich ein Plättchen ohne funktionale Strukturen.

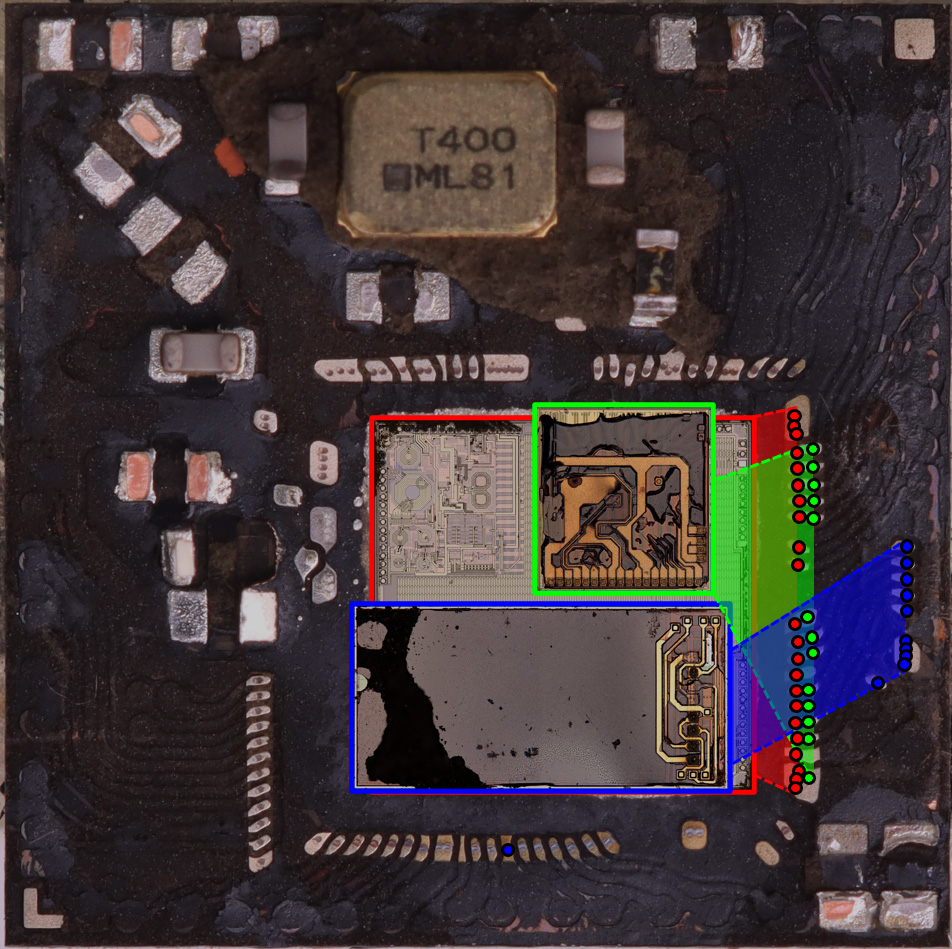

Nach der Dokumentation der drei integrierten Schaltkreise lohnt ein erneuter Blick auf den Interposer und die Platzierung der Elemente. Der HF-Bereich des Controllers befindet sich in der linken oberen Ecke des Dies. passend dazu sind in diesem Bereich einige Potentiale mit mehreren Bonddrähten angebunden. Dort sind auch die meisten passiven Elemente platziert. Dabei dürfte es sich unter anderem um Elemente zur Impedanzanpassung und um Kapazitäten zur Entkopplung der Versorgungsspannung handeln.

Rechts des Controllers fällt auf, dass viele Bondflächen mit zwei Bonddrähten hintereinander kontaktiert wurden. An einer Stelle ist zusätzlich eine zweite Reihe mit Bondflächen platziert. Die Bonddrähte kann man auch relativ gut in den Überresten des Gehäusematerials erkennen.

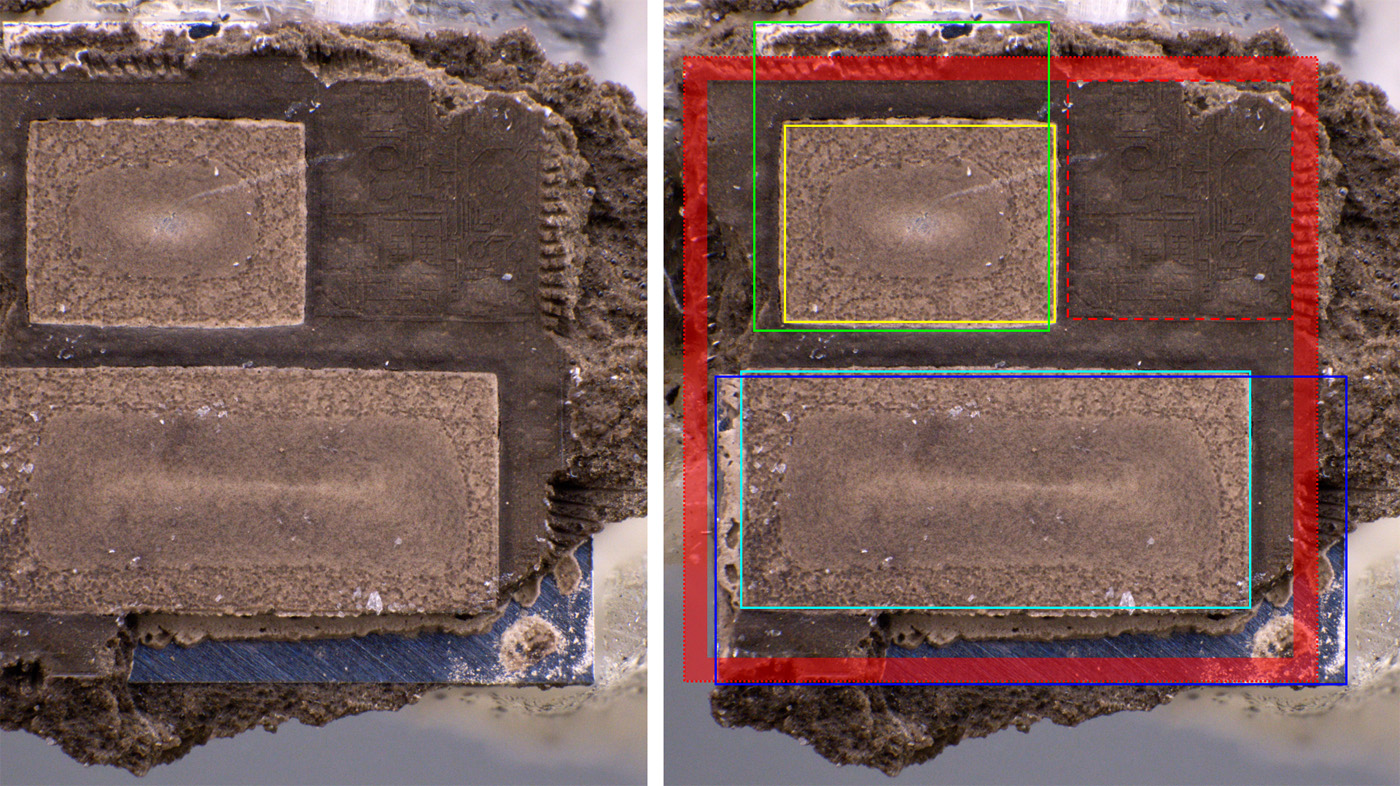

Bei einem ESP32-S3-PICO1 konnte man den Controller so von den Speicherelementen lösen, dass der Aufbau deutlicher wird. Die prägnanten Strukturen des HF-Bereichs des Controllers haben sich im Epoxid abgebildet. Außerdem sind die blanken Siliziumblöcke direkt zu erkennen (gelb/türkis). Ein Stück weit zeigen sich auch schon die Speicherelemente selbst (grün/blau). Mit dem Wissen um die Größen der einzelnen Elemente kann man die Anordnung rekonsturieren.

Damit ergibt sich folgendes Bild bei der Anordnung der integrierten Schaltkreise.

Auch aus der Anordnung der Bonddrähte und den erkennbaren Verbindungen kann man einiges herauslesen. Wie im Blockschaltbild dargestellt, teilen sich der Flash-EEPROM und der kleine PSRAM den gleichen Quad-SPI Bus. Der große PSRAM ist zusätzlich an den GPIOs 33 bis 37 angeschlossen. Diese Verbindungen finden sich auf dem Interposer wieder. Ein Potential des Controllers ist exklusiv mit dem Flash-EEPROM und ein anderes Potential exklusiv mit dem PSRAM verbunden. Dabei muss es sich um die Auswahlleitungen handelt.

Es fällt auf, dass beim Flash-EEPROM ein Potential mit vier Bonddrähten kontaktiert wurde. Dabei müsste es sich um das Bezugspotential handeln. Unklar bleibt, wie man vier Bonddrähte mit einem einfachen Bondpad des Flash-EEPROMs verbinden konnte oder ob es noch andere Verbindungen gab. Die blanken Siliziumplättchen sind auf jeden Fall von den Speicherelementen verdeckt und sind daher nicht mit Bonddrähten erreichbar.

Auf dem Die des PSRAM befindet sich ein Bondpad mehr als im Blockschaltbild dargestellt. Man zählt auch einen zusätzlichen Bonddraht auf dem Interposer. Das erscheint logisch, da im Blockschaltbild das Bezugspotential fehlt. Im Fall des Flash-EEPROMs fehlt im rechten Bereich des Interposers dieser zusätzliche Bondkontakt. An der unteren Kante des Interposers zählt man allerdings ein kontaktiertes Potential mehr als man erwarten würde. Es scheint so, als ob dort auch ein Bonddraht des Flash-EEPROM endete.

Die Kontaktierung von Controller, PSRAM und Flash-EEPROM ist eine Herausforderung. Vermutlich waren die Siliziumblöcke unter dem PSRAM und dem Flash-EEPROM notwendig, um die passenden Abstände für die Bonddrähte zu erreichen. Das Package ist 1mm hoch. Abzüglich des Interposers beträgt die Höhe nur 0,75mm. In dieser Höhe überlagern sich drei Gruppen von Bonddrähten. Der dafür freie Raum reduziert sich teilweise noch um die Höhen der integrierten Schaltkreise und Siliziumblöcke. Außerdem muss ein Abstand zur Oberfläche des Gehäuses gehalten werden.

Beim PSRAM (grün) wundert man sich, dass das Die nicht gedreht wurde. Die meisten Kontakte reihen sich an der unteren Kante des Dies auf, während sich die Kontaktflächen auf dem Interposer rechts befinden. Die Abmessungen sprechen aber tatsächlich dafür, dass der PSRAM wie hier dargestellt im Package liegt. Der verhältnismäßig weite Weg zu den untersten Bondpads des Interposers könnten eine Erklärung für die Ausrichtung sein.