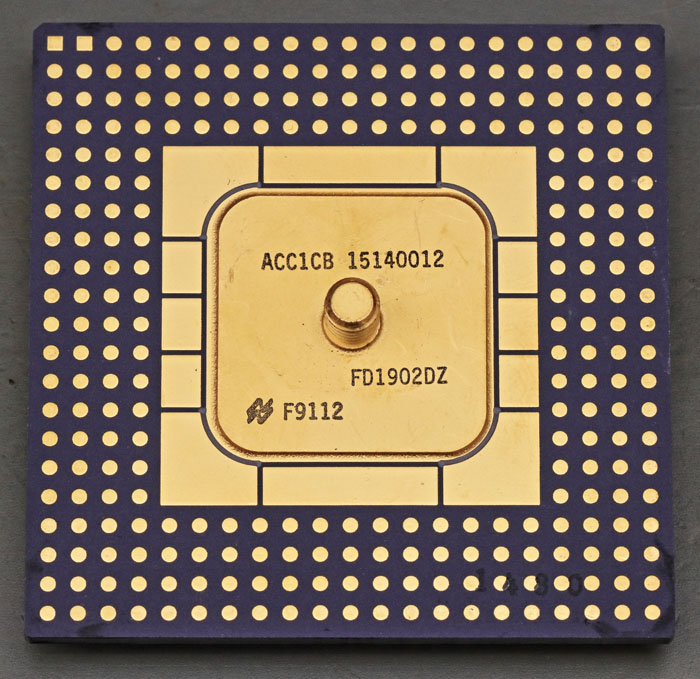

Hier ist ein auf ECL basierendes Gate Array zu sehen, das im CDC Cyber C2000 im Bereich der CPU eingesetzt wurde. Der C2000 gehört zu einer Familie von Supercomputern. Hersteller des Gate Arrays ist National Semiconductor. Der Datecode verweist auf das Jahr 1991. Wie sich noch zeigen wird, ist FD1902 die Bezeichnung des Bausteins. Ein zweites Gate Array des CDC Cyber 2000 ist der FD2104.

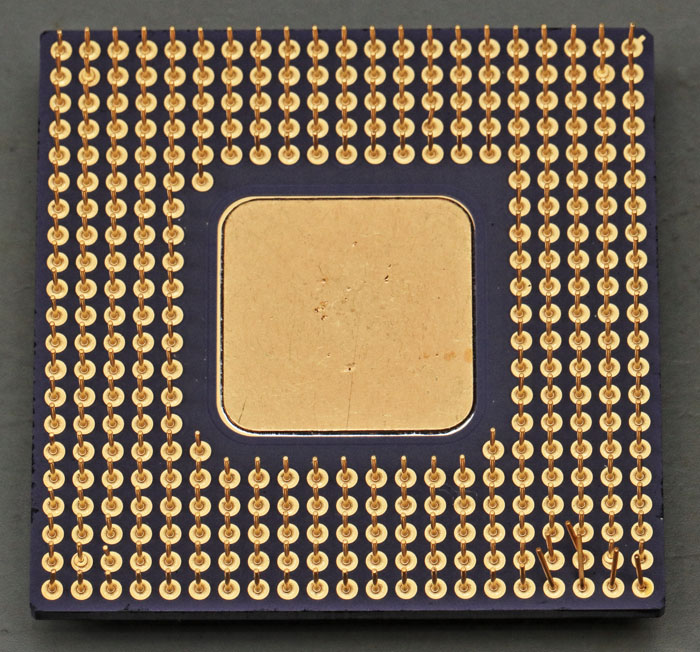

Das PGA-Gehäuse besitzt sowohl auf der Unterseite als auch auf der Oberseite einen Metalldeckel. Der obere Metalldeckel trägt den Chip und besitzt einen Metallbolzen, der höchstwahrscheinlich dazu dient einen Kühlkörper zu befestigen. Der obere Metalldeckel ist etwas erhöht. Das ist im Hinblick auf den Kühlkörper sinnvoll, da sich auf der Oberseite des Gehäuses sehr viele Kontaktflächen befinden, die ansonsten eigens isoliert werden müssten.

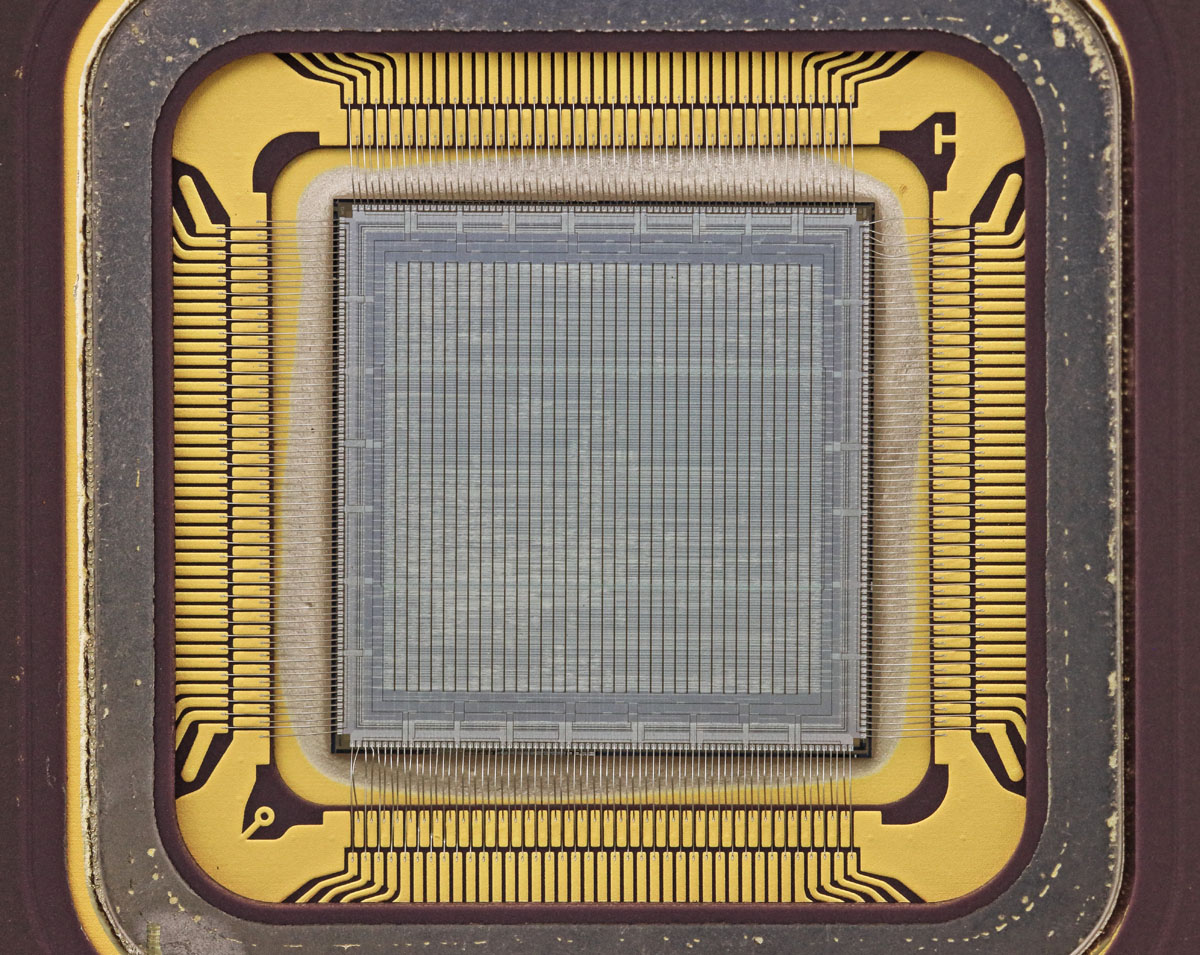

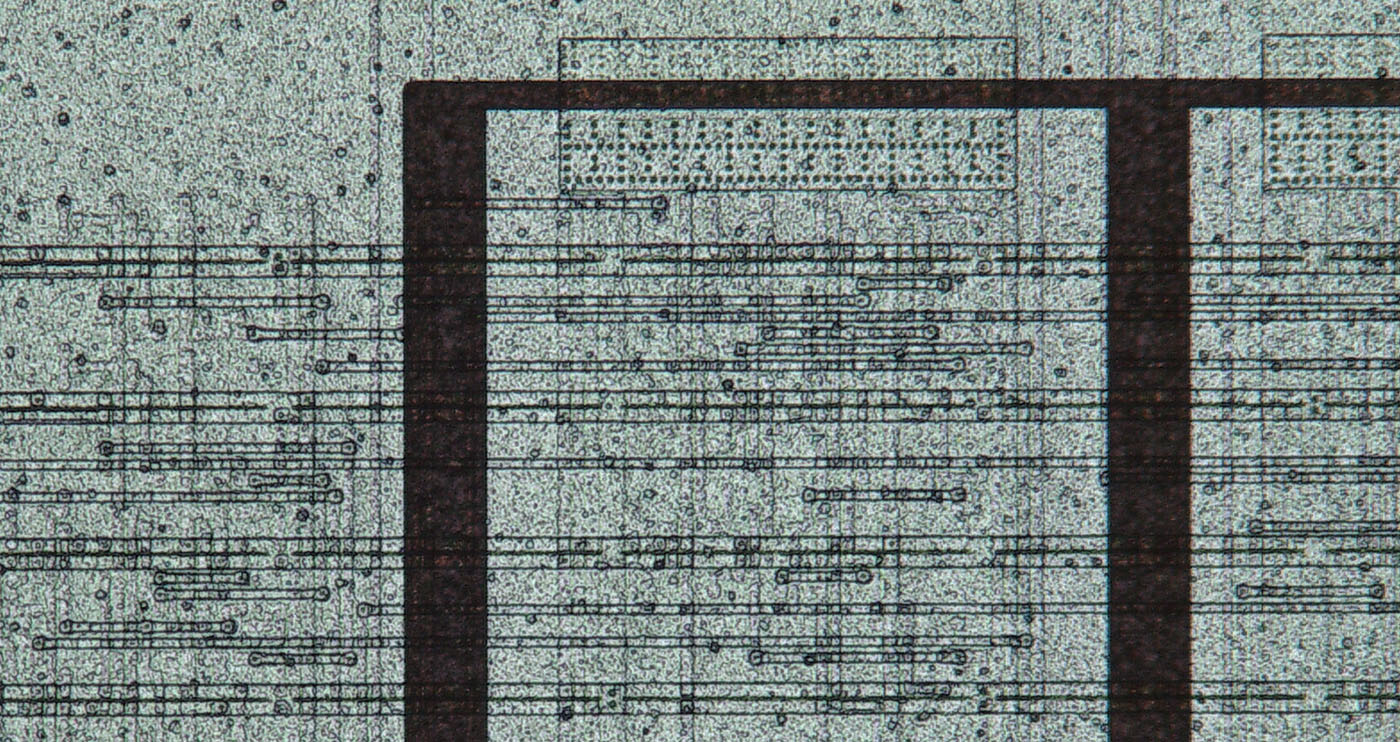

Entfernt man den unteren Deckel, so kann man einen Blick auf das Die werfen. Die Abmessungen betragen 11,8mm x 11,6mm. Im Überblick fallen die sehr breiten Versorgungsleitungen auf, die mehrere Rahmen bilden und auch im Inneren des Dies fast die vollständige Fläche bedecken.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 70MB

Die Buchstaben FCI, die neben dem Copyrightsymbol abgebildet sind, könnten für Fairchild Camera and Instruments stehen. Fairchild ist im Laufe der Zeit in National Semiconductors aufgegangen.

An der oberen Kante ist eine Teststruktur zu erkennen, die offenbar das Auflösungsvermögen des Prozesses im Bereich zwischen 1,3µm und 0,7µm dokumentiert.

FD1902 scheint die Bezeichnung des Bausteins zu sein. Diese Zeichenfolge findet sich auch auf dem Gehäuse.

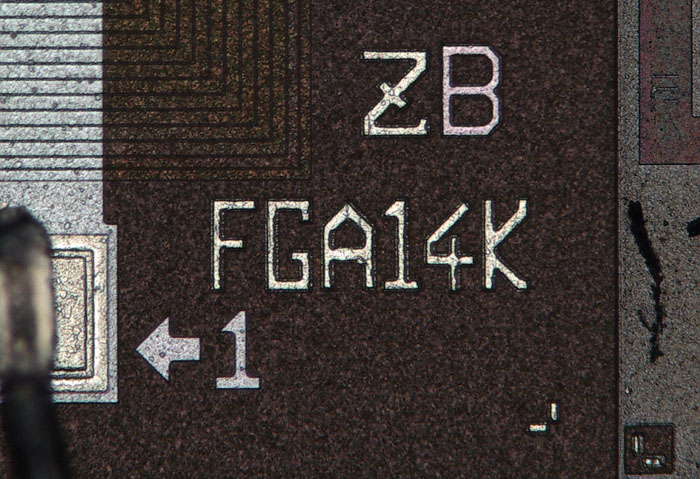

Die Bedeutung der Zeichenfolge ZB bleibt offen. FGA14K ist die Bezeichnung des Gatearrays.

Beim hier verwendeten Gate Array handelt es sich um das Modell FGA14000. Im "National Semiconductor F100K ECL Logic Databook and Design Guide" finden sich einige Informationen zu der dahinterstehenden Produktfamilie.

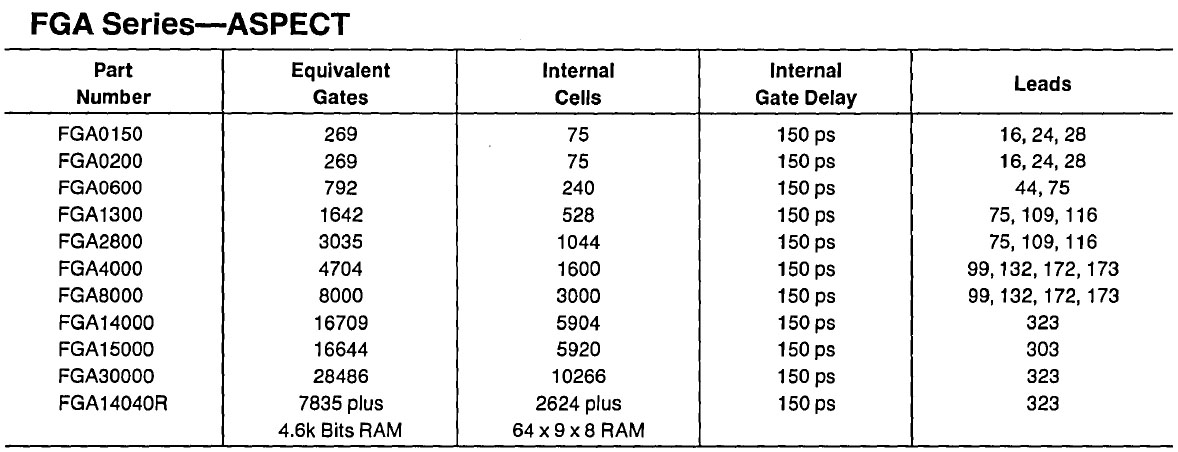

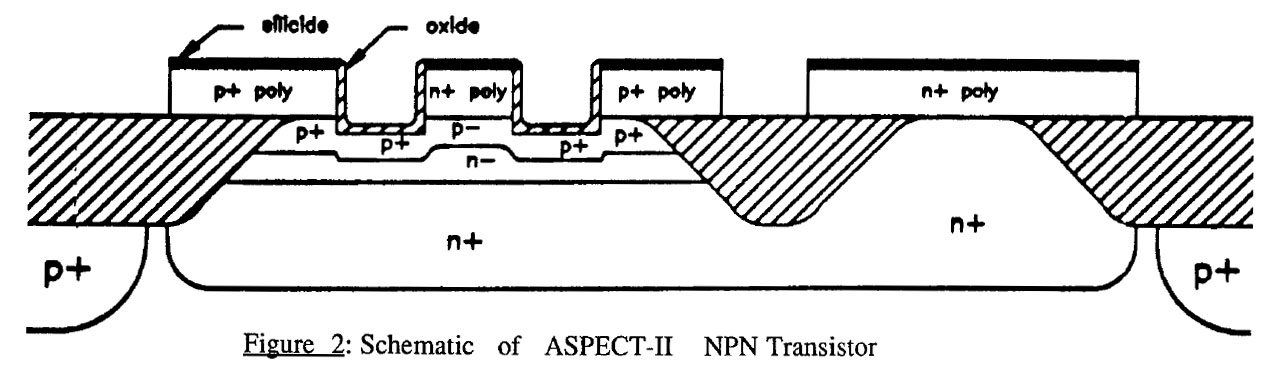

Die FGA Gate Arrays hat National Semiconductor mit dem Prozess ASPECT-II aufgebaut. ASPECT steht für "Advanced Signal Poly Emitter Coupled Technology". Hintergrundinformationen zu diesem Prozess finden sich in der IEEE Veröffentlichung "A 30,000 Gate ECL Gate Array using advanced single poly technology and four level metal interconnect". Demnach beträgt die minimale Strukturbreite 1,5 µm und die Verdrahtung erfolgt in vier Metalllagen. Das Schnittbild zeigt einen der Bipolartransistoren, die eine Grenzfrequenz von 10GHz bieten.

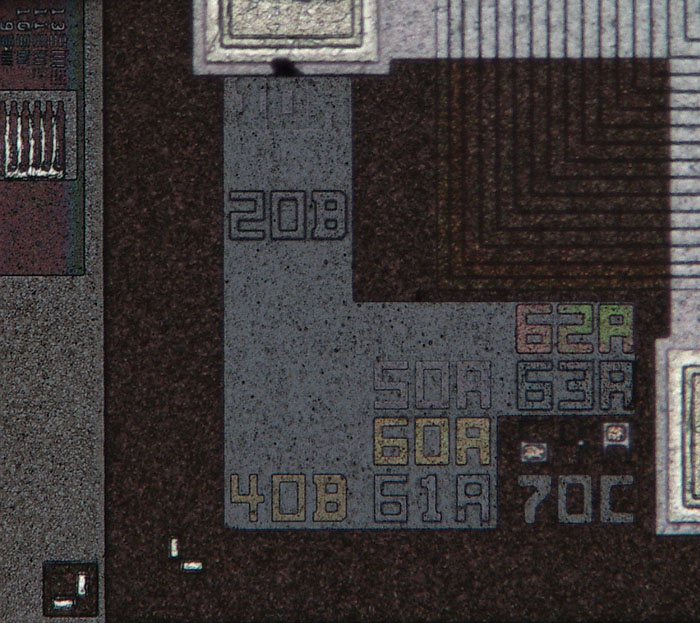

In einer Ecke des Bausteins sind mehrere Masken abgebildet.

Von der integrierten Schaltung selbst ist kaum etwas zu erkennen. Das liegt nicht nur an den massiven Versorgungsleitungen und den vier Metalllagen, sondern auch daran, dass zumindest eine der oberen Isolationsschichten fast vollständig undurchsichtig ist.