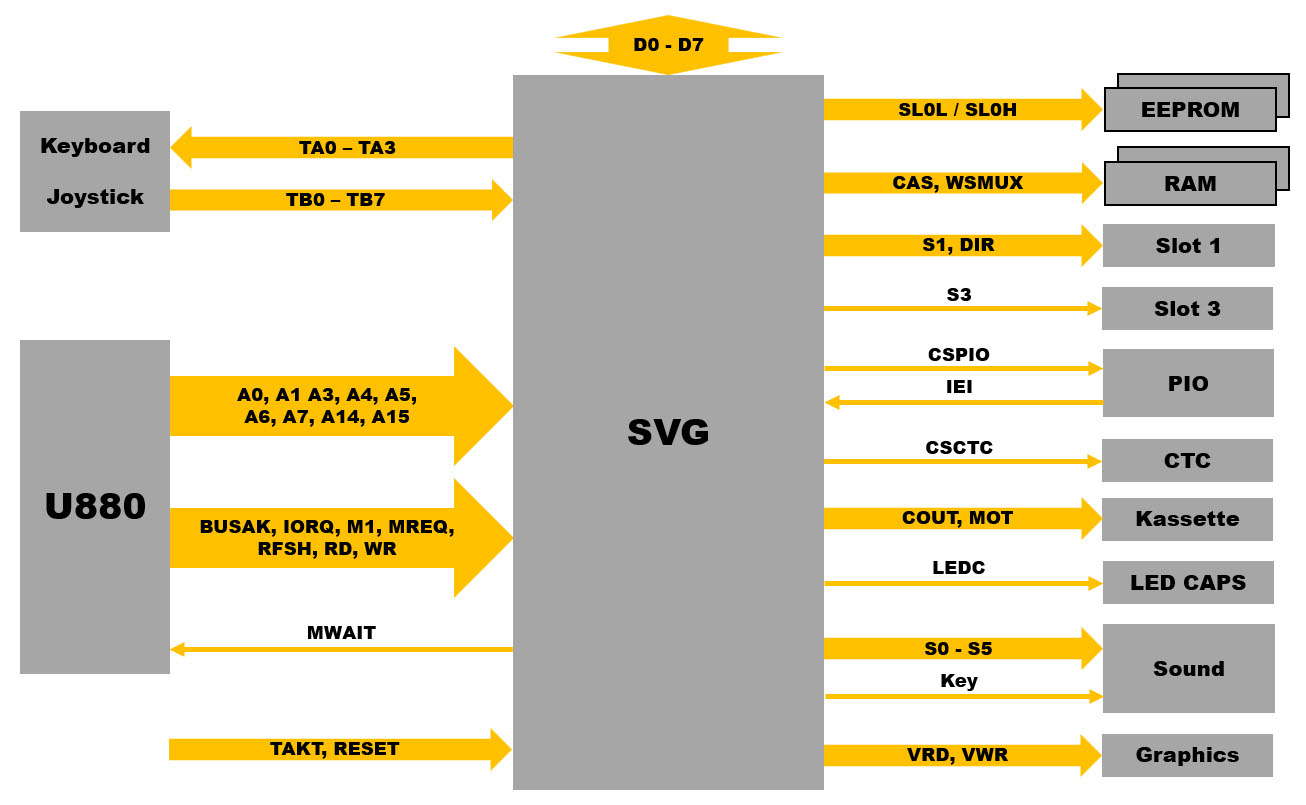

Aus dem Schaltplan des Bildungscomputer Robotron A5105 kann man die Schnittstellen des U1525FC007 extrahieren. Der Baustein ist an den 8Bit breiten Datenbus angebunden und erhält das Taktsignal und das Resetsignal, mit dem auch der Prozessor, arbeitet. Der Prozessor ist ein U880, der funktional einem Z80 entspricht. Direkt vom Prozessor erhält der U1525FC007 einige Steuersignale, woraus er unter anderem das MWAIT-Signal generiert. Aus dem 16Bit breiten Adressbus werden neun Adressleitungen verarbeitet. Der Baustein übernimmt das Einlesen der Tastatur oder der Joysticks und die Sounderzeugung. Außerdem unterstützt der U1525FC007 den U880 bei der Auswahl diverser Funktionsgruppen: ROM, RAM, optionale Einsteckkarten, PIO- und CTC-Baustein, Grafikeinheit und ein optionales Kassettenlaufwerk.

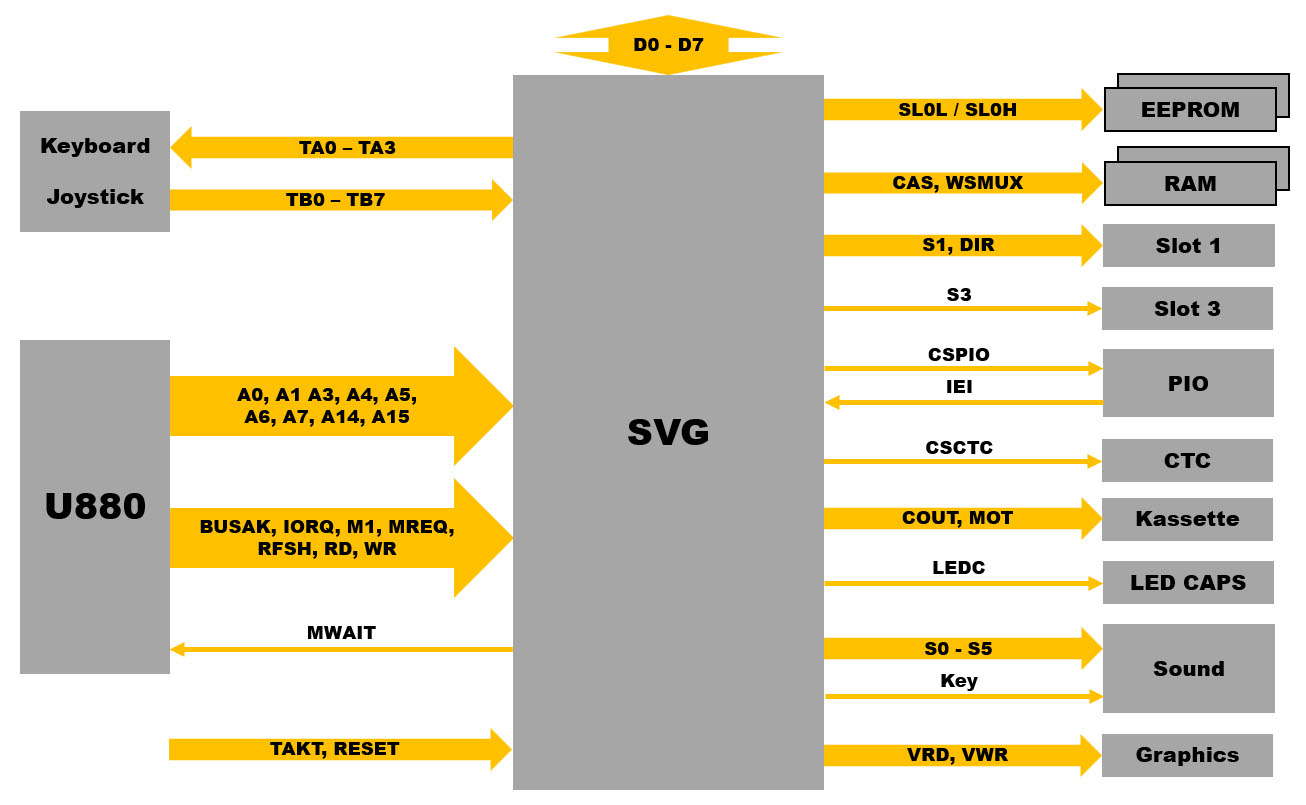

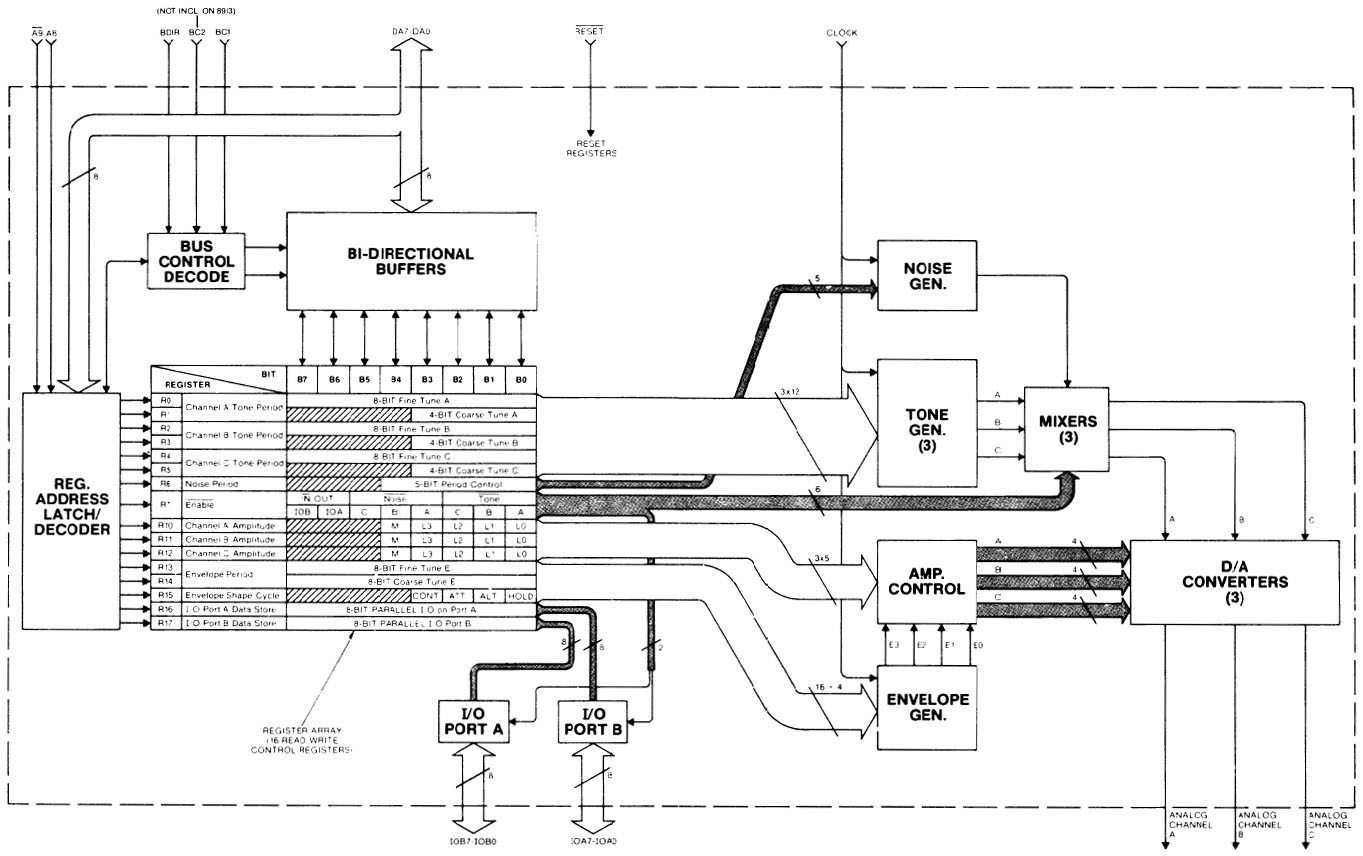

In den Referaten des 13. Mikroelektronik-Bauelemente-Symposiums (Band 7) findet sich einige Informationen zum U1525FC007. Dort nutzt man die Bezeichnung U1520-FC-007, bei der die Chipgröße fehlt. Neben dem Kürzel SVG wird der Baustein außerdem als "Schaltkreis für Speicherverwaltung und Sounderzeugung" bezeichnet. Das abgedruckte Blockschaltbild passt zur Einbindung im Robotron A5105.

Nativ kann der U880 wie der Z80 maximal ein Speichervolumen von 64kB ansteuern. Der U1525FC007 erweitert den Adressierungsbereich. Im Robotron A5105 befinden sich zwei EPROMs, mit Speichergrößen von 32kB und 8kB. Dazu kommen zwei DRAM-Bausteine mit jeweils 32kB. Über Einsteckkarten lässt sich der Speicher erweitern. Im Mikroelektronik-Bauelemente-Symposium ist von 256kB Arbeitsspeicher die Rede. Plausibler ist, dass sich der Speicherbereich insgesamt auf 256kB erweitern lässt. Der Arbeitsspeicher darf im Rahmen der Einteilung im A5105 dann maximal 192kB groß sein.

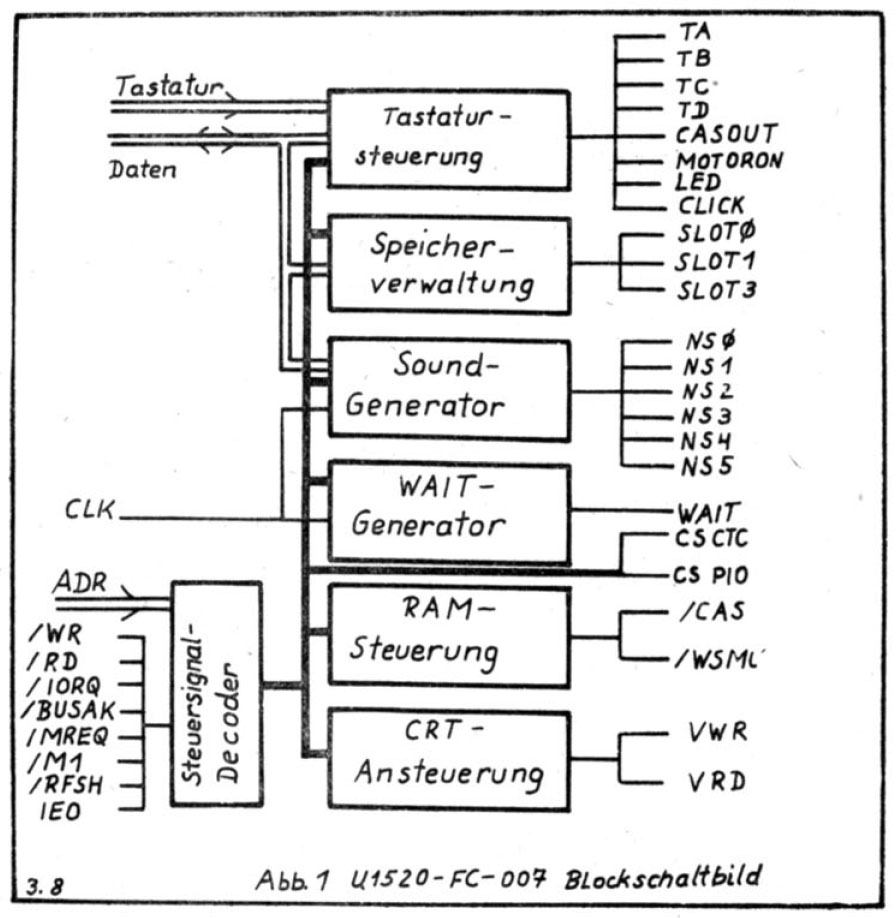

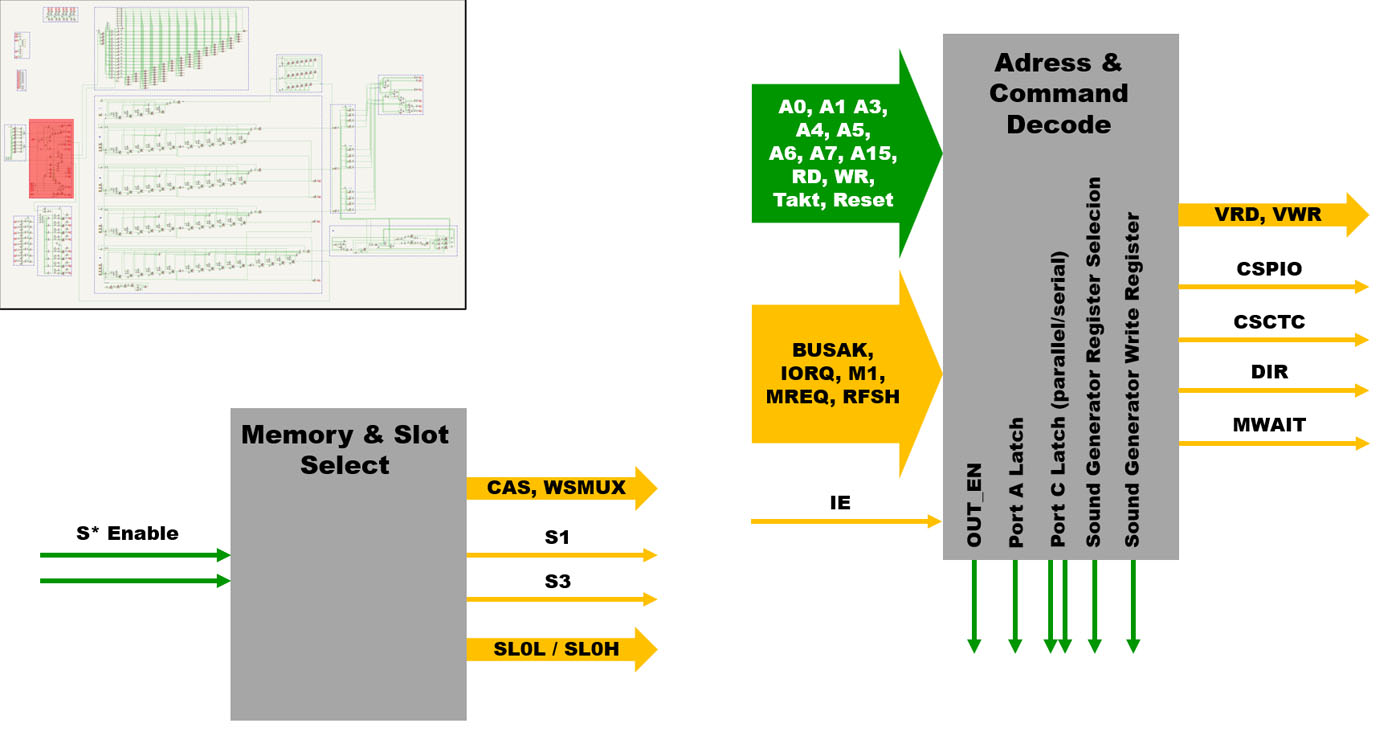

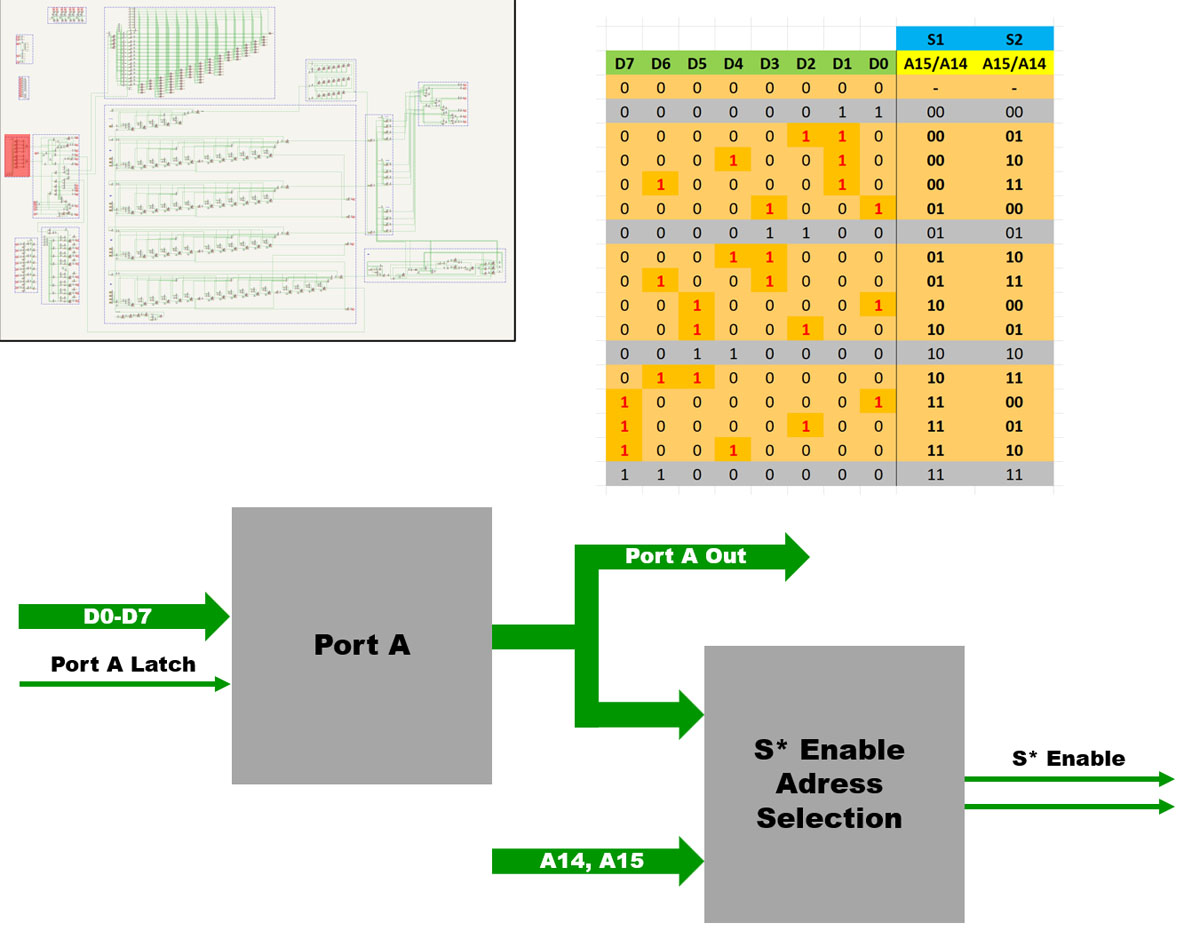

Die Logik im U1525FC007 wurde vollständig in einen KiCad-Schaltplan überführt. Die Nutzung von nur einem Schaltplanblatt vereinfacht die Erstellung der Logikschaltung, da man kreativer arbeiten kann. Außerdem existieren sehr große Schaltungsblöcke, deren Aufteilung sich ungünstig auf die Übersichtlichkeit auswirken würde. Die dicken blauen Rahmen stellen eine Abgrenzung in sich abgeschlossener Funktionsblöcke dar. Das Blockschaltbild aus dem 13. Mikroelektronik-Bauelemente-Symposium war hier noch nicht verfügbar, weswegen die Aufteilung der Schaltung nicht daran angelehnt ist. Das Blockschaltbild deckt sich aber vollkommen mit den extrahierten Funktionen.

Die KiCad-Datei kann hier heruntergeladen werden (2MB). Derart große Grafiken lassen sich nicht sinnvoll in gängige Bildformate wie JPEG packen. Eine SVG-Datei ist hier abgelegt (14MB). Sie lässt sich in Inkscape öffnen und bearbeiten.

Die folgenden Zusammenhänge und Funktionen wurden nach bestem Wissen und Gewissen extrahiert und dokumentiert. Es ist aber durchaus möglich, dass sich kleinere Fehler eingeschlichen haben, einzelne Adressen nicht ganz korrekt sind oder Potentiale invertiert wurden.

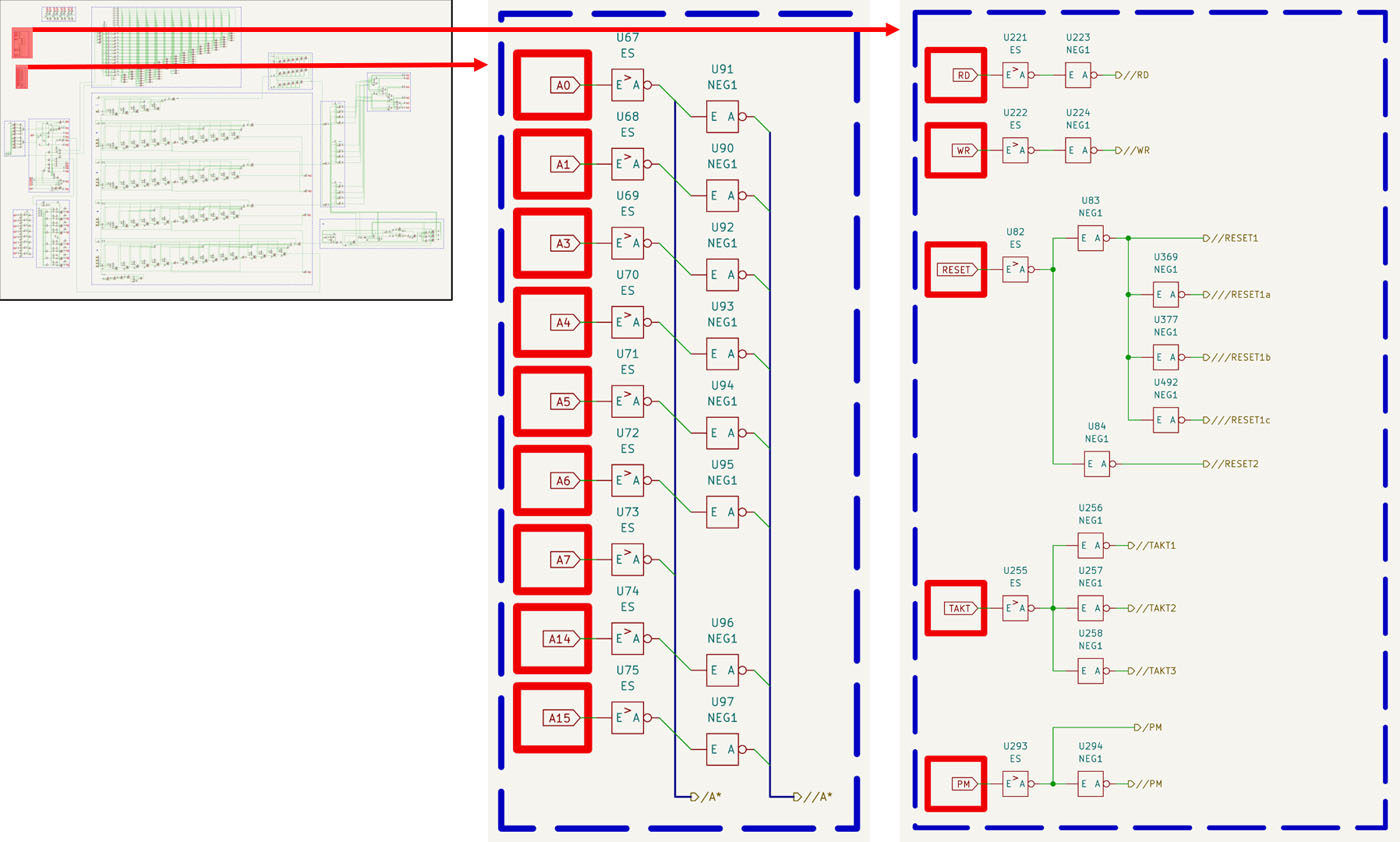

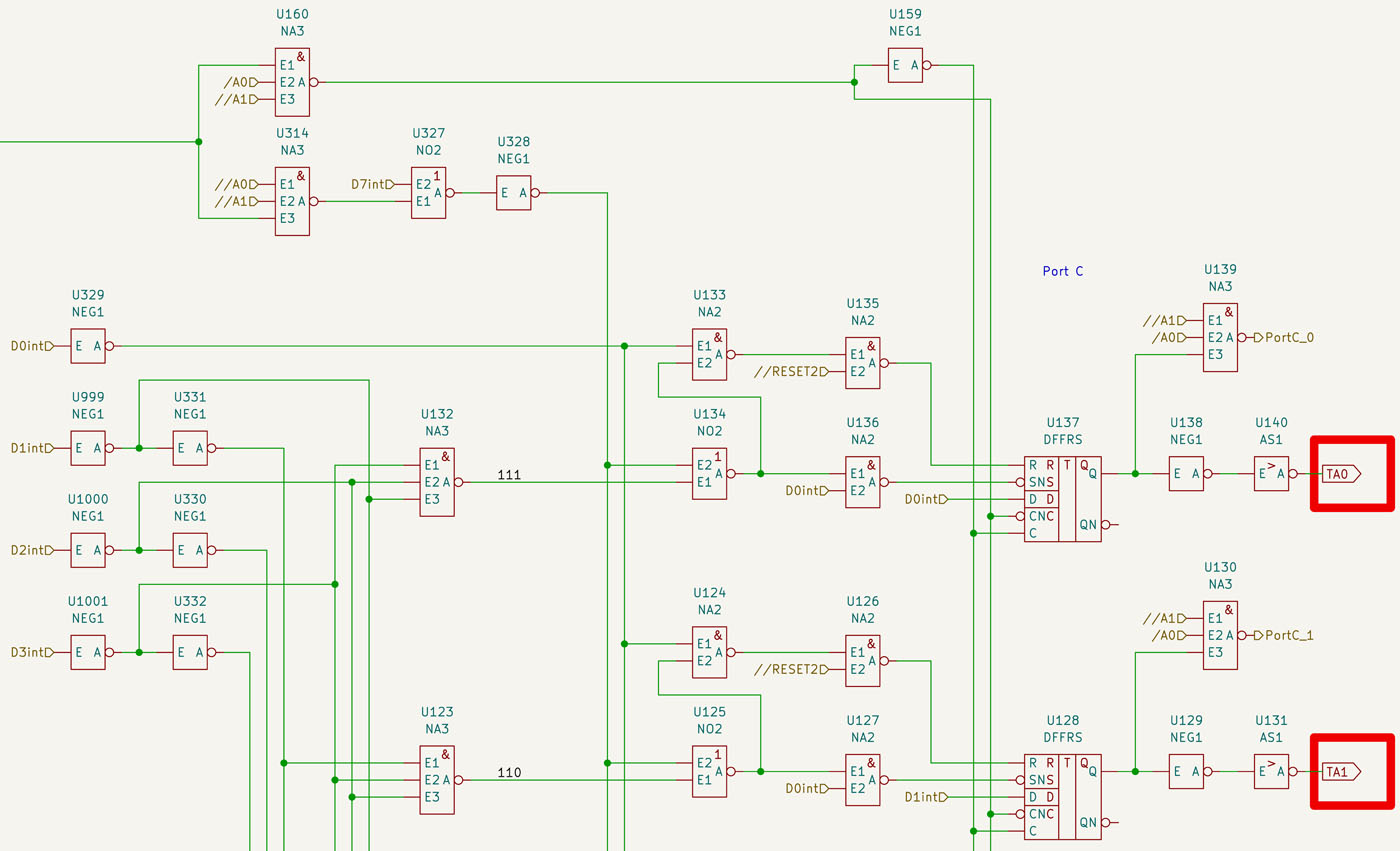

Einige Schnittstellen bieten sich als Start für die Dokumentation der Schaltung an. Dazu zählt zum Beispiel der Adressbus. Die rot umrandeten globalen Bezeichner sind die Schnittstellen nach außen, also die Bondpads. Intern sind die meisten Verbindungen als durchgängige Leitungen eingezeichnet. Lediglich einige stark verzweigte Potentiale, wie der Adressbus, sind mit sogenannten hierarchischen Bezeichnern auf dem Schaltplan verteilt. Der Adressbus durchläuft zuallererst die Eingangsgatter. Die meisten Adressleitungen werden zur weiteren Verwendung zusätzlich invertiert.

Rechts sind weitere globale Signale gesammelt, zum Beispiel das Lese- und das Schreibsignal. Das Resetsignal bedient insgesamt 55 Gatter. Die große Anzahl dürfte ein Grund dafür gewesen sein, dass fünf Inverter das Signal vorverarbeiten. Das Taktsignal bedient nur sieben Gatter, trotzdem hat man hier drei Inverter integriert. Wahrscheinlich waren hier die Anforderungen an die Signalintegrität höher als bei anderen Signalen. Das Signal PM ist im Robotron A5105 über einen Pull-Up-Widerstand mit dem 5V-Potential verbunden. Die Funktion dieses Signals wird später genauer betrachtet.

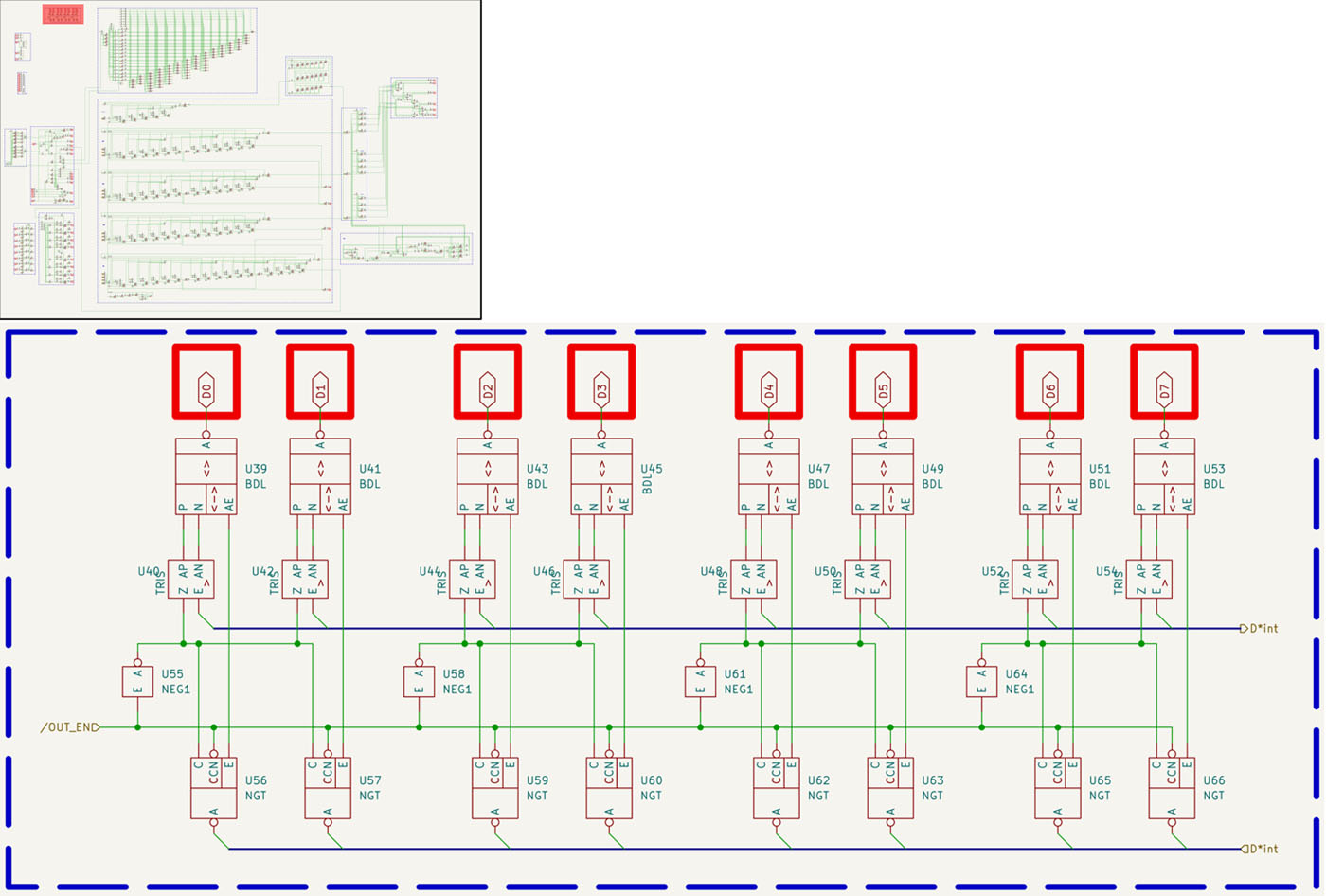

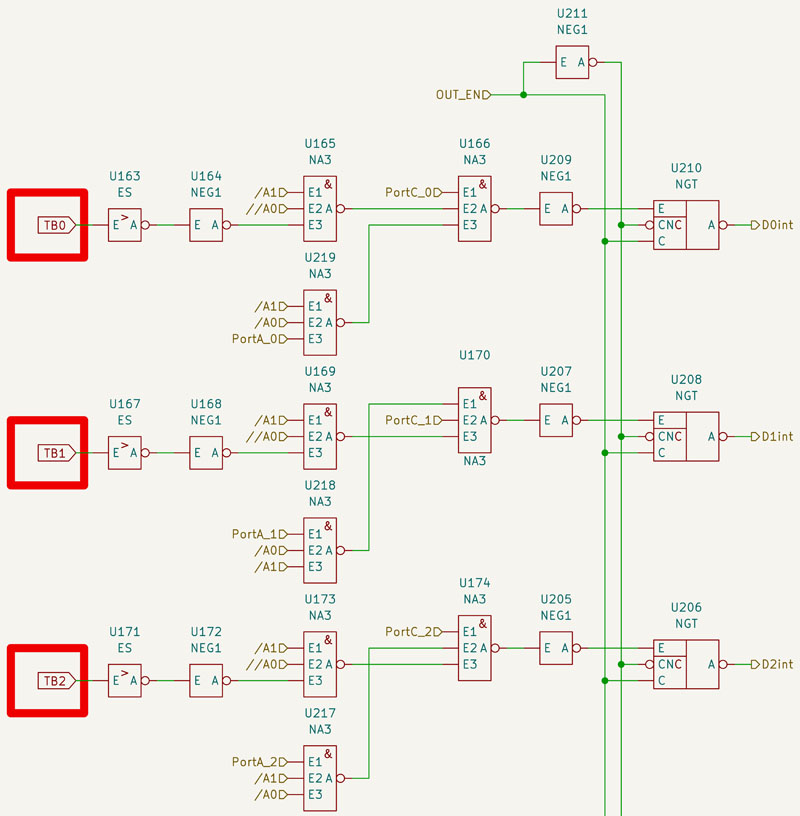

Der Datenbus wird auf bidirektionale Schnittstellengatter mit Tristate-Funktion geführt. Angesteuert werden diese Schnittstellengatter über TRIS-Gatter. Das Signal /OUT_EN steuert, ob Daten auf den Datenbus gelegt werden dürfen oder ob die aktuellen Potentiale einzulesen sind. Das Einlesen übernehmen getaktete Inverter. Aus dieser Schaltung wird ein interner Datenbus generiert.

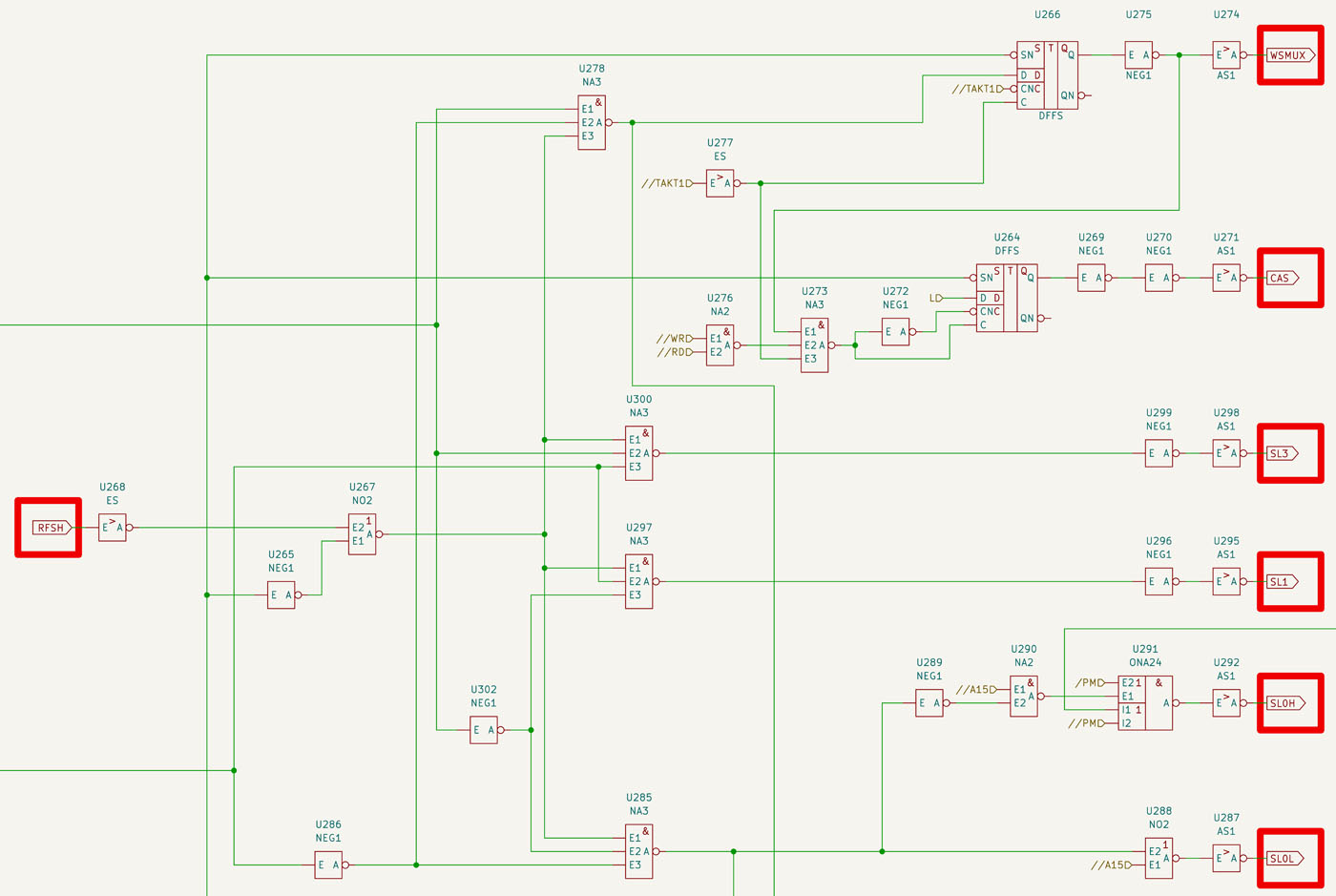

Ein Funktionsblock steuert die Adressierung der Speicherbereiche. SL0L und SL0H aktivieren jeweils einen der zwei EPROM-Bausteine. Mit S1 und S3 können die zwei Schnittstellen für optionale Module angewählt werden. Über CAS und WSMUX wird die Auswahl der zwei 32kB-RAM-Bausteine gesteuert. Die Steuerung erfolgt über die internen Steuersignale S1 und S2.

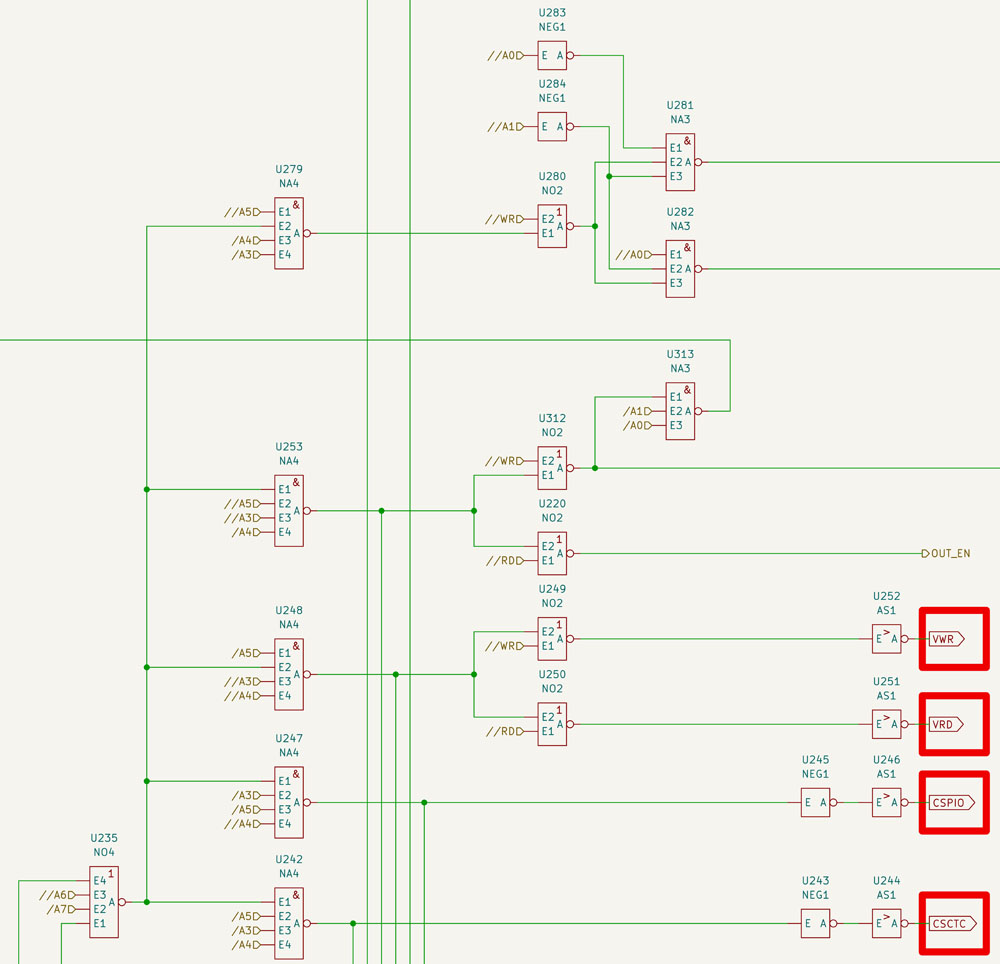

Der zweite Funktionsblock erzeugt eine ganze Reihe von Steuersignalen basierend auf den Adressleitungen und den Steuersignalen des U880. Zusätzlich wird der Interruptausgang des PIO-Bausteins ausgewertet. Direkt ausgegeben werden das Lese- und das Schreibsignal für die Grafikeinheit, die gleichzeitig als Auswahlsignal dienen. Ebenfalls direkt ausgegeben werden die Auswahlsignale für PIO und CTC. Das Signal DIR definiert die Flussrichtung der Daten-Transceiver an den Steckern für die optionalen Module. Über das WAIT-Signal wird dem Prozessor signalisiert, wann die adressierte Ressource verfügbar ist.

Der rechte Funktionsblock erzeugt außerdem einige interne Steuersignale. Eines davon ermöglicht es Daten auf den Datenbus zu legen. Über weitere Steuersignale können Daten in die internen Register übernommen werden. Im Referat aus dem Mikroelektronik-Bauelemente-Symposium werden zwei der Register als Port A und Port C bezeichnet. Port A wird parallel beschrieben. Port C kann man über zwei Steuersignale parallel oder seriell beschrieben. Der integrierte Soundgenerator besitzt sehr umfangreiche Konfigurationsmöglichkeiten. Über ein Steuersignal wird dort das zu beschreibende Register ausgewählt. Mit einem zweiten Steuersignal kann man dieses Register dann beschreiben.

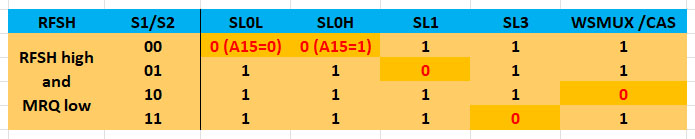

Die Auswahl der Steuersignale SL0L, SL0H, SL1, SL3, WSMUX und CAS erfolgt über eine Verknüpfung der internen Steuersignale S1 und S2 mit den Steuersignalen des Prozessors. S0L und SL0H sind zusätzlich abhängig vom Adressbit A15.

WSMUX und CAS besitzen zusätzlich Flip-Flops, die dafür sorgen, dass die Adresse des Prozessors in Zeilen- und Spaltenauswahl aufgeteilt wird. Wird MRQ aktiv, so übernimmt der RAM die Hälfte der Adresse sofort als Zeilenauswahl. Ist der RAM ausgewählt, dann sorgt die Schaltung im U1525FC007 dafür, dass mit WSMUX die zweite Hälfte der Adresse zum RAM durchgeschaltet wird und in der Folge mit CAS dieser Anteil als Spaltenadresse übernommen wird.

Es erscheint auf den ersten Blick eigenartig, dass die Zeilenauswahl im RAM immer erfolgt, auch wenn der RAM gar nicht ausgewählt ist. Diese Transparenz ist notwendig, damit der Refresh des DRAMs erfolgen kann, die der U880 wie der Z80 automatisch durchführt. Da der DRAM erst mit einer Spaltenadresse Daten auf dem Bus ausgibt, führt alleine das Anwählen einer Zeilenadresse noch nicht zu einer Buskollision.

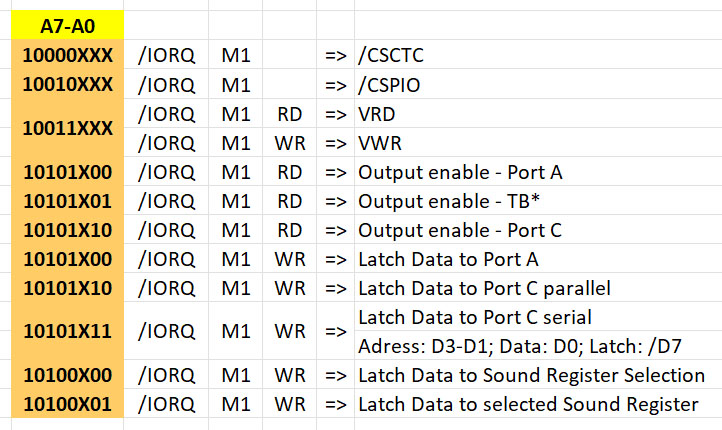

Die Dekodierung der Steuersignale ist recht übersichtlich. Die Verknüpfungen der Adressen mit den Steuersignalen lassen sich gut extrahieren. Während MRQ einen Zugriff auf den Speicherbereich anzeigt, kommuniziert der Prozessor mit IORQ einen Zugriff auf eine periphere Schaltung. Das Signal M1 gehört zu einem solchen Interrupt-Zyklus.

Hier ist die Erzeugung des DIR- und des MWAIT-Signals zu sehen. Zwischen dem Start einer Speicherinteraktion und der positiven Rückmeldung über MWAIT fügt der U1525FC007 lediglich eine feste Verzögerung ein.

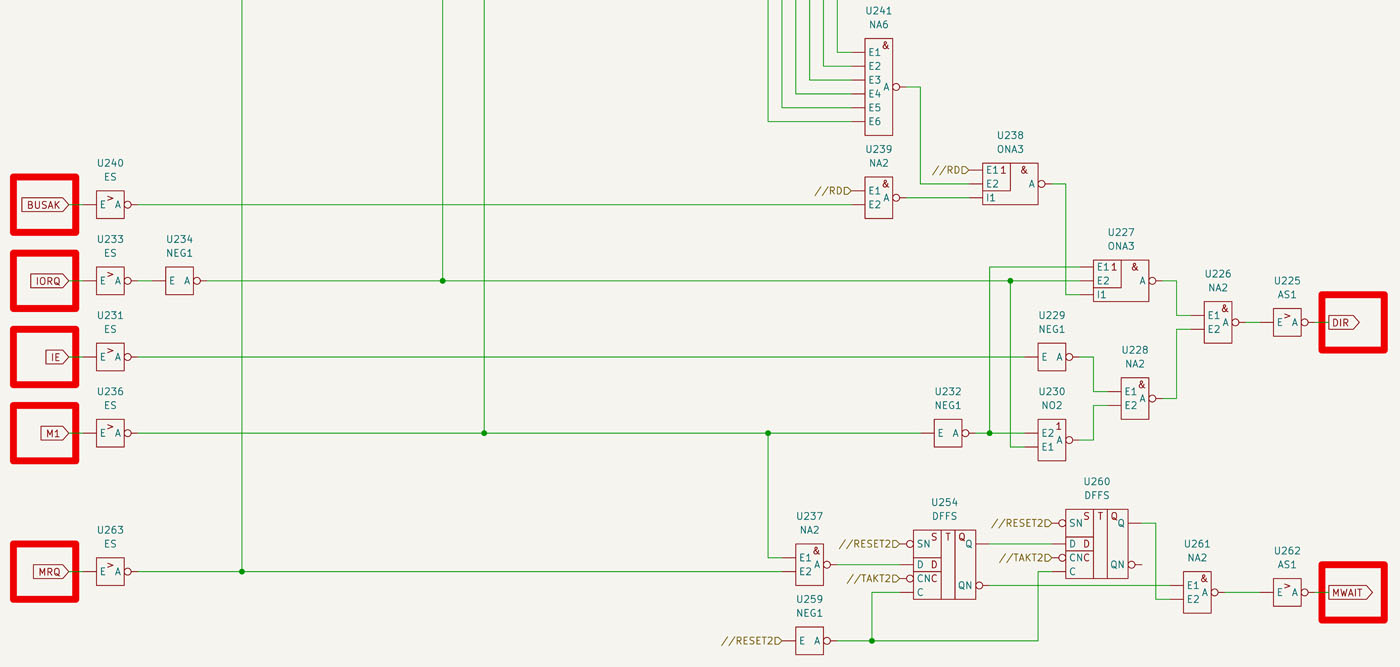

Mit Hilfe des Registers Port A kann man die Adressierung der Speicherbereiche konfigurieren. Mit dem zugehörigen Steuersignal wird der aktuelle Wert des Datenbusses im Port A gespeichert. Den abgelegten Wert kann man auch wieder auslesen.

Je nachdem welche der acht Bits im Port A gesetzt sind, benötigt man andere Kombinationen der Adressbits 14 und 15, um die Steuersignale S1 und S2 zu aktivieren. Diverse Kombinationen sind nicht sinnvoll. Man setzt höchstwahrscheinlich immer nur zwei Bits im Port A. Kombinationen die S1 und S2 mit der gleichen Adresskombination aktivieren scheinen ebenfalls kaum sinnvoll und sind hier grau hinterlegt.

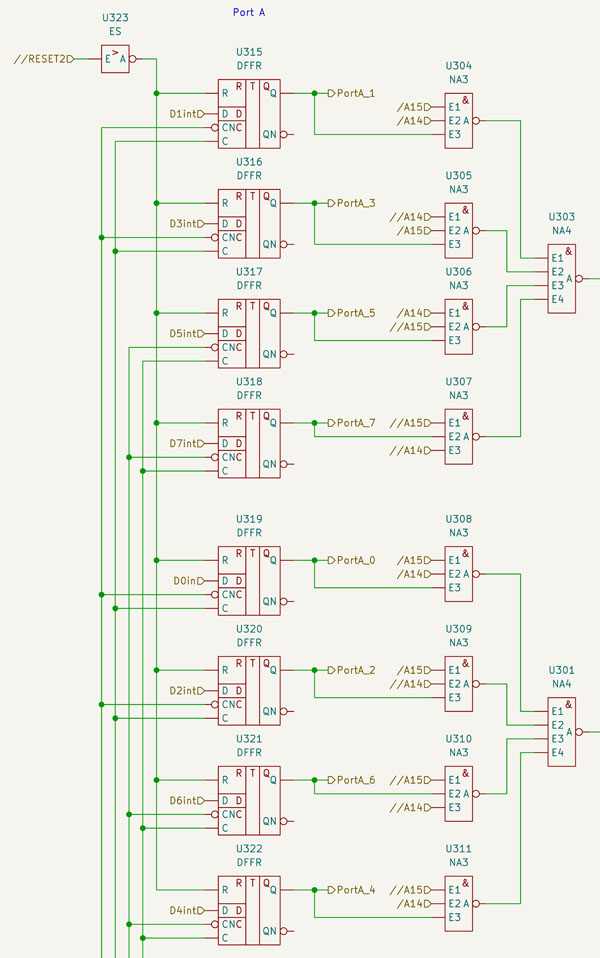

Das Register Port A ist mit DFFR-Flip-Flops aufgebaut.

Um einen Speicherbereich auswählen zu können, muss RFSH einen High-Pegel und MRQ einen Low-Pegel führen. Das bedeutet, dass aktuell kein Refresh-Zyklus aktiv sein darf und der Prozessor auf einen Speicher zugreifen will. Mit den Steuersignalkombinationen 01 und 11 kann man die Schnittstellen der optionalen Einsteckkarten auswählen (SL1/SL3). 10 aktiviert WSMUX / CAS und damit die Schnittstelle der RAM-Bausteine.

SL0L und SL0H, die beidem EPROM-Bausteine werden nur aktiv, wenn im Register Port A kein Bit gesetzt ist. Das erscheint auf den ersten Blick unlogisch, da in diesem Zustand kein anderer Speicherbereich aktiviert werden kann. Es muss zuerst der Port A neu beschrieben werden. Diese Umsetzung hat aber den Vorteil, dass nach einem Reset ohne eine Initialisierung des SVG sofort auf die EPROMs zugegriffen werden kann, wo sich das Programm befindet. Durch die Verknüpfung mit den Adressbit 15 erscheint dem Prozessor die Ansteuerung des EPROM initial vollständig transparent.

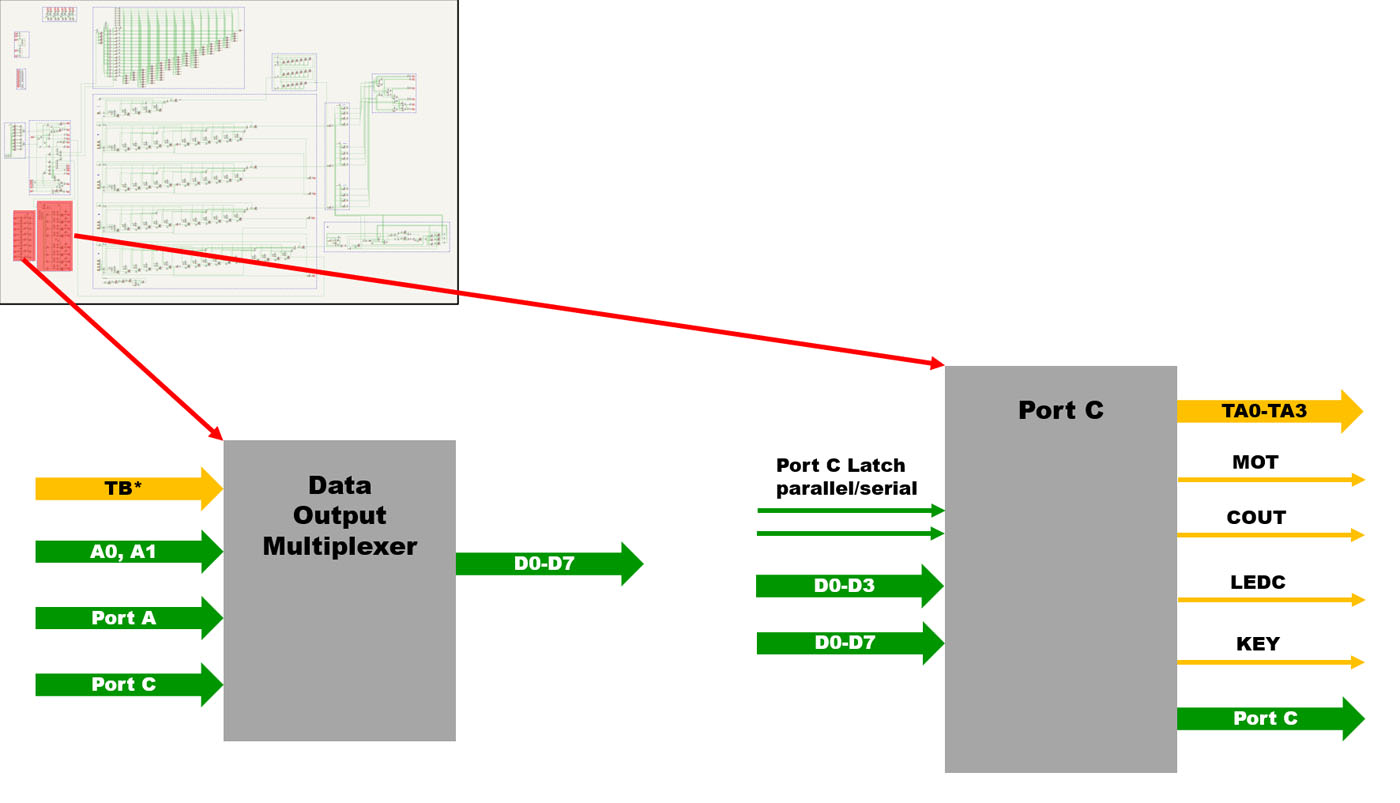

Ein Multiplexer ermöglicht es verschiedene Daten auf den Datenbus zu legen. Eine Datenquelle sind die Eingänge TB*, die dem Prozessor zeigen welche Taste der Tastatur gedrückt ist. Alternativ können die Daten in den Registern Port A oder Port C auf den Datenbus gelegt werden. Über die Adressleitungen A0 und A1 wählt man eine der drei Datenquellen aus.

Das Datenregister Port C kann parallel oder seriell mit Daten geladen werden. Der Inhalt des Registers steuert die Zeilenauswahl der Tastaturlogik (TA*), den Kassettenrekorder, die Caps-Lock-LED und das Signal für den Tastenton.

Hier ist ein Ausschnitt des Multiplexers zu sehen.

Das Register Port C ist mit DFFRS-Flip-Flops aufgebaut. Über die D-Eingänge kann man das Register parallel laden. Das serielle Laden erfolgt über die Set- und Reset-Eingänge. Die dahinter liegende Logik wertet den Pegel des Datenbits 0 aus. Welches Bit des Registers beschrieben werden soll definieren die Datenbits 1 bis 3.

Der Soundgenerator belegt im U1525FC007 sehr viel Fläche. Die Konfigurationsregister haben einen großen Anteil daran. Es handelt sich um 16 Register mit insgesamt 83 Bits.

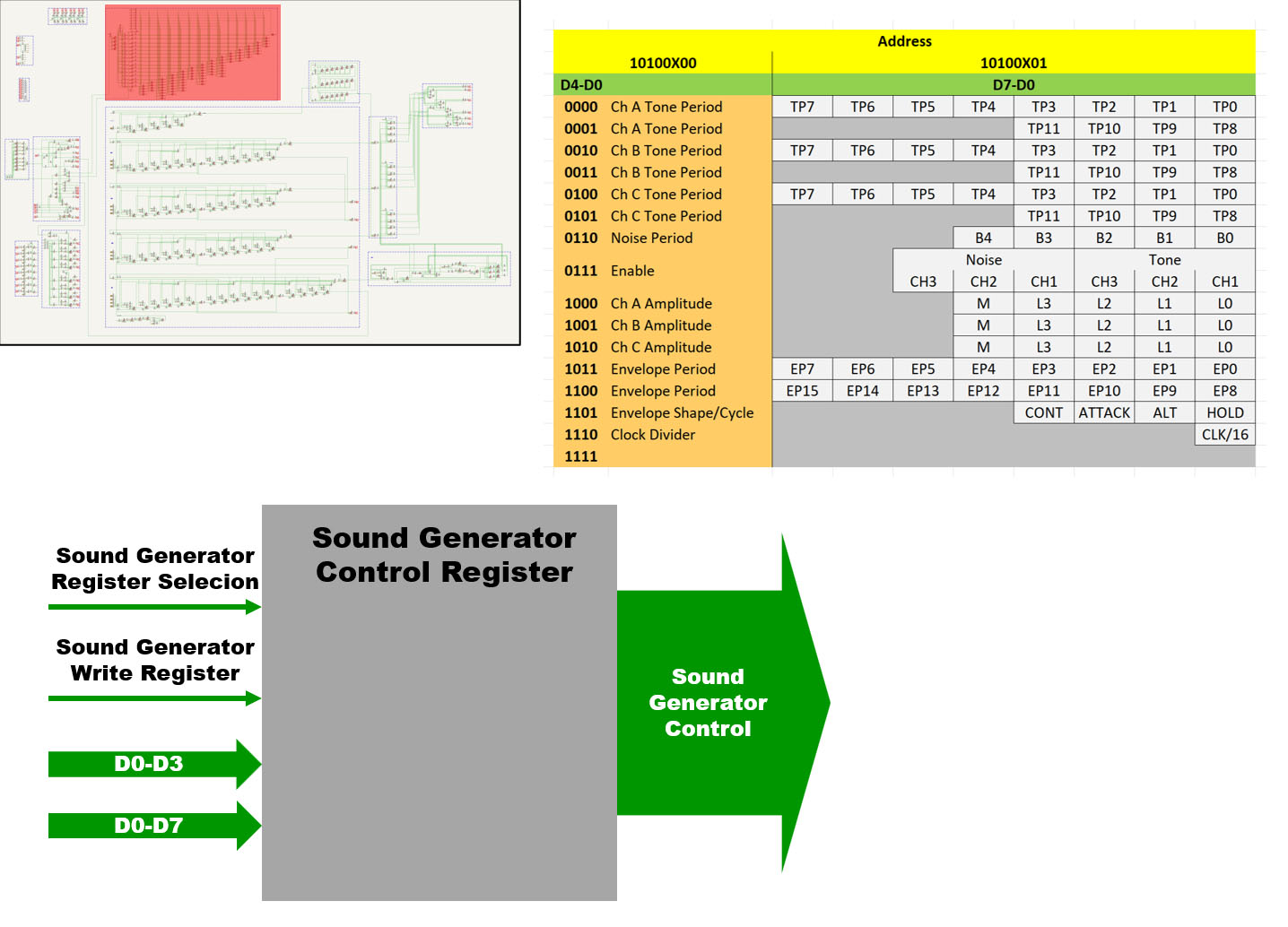

Der im U1525FC007 integrierte Soundgenerator funktioniert sehr ähnlich wie der Soundgenerator AY-3-8910 von General Instrument. Sogar die Steuerregister sind gleich aufgebaut und angeordnet. Im U1525FC007 fehlen lediglich die Schnittstellen Port A und Port B und der Mischer am Ausgang mischt die Signale zu einem einzelnen Kanal. Außerdem ist der Digital-Analog-Wandler extern angeordnet.

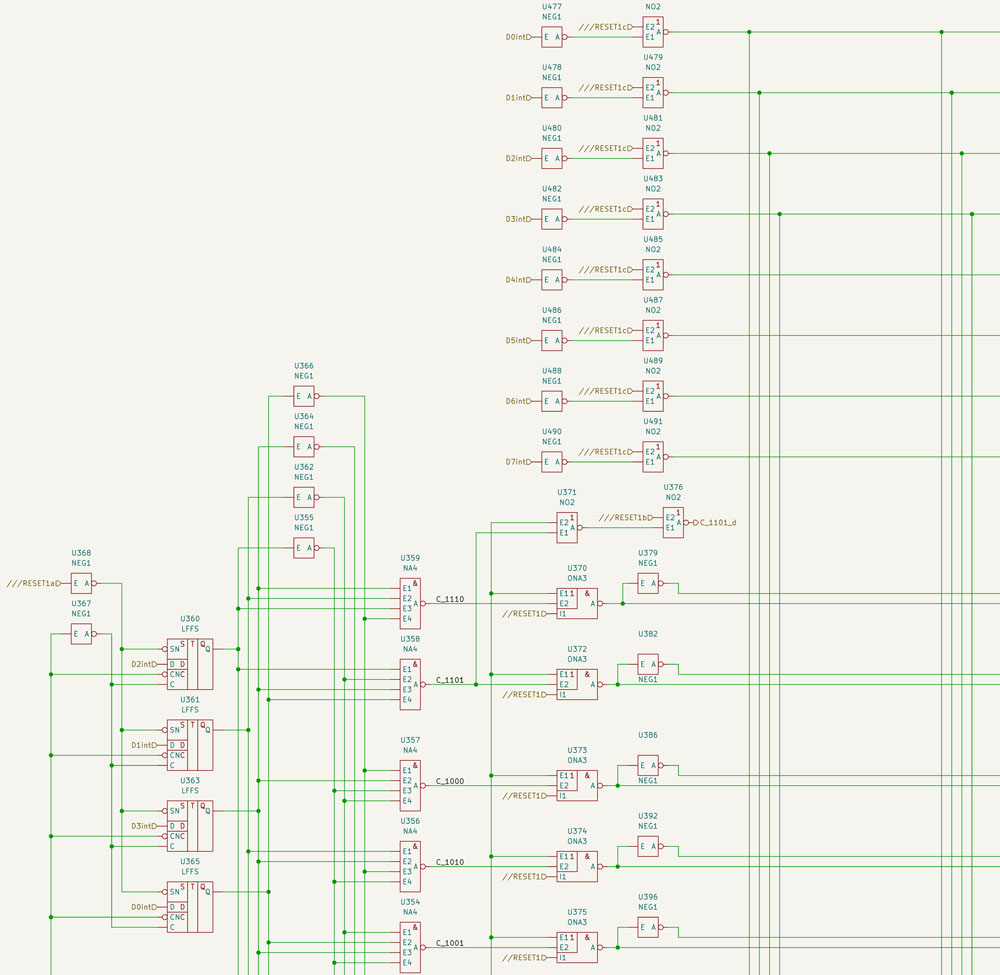

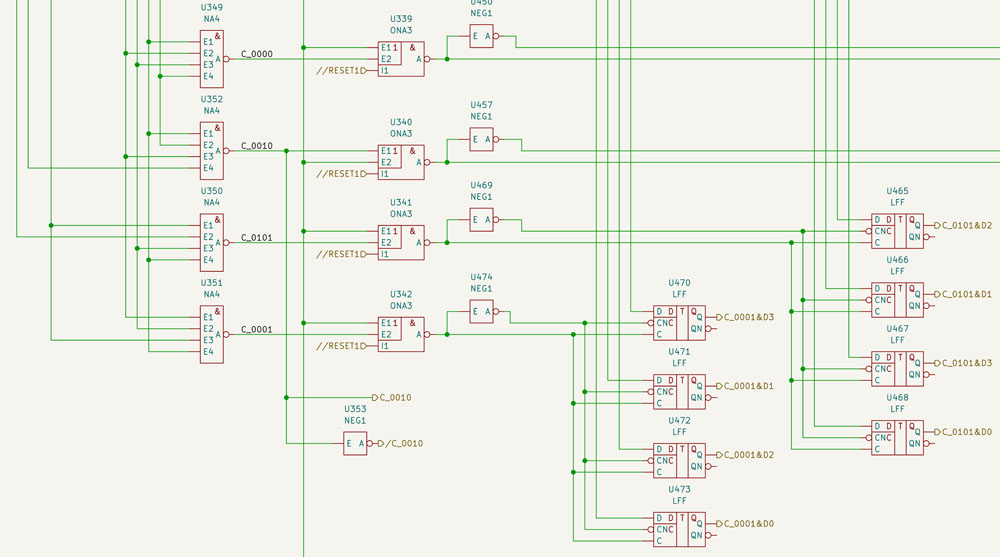

Vier LFFS-Flip-Flops wählen mit den ersten vier Bits des Datenbusses eine Zeile des Konfigurationsregisters für den Soundgenerator aus.

Die LFFS-Flip-Flops erzeugen mit etwas zusätzlicher Logik die Taktsignale für LFF-Flip-Flops, die die Konfigurationsregister selbst darstellen. Die Eingänge sind mit dem Datenbus verbunden. Eine Adresse stößt die LFFS-Flip-Flops und damit die Zeilenauswahl an. Eine weitere Adresse lässt dann die LFF-Flip-Flops die Daten auf dem Datenbus übernehmen.

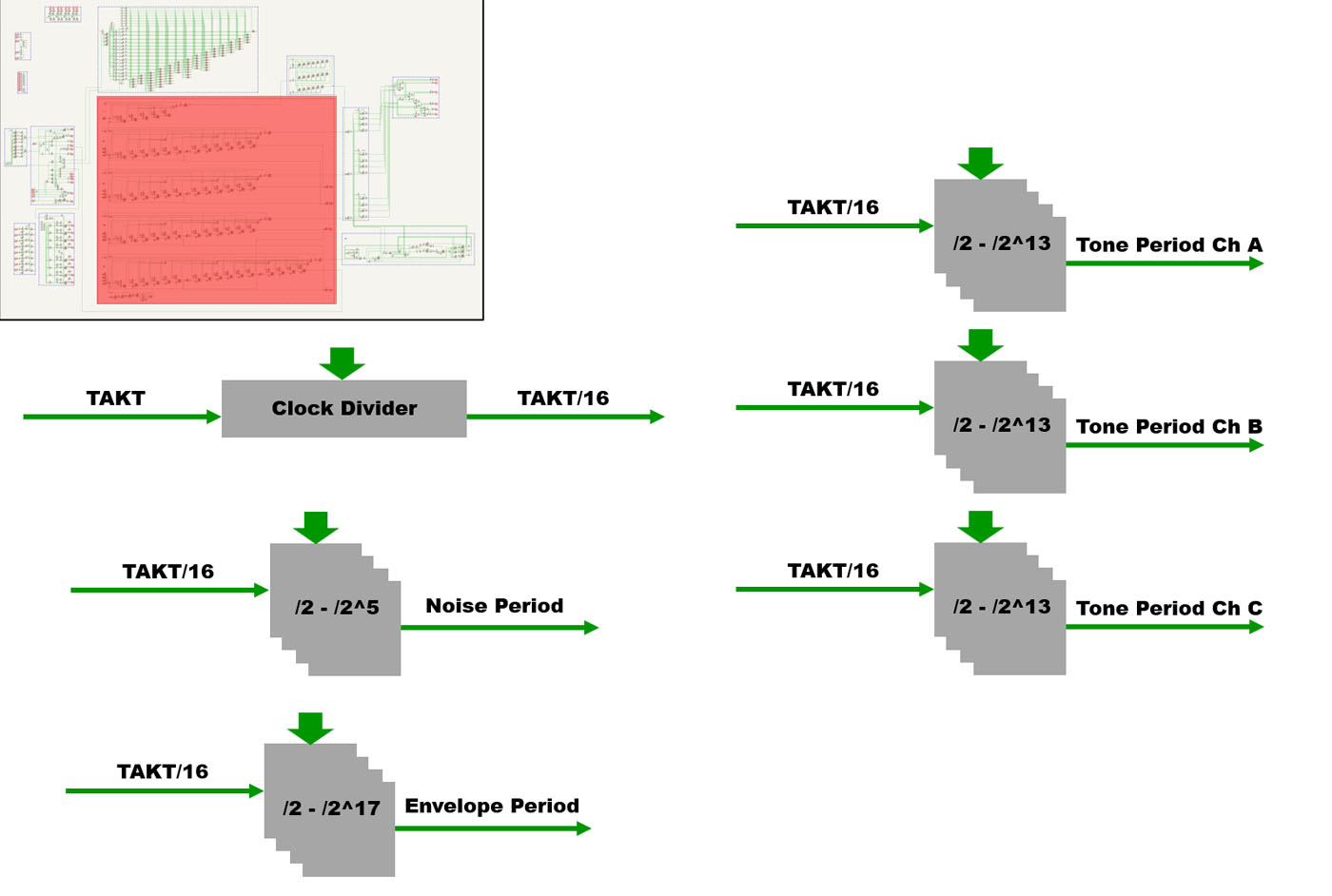

Grundlage des Soundgenerators bilden sechs Taktteiler. Der 3,75MHz-Grundtakt des A5105 kann zuerst mit einem Faktor 16 heruntergeteilt werden, bevor dieser dann als Arbeitstakt zu den fünf anderen Taktteilern geleitet wird.

Ein Taktteiler definiert die Grundfrequenz des Rauschgenerators und kann den Arbeitstakt um 2 bis 2^5 herunterteilen. Ein weiterer Taktteiler erzeugt den Takt für die Amplitudenmodulation mit einem Teilerfaktor von 2 bis 2^17. Die drei Töne, die der Soundgenerator erzeugen kann, werden über drei Taktteiler mit jeweils einem Teilerfaktor von 2 bis 2^13 erzeugt. So ergibt sich mit Vorteiler ein Frequenzbereich von 28Hz bis 117kHz.

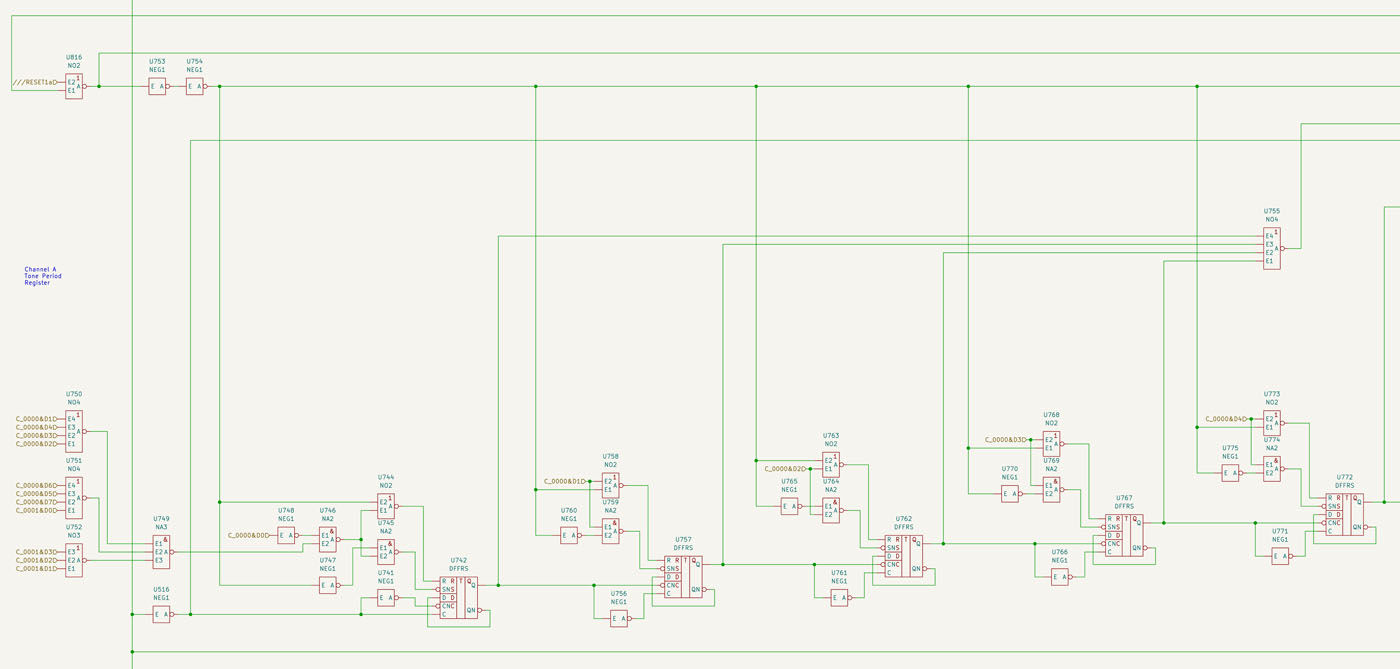

Die Taktteiler basieren auf DFFRS-Flip-Flops. Ihre genaue Funktionsweise erschließt sich erst auf den zweiten Blick. Die Schaltung nimmt nicht nur auf dem Schaltplan sehr viel Fläche ein, sondern auch auf dem Die.

Die Schnittstellen PM, OP0, OP1, OP2 und OP3 scheinen Diagnosezwecken zu dienen. Die Frequenzteiler der Kanäle A, B, C und des Hüllkurvengenerator sind in Sechsergruppen und eine Vierergruppe aufgeteilt. So ergeben sich neun Bereiche, die einzeln ausgelesen werden können. Das Auswahlsignal für das Register 0010 schaltet dazu die vier OP-Ausgänge um, was es ermöglicht, acht der neun Gruppen zu erreichen. Mit dem Eingang PM kann man die Gruppen voneinander isolieren und mit dem gleichen Taktsignal speisen. Außerdem schaltet das PM-Signal die verbliebene Gruppe auf den S0H-Ausgang.

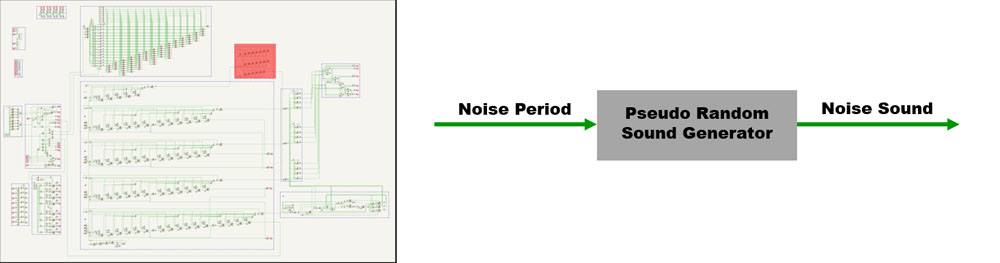

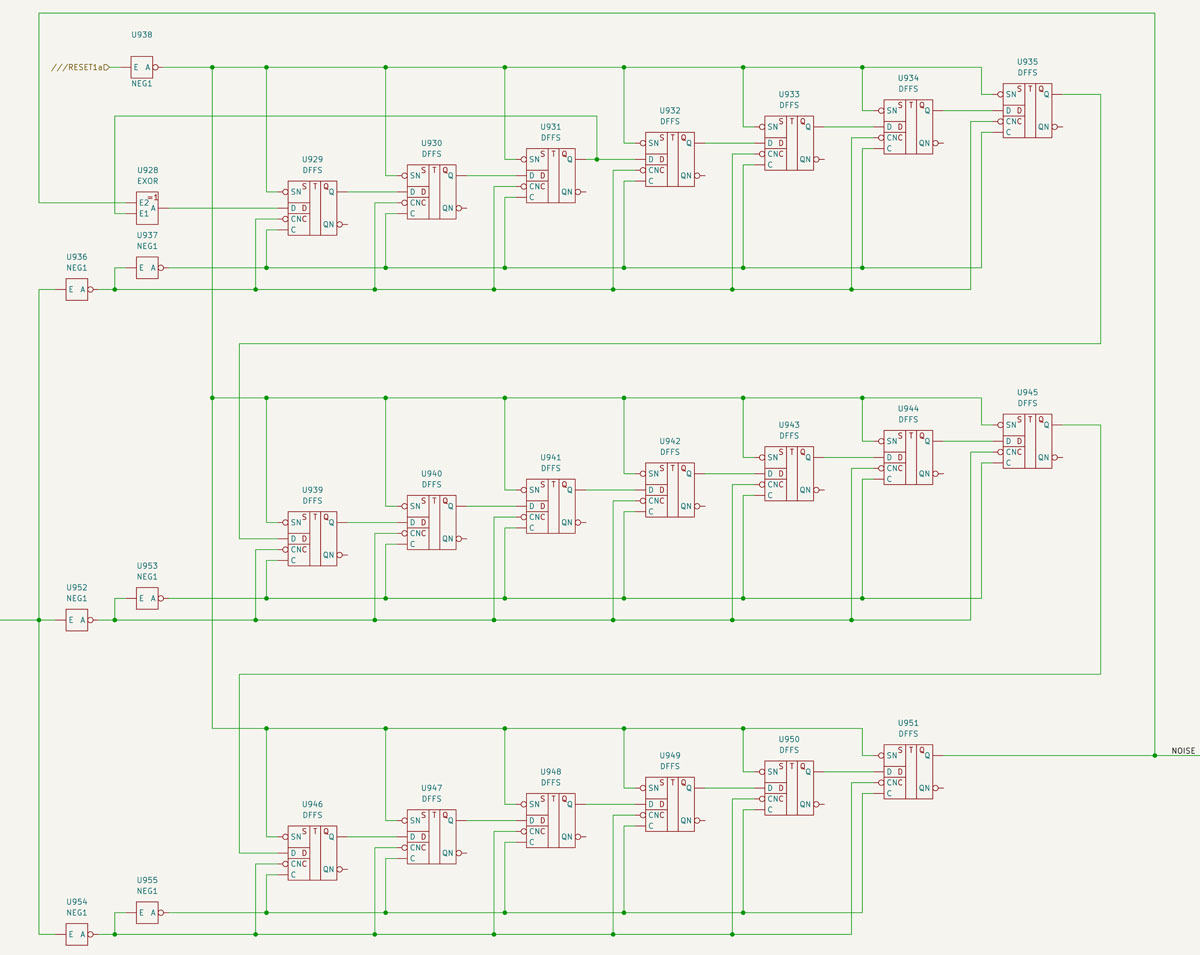

Der Soundgenerator besitzt einen Rauschgenerator, der mit der heruntergeteilten Taktfrequenz arbeitet.

Es handelt sich natürlich nur um einen Pseudo-Rauschgenerator, der kein wirklich zufälliges Rauschen erzeugt. Es sind 20 DFFS-Flip-Flops hintereinander geschaltet. Das Eingangssignal wird von einem EXOR-Gatter generiert, das das aktuelle Ausgangssignal mit dem Ausgangssignal des dritten Flip-Flops verknüpft. So ergibt sich ein pseudo zufälliges Ausgangssignal.

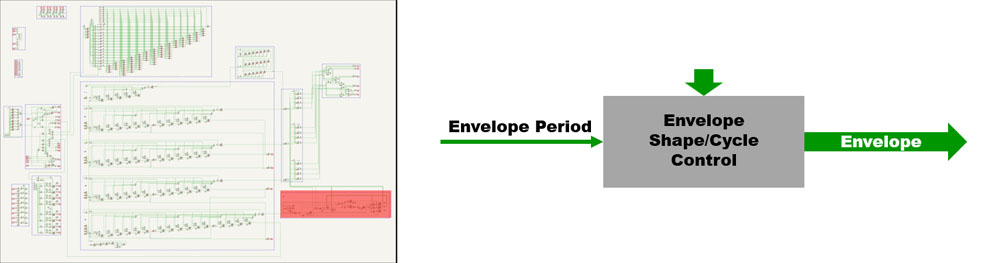

Mit einem weiteren Schaltungsteil kann man die Hüllkurve, also die Amplitudenmodulation des Ausgangssignals definieren. Grundlage bildet auch hier der heruntergeteilte Arbeitstakt.

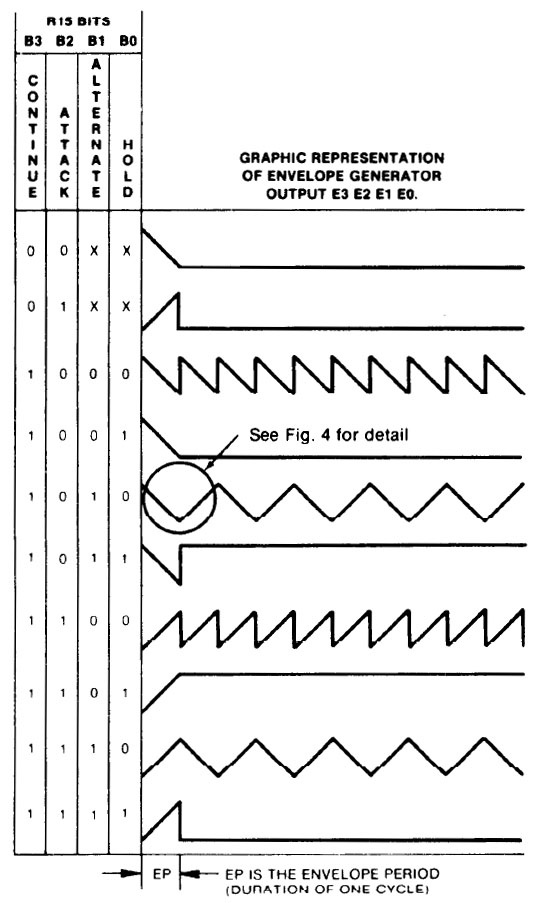

Das Datenblatt des AY-3-8910 zeigt welche Hüllkurven erzeugt werden können. Die Schaltung selbst ist eher unübersichtlich. Sie speist vier Datenleitungen, deren Wert die aktuelle Amplitude darstellt.

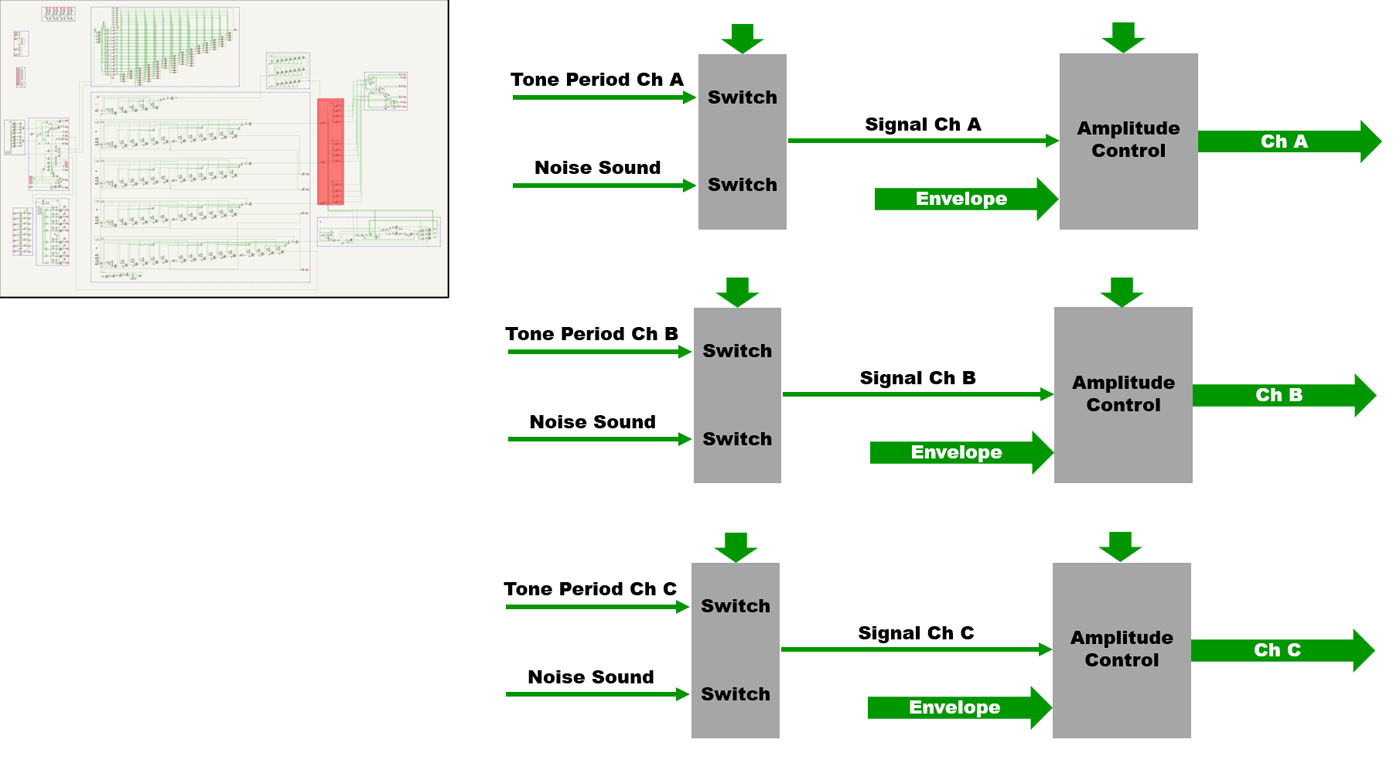

Über das Konfigurationsregister ist letztlich definiert, welcher der drei Töne weitergeleitet wird. Man kann jeden Ton mit dem Rauschsignal verknüpfen oder nur das Rauschsignal weiterleiten. Die drei Signale durchlaufen dann eine Amplitudenregelung, die über das Konfigurationsregister eingestellt werden kann und zusätzlich mit der generierten Hüllfunktion moduliert wird.

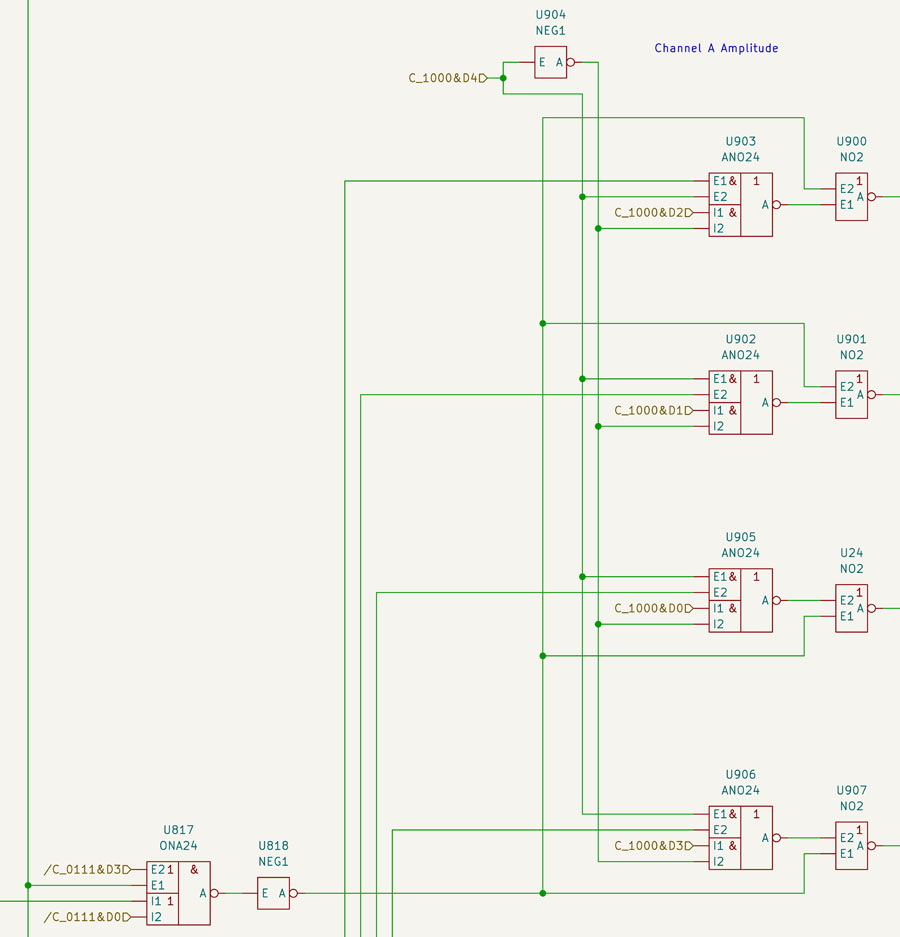

Hier ist die Schaltung für einen Kanal zu sehen. Im Gatter U817 wird der Ton oder das Rauschsignal oder beide Signale ausgewählt. Die NOR-Gatter ganz rechts leiten das Signal weiter, wenn die davor liegenden ANO24-Gatter das zulassen. In diesen Gattern werden die Amplitudenkonfiguration und die Hüllkurveninformation verknüpft. Die vier Ausgänge führen alle die gleichen Signale, wenn sie aktiv sind. Abhängig davon welche der Ausgänge aktiv sind, ergeben sich später unterschiedliche Amplituden.

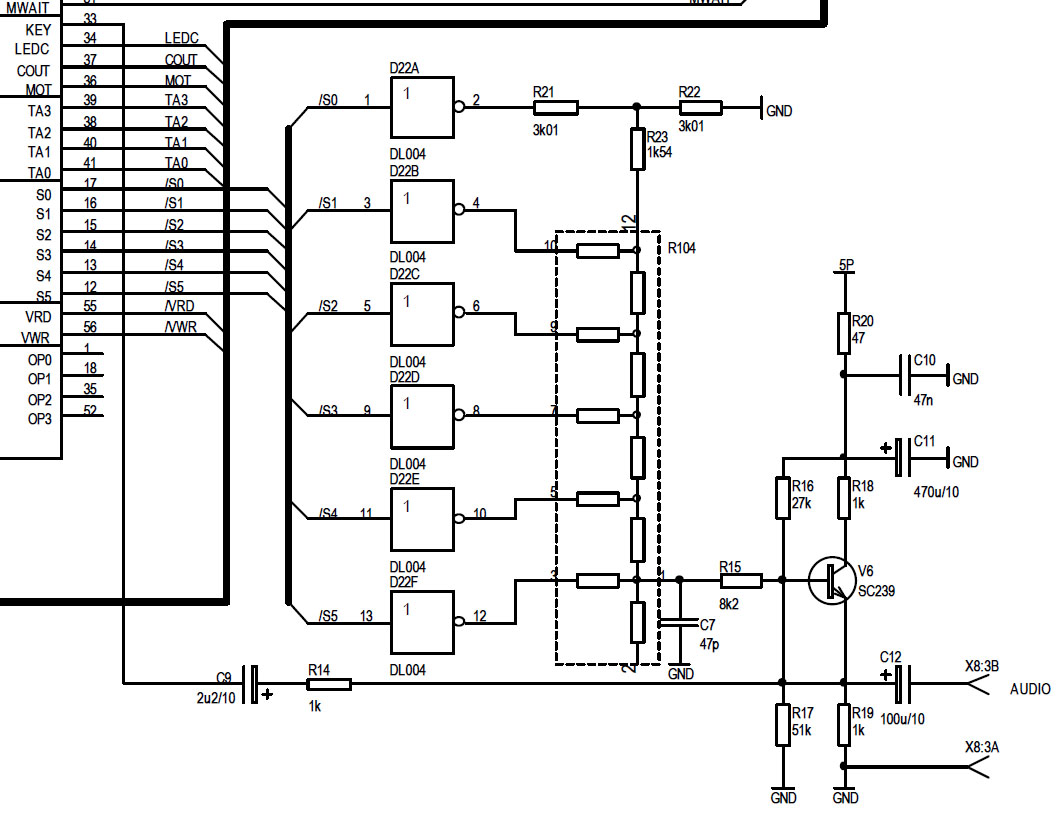

Die Funktionsweise der Soundausgabe wird klarer, wenn man einen Blick auf den Schaltplan des A5105 wirft. Dort stellt eine Widerstandskette einen diskreten Digital-Analog-Wandler dar. Jeder S-Ausgang bedient einen Inverter, der je nach Anknüpfungspunkt den Ausgangspegel stärker oder schwächer beeinflusst.

Bevor das Soundsignal ausgegeben werden kann, verknüpft ein Mischer die drei erzeugten Kanäle.