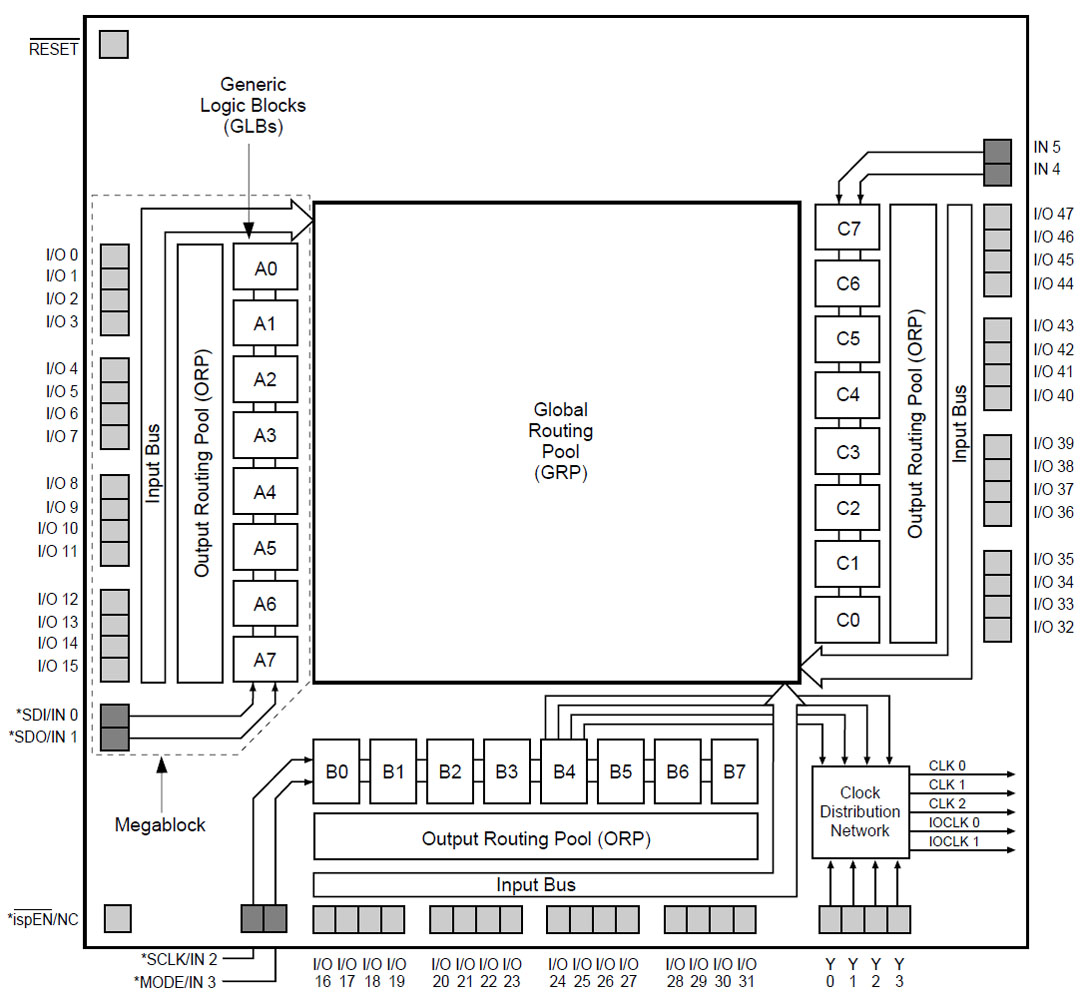

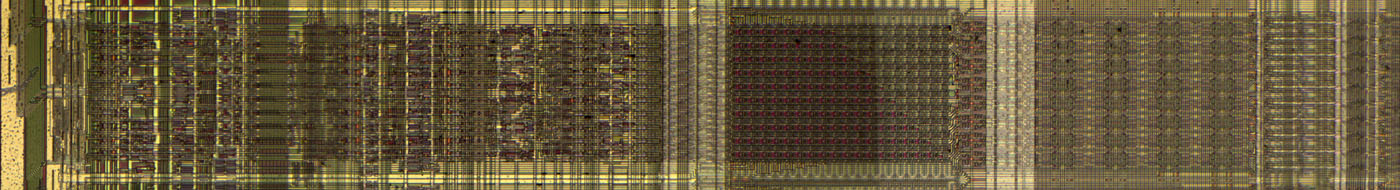

Der LSI1024 ist nach dem LSI1016 das nächst größere Modell dieser CPLD Reihe. Die Variante 1024 bietet 24 Logik Blöcke, 4000 Gates, 144 Register und 54 I/Os.

Der Aufbau des CPLDs ist grundsätzlich gleich wie beim LSI1016 ausgeführt. Der LSI1024 bietet allerdings drei Megablöcke. Außerdem steht der Taktaufbereitung ein zusätzlicher Pin zur Verfügung.

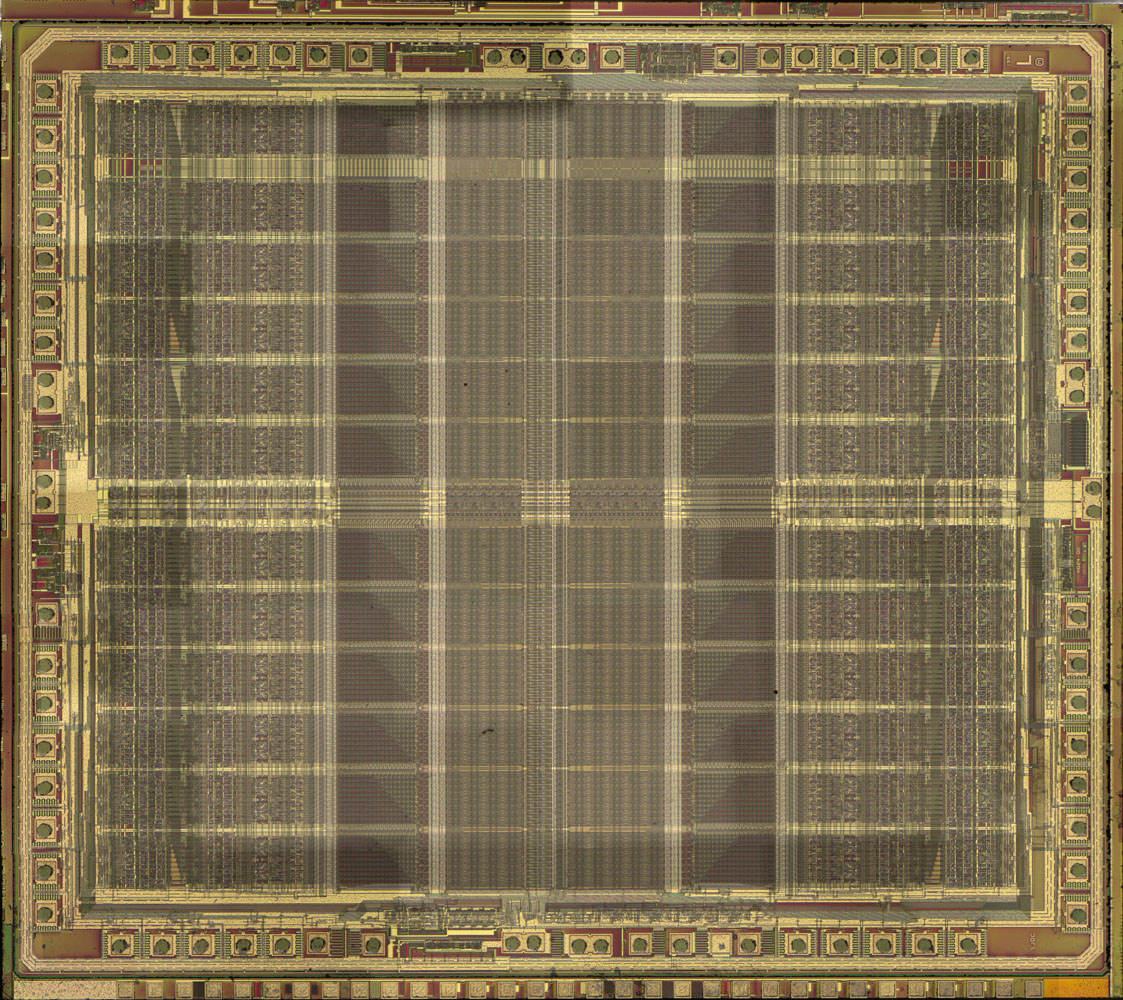

Die Abmessungen des Dies betragen 6,5mm x 5,8mm.

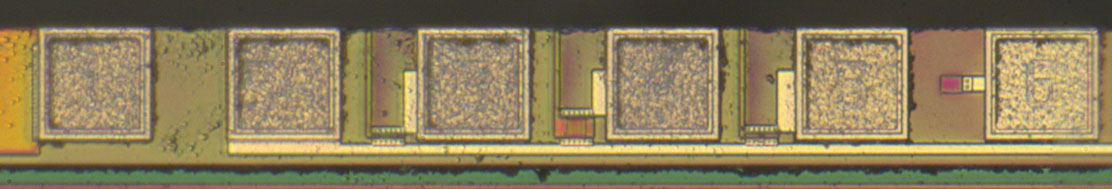

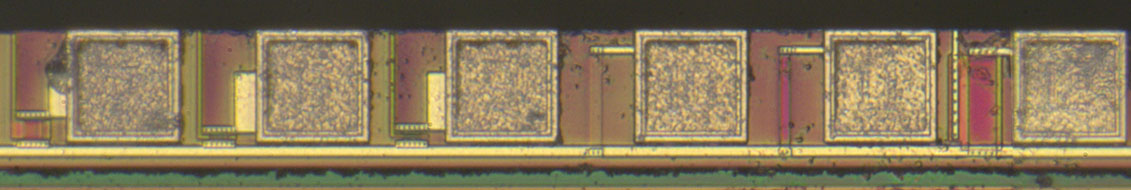

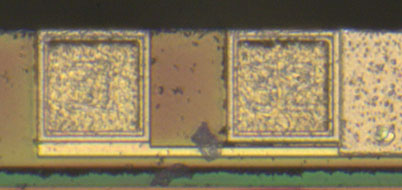

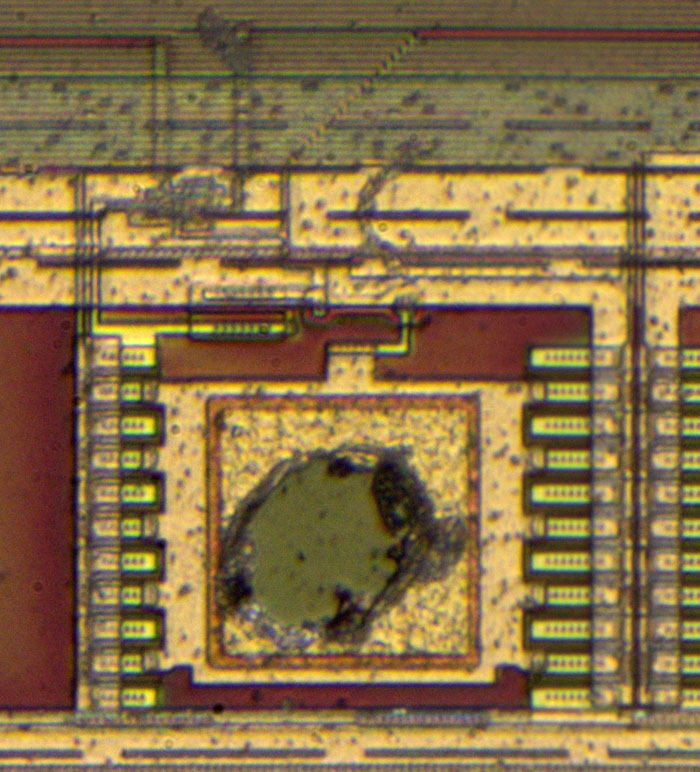

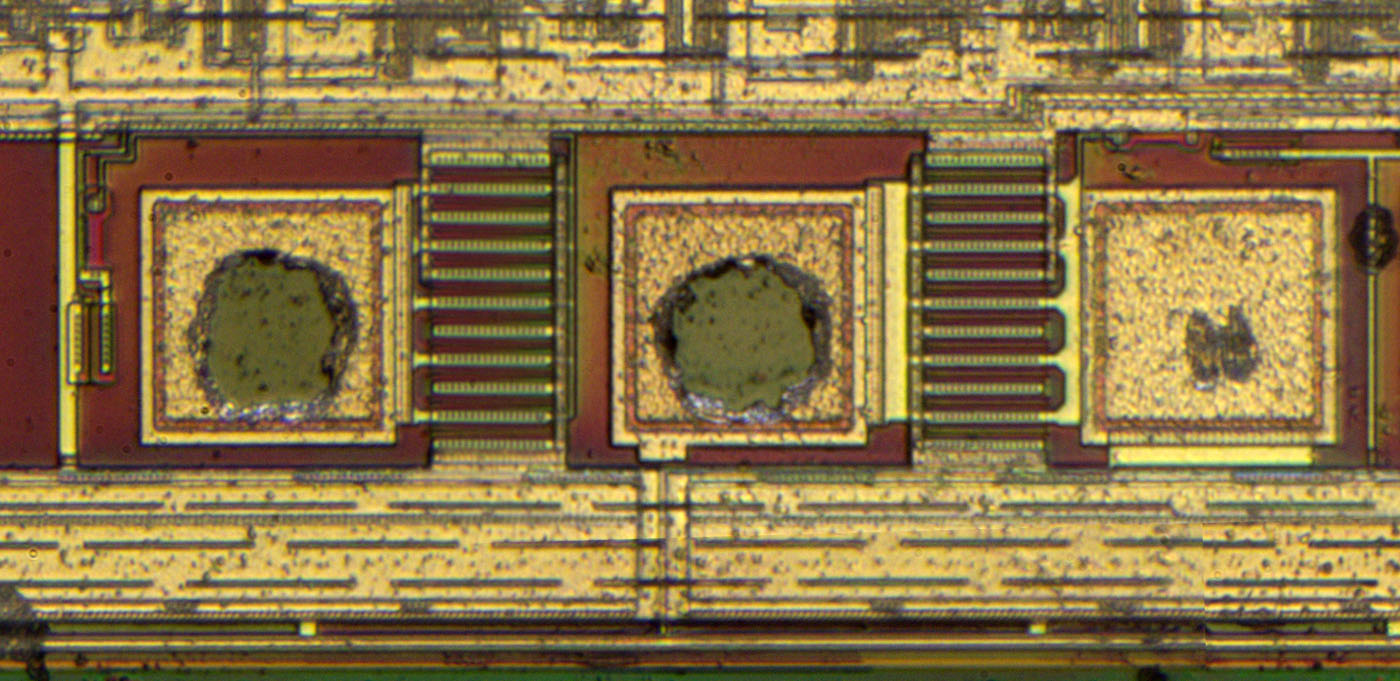

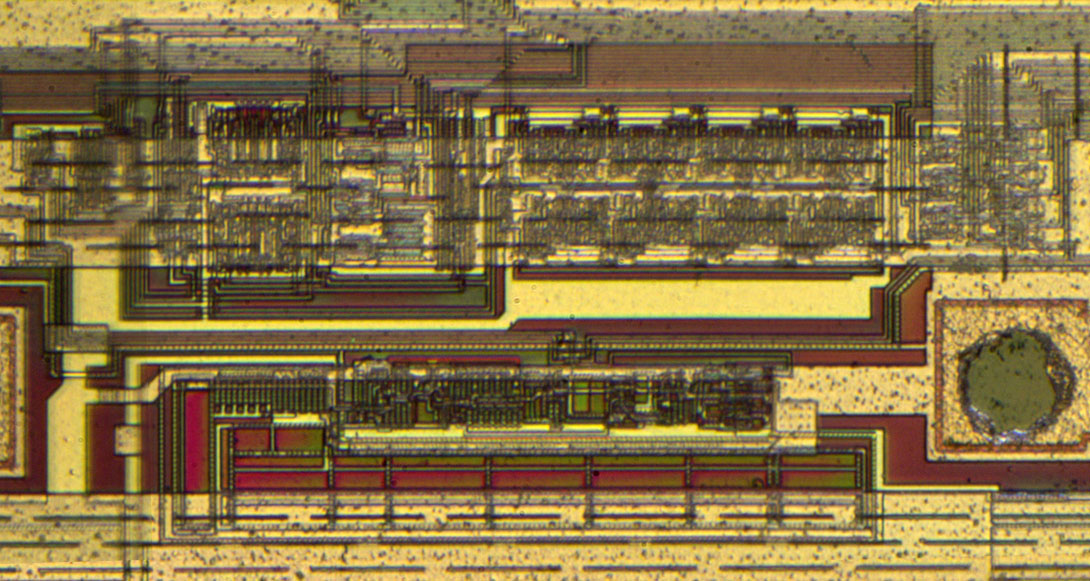

Im Bereich der unteren Frässtraße befinden sich 32 Testpads, die es ermöglichen diverse Strukturen zu vermessen.

In den Frässtraßen befinden sich aber auch mehrere komplexere Schaltungsteile.

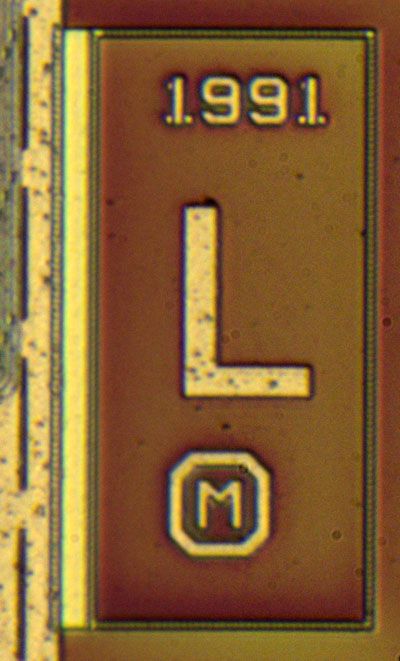

Das Design stammt aus dem Jahr 1991 und ist damit etwas älter als das Design des LSI1016.

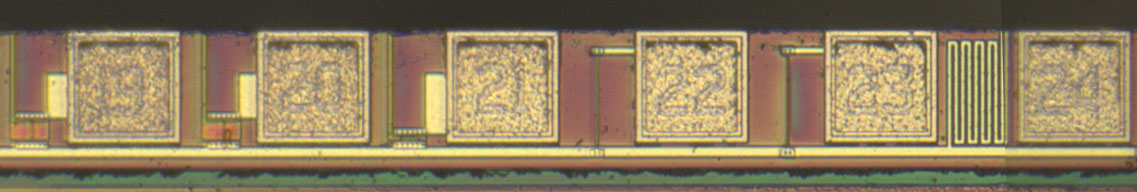

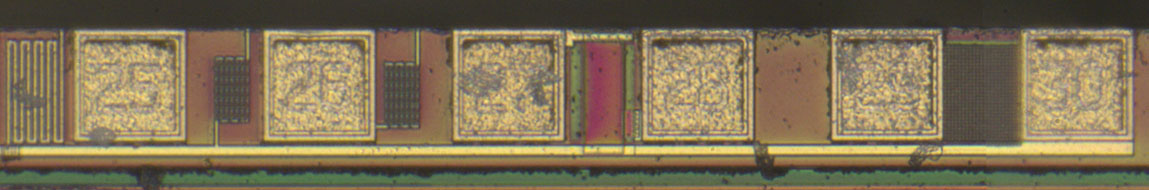

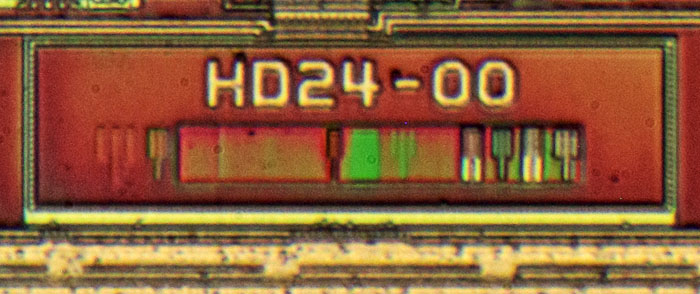

HD24 könnte die interne Bezeichnung des LSI1024 sein. 00 könnte für eine erste Revision stehen. In der unteren Reihe finden sich Teststrukturen, die die Abbildungsleistung der verschiedenen Masken erkennbar machen.

SJDC steht für das San Jose Design Center.

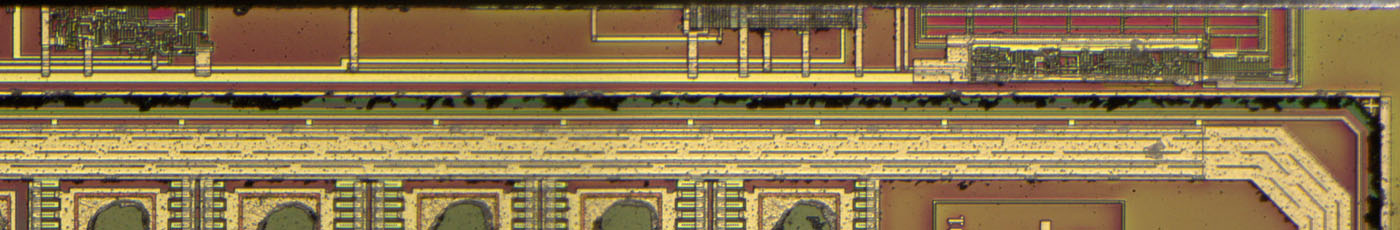

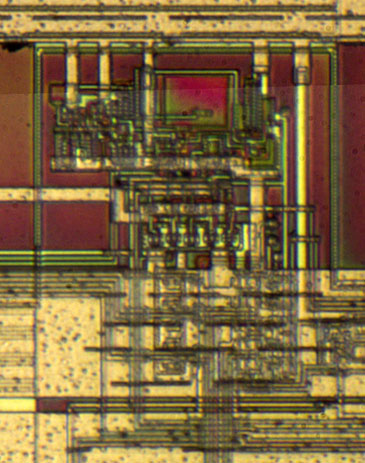

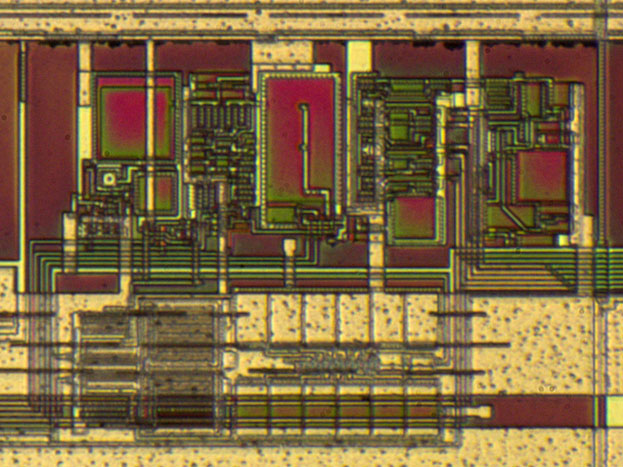

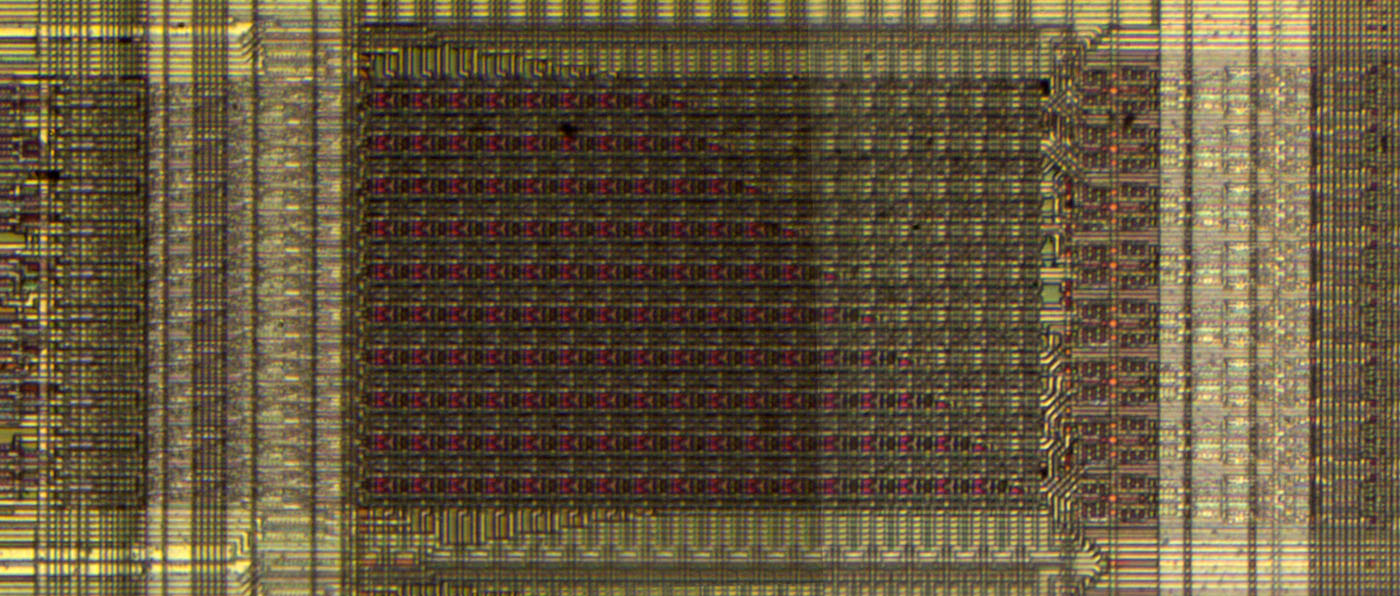

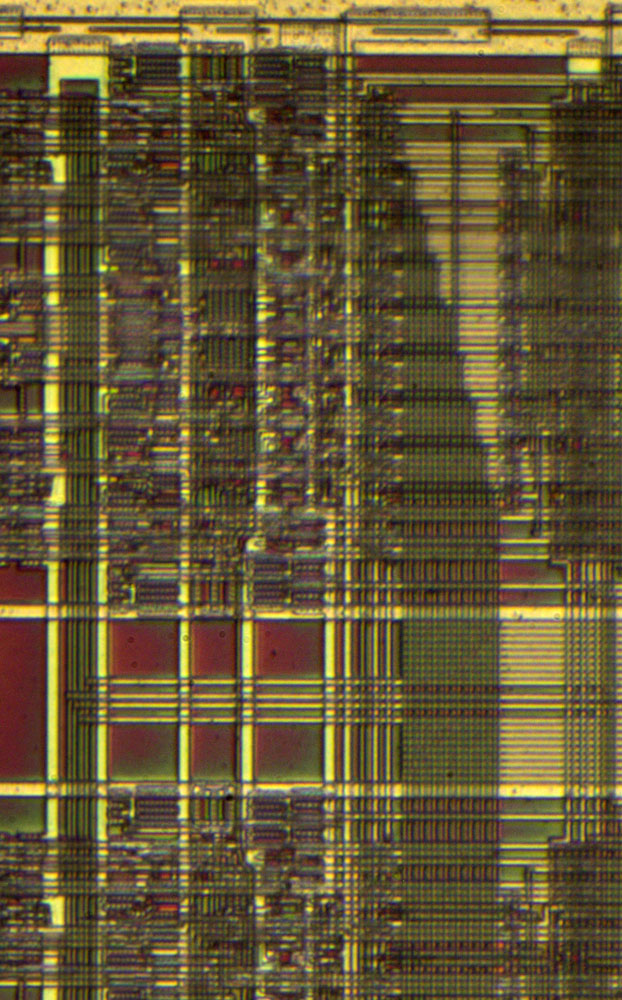

Die Beschaltung der Bondpads ist gut zu erkennen. Rechts und links befinden sich die großen Highside- und Lowside-Transistoren, wobei die rechte Seite etwas größer ausgeführt ist. An der oberen Kante sind die Schutzstrukturen des Eingangs platziert.

An der unteren Kante des Dies befindet sich ein ungenutztes Testpad. Das Bondpad, das unter anderem mit der Rahmenstruktur verbunden ist, scheint der Reset-Eingang zu sein.

Im Bereich der Bondpads befinden sich mehrere kleine Schaltungsteile.

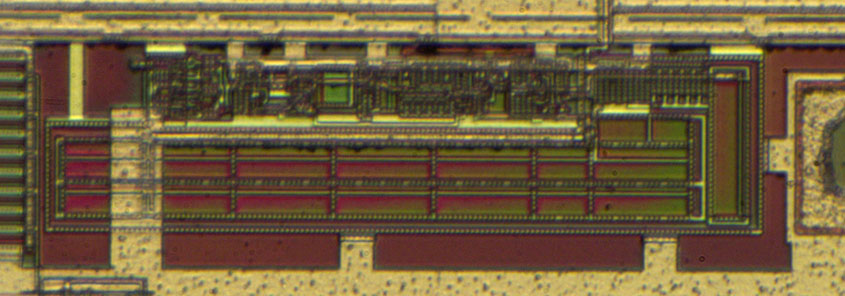

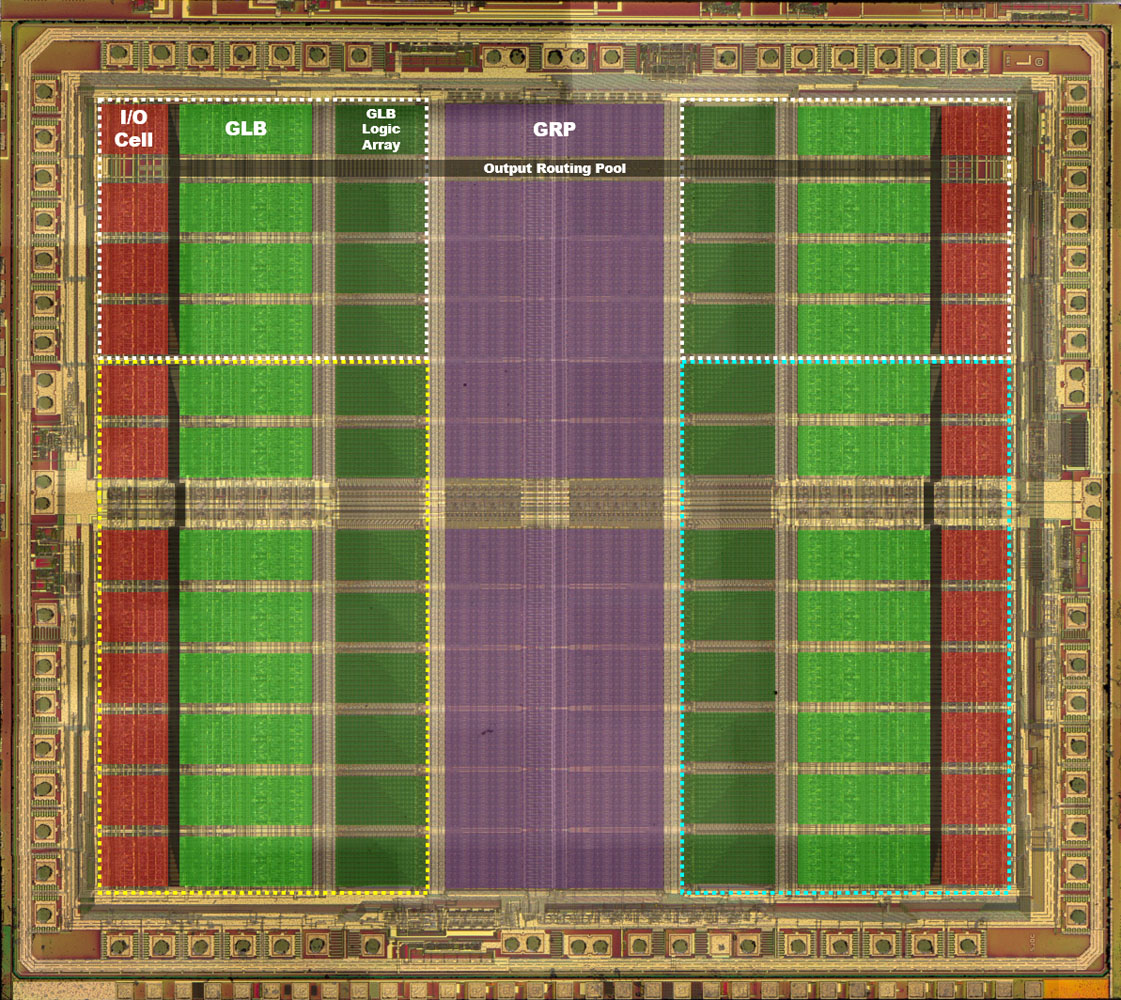

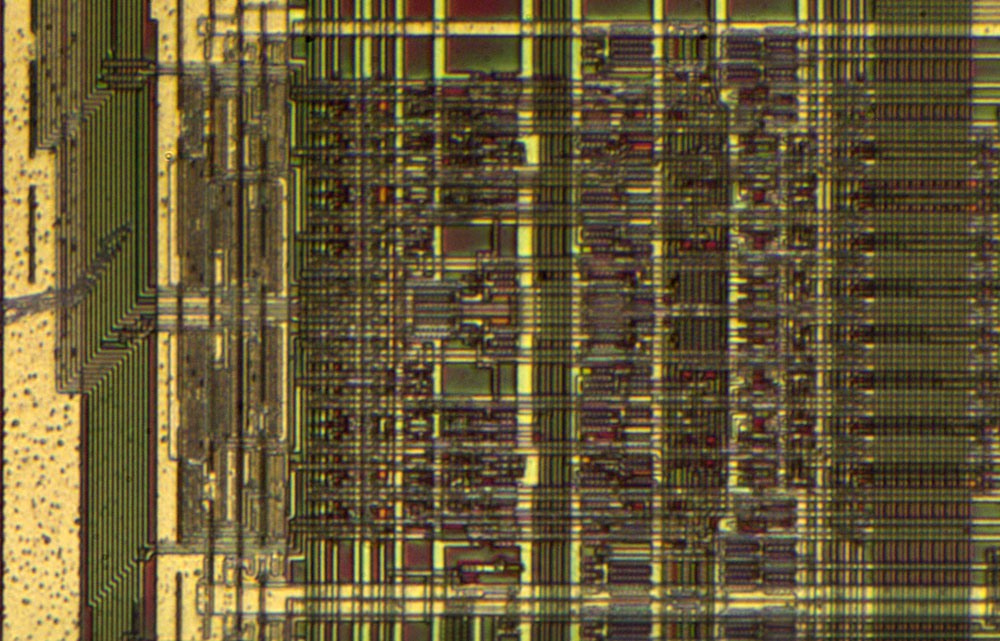

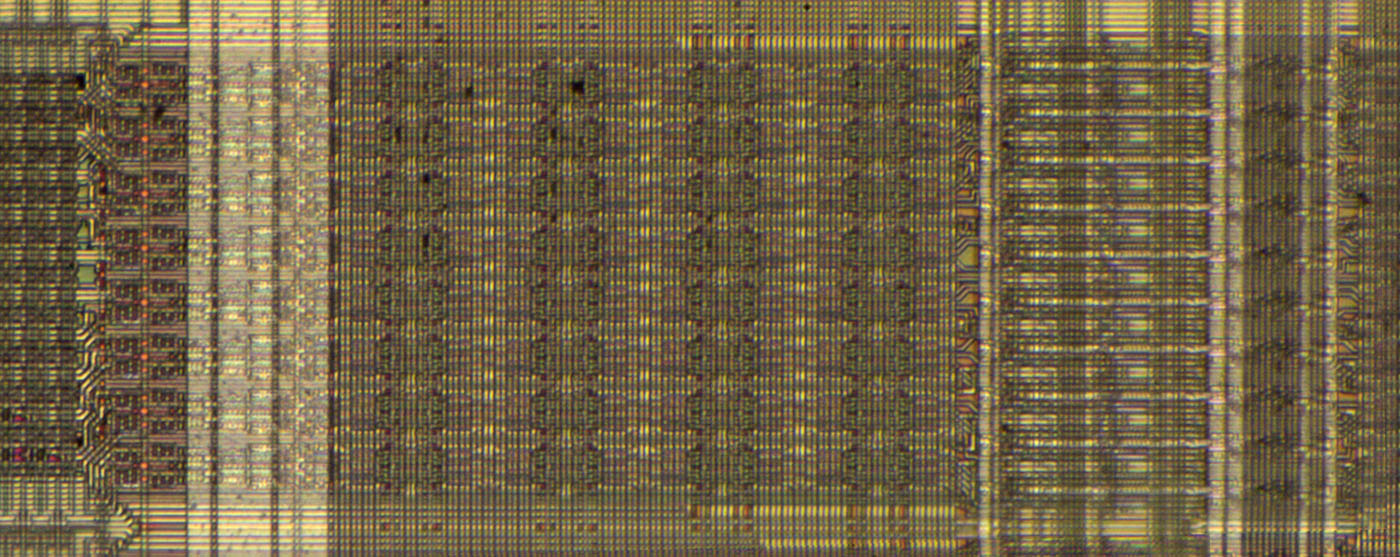

Den größten Teil des Dies nehmen die Logikblöcke ein. Der LSI1024 enthält drei sogenannten Megablöcke. Es wurde links und rechts jeweils ein Megablock integriert (gelb/türkis). Der dritte Megablock verteilt sich im oberen Bereich auf die beiden Seiten des Dies (weiß).

Die Megablöcke sind grundsätzlich genauso aufgebaut wie im LSI1016. Sie beinhalten jeweils acht Global-Logic-Blöcke (hellgrün) und acht kleine Logic Arrays (dunkelgrün). Die acht roten Blöcke müssen jeweils zwei I/O-Zellen enthalten. Mittig befindet sich der Global Routing Pool (lila).

Um den Umfang und durch die Mitte des Dies verlaufen breite Leitungstrassen. Der obere Megablock machte eine zusätzliche Querverbindung notwendig. Oberflächlich betrachtet ist es verwunderlich, dass sich diese Querverbindung nicht in der Mitte oder am Rand des Megablocks befindet.

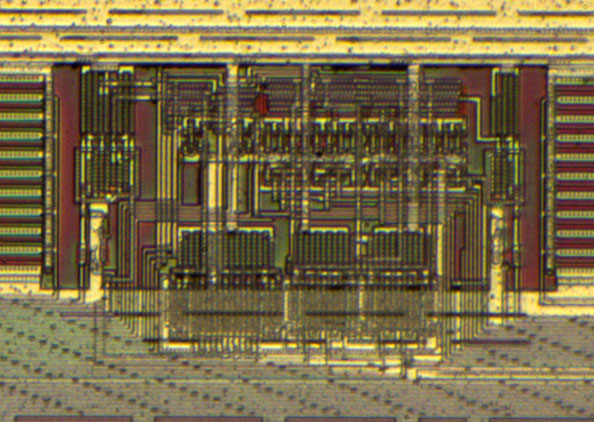

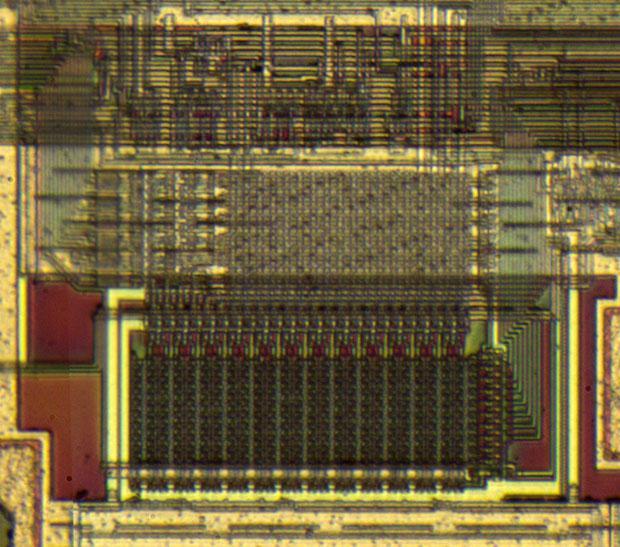

Die einzelnen Funktionsblöcke lassen sich auf Grund der verschiedenen Strukturen relativ gut unterscheiden.

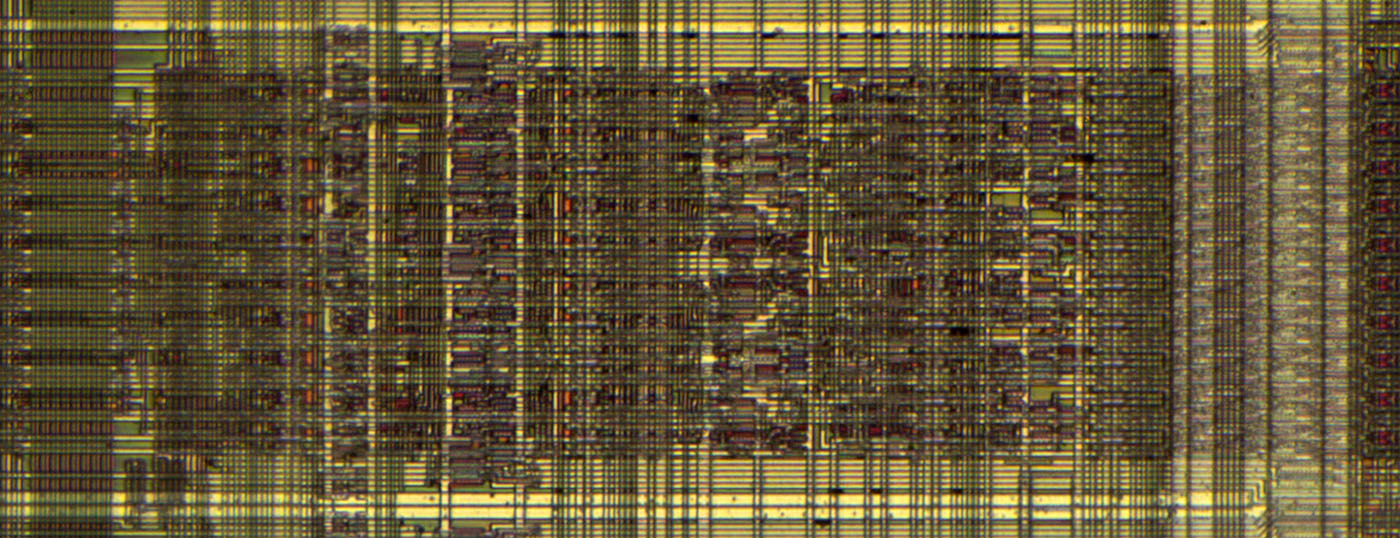

Die in der Übersicht rot markierten Blöcke müssen zwei I/O-Zellen beinhalten. Eine gewisse Symmetrie lässt sich erahnen.

Der in der Übersicht hellgrün markierte Bereich beinhaltet die verschiedenen Gatter des Global-Logic-Blocks.

Der in der Übersicht dunkelgrün markierte Bereich enthält die Verbindungsmatrix des Global-Logic-Blocks.

Im lila markierten Bereich befindet sich schließlich der dich gepackte Global-Routing-Pool. Die vertikal verlaufende Trasse in der Mitte des Global-Routing-Pools ist etwas unsymmetrisch.

Im Detail betrachtet zeigt sich, dass die schwarze Querverbindung nicht nur die 16 Leitungen des Output-Routing-Pools enthält. Aus dem Bereich der I/O-Zellen werden 4 zusätzliche Potentiale übertragen. Es könnte sich dabei um die zwei Taktleitungen, das Enable- und das Reset-Signal handeln, die allen I/O-Zellen gemein sind.