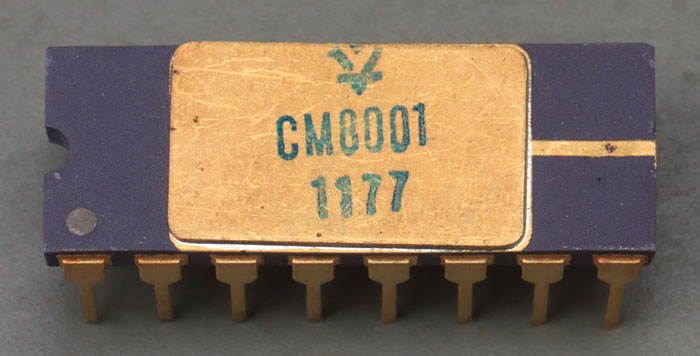

Der Mikroelektronika Botevgrad CM8001 (SM8001) ist ein SRAM mit einer Speichertiefe von 256Bit. Er entspricht dem Intel 1101A. Der 1101 war der zweite von Intel kommerziell vertriebene SRAM. Mit dem 1101A lieferte Intel eine verbesserte Variante. Der SM8001 basiert wie der 1101 und der 1101A auf PMOS-Transistoren und benötigt daher als Versorgung ein +5V-Potential und ein -9V-Potential. Den 1101 musste man noch mit 5V, -7V und -10V versorgen. Den 1101A hatte man so weit optimiert, dass er mit 5V und -9V arbeiten konnte. Die Zugriffszeit des SM8001 ist mit maximal 1,5µs spezifiziert. Per Selektion konnte man unter 1µs bleiben. Die Beschriftung zeigt, dass der Baustein 1977 gefertigt wurde.

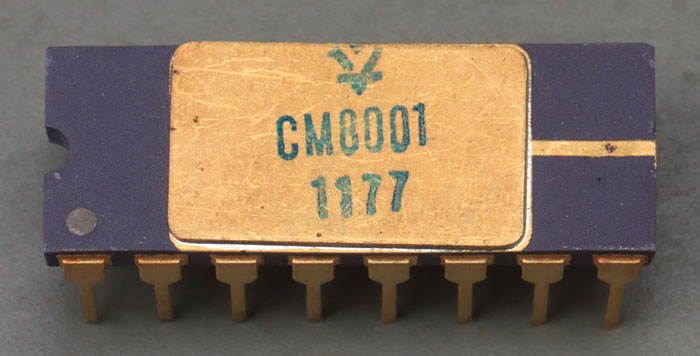

Das Die des SM8001 hat man weit außerhalb der Mitte im Gehäuse platziert.

Die Abmessungen des Dies betragen 3,1mm x 3,3mm.

Dieses Bild ist auch in einer höheren Auflösung verfügbar: 14MB

Die Zeichen neben den Zahlen 8001 könnten für die Revision des Designs stehen. Б1 wäre kyrillisch für B1.

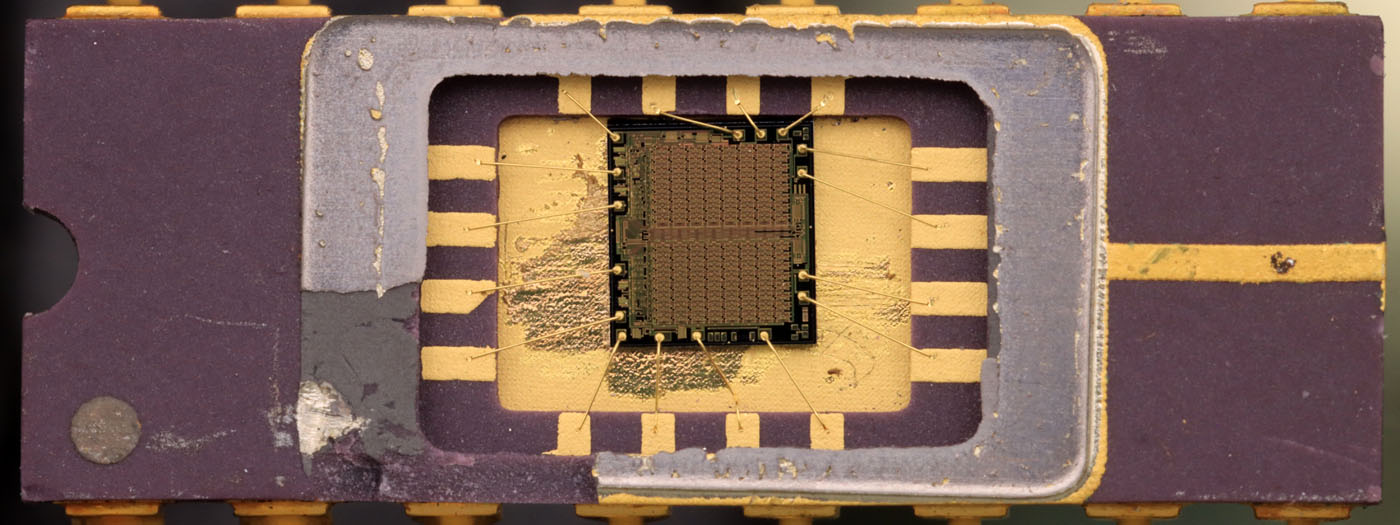

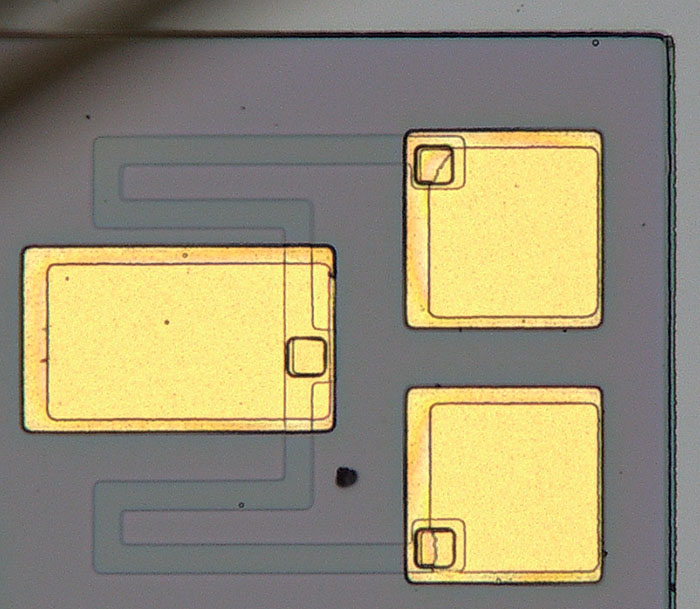

In der Mitte einer jeden Kante ist eine Struktur abgebildet, die zeigt wie gut die Masken während der Produktion zueinander ausgerichtet waren.

Im Außenbereich des Dies befinden sich mehrere Teststrukturen. Hier ist ein Widerstand mit einem Abgriff integriert.

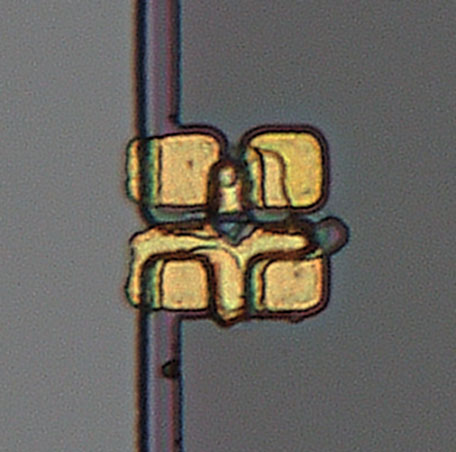

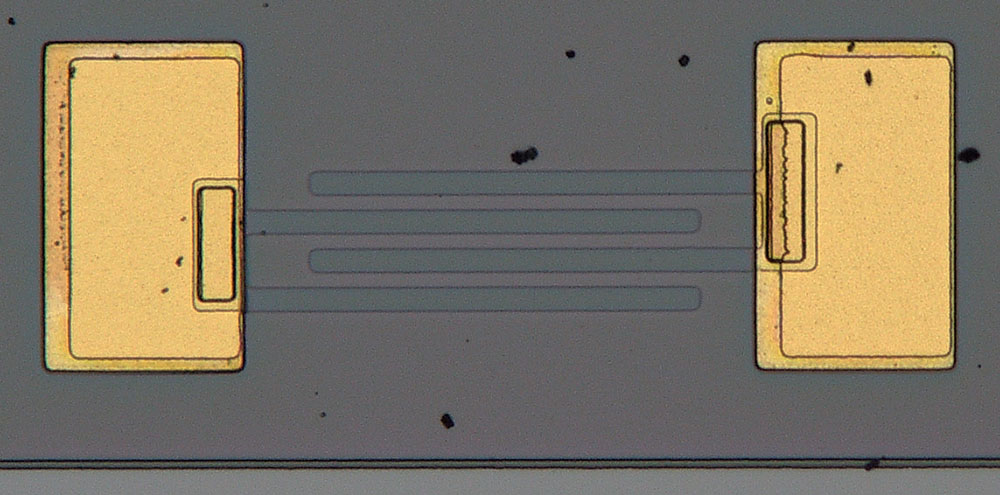

Die ineinandergreifenden Strukturen könnten dazu dienen die Leckströme zwischen den Leitungen im Substrat zu bestimmen. Auch die parasitäre Kapazität könnte man damit vermessen.

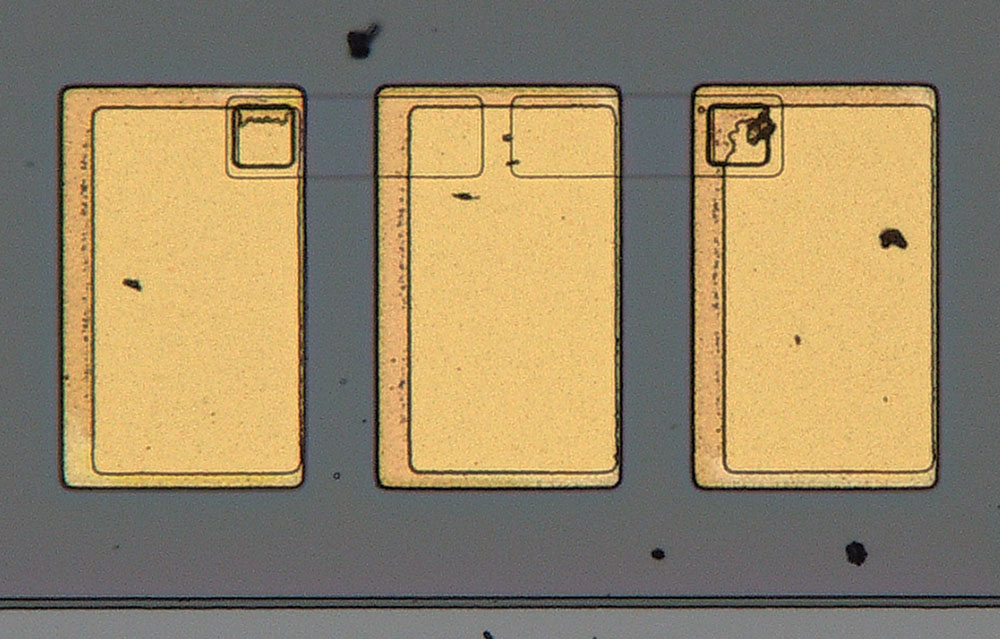

Der SM8001 basiert noch auf einem Metal Gate Prozess, bei dem die Metalllage die Gate-Elektroden der MOS-Transistoren darstellen. Wo die Metalllage als Gate-Elektrode wirken soll, befindet sich im dicken, sogenannten Feldoxid, ein Fenster mit einer sehr dünnen Siliziumoxidschicht. Den 1101 und den 1101A hat Intel bereits mit einem moderneren Silicon Gate Prozess gefertigt. Die Gate-Elektroden aus Polysilizium ermöglichen es präzisere Geometrien herzustellen.

Source- und Drainbereich sind beim hier integrierten Transistor nur schlecht zu erkennen. In anderen Bereichen zeichnen sich die Strukturen besser ab. Rechts führt ein Widerstand zu einem vierten Testpad. Der Kontakt zwischen dem Widerstand und dem Drain/Source-Bereich scheint sich ohne einem speziellen Kontaktfenster zu ergeben.

Mit einer weiteren Teststruktur kann man einen parasitären MOSFET vermessen. Dabei handelt es sich um eine Metallleitung, die einen Isolationsbereich zwischen zwei Leitungen im Substrat überdeckt. Durch das dicke Feldoxid hat die Ladung der Metallleitung einen deutlich geringeren Einfluss auf die darunter liegenden Strukturen.

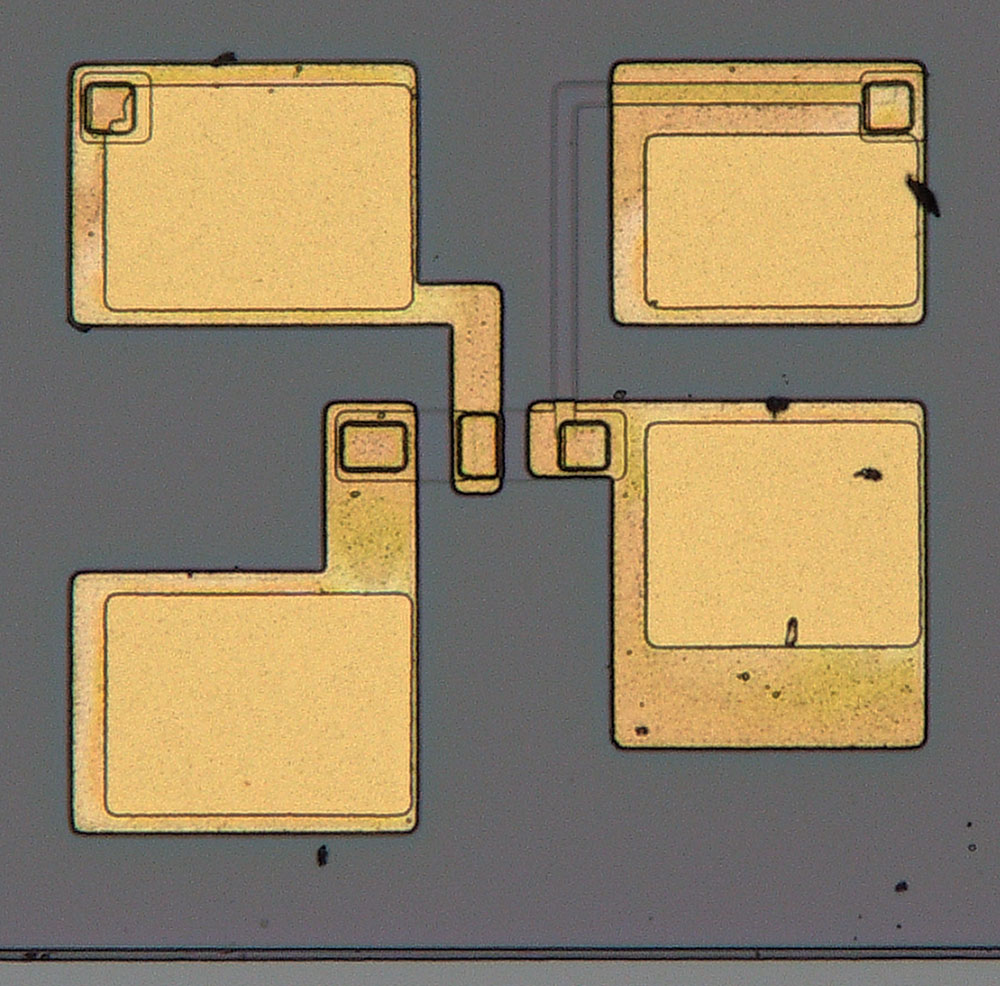

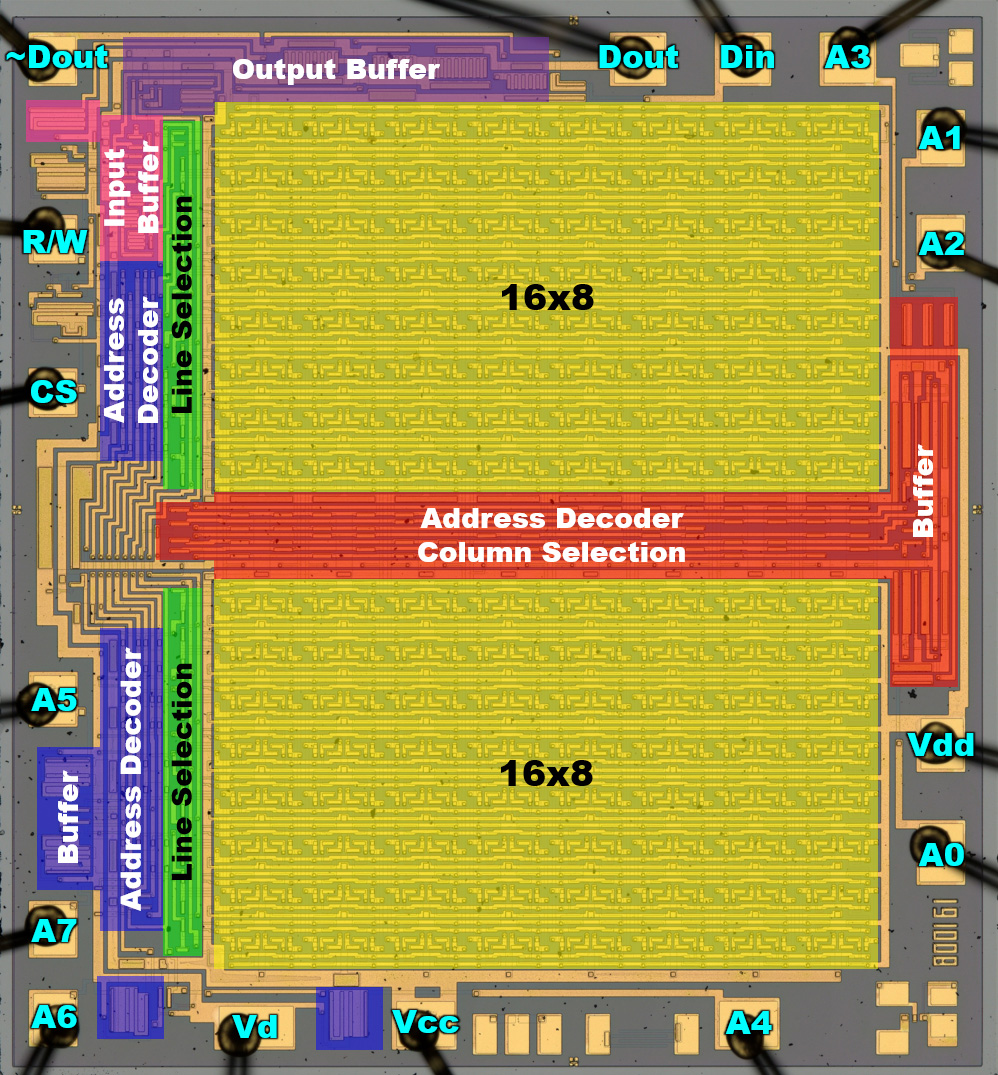

Die Funktionsweise des SM8001 ist sehr übersichtlich. Die Adressleitungen A0 bis A3 werden eingelesen, decodiert (rot) und aktivieren schließlich eine von 16 Spalten in zwei Speicherbereichen (gelb). Der Speicher ist in zwei Blöcken mit jeweils 16x8 Speicherzellen aufgeteilt. Die Adressleitungen A4 bis A7 werden ebenfalls decodiert (blau) und steuern dann die Auswahl der Speicherzeile (grün). Im Bereich der Zeilenauswahl verlaufen zwei Leitungen, die entweder ein differentielles Signal zu der jeweiligen Speicherzelle übertragen oder den Zustand der Speicherzelle in die Schaltung im oberen linken Bereich weiterleiten.

Im oberen linken Bereich befindet sich der Eingangspuffer (rosa) und der Ausgangstreiber (lila). Beide Schaltungen sind mit dem Chipselect- und dem R/W-Eingang verbunden. Wie der 1101 bietet auch der SM8001 zum Datenausgang zusätzlich einen komplementären Ausgang. Die beiden großen Push-Pull-Endstufen sind deutlich zu erkennen. Neben dem positiven Versorgungspotential Vcc und dem negativen Versorgungspotential Vdd besitzt der Speicher noch einen Vd Kontakt. Vd ist ebenfalls mit -9V zu verbinden und versorgt die Eingangs- und Ausgangsschaltungsteile, während Vdd den Speicherbereich selbst versorgt.

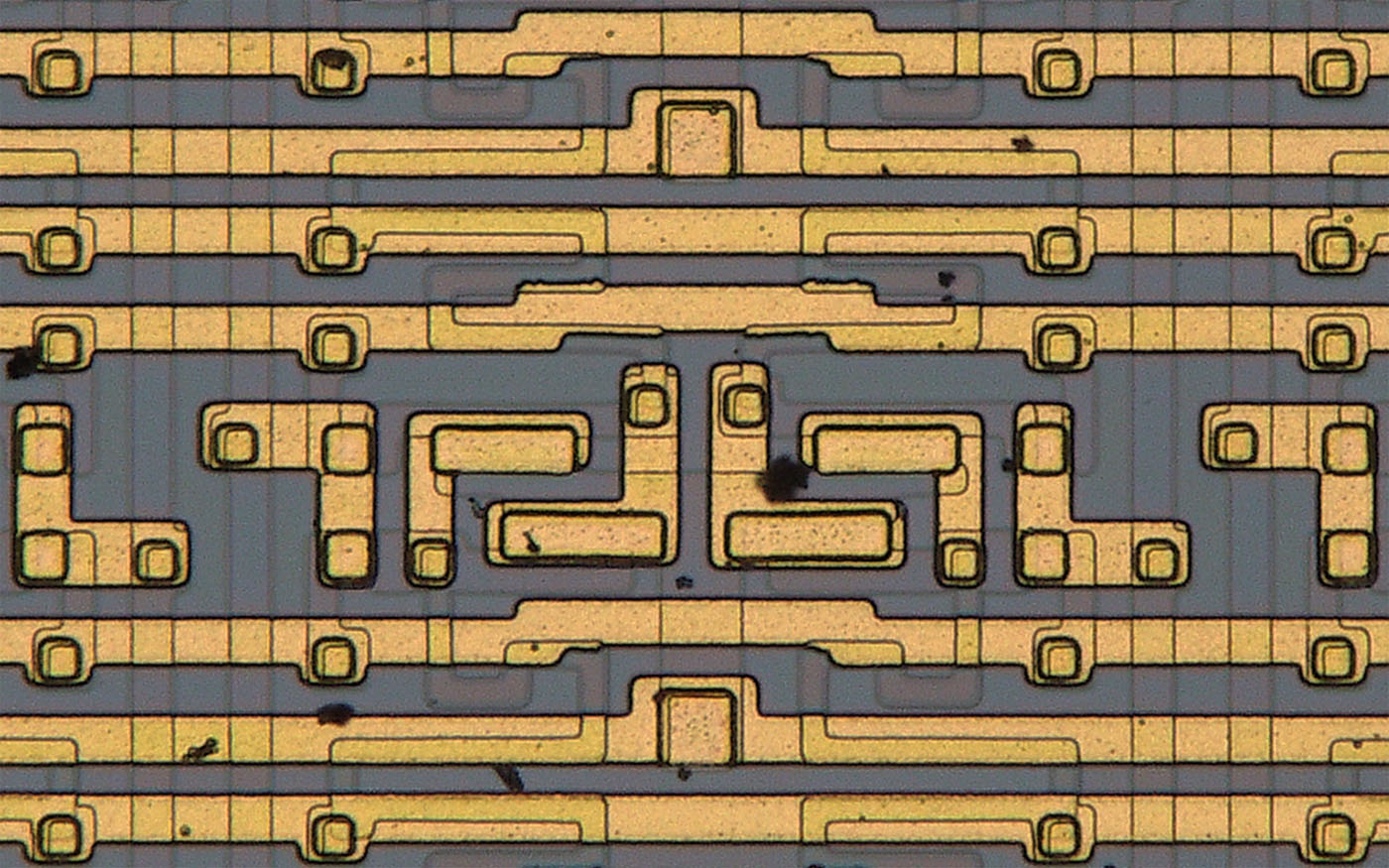

Der regelmäßige Aufbau des Speicherbereichs ist deutlich zu erkennen. Er besteht aus Blöcken, die jeweils zwei Speicherzellen enthalten.

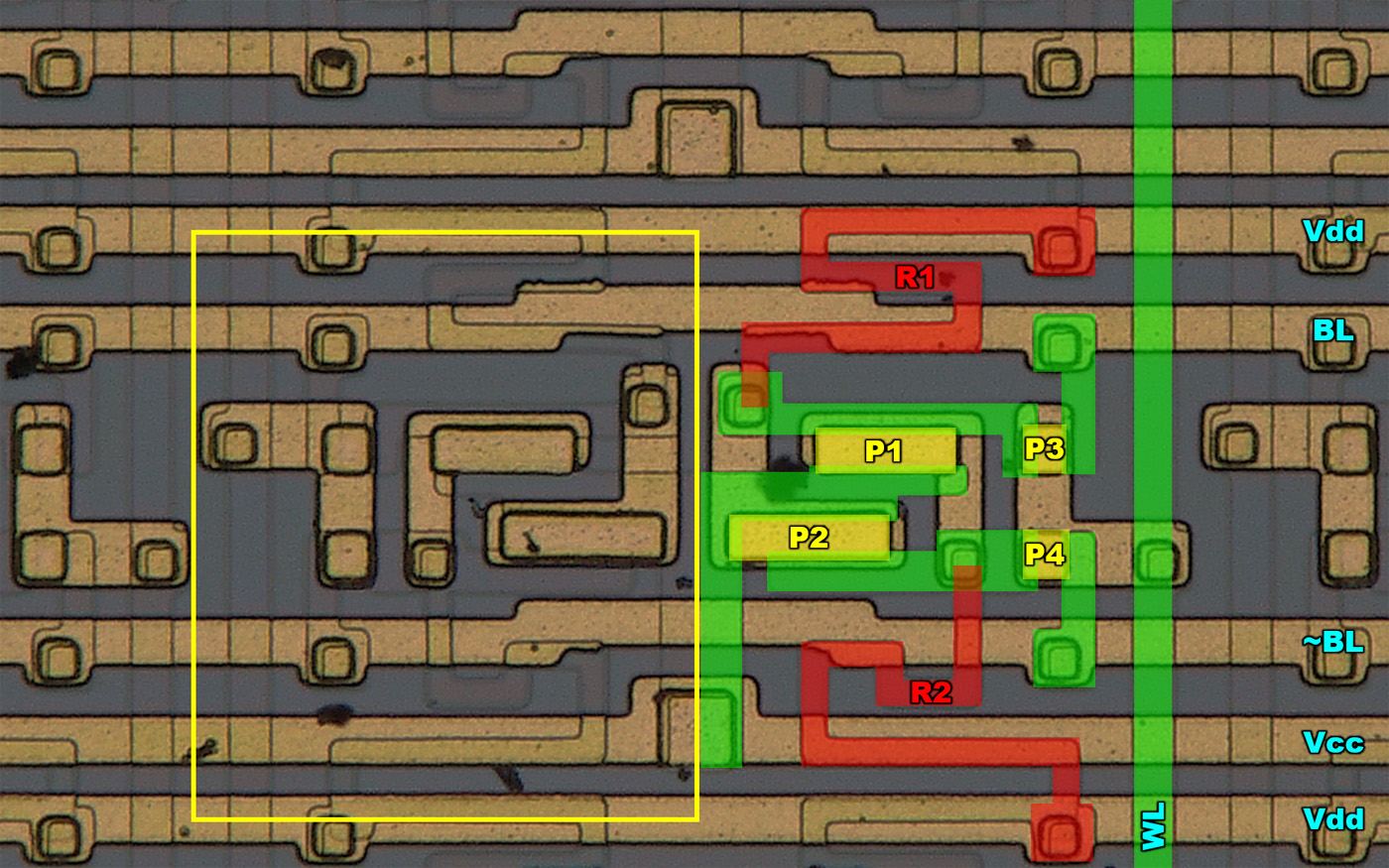

Unterhalb jeder Speicherzelle befindet sich eine Vcc-Leitung. Das Vdd-Potential findet sich oben und unten. Diese Vdd-Leitungen werden auch von den oben und unten anschließenden Speicherzellen genutzt. Rechts und links der zwei Speicherzellen verlaufen im Substrat die Wortleitungen, die die zugehörige Spalte des Speichers aktivieren. Die beiden horizontal verlaufenden Bitleitungen übertragen den Zustand der ausgewählten Speicherzelle.

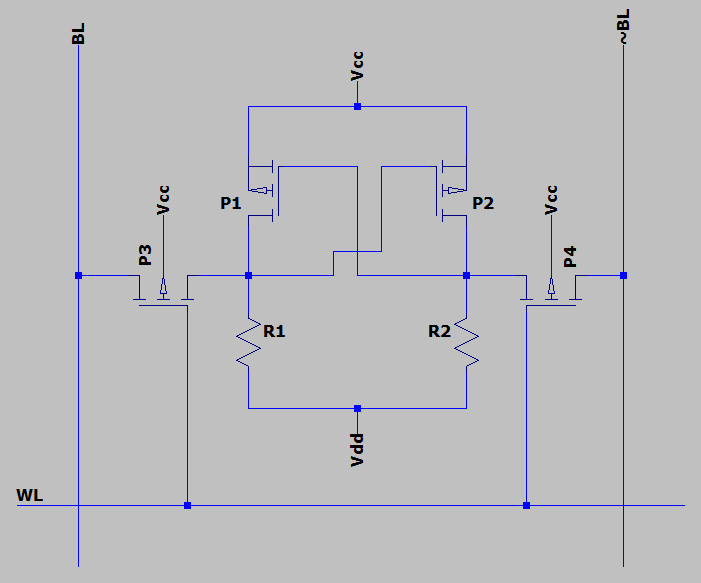

Der SM8001 basiert auf 4T-Speicherzellen, die vier PMOS-Transistoren und zwei Widerstände enthalten.