Der КM537РУ1 (KM537RU1) ist ein SRAM mit einer Speichertiefe von 1kBit. Neben dem Keramikgehäuse war auch eine Variante im Kunststoffgehäuse verfügbar, deren Bezeichnung КP537РУ1 (KR537RU1) lautet.

Der Hersteller lässt sich nicht klären, was oft der Fall ist bei Halbleitern aus dem sowjetischen Raum. Weit verbreitete Typen wurden meist von mehreren Herstellern produziert. Der Datecode zeigt, dass der Baustein aus dem Jahr 1984 stammt.

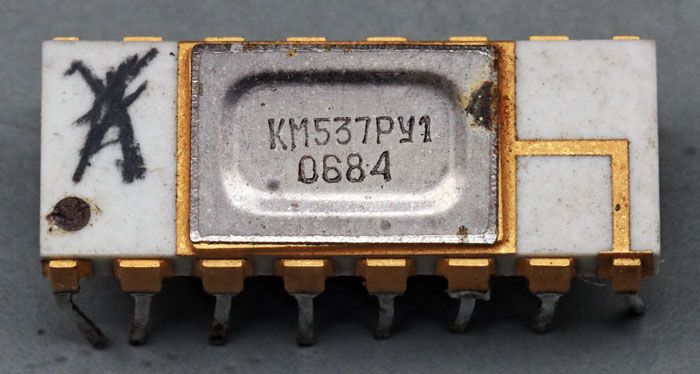

Das russische Datenblatt führt neben dem КM537РУ1 (KM537RU1) und dem КP537РУ1 (KR537RU1) zusätzlich die Varianten К537РУ1 (K537RU1) und КИ537РУ1 (KI537RU1). Es handelt sich dabei lediglich um unterschiedliche Pinanordnungen. Das Symbol im russischen Datenblatt (links) zeigt die Pinbelegung der Typen KM537RU1 und KR537RU1 in Klammern. Daneben befindet sich die Pinbelegung der Varianten K537RU1 und KI537RU1.

In der Datenblattsammlungen des Kombinats Mikroelektronik Erfurt findet sich in der Ausgabe 1/86 ein deutschsprachiges Datenblatt für den KM537RU1 und den KR537RU1. Dort ist ein anderes Pinning dargestellt (rechts). Der Eingang zur Aktivierung des Bausteins und die Umschaltung zwischen Schreiben und Lesen sind vertauscht. Wie sich noch zeigen wird, ist das Pinning im russischen Datenblatt falsch.

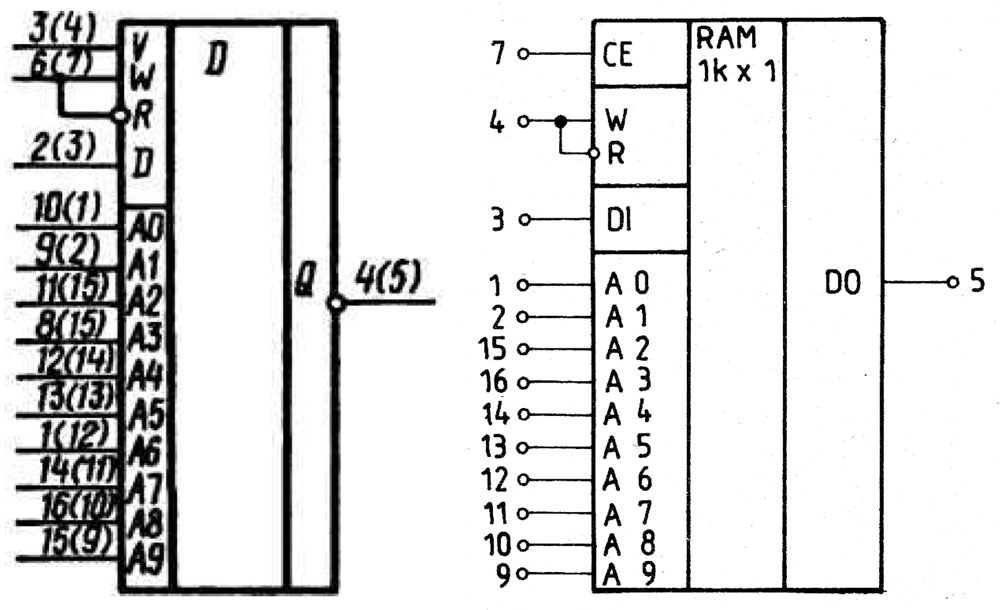

Auch die Tabelle, die die Zustände und das Verhalten des SRAM beschreibt, enthält im russischen Datenblatt einen Fehler, der allerdings leicht zu erkennen ist. Beim Potential CE, das den Baustein aktiviert, muss in der ersten Zeile eine 0 stehen. Interessant ist, dass der Speicher beim Beschreiben am Ausgang das Eingangssignal invertiert ausgibt.

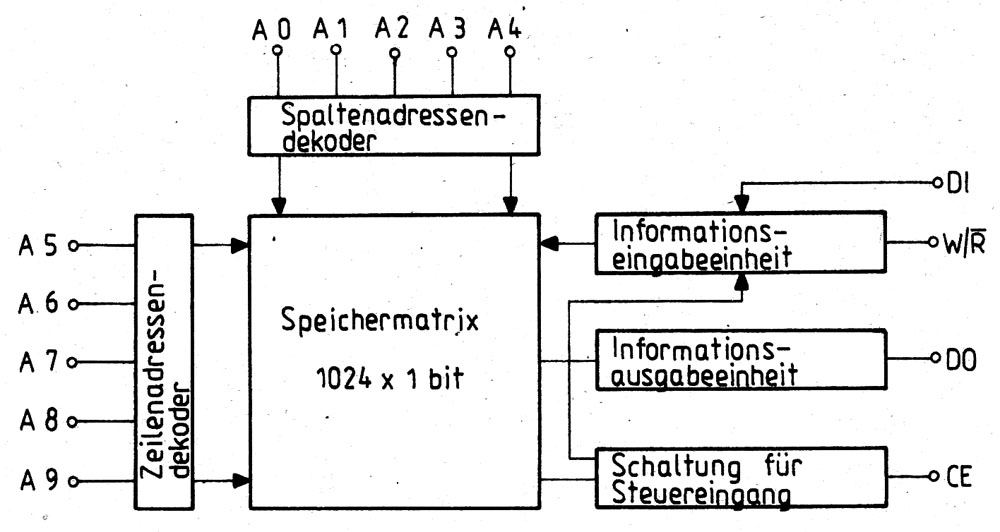

Das Datenblatt enthält ein Blockschaltbild, das keine Überraschungen enthält.

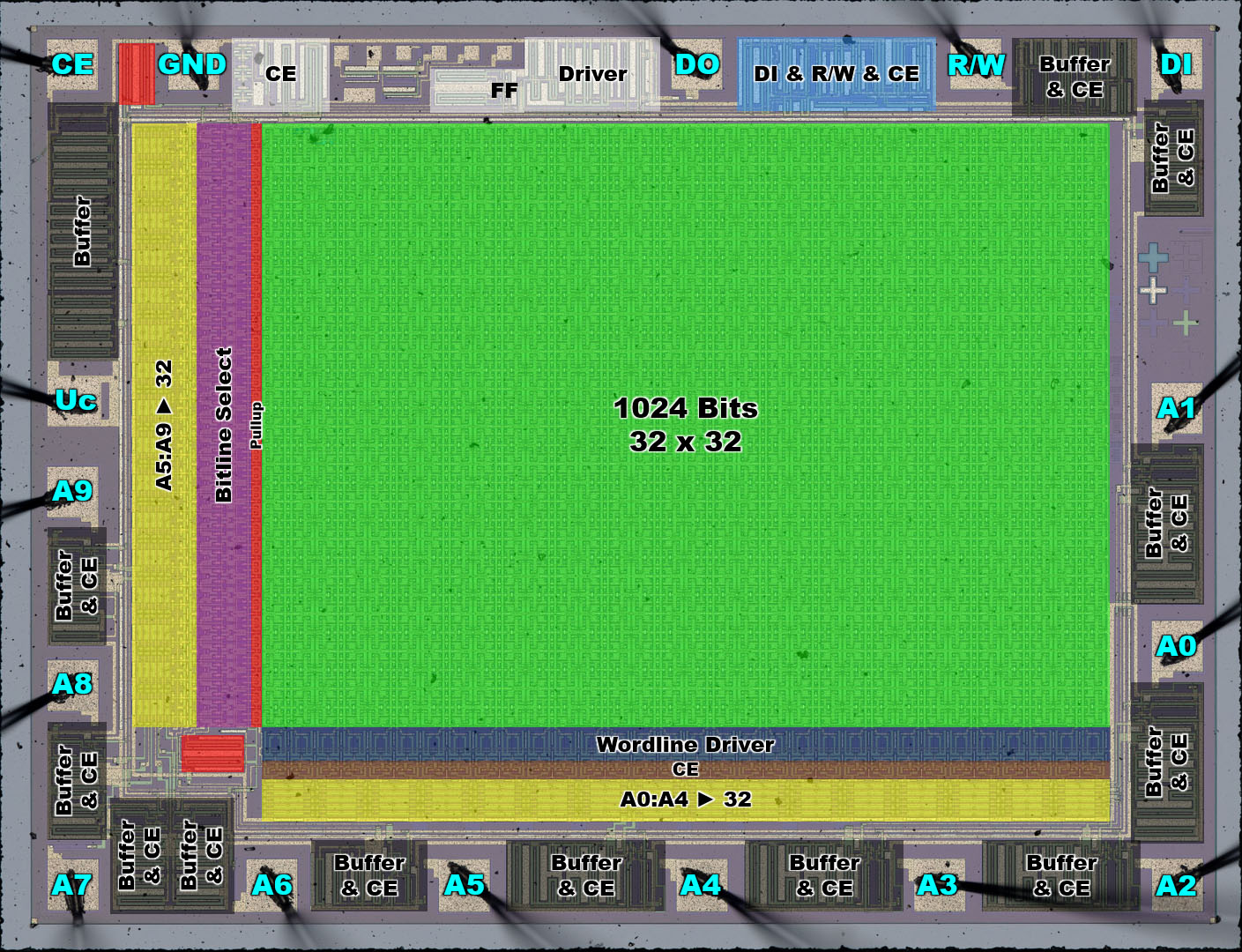

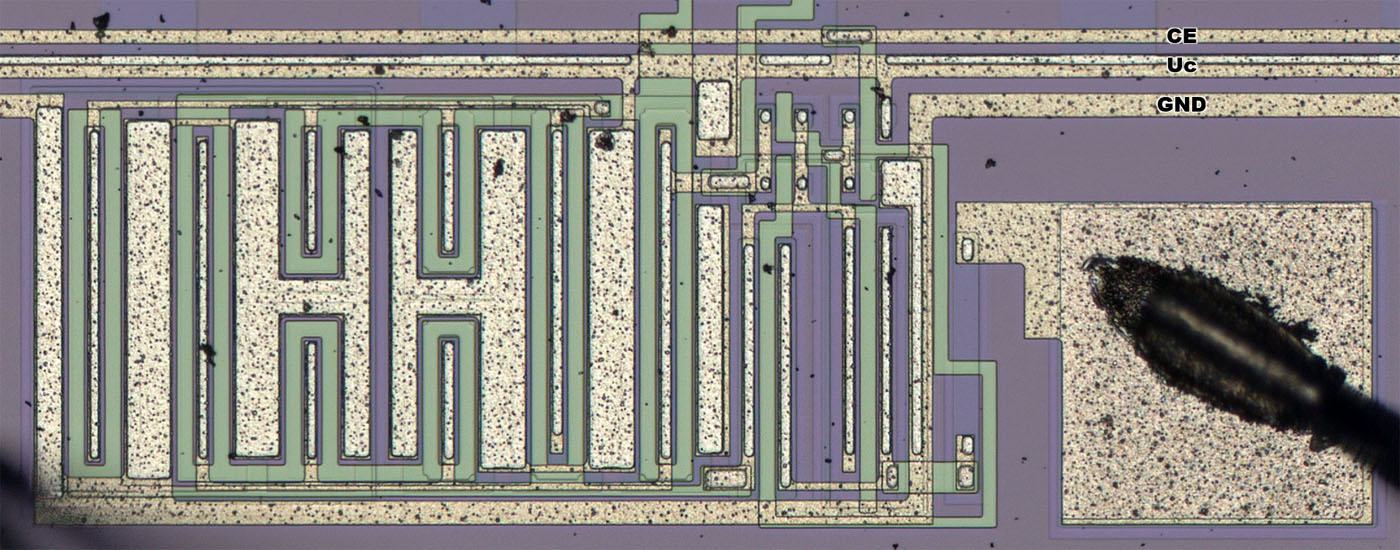

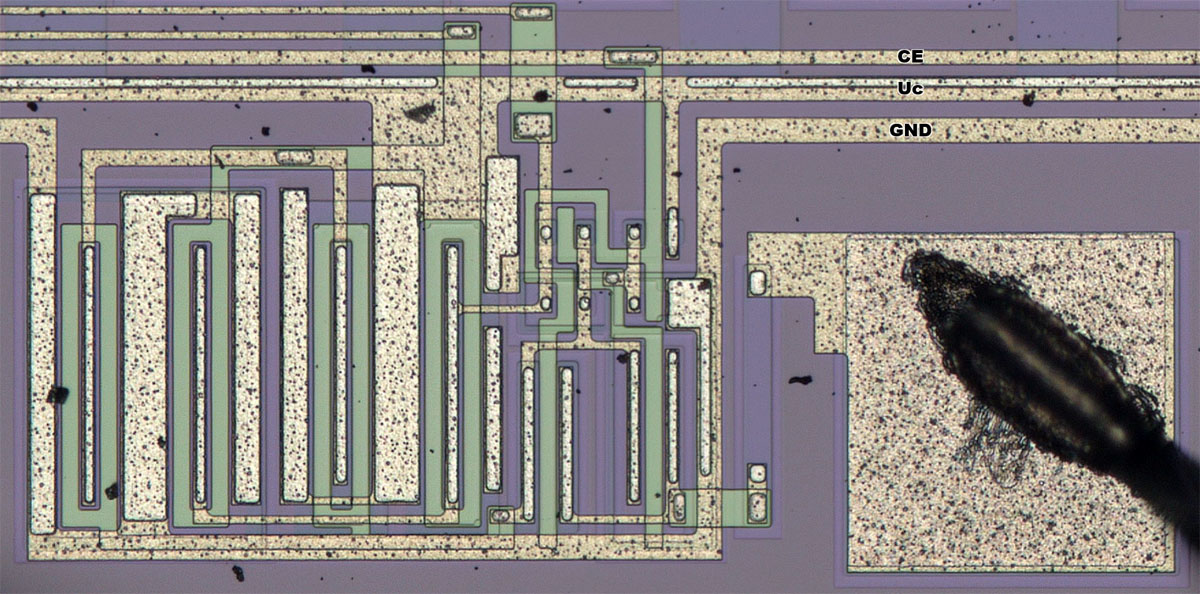

Die Abmessungen des Dies betragen 3,9mm x 3,0mm. Laut Datenblatt sind darauf 7.200 Transistoren integriert. Dieses Bild ist in höherer Auflösung verfügbar: 45MB

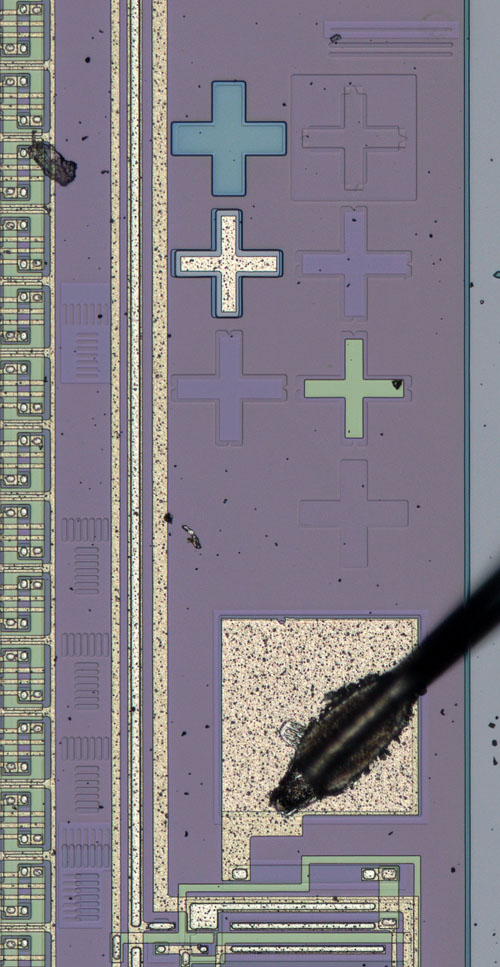

Auf dem Die befinden sich keine Strukturen, die einen Hinweis auf den Hersteller geben. Am rechten Rand zeigen lediglich einige Hilfsstrukturen wie gut die Masken zueinander ausgerichtet sind.

An der oberen Kante befindet sich eine Teststruktur, die anscheinend drei Transistoren enthält.

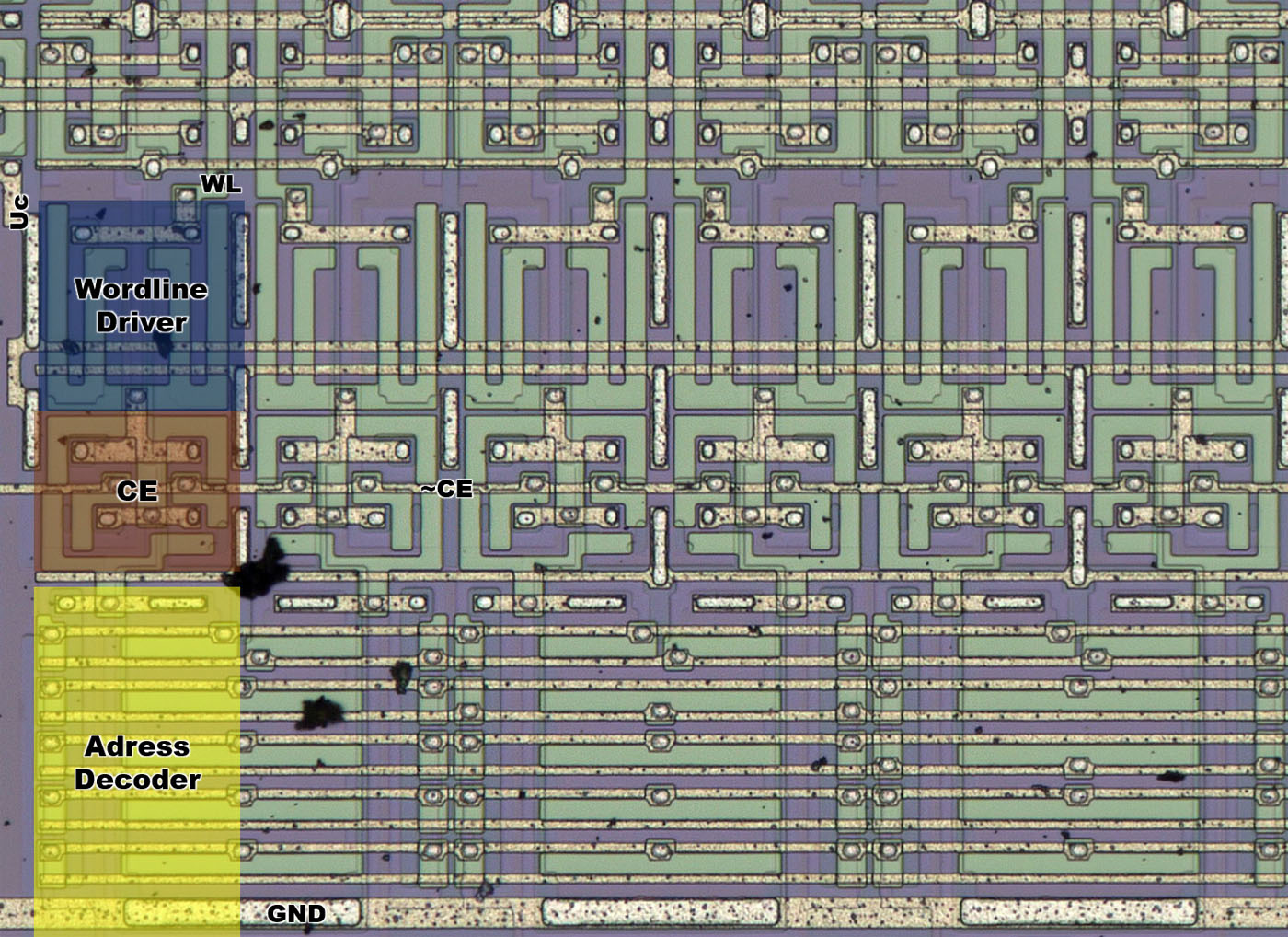

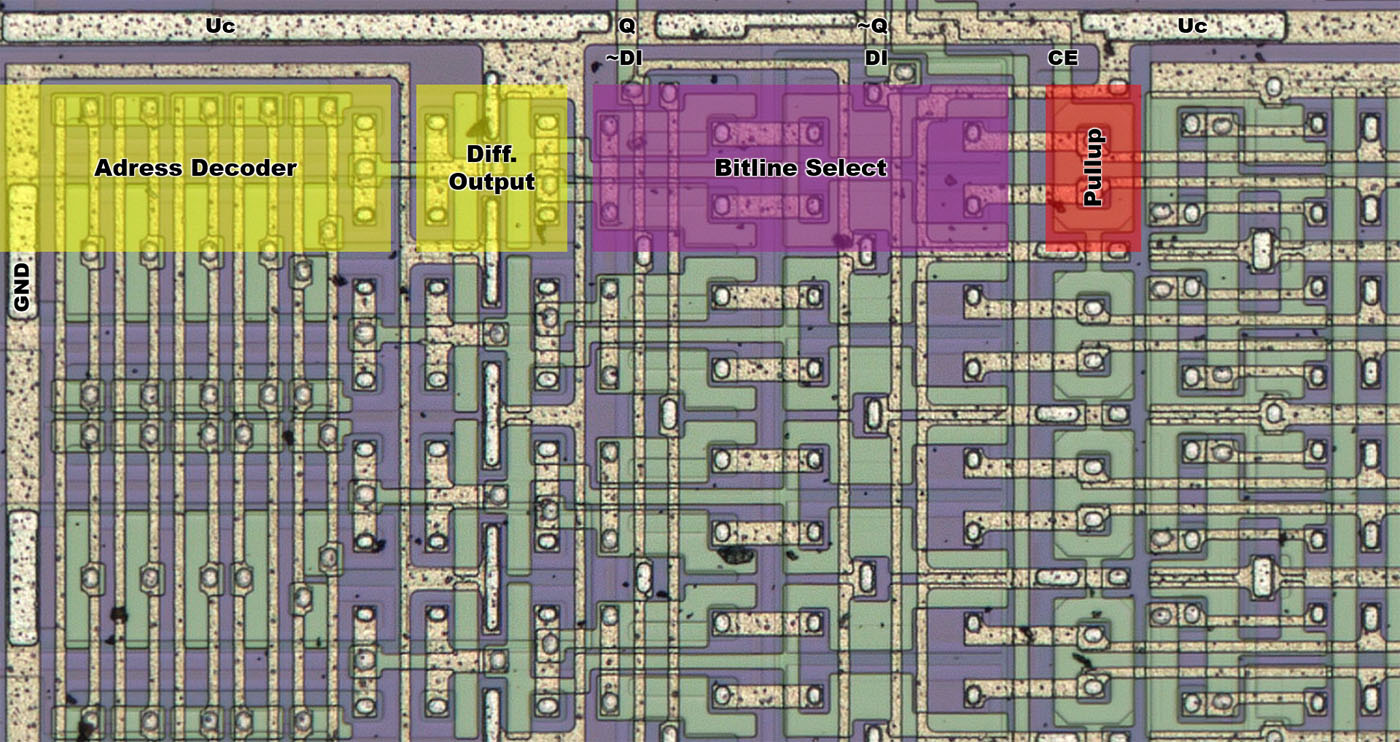

Direkt neben den Bondpads die Eingänge darstellen befinden sich Pufferstufen (schwarz). Der Puffer für das CE-Signal ist verhältnismäßig groß, weil dieses Signal an vielen Stellen in der Schaltung verwendet wird. Alle Pufferstufen werden mit dem CE-Signal aktiviert. Das DI-Signal ist zusätzlich mit dem R/W-Signal verknüpft (hellblau). Am Ausgang befindet sich ein Treiber (weiß). Davor wertet ein Flip-Flop das differentielle Signal aus, das der Speicherbereich ausgibt. Ein weiterer Schaltungsteil verknüpft den Ausgangstreiber mit dem CE-Signal. Dieser Schaltungsteil scheint außerdem eine gewisse Verzögerung zu erzeugen, so dass der Ausgang erst aktiv wird, wenn dort ein gültiges Signal anliegt.

Den Großteil der Fläche des Dies nimmt der Speicherbereich ein (grün). An der unteren Kante befinden sich die Spaltenauswahl. Dort werden die Adressleitungen A0 bis A4 ausgewertet (gelb) und mit dem CE-Signal verknüpft (braun). Ein Treiber aktiviert schließlich eine sogenannte Wordline. Die Zeilenauswahl befindet sich links des Speicherbereichs. Die Auswertung der Adressleitungen A5 bis A9 definiert welche Zeile ausgewählt werden soll (gelb). Darauf folgt eine Schaltung, die das Eingangssignal in die jeweilige Zeile weiterleitet oder das im Speicher anliegende Signal nach oben herausführt (lila). Zwischen dieser Schaltung und dem Speicherbereich befinden sich Pullup-Strukturen (rot).

Die Eingangspuffer für die Adressleitungen A0 bis A4 (oben) sind deutlich größer als die Puffer für die Adressleitungen A5 bis A9 (unten). Das erklärt sich dadurch, dass die Spaltenauswahl insgesamt mehr Gatefläche enthält und so mehr Leistung für das Umladen der Gatekapazitäten benötigt wird. Das CE-Signal aktiviert die Puffer, die den Zustand der Adressleitung differentiell ausgeben.

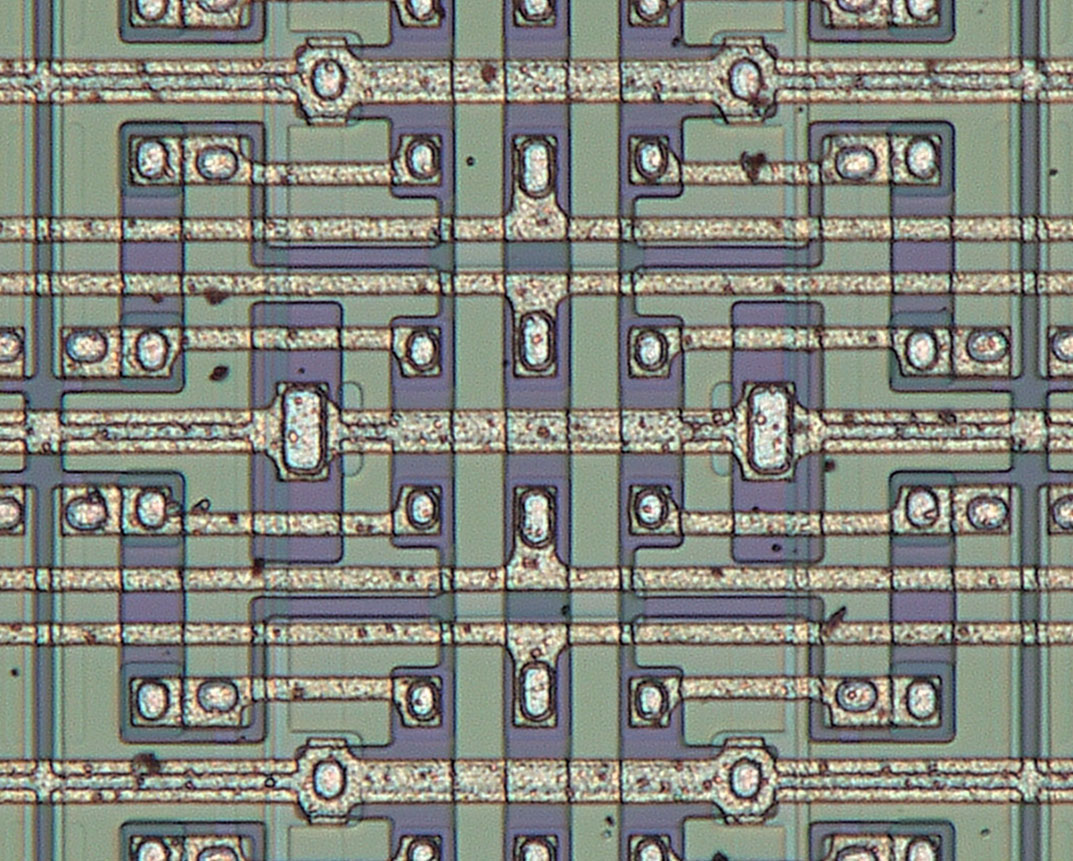

Auf den ersten Blick wirkt der Speicherbereich unübersichtlich, man erkennt aber schließlich die sich wiederholenden Strukturen der einzelnen Speicherzellen.

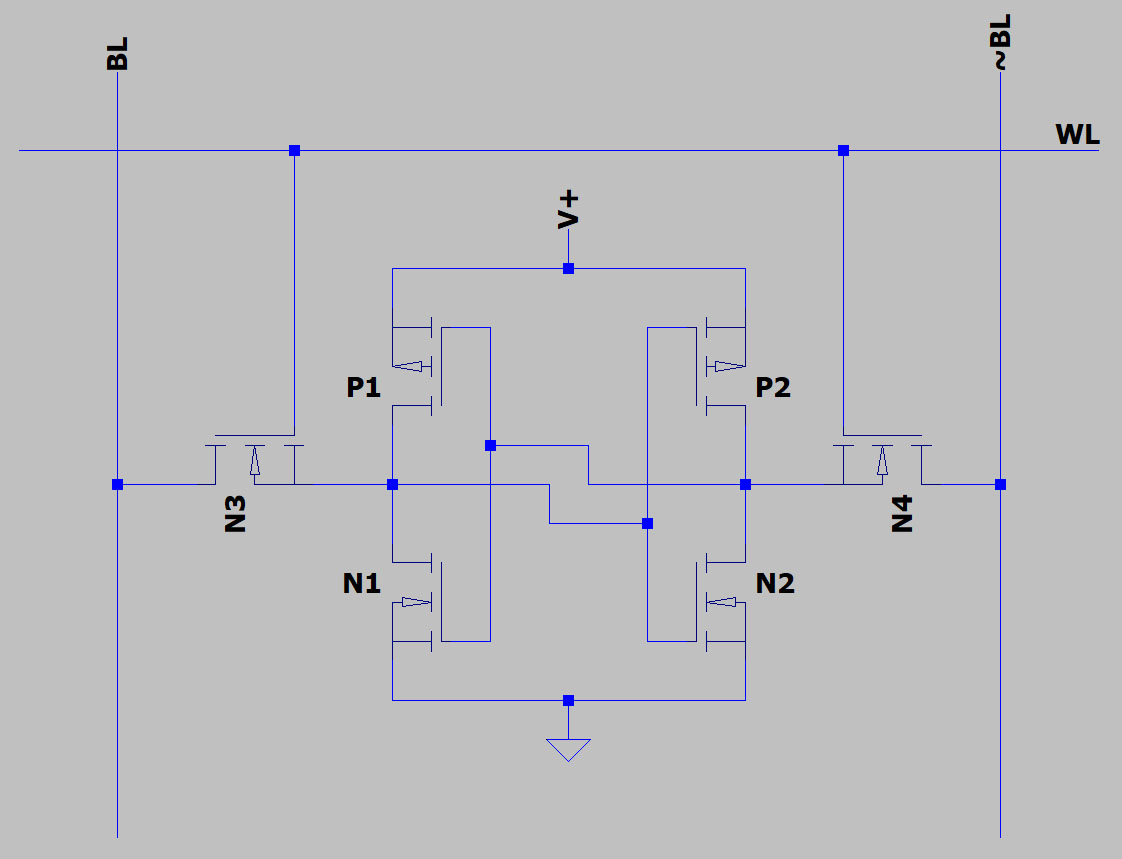

Es handelt sich um die bekannten SRAM-Zellen mit sechs Transistoren. Die sogenannte Wordline aktiviert die Transistoren N3 und N4, woraufhin über die differentiellen Bitline-Potentiale der Status der Transistoren P1/N1/P2/N2 ausgelesen oder überschrieben werden kann.

Der Einfachheit halber wurden hier die in LTSpice üblichen MOSFET-Symbole verwendet. Tatsächlich ist das Bodypotential nicht hart mit dem Source-Potential verbunden, was für die Transistoren N3 und N4 relevant ist.

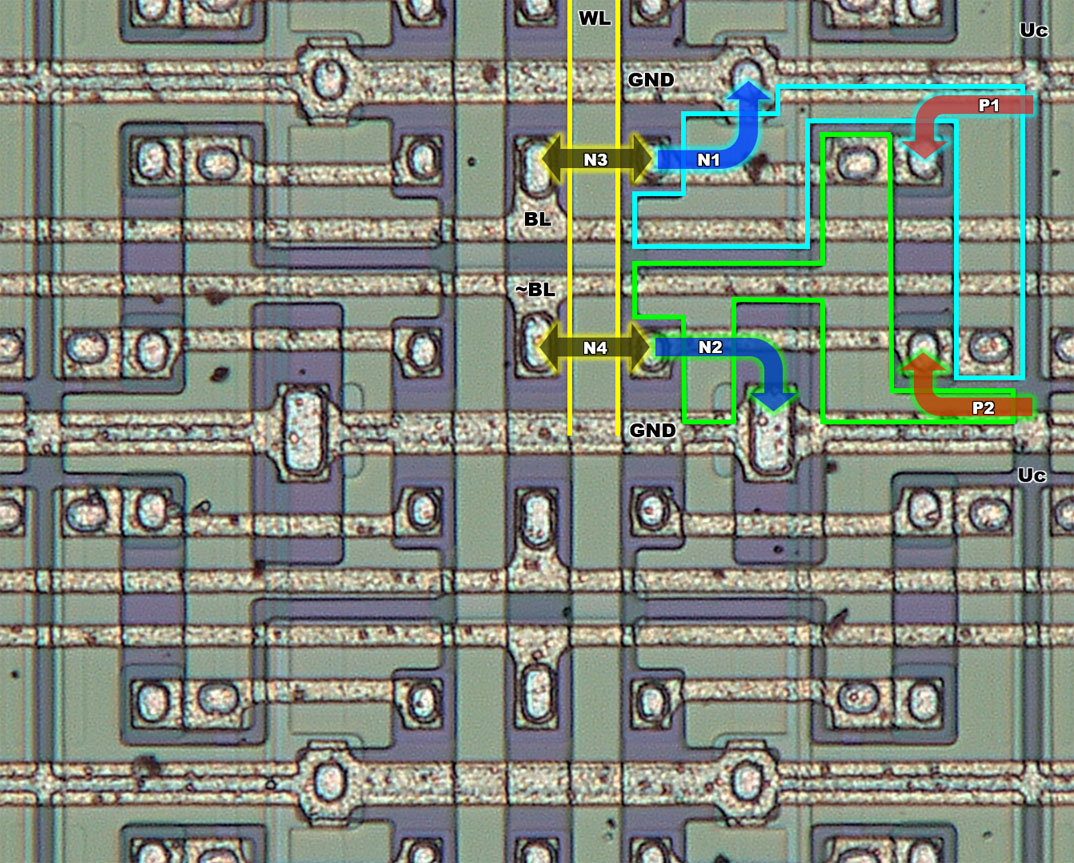

In der realen Umsetzung versucht man die SRAM-Zellen auf eine möglichst kleine Fläche zu integrieren. Da sich der Flächenbedarf einer Zelle mit der Speichertiefe multipliziert, hat jede Einsparung eine große Wirkung. Der Aufbau der Zellen ist dadurch aber oft nicht mehr auf den ersten Blick ersichtlich.

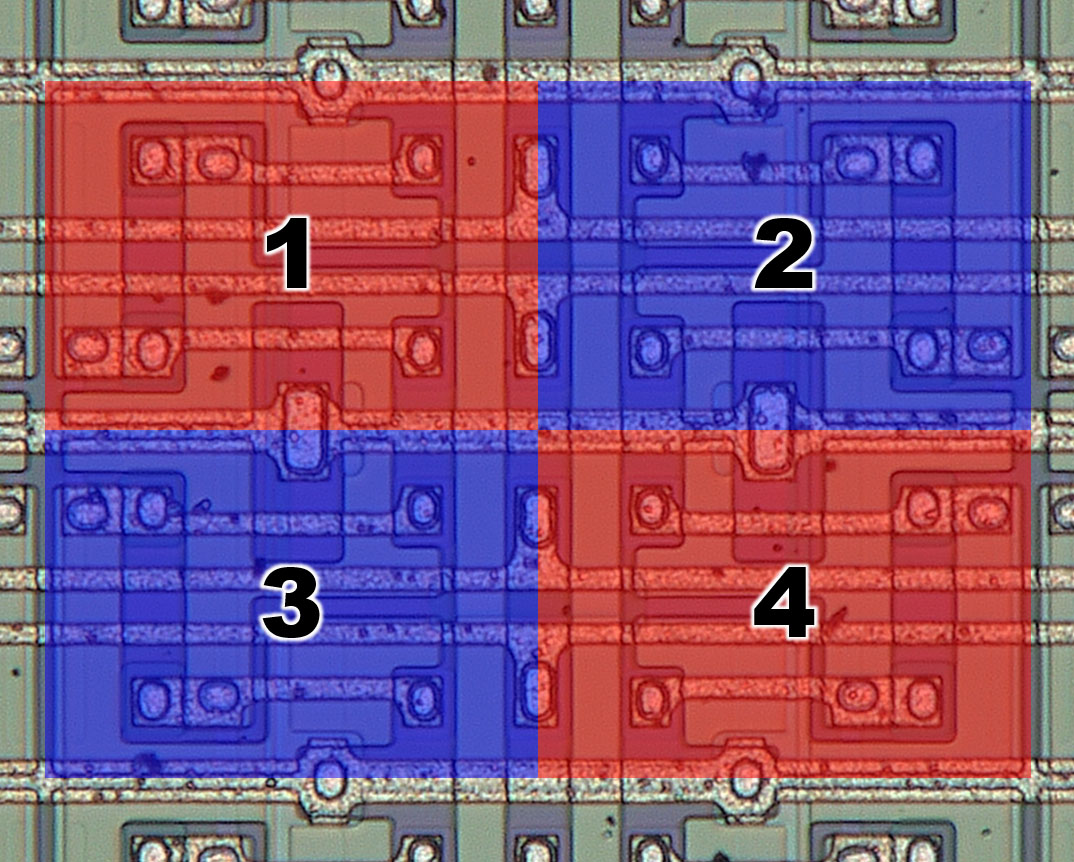

Im Vergleich zum Schaltplan ist die Schaltung hier um 90° gedreht. Oberhalb und unterhalb der Speicherzelle verlaufen GND-Leitungen in der Metalllage. Das Versorgungspotential wird rechts der Speicherzelle durch das Silizium übertragen. Zwischen den GND-Leitungen führt die Metalllage die differentiellen Bitline-Potentiale der Zeilenauswahl über den Speicherbereich. Das Wordline-Potential verläuft von der Spaltenauswahl ausgehend in der Polysiliziumlage von unten nach oben (gelb).

Die Transistoren N3 und N4, die alle Speicherzellen einer Spalte aktivieren, bilden sich direkt unter der Leitung, die das Wordline-Potential überträgt. Innerhalb der Speicherzelle befinden sich zwei Polysiliziumflächen (grün/türkis), die der Verteilung der Potentiale dienen und die für die Speicherzelle notwendigen vier Transistoren darstellen (P1/P2/N1/N2).

Auf einer Seite der großen GND-Kontakte sind unter dem Polysilizium längliche Streifen zu erkennen. Anscheinend wurden damit die aktiven Bereiche und damit die Transistoreigeschaften angepasst. Vor allem bei den linken beiden Speicherzellen zeichnen sich ähnliche Streifen parallel zum Versorgungspotential ab. Ohne diese Steuerung wäre der Transistor P1 sehr viel breiter als der Transistor P2 und die Schaltung wäre entsprechend unsymmetrisch.

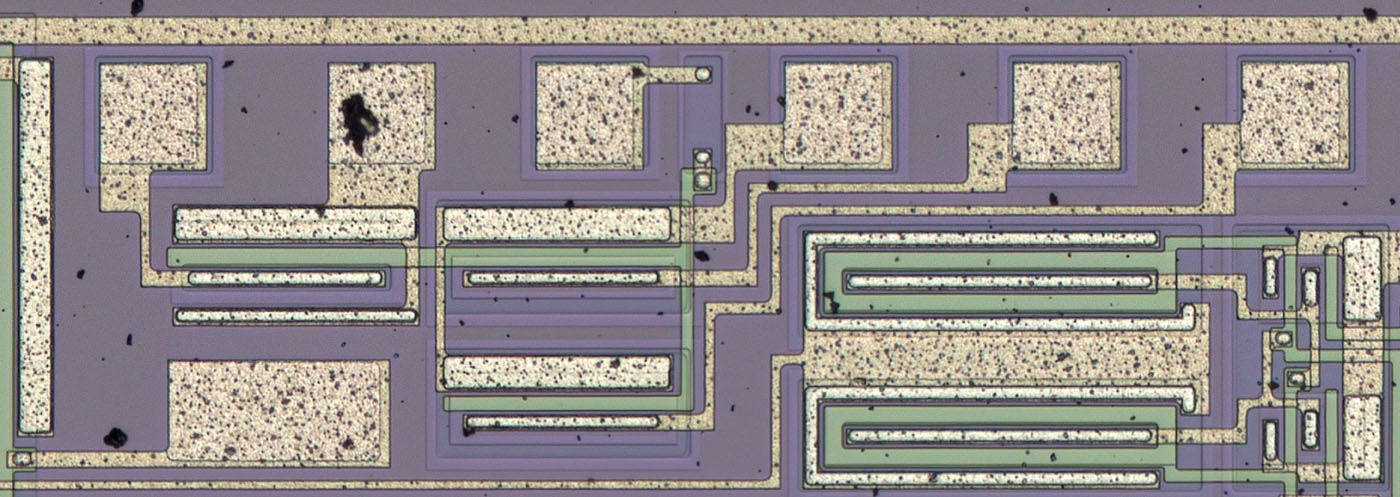

Im unteren Bereich der Spaltenauswahl werden die fünf komplementären Signale des Adressbusses ausgewertet (gelb). Unter jeder Spalte des Speicherbereichs befindet sich ein Stapel mit kleineren Highsidetransistoren und ein Stapel mit größeren Lowsidetransistoren. Bis auf die Transistoren der Adressleitung A0 teilen sich immer zwei benachbarte Spalten die Lowsidetransistoren. Die abwechselnde Kontaktierung der Gateelektroden mit dem invertierten oder nicht invertierten Potential der Adressleitungen sorgt dafür, dass immer nur eine Spalte aktiv ist.

Das Ausgangssignal des Adressdecoders wird mit dem invertierten CE-Potential verknüpft (braun). Es durchläuft dabei außerdem zwei Inverter. Eine Notwendigkeit für diese zwei Inverter ist nicht direkt zu erkennen. Vielleicht wird damit das Timing der Signale angepasst. Größere Treiber (dunkelblau) legen schließlich das jeweilige Steuersignal auf die zugehörige Wordline.

Der Adressdecoder in der Zeilenauswahl ist genauso aufgebaut wie der Adressdecoder in der Spaltenauswahl. Hier sind die Lowsidetransistoren allerdings etwas kleiner ausgeführt. Darauf folgen zwei Inverter, die ein differentielles Ausgangssignal liefern (gelb).

In der aktiven Zeile werden vier Transistoren leitend (lila). Diese Transistoren schalten die differentiellen Bitline-Signale auf zwei Sammelleitungen, die abhängig vom R/W-Signal den Wert aus dem Speicher zum Ausgang führen oder das Eingangssignal zuliefern. In Bezug auf die Potentiale an den Bondpads ist das Ausgangssignal gegenüber dem Eingangssignal invertiert. Das stimmt mit dem Verhalten des Bausteins überein.

Direkt vor dem Speicherblock ist ein Doppeltransistor integriert, der anscheinend als Pullup-Struktur dient. Die Pullup-Struktur ist nur aktiv, wenn das CE-Signal anliegt.

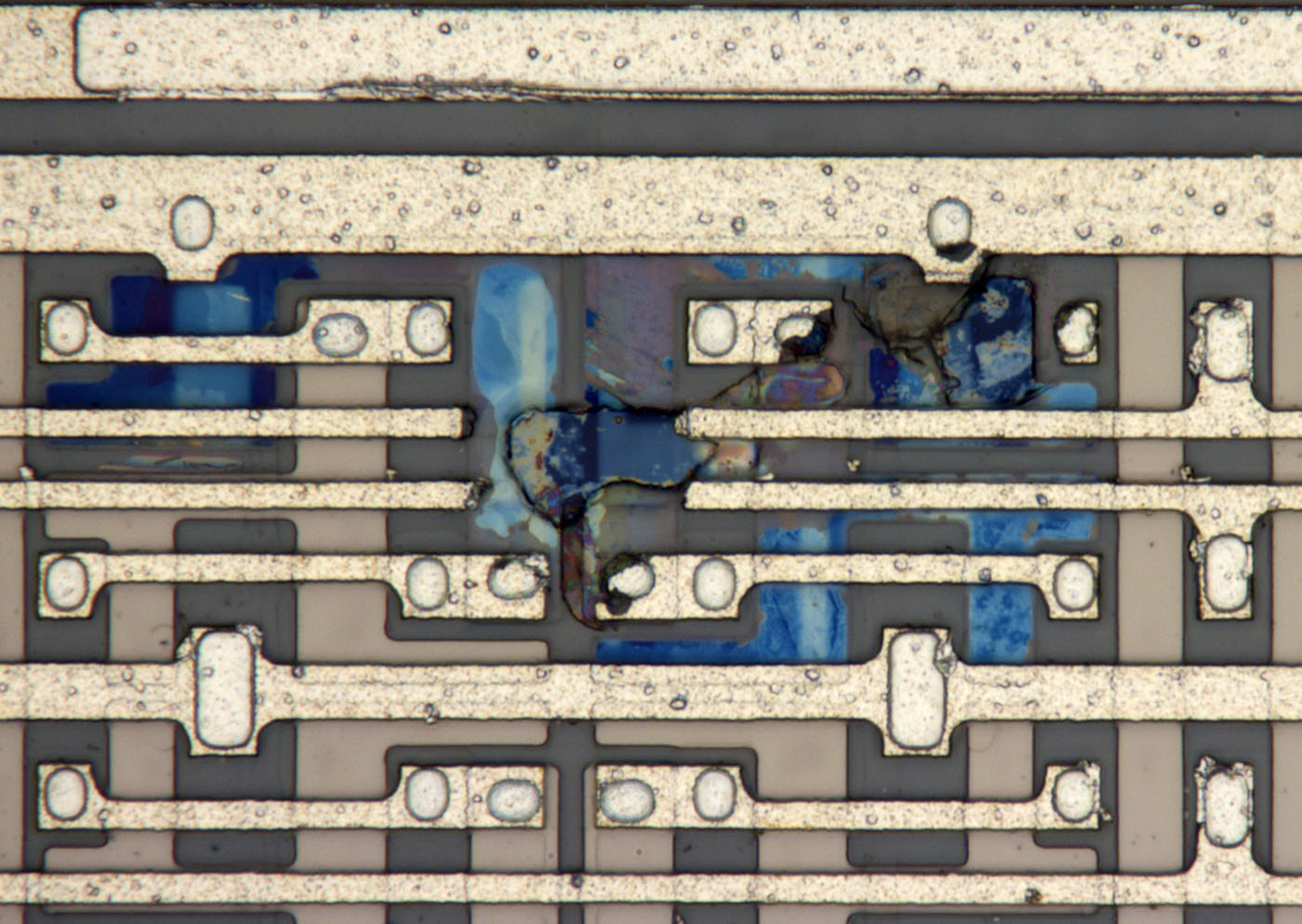

An der oberen Kante der Speicherfläche wurde ein Bereich stark überlastet und zerstört. Die beiden Bitleitungen dieser Zeile sind unterbrochen. Auch eine Leitung der rechten oberen Speicherzelle ist aufgeschmolzen. Die Polysiliziumlage, die die Gate-Elektroden ausbildet, hat sich teilweise stark verfärbt. Es scheint ein hoher Strom vom positiven Versorgungspotential in der Mitte des Bilds zu den GND-Potentialen geflossen zu sein.