Das КР132РУ5 ist ein russisches SRAM mit

einer Speichertiefe von 4kBit. Es ist kompatibel zum Intel 2147.

Die

Bezeichnung lautet nicht KP132PY5 wie man auf den ersten Blick meinen könnte. Es

handelt sich hier um kyrillische Schriftzeichen, in lateinischer Schrift stehen

sie für die Zeichenfolge KR132RU5.

Dem Datecode nach wurde der Chip in der Kalenderwoche 3 des Jahres 1990 produziert.

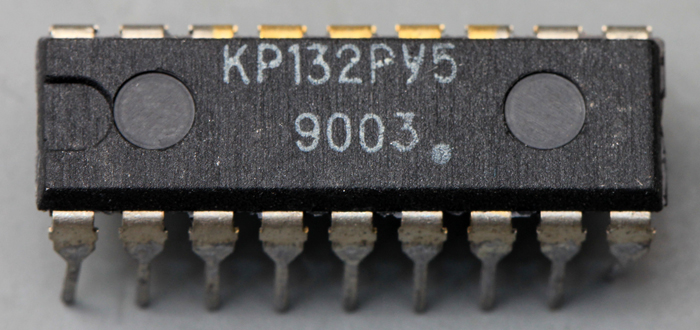

Für den KR132RU5 ist kein Datenblatt aufzutreiben, aber das Datenblatt des Intel 2147 enthält ein Blockschaltbild, das einen Eindruck vermittelt, was im Inneren zu erwarten ist.

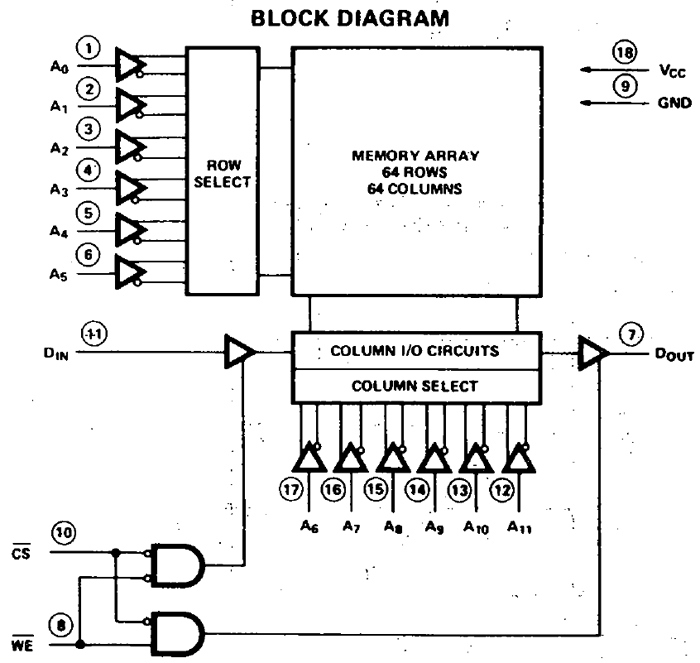

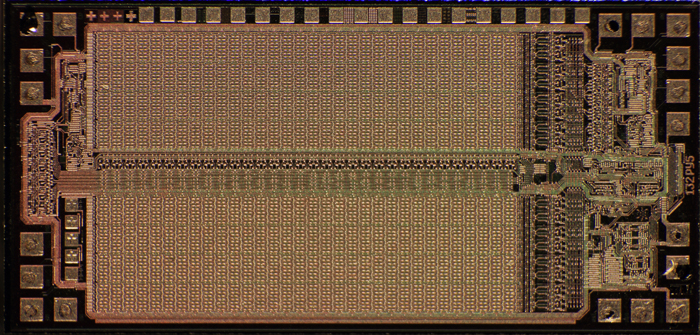

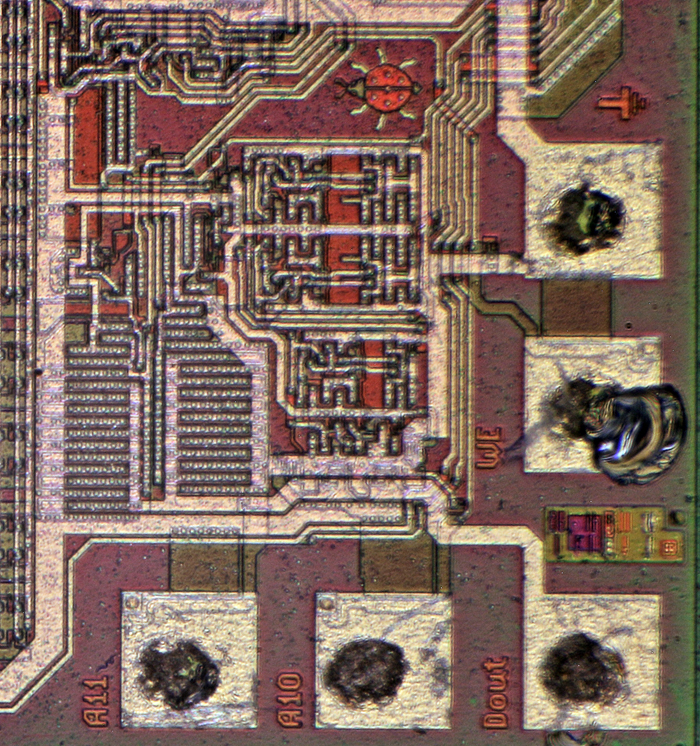

Obwohl das Package nur 18 Pins bietet, befinden sich auf dem Die 19 Bondpads, die auch alle kontaktiert wurden.

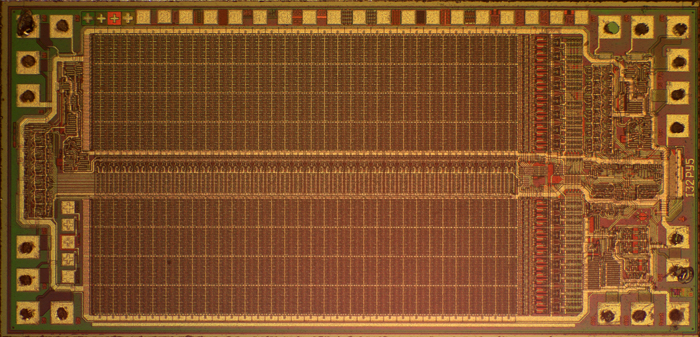

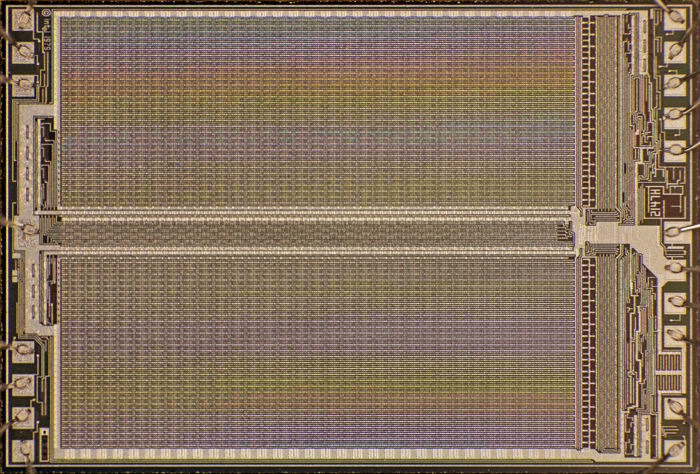

Einen Großteil der Fläche wird von zwei großen Speicherblöcken eingenommen. Hauptsächlich rechts davon befindet sich die Steuerungslogik. Einzelne Schaltungsteile sind auch links der Speicherblöcke und dazwischen angeordnet.

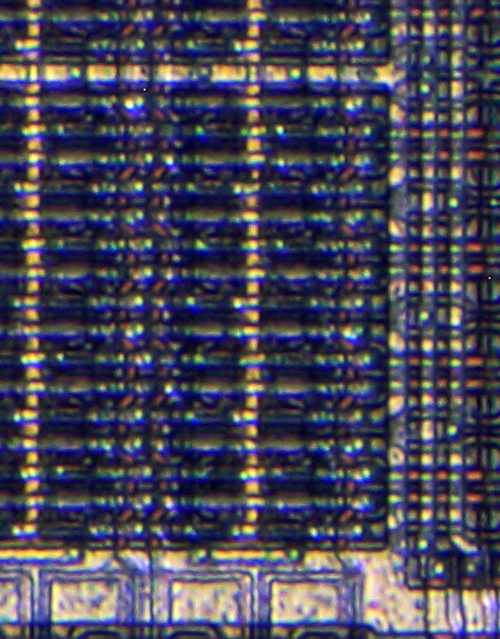

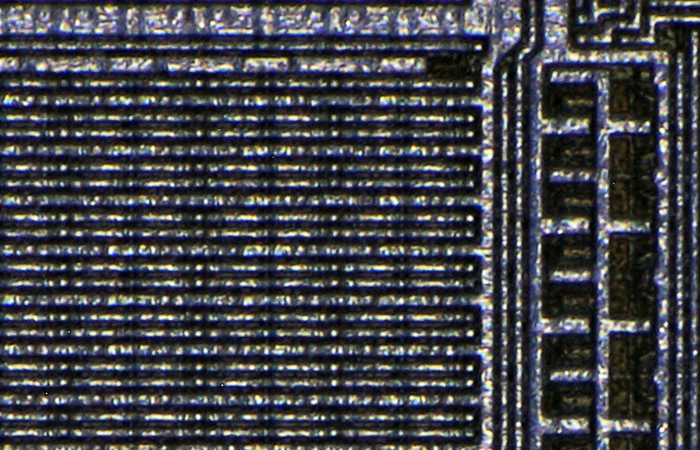

Die zwei Speicherblöcke enthalten jeweils

vier Zeilen, die sich wiederum in 32 Segmente gliedern. Bei genauerer

Betrachtung handelt es sich um 64 Segmente, die sich rechts und links der hellen

Leitungen anordnen. Jedes dieser Segmente muss folglich eine Speichertiefe von 8

Bit bereitstellen.

Das Datenblatt des Intel 2147 gibt mit 64 Zeilen und 64

Spalten die gleiche Speicherkonfiguration an.

An der rechten Kante des Dies ist die Bezeichnung 132РУ5 abgebildet.

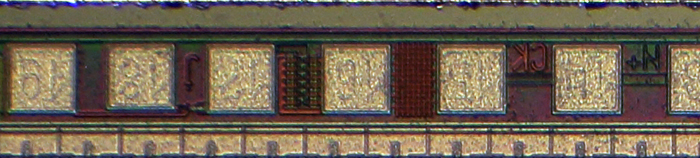

Das Die besitzt äußerst umfangreiche Teststrukturen.

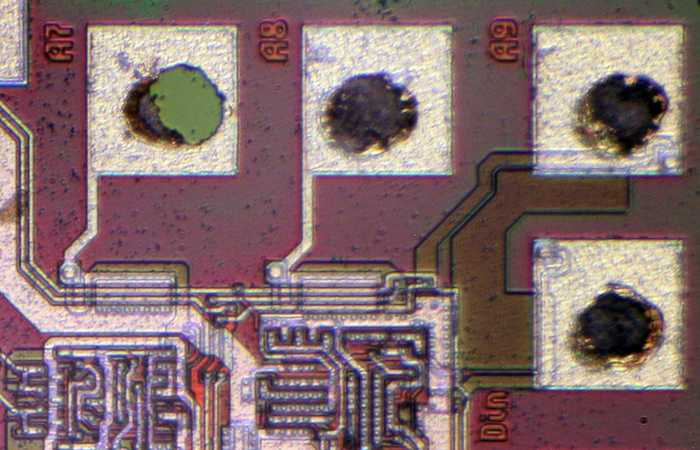

An der oberen Kante des Dies befinden sich 19 Testpads. Die Pads tragen fortlaufende Nummern. Zwischen den Pads sind die unterschiedlichsten Strukturen aufgebracht, die es ermöglichen sehr viele unterschiedliche Schaltungsteile zu vermessen.

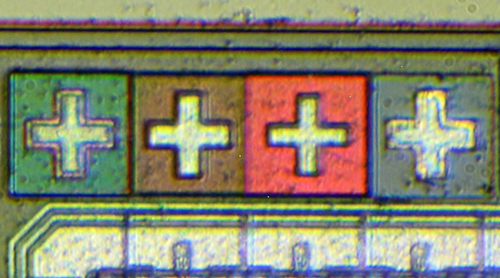

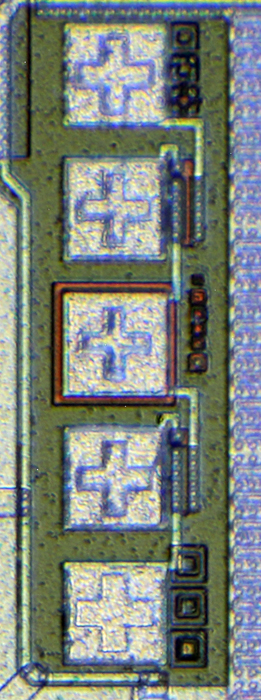

Links der 19 Testpads befinden sich vier Quadrate mit Fadenkreuzen. Entweder konnten darüber die verschiedenen Masken justiert oder später ihre korrekte Abbildung überprüft werden.

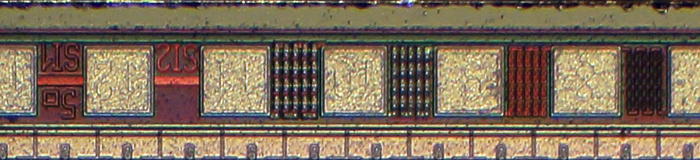

Links des Speicherbereichs befinden sich weitere Teststrukturen.

Die vier Quadrate an der Kante des Dies könnten Ätzmarker darstellen, die es ermöglichen einzelne Ätzprozesse rein optisch zu prüfen.

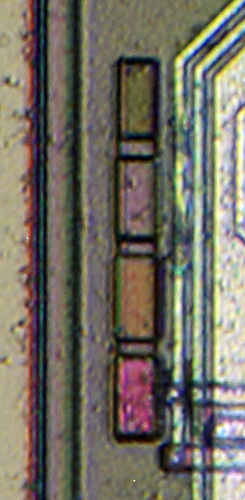

Näher am Speicherblock sind Teststrukturen aufgebracht, die sich über fünf Pads kontaktiert lassen und mit zwei daneben aufgebrachten, unterschiedlichen Transistoren verbunden sind. Nachdem es sich um einen CMOS-Speicher handelt ist davon auszugehen, dass hier ein nMOS- und ein pMOS-Transistor integriert wurde, deren Eigenschaften sich hier direkt und ohne den Einfluss umgebender Schaltungsteile vermessen lassen.

Neben den Kontaktpads befinden sich drei weitere Gruppen von Teststrukturen.

In der unteren rechten Ecke ist ein Bereich mit sehr kleinen Strukturen zu finden. Darüber lassen sich Aussagen über die Leistungsfähigkeit der optischen Prozesse treffen.

Weiter oben ist ein Käfer, wahrscheinlich ein Marienkäfer, im Die verewigt.

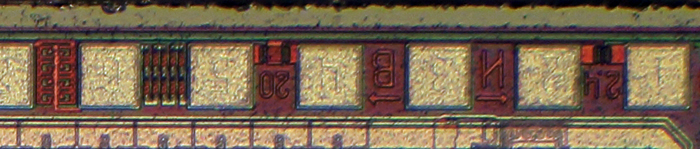

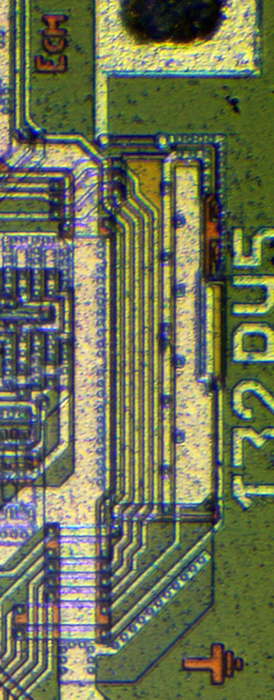

Jedes der 19 Bondpads ist mit seiner

Funktion beschriftet: A0 bis A11, CS, Din, Dout, E, ECM, "Ground" und WE.

Die

meisten Funktionen sind selbsterklärend. E steht für das positive Potential der

Versorgungsspannung, das Erdungssymbol steht für das Bezugspotential der

Versorgungsspannung. Offen bleibt die Funktion des Pins "ECM".

Oberhalb des Pads A11 ist bereits der Ausgangstreiber zu erkennen, der direkt mit Dout verbunden ist. Die zwei großen, rechteckigen Elemente stellen den Highside- und den Lowside-Transistor dar. An der Oberseite der Elemente befinden sich etwas anders angebundene Strukturen, von denen zwei Leitungen an der Seite der Endstufentransistoren entlang führen. Es handelt sich mit ziemlicher Sicherheit um Treibertransistoren für die eigentlichen Endstufentransistoren.

An den Bondpads befinden sich Schutzstrukturen in leicht unterschiedlichen Ausführungen.

Bei den linken beiden Bondpads führt die Metalllage zuerst ein Stück nach unten, wo sie gleichzeitig eine grünlich erscheinende Schleife kontaktiert und als Gateelektrode ein Stück nach rechts geführt wird. Die Schleife stellt einen Schutzwiderstand dar, der zum MOSFET führt, der sich unter der Gateelektrode befindet. Den Sourceanschluss bildet eine Fläche des grünlichen Materials, das an die breite Versorgungsleitung darunter angebunden ist. Im normalen Betrieb ist der MOSFET inaktiv. Bei einem ESD-Impuls wird der MOSFET allerdings leitend und aktiviert dabei gleichzeitig einen parasitären Bipolartransistor im Substrat, der den ESD-Impuls ableitet. Das eigentliche Signal wird rechts aus der Schutzstruktur heraus geleitet und nach unten geführt.

Interessant ist, dass die Schutzstrukturen teilweise an das Versorgungspotential und teilweise an das Massepotential angebunden sind. Auch bei einer Anbindung an das Massepotential und einem Highpegel am Pad leitet der MOSFET nicht, da die Struktur keinem gewöhnlichen MOSFET im Sinne der auf dem Die integrierten MOSFETs entspricht. Gewöhnliche MOSFETs besitzen Gateelektroden aus Polysilizium und darunter eine dünne Oxidschicht. Unter der Metallelektrode der Schutzstruktur befindet sich allerdings eine dicke Oxidschicht, wodurch sich die Thresholdspannung verschiebt und der MOSFET auch mit einem nicht allzu hohen Highpegel am Bondpad inaktiv bleibt.

Bei einigen Bondpads befinden sich die Schutzstrukturen direkt am beziehungsweise unter dem Bondpad, wie es hier rechts zu sehen ist. Beim unteren Bondpad befindet sich in der oberen linken Ecke der Kontakt zur Widerstandsschleife, deren Form unter der Metallschicht gerade so erkennbar ist. Das Bondpad selbst bildet die Gateelektrode der Schutzstruktur. Der MOSFET bildet sich darunter über die Signalleitung und der großen, grünlichen Fläche, die das Massepotential führt.

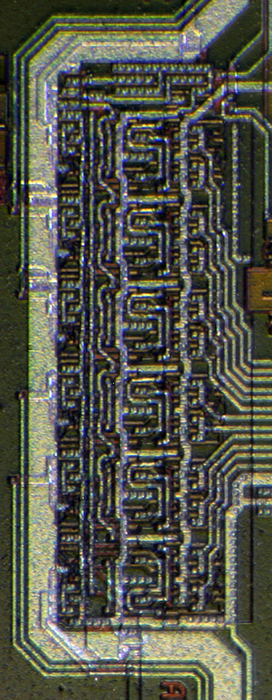

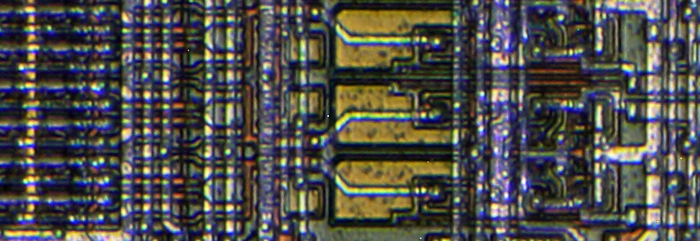

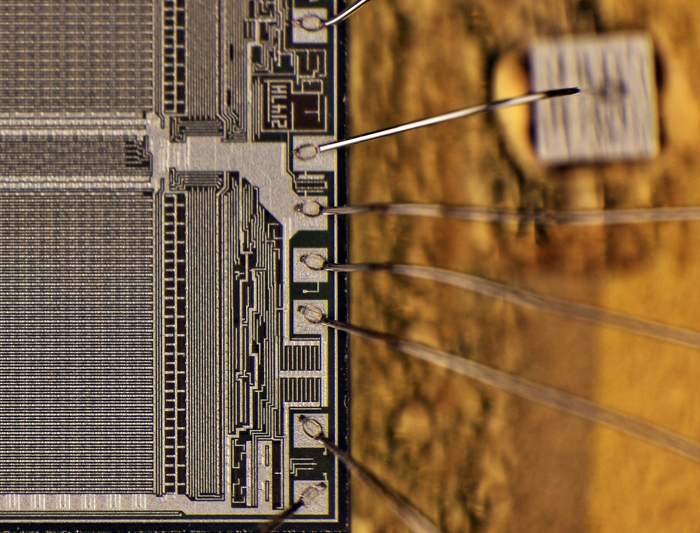

Ganz links und im rechten oberen Bereich des Dies befindet sich jeweils ein relativ großer, gleichmäßig strukturierter Funktionsblock. Es handelt sich dabei um die sechs Transceiver, die die Potentiale der Adressleitungen entgegen nehmen und differentiell ausgeben. Die sechs Transceiver sind realtiv gut zu erkennen.

Bei den linken Transceivern werden von

links die Potentiale der ersten sechs Adressleitungen zugeführt. Die

differentiellen Ausgänge führen zwölf Leitungen der Metalllage zwischen die zwei

großen Speicherblöcke.

Die rechten Transceiver sind gespiegelt angeordnet.

Die Ausgänge münden in acht vertikale Leitungen, die die komplette Breite des

Speicherblocks überstreichen. Je eine zusätzliche Leitung ist exklusiv einem der

zwei großen Speicherblöcke zugeordnet, worüber eine Adressleitung die

Umschaltung zwischen den Blöcken realisiert. Zwei weitere Leitungen werden

anderweitig verarbeitet.

Im Bereich zwischen den Speicherblöcken ist gut zu erkennen wie bei jeder Spalte andere Adressleitungen kontaktiert werden und so die Adressleitungen immer ein andere Spalte aktivieren.

Oberhalb der Adressleitungen befindet sich

noch ein relativ kleiner Schaltungsteil, dessen Funktion sich nicht mit letzter

Sicherheit zuordnen lässt.

Wahrscheinlich handelt es sich um die

Push-Pull-Treiber für die Spaltenauswahlleitungen. Es bleiben drei ungeklärte

Potentiale, die bei jeder Spalte genutzt werden. Eines davon dürfte ein

Enable-Signal darstellen.

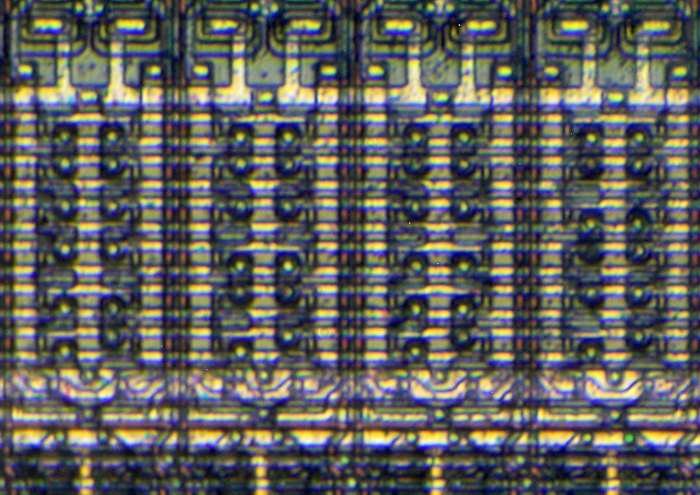

Die Strukturen der Speicherzellen selbst lassen sich ansatzweise auflösen. Sie überlagern sich allerdings zu stark als dass die einzelnen Elemente und deren Funktion bestimmt werden könnten. Es ist gerade noch die Symmetrie links und rechts der hier gelb dargestellten Leitung der Metalllage zu erkennen.

Rechts im Bild endet der Speicherbereich und es sind die acht differentiellen Datenleitungen zu erkennen. Es wechseln sich immer eine rötliche und eine graue Leitung ab.

Die Anbindung der Datenleitungen und die Platzierung der Durchkontaktierungen im Speicherbereich, die mit anderen Belichtungen noch besser zu erkennen sind, zeigen, dass immer zwei der horizontalen Zeilen eine Speicherzelle darstellen.

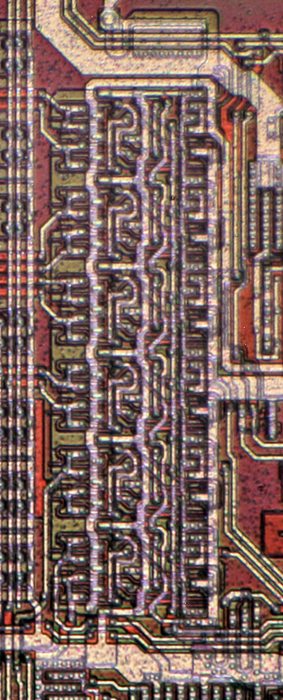

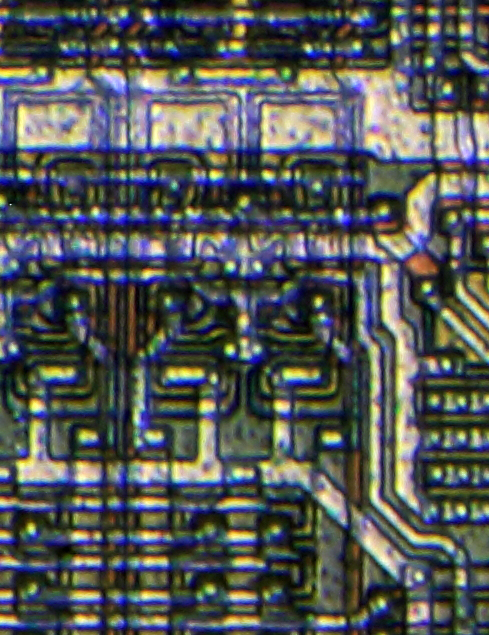

Das rechte Ende der Speicherblöcke ist deutlich komplexer als die

Spaltenauswahl. Hier ist nur der obere Speicherblock zu sehen. Auf dieser Seite,

an der die differentiellen Datenleitungen einer jeder Zeile ankommen, muss sich

ein Großteil der Logik zum Lesen und Schreiben der Daten befinden.

Üblicherweise müssen zum Lesen von Daten die differentiellen Datenleitungen

vorgeladen werden. Dieser Teil der Ausleselogik könnte sich der optischen

Erscheinung nach auch an der linken Kante des Speicherblocks befinden. Außerdem

ist eine Symmetrierung notwendig, damit die jeweilige Information sicher

ausgelesen werden kann. Zuletzt müssen die Signale der Zeilen auf den Ausgang

gemultiplext werden.

Für das Schreiben benötigt jede Zeile dann noch eine

Umschaltung und falls noch nicht erfolgt eine Konvertierung des Datenstroms in

ein differentielles Signal.

Mittig sind deutlich 16 Funktionsblöcke

erkennbar, die jeweils eine größere rechteckige Fläche beinhalten. Nachdem sich

davor viermal acht Speicherzeilen befinden, muss dazwischen bereits eine Art

Multiplexing erfolgen.

Rechts befinden sich acht senkrecht angeordnete

differentielle Adressleitungen und eine einzelne Adressleitung. Letztere

aktiviert den Speicherblock. Die acht differentiellen Adressleitungen

ermöglichen die Auswahl von 16 Zeilen, was zeigt, dass es sich bei den 16

größeren Funktionsblöcken nicht mehr um eine differentielle Signalverarbeitung

handelt, auch wenn die optische Erscheinung diesen Anschein erweckt.

Von links nach rechts durchlaufen die Datenleitungen zuerst drei Spalten, bevor die Funktionsblöcke mit den großen, rechteckigen Flächen folgen.

Da keine größeren Multiplexingstrukturen

zu erkennen sind, kann man davon ausgehen, dass die 16 großen Elemente die

Speicherzeilen nicht blockweise auslesen, sondern dass ein Element zwischen zwei

gegenüberliegenden Speicherzeilen umgeschaltet wird.

Die ersten

beiden Spalten erhalten fünf Potentiale, das Massepotential und vier Potentiale,

die dem Anschein nach zu den Ausgangstreibern und zu einer darüber angeordneten

Schaltung führen. Es könnte sich hier um die Auskopplung der ausgelesenen Pegel

handeln.

Die dritte Spalte erhält das Versorgungspotential und zwei weitere

Potentiale, die sich nicht weiter zuordnen lassen. Darunter sind zwei Quadrate

zu erkennen, die Kapazitäten darstellen könnten. Hier oder in der Spalte davor

muss eine Art Multiplexing und Signalwandlung erfolgen, da für zwei

differentielle Zeilensignale nur ein Potential zum folgenden Funktionsblock

weitergeleitet wird.

Es folgt der Funktionsblock, der mit den relativ großen, braunen Flächen beginnt und rechts endet wo die Spalte mit den differentiellen Adressleitungen von oben nach unten führt. Es könnte sich hier um die Schaltungsteile für den Schreibvorgang handeln.

Bei den obersten Zeilen ist die

Zeilenauswahlmimik zu erkennen.

Hier ist zu sehen, dass es sich bei den

größeren Funktionsblöcken nicht um eine differentielle Signalverarbeitung,

sondern um einzelne Schaltungsteile handelt. Das über eine breite Metallleitung

mittig zugeführte Massepotential schalten fünf Transistoren nur dann nicht zur

jeweiligen Zeile durch, wenn über die Adressleitungen genau diese ausgewählt

wird. Für jeden Funktionsblock existieren einmal fünf Transistoren zur Auswahl

desselben.

Die Funktion des mit ECM bezeichneten Bondpads lässt sich nicht endgültig klären. Das Potential führt ohne ESD-Schutz zu einer großen Struktur an der rechten Kante des Dies.

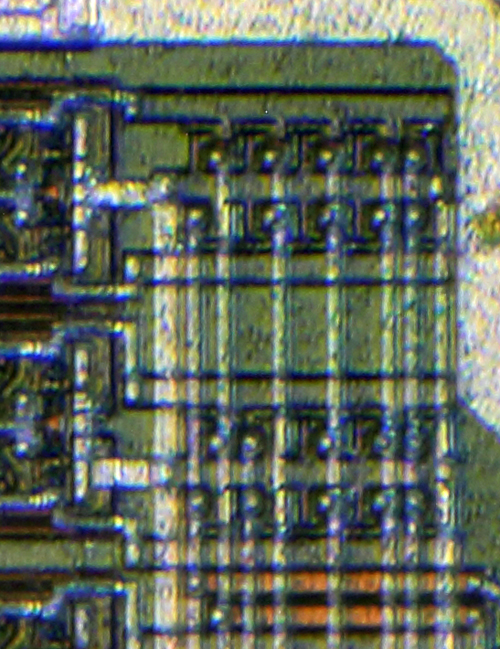

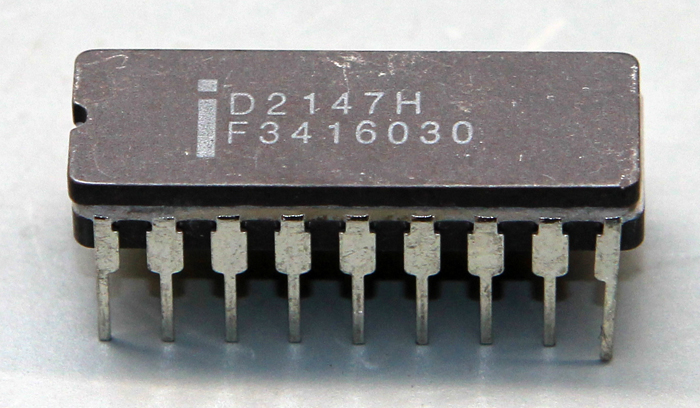

Die pinkompatible Intel-Variante des 4kBit-SRAM trägt die Bezeichnung D2147 und befindet sich in einem Keramikgehäuse.

Es zeigt sich, dass die Strukturen im D2147 denen im КР132РУ5 ähneln. Im Detail unterscheidet sich der Aufbau aber. Der Speicherplatz ist in zwei horizontale Bänke aufgeteilt. Die Steuerung befindet sich ebenfalls zu einem Großteil rechts der Speicherbereiche. Im rechten unteren Bereich ist wie beim КР132РУ5 der Ausgangstreiber angeordnet. Links des Speichers und in den rechten Ecken des Dies befinden sich die Transceiver, die die Adressleitungen aufbereiten. Hier handelt es sich allerdings um eine Aufteilung 7 zu 5 und nicht 6 zu 6 wie beim КР132РУ5. Intel kam fast ohne Teststrukturen aus. Nur in der linken unteren Ecke befindet sich eine Abbildung des Maskensatzes.

Das Bondpad, das dem ECM-Pad beim КР132РУ5 entsprechen müsste, ist über einen kleinen Sockel mit dem Potential des Gehäuses verbunden. Auch hier ist auf dem Die eine nicht identifizierbare Struktur an das Bondpad angebunden. Wahrscheinlich handelt es sich um eine diodenähnliche Funktion, die zwischen dem Bezugspotential und dem Gehäusepotential eine gewisse Spannung einstellt und so einen sicheren Betrieb der integrierten Schaltungen garantiert.

Der Aufbau der Speicherzellen selbst erscheint abweichend zu den Strukturen im КР132РУ5. Horizontal scheint jede Speicherzelle mit einem Potential, vermutlich einem Versorgungspotential, verbunden zu sein.