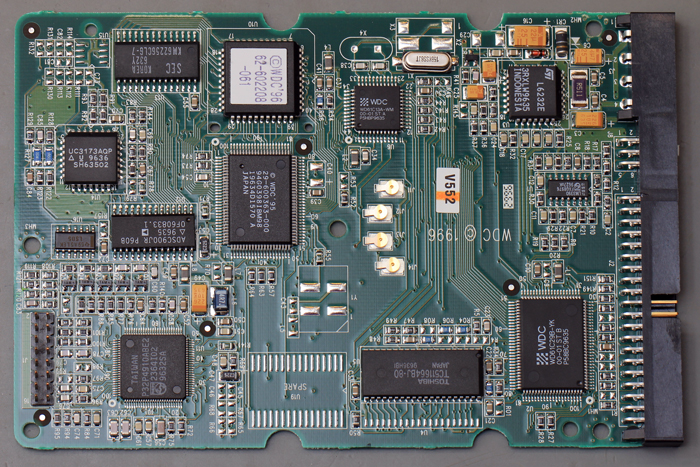

Diese Western Digital Festplatte stammt aus dem Jahr 1996. Die Modellbezeichnung lautet Caviar 22100. Die Festplatte bietet 2111,8 MB Speicherplatz.

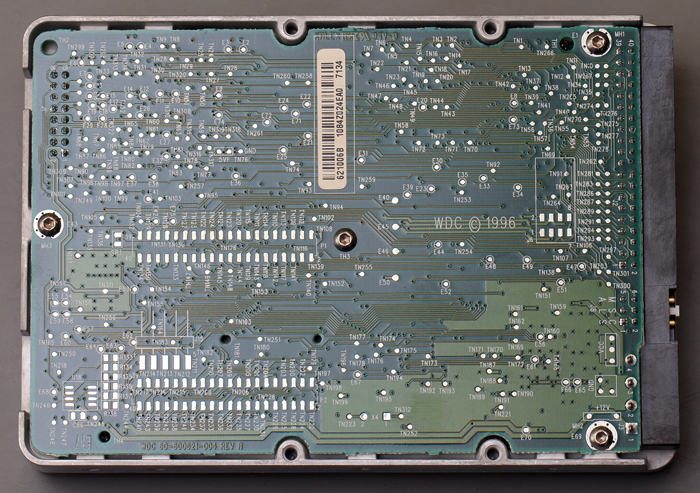

Die Unterseite der Festplatte ist vollständig von der Steuerungsplatine bedeckt.

An der oberen Kante der Platine befindet sich ein Hinweis auf den Platinenhersteller Kalex. Die WD-Bezeichnung der Platine lautet "WDC 60-600621-004 REV A".

Auch wenn einzelne Bestückplätze vorhanden

sind, befinden sich auf der Unterseite keine Bauteile.

Es wurden sehr viele

Testpunkte in das Layout integriert. Erkennbar sind zwei Arten von Testpunkten.

Die Bezeichnungen der einen beginnen mit den Buchstaben TN, die anderen mit

einem E. Letztere werden noch einmal in zwei Gruppen aufgeteilt, indem manche

mit Kreisen um die Testpunkte ausgestattet wurden und andere nicht. Zwei

Padreihen scheinen Bestückplätze für SMD-Stiftleisten oder etwas ähnliches

darzustellen. Dazwischen befinden sich fünf Pads, die einen JTAG-Anschluss

darstellen könnten.

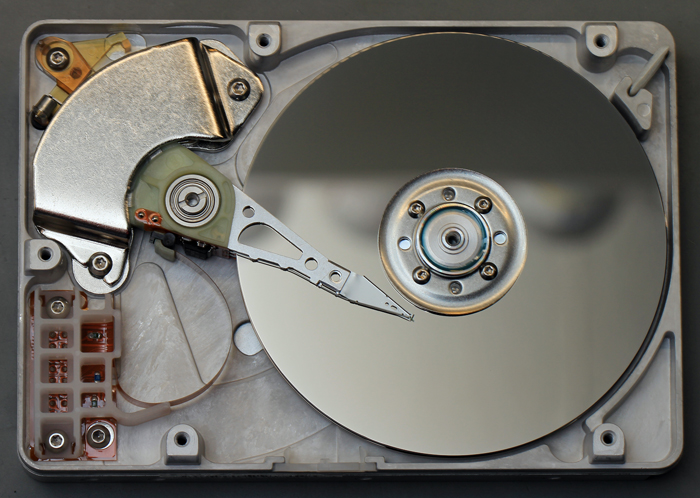

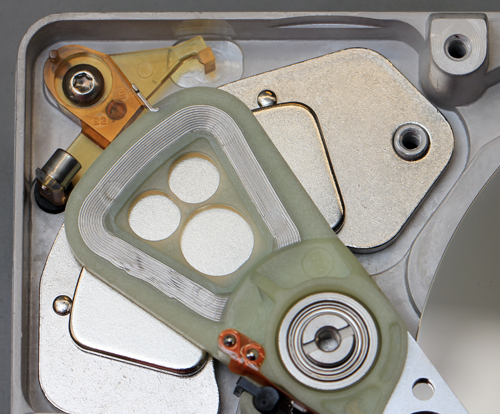

Der Deckel der Festplatte hält einen großzügigen Abstand zum darunter liegenden Aluminiumkörper. Die Abdichtung realisiert ein leitfähiges Klebeband. Allzu robust ist diese Lösung nicht. Wird das Klebeband beim Einschieben in eine Festplattenhalterung beschädigt, so kann Staub in das Gehäuse eindringen und die Festplatte zerstören.

Im Gehäuse befinden sich zwei Speicherscheiben.

Der Arm mit den Schreib-/Leseköpfen

befindet sich in der Parkposition im inneren Bereich der Scheiben.

Unter den

Scheiben befindet sich ein Schlitz im Gehäuse, der abgeklebt wurde. Der

Durchbruch muss wohl während der Fertigung notwendig gewesen sein.

Es zeigt sich, dass das Gehäuse kein diskretes Druckausgleichselement besitzt. Vermutlich waren die vorhandenen Undichtigkeiten ausreichend und aus Sicht des möglichen Schmutzeintritts unkritisch.

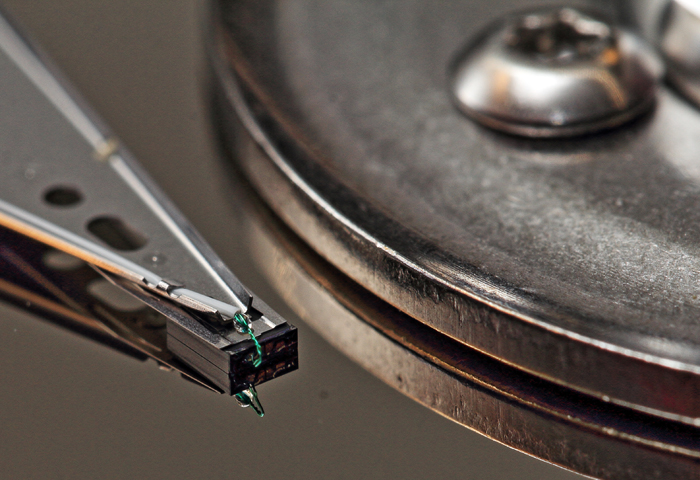

Der Schreib-/Lesekopf liegt im Ruhezustand auf der Scheibe auf. Erst bei einer gewissen Drehzahl hebt sich das Element durch das entstehende Luftpolster. Dieser Umstand ist auch der Grund warum eine Parkposition notwendig ist.

Von oben werden dem Schreib-/Lesekopf zwei verdrillte Drähte zugeführt. Am Ende des weißen Schutzröhrchens sind die Drähte mit einem Klebstofftropfen fixiert.

Von unten betrachtet zeigen sich verschiedene Oberflächen, die eine interessante geometrische Form bilden. Die Struktur der Unterseite hat keine elektrische Funktion, sondern optimiert nur die aerodynamischen Eigenschaften des Schreib-/Lesekopfs. Der elektromagnetisch wirksame Teil befindet sich in dem gerade noch erkennbaren Streifen ganz rechts.

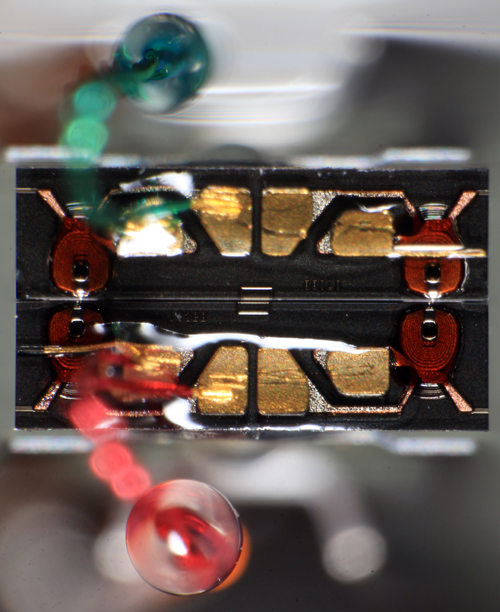

Jede Speicherplatte wird beidseitig von

einem Schreib-/Lesekopf bedient. Entfernt man die Speicherplatten, so kommen die

beiden Schreib-/Leseköpfe aufeinander zu liegen. Es zeigt sich, dass die

Elemente sehr ähnlich, wenn nicht sogar gleich aufgebaut sind. Die Strukturen

erscheinen außerdem symmetrisch.

Bei beiden Sensoren wurde das äußere

Element verdrahtet. Während für den oberen Schreib-/Lesekopf grüner Lackdraht

verwendet wurde, kam beim unteren roter Lackdraht zu Einsatz.

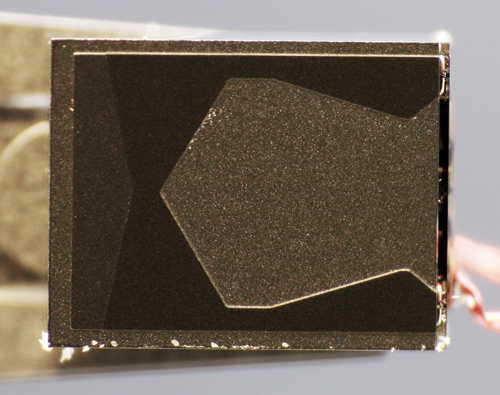

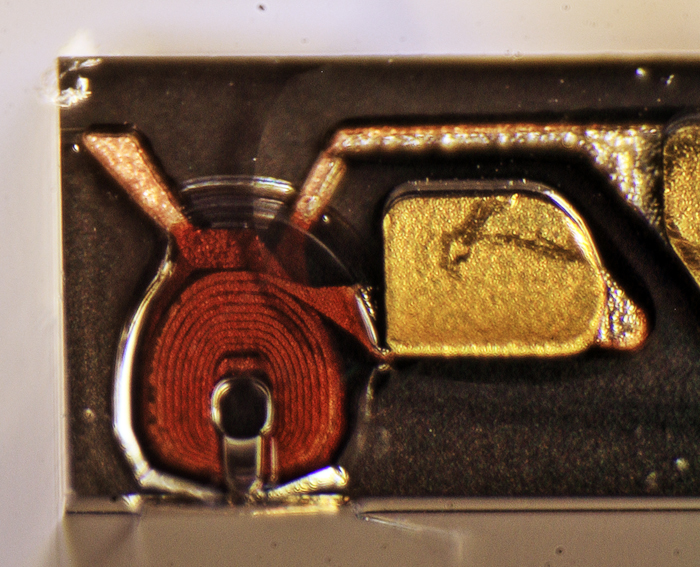

Das aktive Element befindet sich am Rand

des Schreib-/Lesekopfs. Es besteht aus einer Spulenstruktur, die an zwei

Kontaktpads angeschlossen ist.

Die Aufgabe des dritten Kontakts lässt sich

nicht mit letzter Sicherheit klären. Der optischen Erscheinung nach handelt es

sich nicht um einen alternativen Kontakt für den hinteren Spulenanschluss. Auf

beiden Seiten scheint die gleiche Struktur nicht kontaktiert worden zu sein.

In der Mitte der Spule befindet sich ein silbernes Element, dass höchstwahrscheinlich den magnetischen Fluss konzentriert und lenkt.

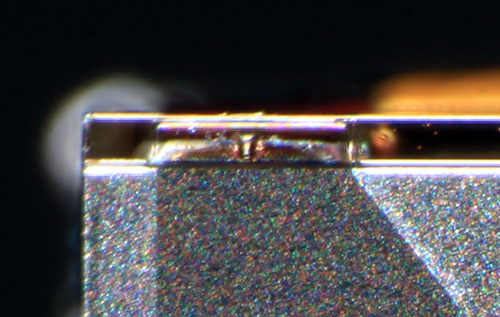

Das silberne Element lenkt den magnetischen Fluss auf die Unterseite des Schreib-/Lesekopfs, dort ist es nur etwas mehr als 25µm lang und nicht ganz 10µm breit. Der Schreib-/Lesevorgang erfolgt über einen gerade noch zu erkennenden Spalt am unteren Ende des silbernen Elements. Dort schließt sich der magnetische Fluss über die Speicherscheiben und der jeweilige Bereich wird entsprechend magnetisiert oder das Magnetfeld ausgelesen.

Bei neueren Festplatten ist der Aufbau des Schreib-/Lesekopfs komplexer und filigraner.

Noch auf dem Arm, der die Schreib-/Leseköpfe trägt, befindet sich mit dem 775430FSSL eine spezielle Verstärkerstufe.

Im Vordergrund sind die vier Leitungen der Schreib-/Leseköpfe zu sehen. Der Keramikkondensator stützt das Versorgungspotential.

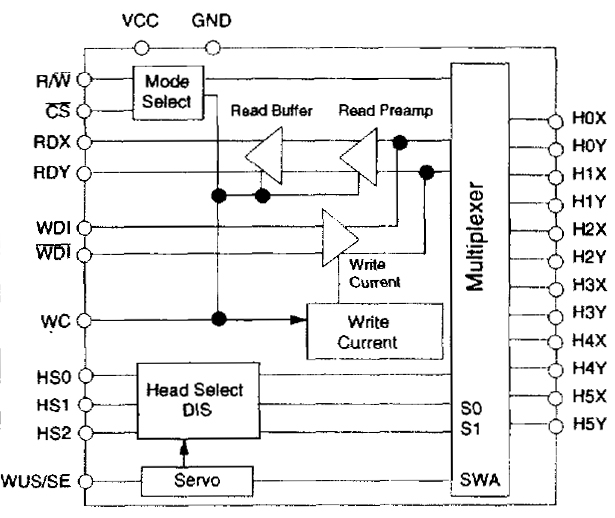

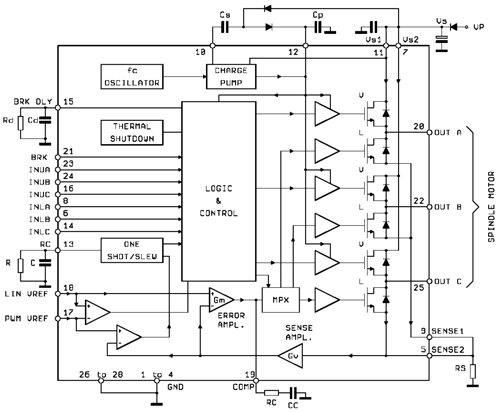

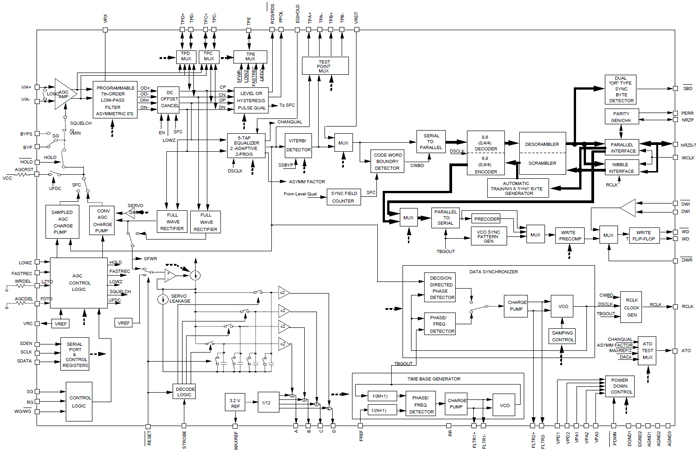

Das Datenblatt zeigt das Blockschaltbild

des sechskanaligen Verstärkers.

Enthalten ist ein Multiplexer, der die

einzelnen Kanäle zusammenfasst. Über drei beziehungsweise hier zwei Pins kann

der gewünschte Ausgang ausgewählt werden.

Beim Lesevorgang verstärkt ein Vorverstärker das Signal des Schreib-/Lesekopfs das schließlich über einen Puffer ausgegeben wird. Das Eingangssignal ist verständlicherweise relativ klein und hat eine hohe Bandbreite. Das Datenblatt gibt dazu passende Spezifikationen an: Verstärkungsfaktor 300, Bandbreite 70MHz, Eingangskapazität 11pF, Dynamikbereich 0,2mV bis 2,6mV.

Beim Schreibvorgang sorgt der Chip dafür,

dass abhängig vom Pegel am Eingang ein Strom vom X- zum Y-Ausgang oder vom Y-

zum X-Ausgang fließt. Die Anstiegs- und Abfallzeiten bewegen sich laut

Datenblatt im kleinen, einstelligen Nanosekundenbereich. Die Bandbreite beträgt

1MHz.

Die Höhe des Stroms zum Schreiben von Informationen lässt sich über den

WC-Pin von außen einstellen. Direkt beim Chip befindet sich in dieser Festplatte

ein 10kOhm-Widerstand, der den minimalen Strom mit 5mA festlegt. Laut Datenblatt

sind bis zu 20mA möglich. Das Potential des WC-Pins wird allerdings zusätzlich

nach außen zur Steuerungsplatine geführt, wodurch sich der Strom von dort aus

auf Werte über 5mA regeln lässt.

Der Pin WUS/SE hat eine Doppelfunktion. Er kann Fehler des Schreibvorgangs kommunizieren oder das Aktivieren des "Servo Write Mode" ermöglichen. In diesem Modus wird das Eingangssignal über alle Kanäle ausgegeben.

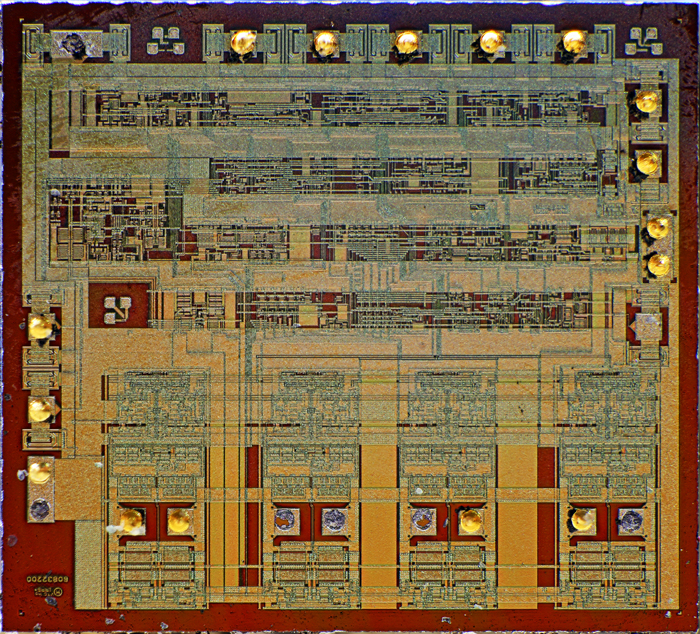

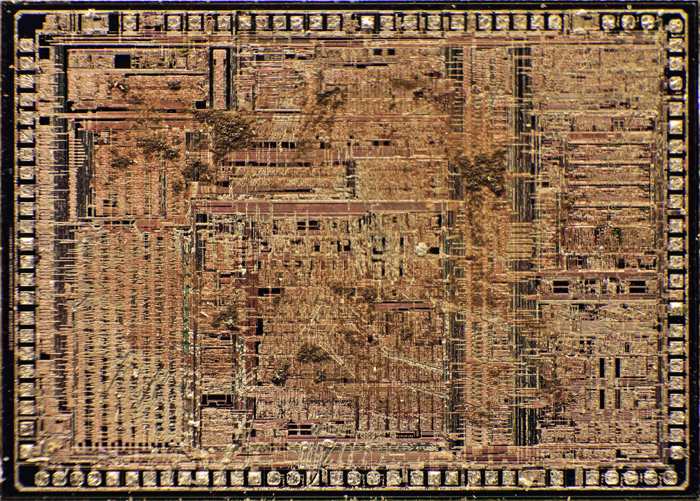

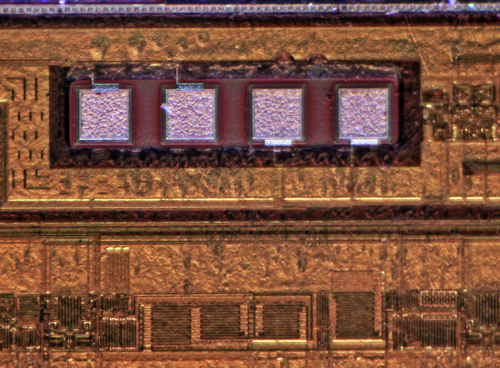

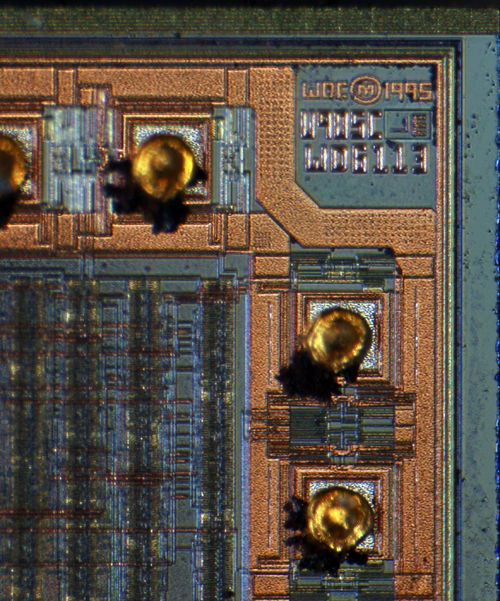

Das im Package enthaltene Die ist relativ groß. Darauf sind neben den eigentlichen Schaltungsteilen drei unterschiedliche Teststrukturen zu erkennen.

An der unteren Kante sind die Kontaktpads

der vier differentiellen Ein- und Ausgänge platziert.

Die minimale

Strukturbreite ist relativ klein, wodurch sich nicht alles auflösen lässt,

dennoch kann man die Funktionsblöcke um die Ein-/Ausgänge erahnen. Direkt unter

den Pads befinden sich jeweils vier große Strukturen, die mit ziemlicher

Sicherheit die Ausgangstransistoren darstellen. Zwischen den Pads führen zwei

dünne Leitungen von oben zu den Transistoren. Dabei dürfte es sich um

differentielle Ansteuerung handeln. Oberhalb der vier Kanäle befinden sich vier

gleiche Strukturen, die vermutlich den Eingangsverstärker darstellen.

Die

großen Abstände zwischen den Kanälen sorgen für eine niedrige Überkopplung. Auch

die Platzierung der Bondpads wurde optimal gewählt. Durch die Verlegung vom Rand

ein Stück ins Innere wurde genug Platz frei, um die Ausgangstreiber und die

Eingangsverstärker um die Bondpads herum anzuordnen, was elektrisch noch idealer

ist.

VTC steht laut Datenblatt für "Value the

Customer".

Der Maskensatz stammt aus dem Jahr 1995.

Die interne

Bezeichnung des Chips lautete anscheinend "60832200".

Der Arm der Schreib-/Leseköpfe besitzt hinter dem Gelenk eine Spule, die im Kunststoff des Arms eingearbeitet ist und über die flexible Leiterplatte kontaktiert wird. Die Spule befindet sich in einem zweiteiligen Metallkäfig. Am unteren Element ist ein relativ starker Magnet angebracht. Eine hohe Flussdichte ist notwendig, da sie die Grundlage bietet, um den Arm schnell bewegen zu können. Eine hohe Windungszahl ist nicht wünschenswert, da sie zu hohen Induktivitäten führen würde, was wiederum kontraproduktiv für schnelle Stromänderungen wäre. Hohe Ströme könnten das Nutzsignale negativ beeinflussen. Außerdem wären unpraktisch hohe Spannungen notwendig, um schnell hohe Ströme einstellen zu können. Ein starker Permanentmagnet ist hier die beste Wahl.

Das Kunststoffelement hinter dem Arm

begrenzt in Kombination mit einem Metallstreifen am Arm die Bewegung des

selbigen.

Ein Magnet am linken Anschlag sorgt für eine stabile Parkposition

im inneren Bereich der Speicherplatten.

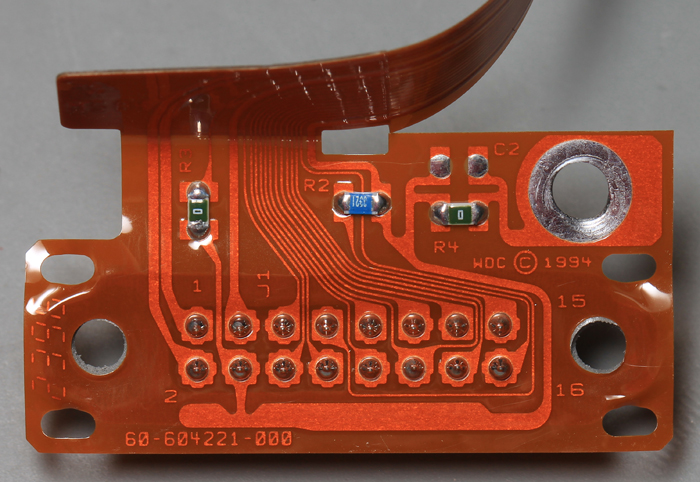

Die flexible Leiterplatte verbindet den

Arm der Schreib-/Leseköpfe mit einer Buchsenleiste, die durch das Alugehäuse die

Steuerungsplatine kontaktiert.

Das Copyright-Zeichen zeigt, dass das Layout

aus dem Jahr 1994 stammt.

Die linken beiden Pins 1 und 2 führen zur

Spule, die den Arm bewegt.

Die zwei darauf folgenden Pins liefern eine

Versorgungsspannung und ein Massepotential.

Die restlichen Pins übertragen

Informationen vom und zum Verstärker für die Schreib- und Leseköpfe.

Interessant ist der Umgang mit dem

Massepotential. Der 0Ω-Widerstand links verbindet das Massepotential mit der

Trägerstruktur der Schreib-/Leseköpfe. Der zugehörige Kontakt ist weiter oben

als Lötstelle neben dem Verstärker zu sehen. Der Bestückplatz ermöglicht es die

Trägerstruktur hochohmiger anzubinden, falls die starre Anbindung zu

problematisch hohen Ströme auf der Masseleitung führt.

Eine weitere Option

ist rechts zu sehen. Der 0Ω-Widerstand R4 verbindet das Massepotential über

eine Schraube direkt mit dem Gehäuse. Mit Hilfe des zusätzlichen Bestückplatzes

C2 kann das lokale Massepotential kapazitiv oder über eine RC-Kombination an das

Gehäuse angebunden werden. Auf diese Weise lässt sich das Massekonzept so

optimieren, dass ein möglichst störungsfreier Betrieb sichergestellt ist.

Der Widerstand R2 verbindet das Massepotential mit einem anderen Pin der Steuerungsplatine. Der Widerstand hat auf den ersten Blick keinen Nutzwert. Höchstwahrscheinlich wurde der Widerstand genutzt, um für mehrere Festplattenmodelle die selbe Steuerungsplatine verwenden zu können. Der Wert des Widerstands kommuniziert dann die jeweilige Variante an die Software der Steuerungsplatine.

Unter der Steuerungsplatine befindet sich die Buchsenleiste, die die internen Signale weiterleitet, der Brushless-DC-Motor und eine Druckausgleichsmembran.

Die Steuerungsplatine ist dem Anschein

nach vierlagig aufgebaut. Abgesehen von den Stiftleisten wurden nur SMT-Bauteile

eingesetzt.

Unter anderem an der unteren Kante sind Bestückoptionen zu

erkennen.

Vier Federkontakte kontaktieren den im Gehäuse eingearbeiteten Brushless-DC-Motor, der die Speicherscheiben antreibt.

Der Schaltungsteil im rechten oberen Bereich erinnert auf den ersten Blick an einen Spannungsregler. Tatsächlich arbeitet aber die ganze Festplatte mit den von außen zur Verfügung gestellten 5V- und 12V-Potentialen.

Die hier zu sehende Schaltung steuert den

Brushless-DC-Motor. Kernkomponente ist der L6232E von ST Microeletronics.

Der

Motor besitzt keine direkte Rotorlagerückmeldung. Die BLDC-Endstufe erwartet an

ihren sechs Eingängen die notwendige Ansteuersignale, so dass der Motor wie

gewünscht läuft. Da das Gesamtsystem wenig Toleranz, Varianz und Alterung

beinhaltet reicht vermutlich eine gesteuerte Ansteuerung um ein Anlaufen und

einen stabilen Betrieb zu gewährleisten.

Das Datenblatt des L6232E enthält ein Blockschaltbild, das alle Funktionen darstellt. Dazu gehört unter anderem ein interner Oszillator und eine Ladungspumpe, die das notwendige höhere Potential darstellt, damit die Highside-Transistoren der Endstufe angesteuert werden können.

Die eigentlichen Endstufen stellen drei Halbbrücken mit Freilaufdioden dar. Der Summenstrom der Halbbrücken wird über einen externen Widerstand bestimmt und nach diversen Verstärkerstufen der Lowside-Ansteuerung zugeführt, um eine Stromregelung zu ermöglichen.

Der Baustein enthält eine Bremsfunktion,

die aktiv wird, wenn die Versorgungsspannung unter einen Grenzwert fällt und

sich über eine RC-Glied verzögern lässt.

Das Datenblatt beschreibt eine

interessante Applikation in Kombination mit dieser Funktion. Nach dem Abschalten

der Versorgung müssen die Schreib-/Leseköpfe noch in die Parkposition gebracht

werden, bevor die Magnetscheiben zur Ruhe kommen und die Schreib-/Leseköpfe

aufsetzten. Durch den Einsatz von Dioden kann der Brushless-DC-Motor nach dem

Abschalten als Generator genutzt werden, der im Auslaufen die Energie bereit

stellt, die notwendig ist um die Schreib-/Leseköpfe in die Parkposition zu

bewegen. Das Datenblatt schlägt vor über eine zusätzliche Diode nur die

notwendigen Schaltungsteile aus dem Baustein zu versorgen. Auf dieser Platine

ist die zusätzliche Diode nicht auszumachen.

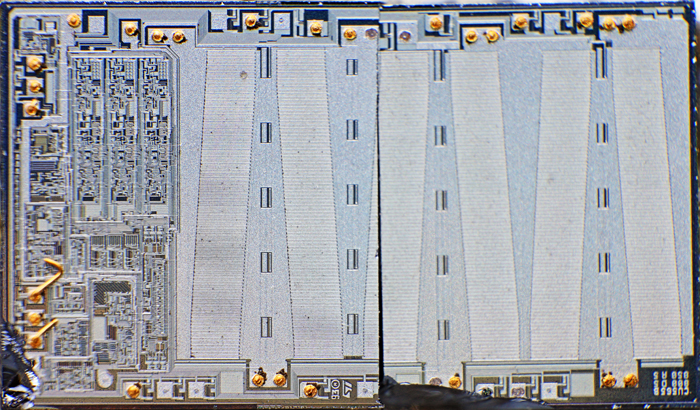

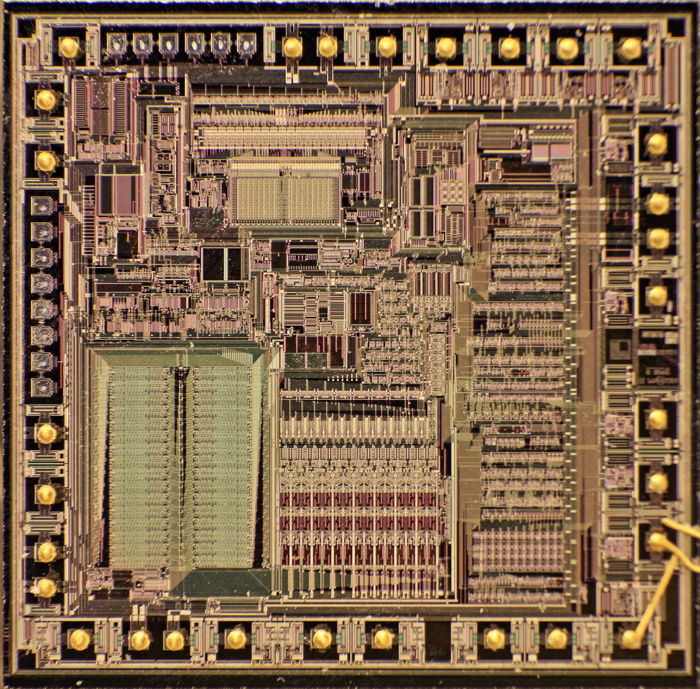

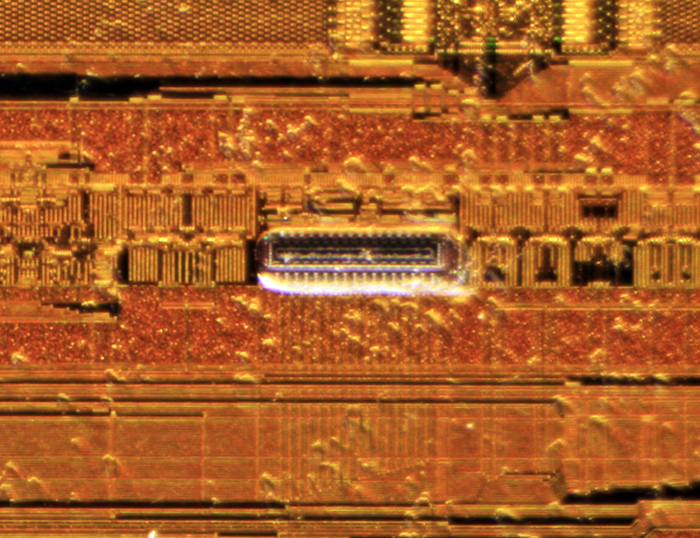

Das Die (etwas beschädigt) besteht

deutlich erkennbar aus einem Steuerungsteil links und einem großen Leistungsteil

rechts.

Die Anschlüsse für die drei Phasen des Motors befinden sich an der

unteren Kante des Dies. Die angrenzenden Metallflächen bilden jeweils einen

Kegel, der beinahe so lang ist wie das Die. Auf beiden Seiten des Kegels

befinden sich Gitterstrukturen, die die Transistoren der jeweiligen Halbbrücke

darstellen. Auch die Zuführung der Versorgung und der Masse ist kegelförmig

ausgeführt. Da sich der Stromfluss über die Länge reduziert, war es möglich die

Fläche entsprechend zu reduzieren. Die Anordnung der Halbbrücken führt dazu,

dass sich die benachbarten Ausgänge jeweils eine Zuleitung oder einen

Masseanschluss teilen können und der komplette Aufbau möglichst wenig Fläche

beansprucht.

Die Transistoren können laut Datenblatt dauerhaft 1,8A und

kurzzeitig 3,5A weiterleiten.

Das zweite Leistungsbauteil befindet sich an der linken Kante der Steuerungsplatine. Der UC3173 ist ein Vollbrückentreiber der Firma Unitrode, der speziell für die Platzierung des Schreib-/Lesearms von Festplatten entwickelt wurde.

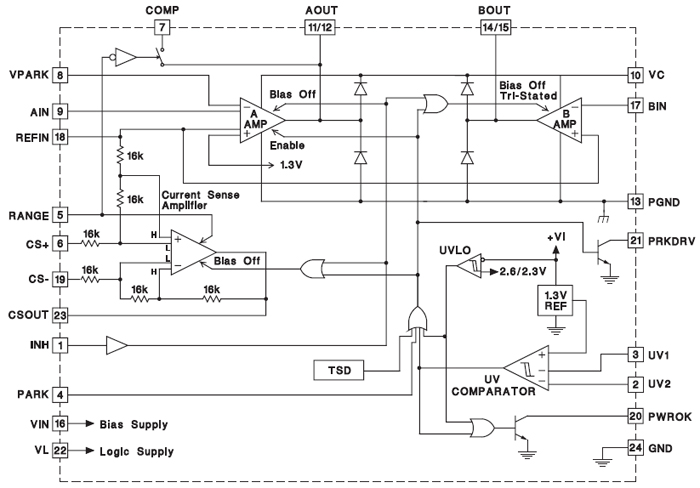

Das Blockschaltbild im Datenblatt zeigt

den internen Aufbau und beschreibt viele mögliche Funktionen.

Die H-Brücke

selbst ist in Form von zwei Differenzverstärkern mit vier Freilaufdioden

dargestellt.

Ebenfalls im Package enthalten ist ein Differenzverstärker, der zur Strommessung genutzt werden kann. Ein zusätzlicher Pin ermöglicht das Umschalten des Verstärkungsfaktors, was den Dynamikbereich der Regelstrecke erhöht. Dabei wird ein weiterer Pin geschalten, der ein zusätzliches Kompensationsglied einbinden kann. Durch diesen Aufbau ist die Regelstrecke bei beiden Verstärkungsfaktoren ideal kompensiert.

Der Baustein übernimmt außerdem die

Parkfunktion des Schreib-/Lesekopfes. Die Parkfunktion wird aktiviert bei einer

Unterspannung auf der internen oder auf einer von bis zu zwei externen

Versorgungsspannungen, außerdem bei einer Übertemperatur im Chip oder einer

Anforderung von außen.

Zur Einleitung des Parkvorgangs wird die Rechte Hälfte

der H-Brücke abgeschaltet und die linke Hälfte gibt eine Spannung aus, die sich

über den VPARK-Pin einstellen lässt. Die Spannung definiert die maximale

Geschwindigkeit, mit der der Schreib-/Lesekopf in die Parkposition fährt. Der

Strompfad schließt sich während des Parkvorgangs über den zusätzlichen

Lowside-Transistor am Pin PRKDRV. Durch einen Widerstand in diesem Strompfad

kann der Strom begrenzt werden.

Mit einer spezielleren Verschaltung bleibt

die Parkfunktion sogar bis zu einer Versorgungsspannung von 1,2V aktiv.

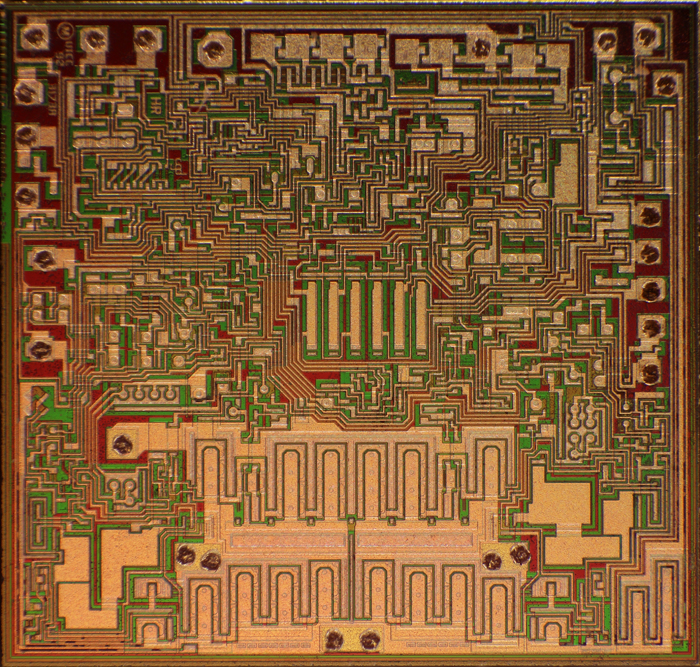

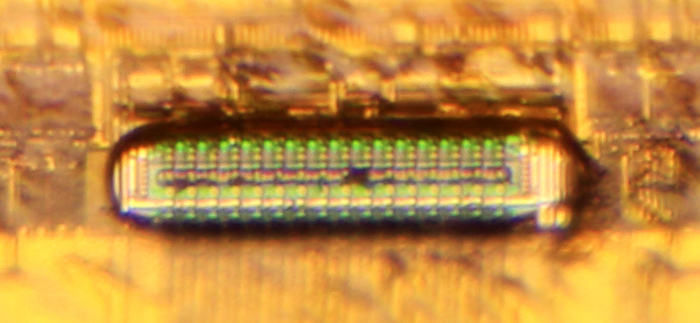

Im unteren Bereich des Dies ist der

Leistungsteil des Chips zu erkennen. Die untersten zwei Bonddrähte stellen den

Massekontakt dar. Darüber befinden sich fingerförmig die Lowside-Transistoren

der zwei Halbbrücken. Rechts und links darüber befinden sich jeweils zwei

Bonddrähte, die den Ausgang der Vollbrücke bilden. Die fingerförmigen Strukturen

darüber stellen die Highside-Transistoren dar. Das Bondpad links der

Highside-Transistoren bindet den Leistungsteil an die Versorgungsspannung an.

In der rechten unteren Ecke befindet sich ein weiterer Leistungstransistor, der

an ein Bondpad in der rechten oberen Ecke angebunden ist und vermutlich als

PRKDRV-Transistor dient.

An der oberen Kante sind acht Testpads zu erkenne, die der optischen Erscheinung nach über Fuses die Justage von zwei Widerstandsgruppen ermöglichen.

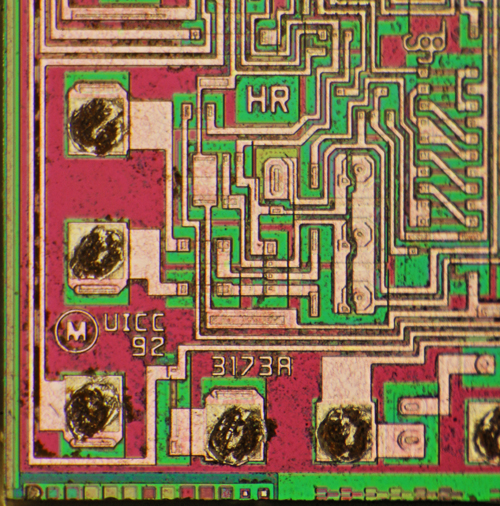

In der linken oberen Ecke des Dies befindet sich das Kürzel der Firma Unitrode, der Jahrgang 1992 und die Modellbezeichnung 3173A.

Die Ätzmarker lassen darauf schließen, dass sehr viele Masken zur Anwendung kamen, um die Schaltung zu fertigen.

Direkt an der Übergabestelle zum inneren Bereich der Festplatte befindet sich mit dem P32P4910 von Philips ein sehr spezieller und komplexer Chip, der die erste Signalverarbeitungsstufen realisiert.

Das Datenblatt beschreibt ansatzweise den

enormen Funktionsumfang des Chips. Die kurze Zusammenfassung auf der ersten

Seite liest sich folgendermaßen:

"The Philips Semiconductors P32P4910A is a

high performance BiCMOS read channel IC that provides all of the functions

needed to implement an entire Partial Response Class 4 (PR4) read channel for

zoned recording hard disk drive systems with data rates from 42 to 125 Mbit/s or

33 to 100 Mbit/s. Functional blocks include AGC, programmable filter, adaptive

transversal filter, Viterbi qualifier, 8,9 GCR ENDEC, data synchronizer, time

base generator, and 4-burst servo."

Eine detaillierte Beschreibung der Funktionen könnte problemlos ein ganzes Buch füllen. Die meisten Funktionen dienen der Signalaufbereitung und generieren aus dem analogen, verschliffenen Ausgangssignal des Lesekopfes ein digitales, nutzbares Signal. Neben der Aufbereitung des Nutzsignals beinhaltet der Chip auch eine Funktion, die das Justieren des Schreib-/Lesekopfes ermöglicht. Dazu wertet der Chip über einen zweiten Kanal den Anfang des eingestellten Sektors aus.

Das Die des Chips hat etwas gelitten, es lassen sich aber die vielen unterschiedlichen Strukturen gut erkennen.

Unter dem Chip taucht ein "MADE IN CHINA" auf, das man anscheinend ein Stück weit verstecken wollte.

Interessanterweise scheint die Servo-Funktion des P32P4910 bei dieser Festplatte nicht genutzt worden zu sein. Stattdessen befindet sich auf der Platine der Chip ADSC900 von Analog Devices.

Zu diesem Chip ist über frei zugängliche Quellen kein Datenblatt aufzutreiben. Es existiert allerdings ein IEEE-Artikel der viele Informationen liefert ("A Monolithic All-CMOS Embedded Servo Channel for Hard Disk Drives"). Es handelt sich um einen speziellen Chip, der die Servo-Funktionalität für einen Schreib-/Lesekopf darstellen kann.

Der Chip enthält eine Referenzspanungsquelle und einen 10Bit-Analog-Digital-Wandler. Das digitalisierte Signal wird ausgegeben und nach der Verarbeitung durch eine Steuerungslogik wieder eingelesen. Im ADSC900 befindet sich zusätzlich ein 10Bit-Digital-Analog-Wandler, der letztlich das Fehlersignal zum Nachregeln des Schreib-/Lesekopfes liefern kann.

Die Spannungsversorgung des ADSC900 ist über zwei LC-Glieder (L6/C49 und L8/C59) entstört.

Der IEEE-Artikel liefert einige Details

zum ADSC900: Die Abmessungen betragen 3,7mm x 3,6mm. Es handelt sich um einen

1µm-CMOS-Prozess.

Anderen Veröffentlichungen nach zu urteilen bestand die

Herausforderung damals vor allem darin auf bipolare Schaltungsteile verzichten

und alle notwendigen Funktionen mit MOS-Transistoren aufbauen zu können.

An der linken Seite sind acht, an der oberen Kante sechs Testpads zu sehen. Der IEEE-Artikel des ADSC900 erklärt, dass darüber die Referenzspannungsquelle und Verstärkung des Demodulators eingestellt werden konnte.

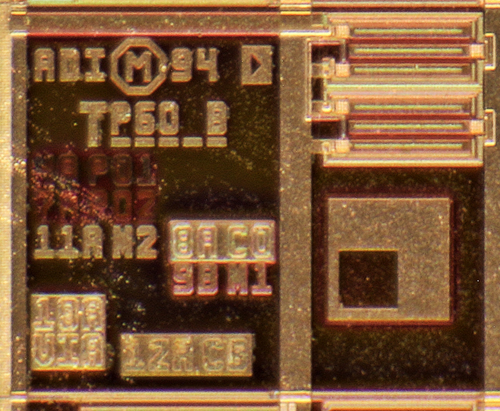

Das Design oder zumindest der Maskensatz

stammt aus dem Jahr 1994.

Die Zeichenfolge "TP60 B" könnte für den

Fertigungsprozess stehen.

Es sind einige Masken zu erkennen. "11A

M2" und "9B M1" passen farblich und auf Grund der Nomenklatur zu jeweils einer

Metalllage. "10A VIA" steht selbsterklärend für Vias. Die Nummerierung lässt

darauf schließen, dass die Vias die beiden Metalllagen verbinden. "8A C0" könnte

dann den Kontakt zwischen der unteren Metalllage und den aktiven Elementen

darstellen. Dass darunter zwei Masken ausgereicht haben, ist nicht nur auf Grund

der Nummerierung unwahrscheinlich. An der unteren Kante des Halbleiters sind

noch zwei weitere Markierungen zu finden, die für zusätzliche Masken stehen

könnten.

Der Buchstabe hinter der Maskennummer steht vermutlich für die

Revision der Maske. Demnach wurde bis zum vorliegenden Design nur die erste

Metalllage einmal überarbeitet.

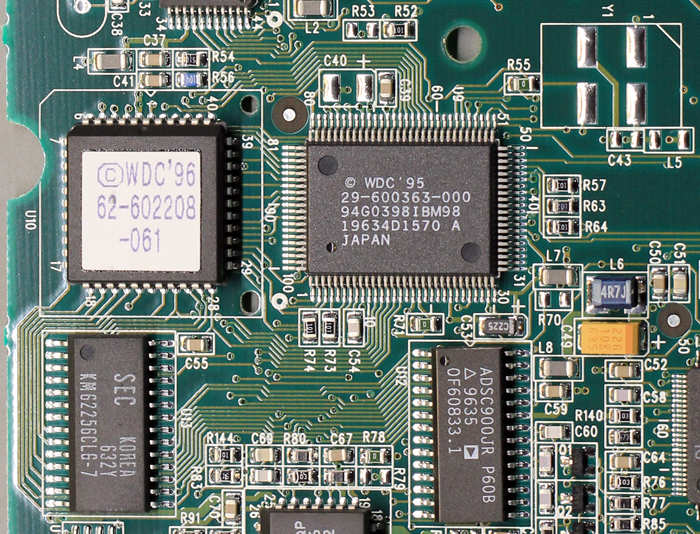

Der ADSC900 und die restlichen ICs der

Platine sind an einen gemeinsamen Bus angeschlossen.

In direkter Nähe

befinden sich ein RAM-, ein PROM-Baustein und ein spezifischer WD-Chip, die

vermutlich miteinander arbeiten.

Der RAM-Baustein ist ein KM62256CLG-7 mit

32kB Speicherplatz.

Der PROM-Speicher ist mit einem WD-Label beklebt. Es

handelt sich um einen AT27C516 von Atmel, der 64kB Platz bietet.

Die

Beschriftung des TQFP-100-Bausteins lässt keinen Schluss auf die Funktion und

die Architektur zu. Die Zahlenfolge 29-600363-000 ist vermutlich die interne

Bezeichnung des Chips. In der rechten, oberen Ecke befindet sich ein

Bestückplatz für einen Oszillator, der den Chip mit einem Taktsignal versorgen

könnte. Stattdessen ist das Potential über eine Brücke mit einem anderen

Potential verbunden, das vermutlich einen alternativen Takt führt.

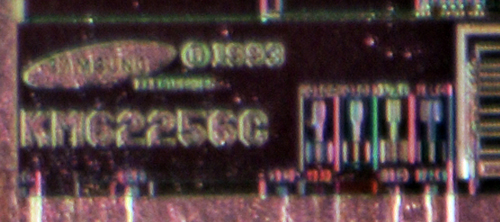

Der Aufbau des RAM-Dies entspricht dem was man von einem RAM-Speicher erwartet. Die meiste Fläche wird von den Speicherelementen selbst eingenommen. Um die Speicher sind nur noch einige wenige Hilfsschaltungen integriert.

Laut Datenblatt basiert der Chip auf einen

0,7µm CMOS-Prozess.

Es sind gerade noch das Samsung-Logo, die Jahreszahl

1993 und die Typbezeichnung zu erkennen.

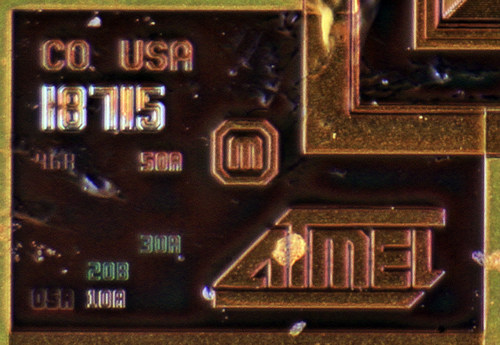

Das Die des PROM-Speichers besteht ebenfalls hauptsächlich aus Speicherelementen.

Die Nummer 18715 könnte eine interne Teilenummer sein. Es sind fünf Maskenbezeichnungen abgebildet.

Der WD-spezifische Chip ist kein

Mikrocontroller oder Mikroprozessor. Der Erscheinung nach handelt es sich um ein

Gatearray.

Um den kompletten Umfang des Dies sind Bondpads angeordnet.

Hinter den Pads sind regelmäßige Strukturen zu sehen, über die sich

höchstwahrscheinlich die Anschlüsse als Aus- oder Eingang konfigurieren lassen.

Innerhalb des Dies sind deutlich vollflächige, regelmäßige Zeilenstrukturen zu

erkennen. Darüber liegen die Verbindungen zwischen den Logikblöcken, die die

eigentliche Gesamtfunktion darstellen.

Auf dem Die sind keine Bezeichnungen zu sehen. An einer Ecke ist allerdings ein kleines Stück Silizium abgebrochen, das theoretisch mehr Informationen enthalten haben könnte.

In der unteren rechten Ecke sind Zeichen abgebildet, die sich nicht entziffern lassen. Um 180° gedreht könnte man "omni wx" erahnen.

Insgesamt ist zu vermuten, dass die drei Chips die Grundfunktionen der Festplatte steuern.

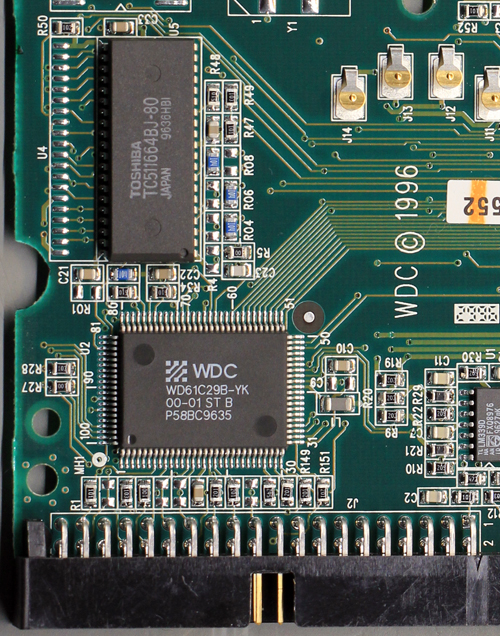

An der IDE-Schnittstelle befindet sich ein weiterer WD-spezifischer Schaltkreis mit der Bezeichnung WD61C29B und ein TC511664BJ-80-RAM-Baustein.

Die Platzierung der Schaltkreise lässt vermuten, dass sie miteinander die IDE-Schnittstelle bedienen. Dazu passt, dass der RAM-Baustein mit 128kB genau den Speicherplatz darstellt, der für die Caviar 22100 als Cache angegeben wird.

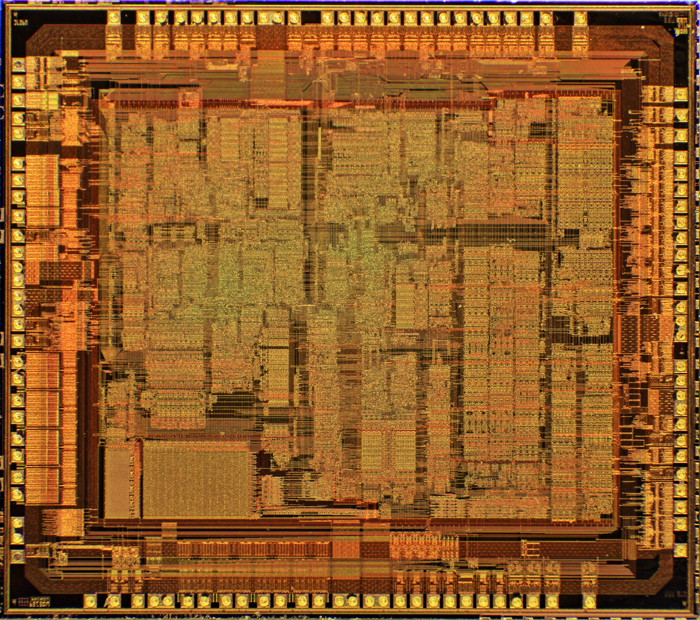

Das Die ist 6,6mm x 5,6mm groß und enthält verschiedene Strukturen. Dem Anschein nach handelt es sich zumindest zum Teil um einen Mikrocontroller. In der linken unteren Ecke sind zwei sehr homogene Blöcke zu erkennen, die vermutlich einen statischen und einen dynamischen Speicher darstellen.

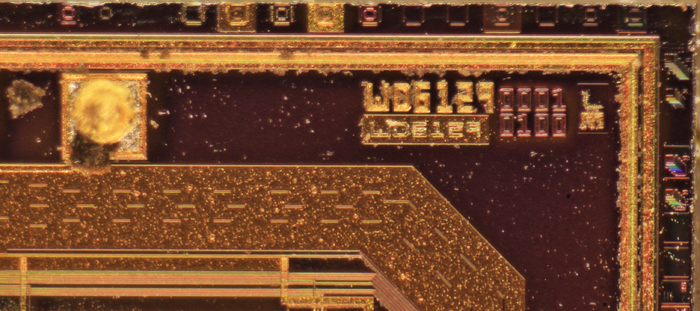

In der linken unteren Ecke ist zweimal die Typbezeichnung WD6129 abgebildet. Das könnte bedeuten, dass es sich um einen speziell von WD entwickelten Halbleiter handelt. Denkbar ist allerdings auch, dass ein eher universeller Mikrocontroller mit einem spezifischen Maskensatz der Metalllage programmiert wurde.

Die Zahlenfolgen 0001 und 0100 lassen sich nicht ohne Weiteres erklären.

Die Ätzmarker an der Kante lassen vermuten, dass zur Herstellung des Chips sehr viele Masken zum Einsatz kamen.

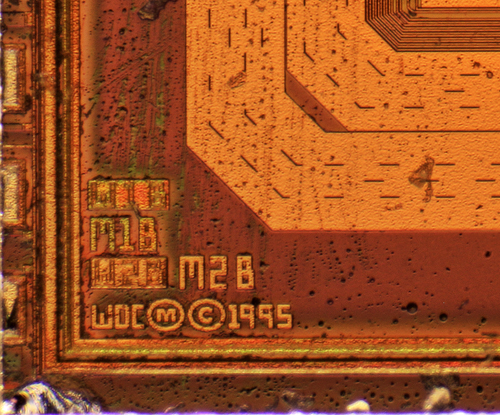

Die rechte obere Ecke des Dies trägt das WD-Logo und die Jahreszahl 1995.

Vier Maskenbezeichnungen stehen ziemlich sicher für die beiden Metalllagen und wahrscheinlich für die Kontaktierungen zwischen den Metalllagen und zu den aktiven Elementen.

Das Die des RAM-Bausteins ist mit den Abmessungen 10mm x 4,9mm sehr groß.

Es sind acht Spalten zu erkennen, die wiederum acht Speicherblöcke enthalten. Darin befinden sich rechnerisch 1000 16-Bit-Speicherplätze.

Ansatzweise lassen sich hier bereits oberhalb oder unterhalb von jeder Spalte Artefakte erkennen. Dazu später mehr.

Der Chip ist mit einer zusätzlichen Passivierungschicht überzogen, die nur an den vielen Testpads ausgespart wurde und das Analysieren der Strukturen erschwert.

Höchstwahrscheinlich handelt es sich bei

der Schicht um Polyimid. Polyimid wird als zusätzliche Schutzschicht auf

integrierten Schaltkreisen eingesetzt.

Bei Speicher-Chips hat die

Polyimidschicht eine zusätzliche, recht spezielle Funktion. Im Packagematerial

befinden sich immer auch äußert geringe Mengen radioaktiver Elemente. Bei den

sehr kleinen Strukturen können einzelne Zerfälle bereits zum Umkippen von

gespeicherten Bits führen. Die Polyimidschicht reduziert diesen Effekt.

Der Beschriftung auf dem Die nach zu urteilen stammt das Design aus dem Jahr 1990.

Die bereits beschriebenen Artefakte sind nachträglich in den Halbleiter eingebrachte Unterbrechungen. An diesen Stellen wurde die Polyimidschicht ausgespart. Darunter befinden sich 16 Leitungen, die alle unterbrochen wurden. Vermutlich kam dafür ein Laser zum Einsatz.

Eine mögliche Erklärung für die

Unterbrechungen wäre das Abschalten von Speicherbereichen, um einen größeren

Chip zusätzlich als kleineres Modell verkaufen zu können ohne zwei Arten von

Speichern fertigen zu müssen. Dagegen spricht allerdings, dass auf dem Die exakt

die Bezeichnung des vorliegenden Speichers abgebildet ist.

Es erscheint

wahrscheinlicher, dass die Leitungen während der Produktion zum Beispiel für

einen abschließenden Test notwendig waren, für den normalen Betrieb aber

unterbrochen werden mussten.

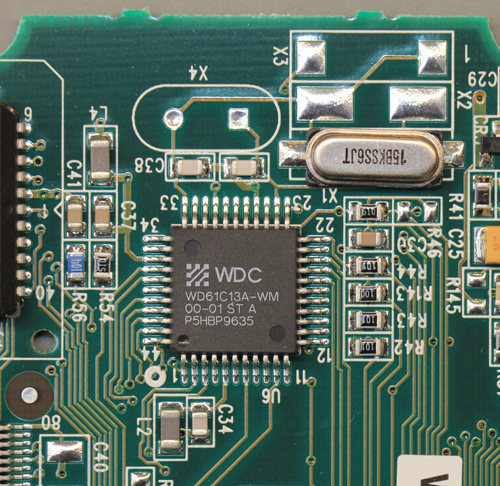

Zwischen dem IDE-Controller und der bereits beschriebenen Steuerung der Festplatte selbst befindet sich ein weiterer WD-spezifischer Schaltkreis mit der Bezeichnung WD61C13A.

Oberhalb des Chips befinden sich vier

parallel geschaltete Bestückplätze für verschieden Quarz-Größen, was nicht

gerade üblich ist.

Da es sich hier um den einzigen Quarz auf der ganzen

Platine handelt, ist zu vermuten, dass sich auch die restlichen Bausteine auf

diesen Takt synchronisieren.

Im Inneren des Dies befindet sich ein

Gatearray. Es ist denkbar, dass es sich um eine Art Glue-Logik zwischen dem

IDE-Controller und der restlichen Steuerung handelt.

Eventuell erfolgt

innerhalb der Logik auch eine komplexere Anpassung oder Umschaltung der

Taktfrequenzen für die einzelnen Baugruppen. Das würde zumindest erklären warum

dieses einzelne, kleinere Gatearray mit dem einzigen Quarz der Festplatte

ausgestattet ist.

Auf dem Die ist die klassische Gatearray-Struktur mit zwei Metalllagen zu erkennen.

Es handelt sich um ein Design von Western Digital aus dem Jahr 1995.

Der Vollständigkeit halber ist hier das Die des Vierfach-Komparators LM339 abgebildet.

Ebenso ist hier das Die des Sechsfach-Inverters 74LS05 zu sehen.

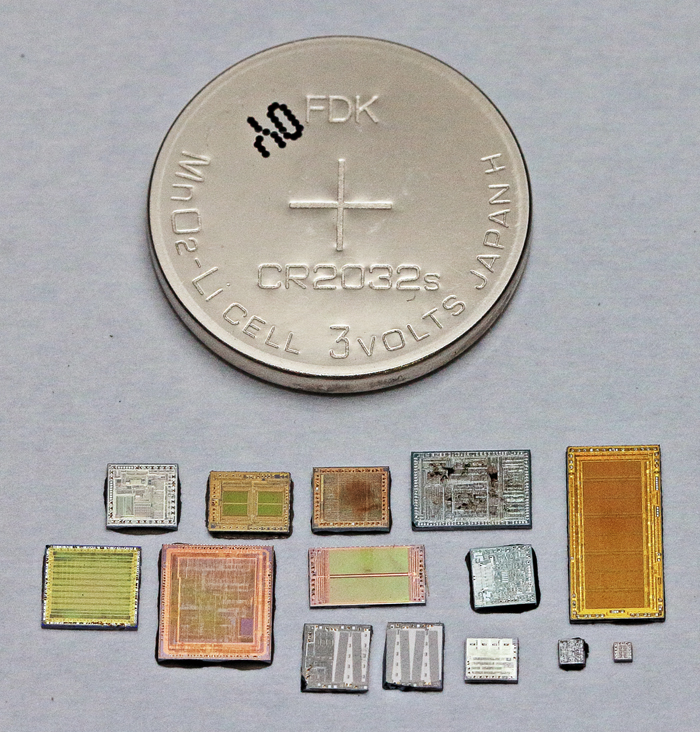

Alle komplexeren Halbleiter der Caviar 22100.