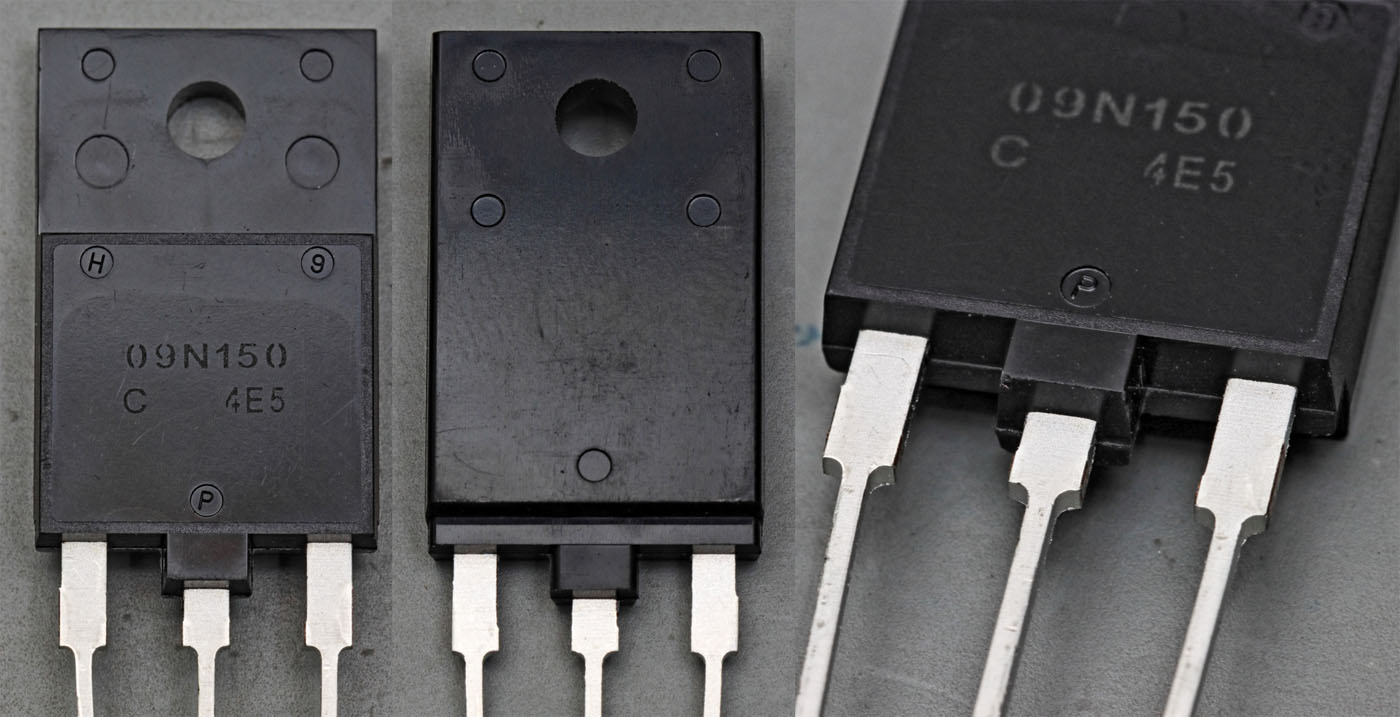

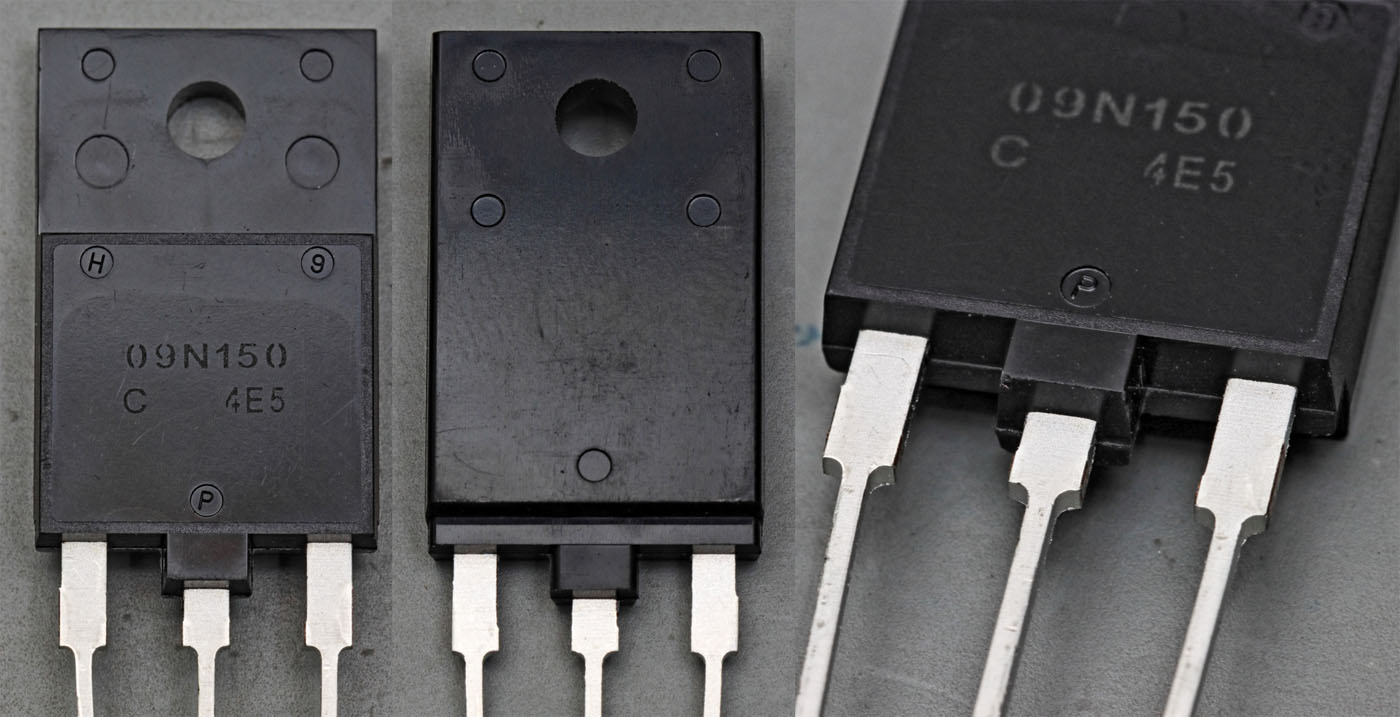

Der NDUL09N150C von ON Semiconductor ist ein Leistungs-MOSFET, der bis zu 1500V sperren kann. Um dafür ausreichend Isolationsabstände darstellen zu können, besitzt das TO-3PF Gehäuse am Drain-Pin einen zusätzlichen Kunststoffkragen. Eine metallische Kühlfahne fehlt. Das verschlechtert den Wärmewiderstand (1,6°C/W), erleichtert aber die Montage, da keine zusätzliche Isolationsschicht eingeplant werden muss. Bei einer Gehäusetemperatur von 25°C kann der MOSFET bis zu 78W abführen. Voll ausgesteuert beträgt der typische Widerstand 2,2Ω. Das Datenblatt gibt zwei verschiedene Stromtragfähigkeiten an. Der Transistor selbst würde dauerhaft 9A erlauben, das Package begrenzt diesen Wert aber auf 6A. Bei 6A fällt bereits mehr Verlustleistung an, als sich sinnvoll über das Gehäuse abführen lässt. Kurzzeitig sind bis zu 18A zulässig.

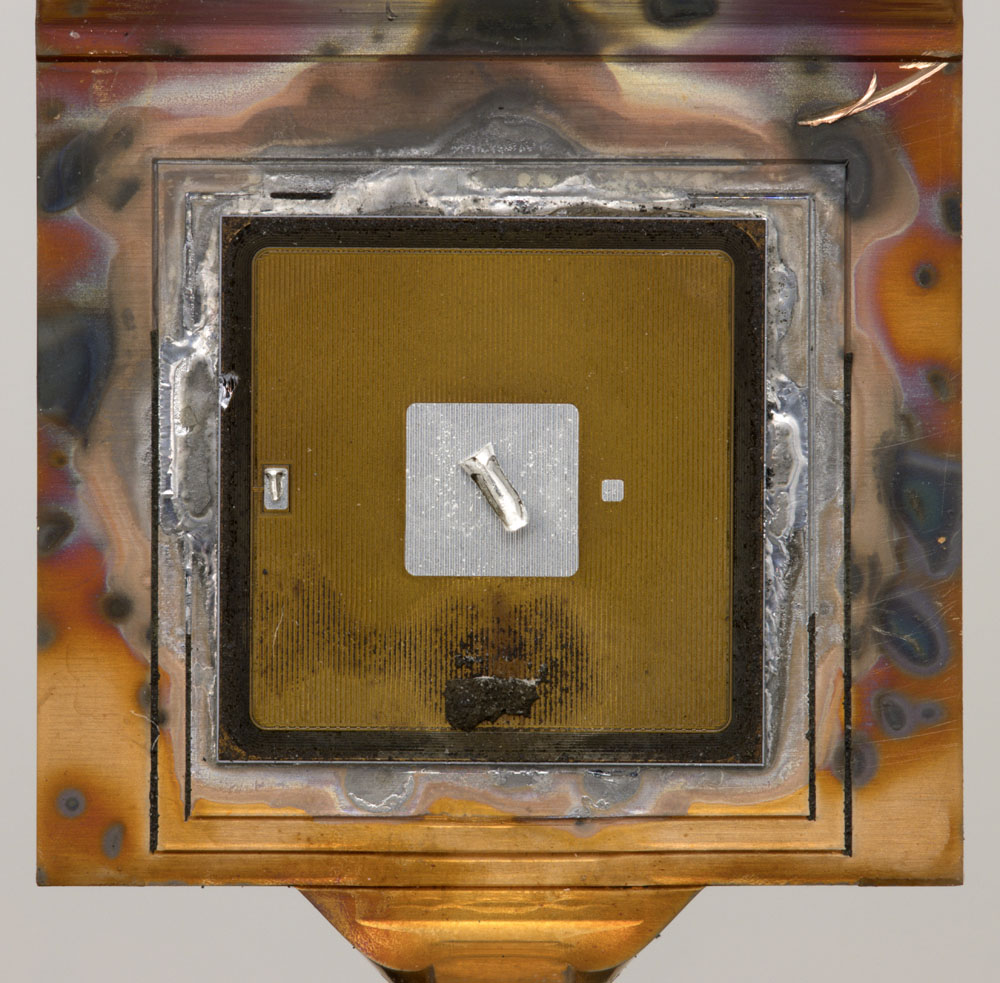

Das Die weist eine Kantenlänge von 8mm auf. Die Dicke beträgt circa 0,25mm. Mittig befindet sich der Source-Bondbereich. An der linken Kante ist der Anschluss für das Gate-Potential platziert. Für den Source-Anschluss wurde nur ein Bonddraht verwendet, allerdings mit einem deutlich dickeren Querschnitt als für den Gate-Anschluss.

Das Die ist mit einer Schutzschicht, vermutlich Polyimid, überzogen. Neben dem Source-Anschluss befindet sich ein Fenster, das anscheinend Testzwecken dient.

Am Rand des Dies sind die bekannten runden Strukturen zur Potentialsteuerung integriert, damit bei bis zu 1500V keine Überschläge auftreten.

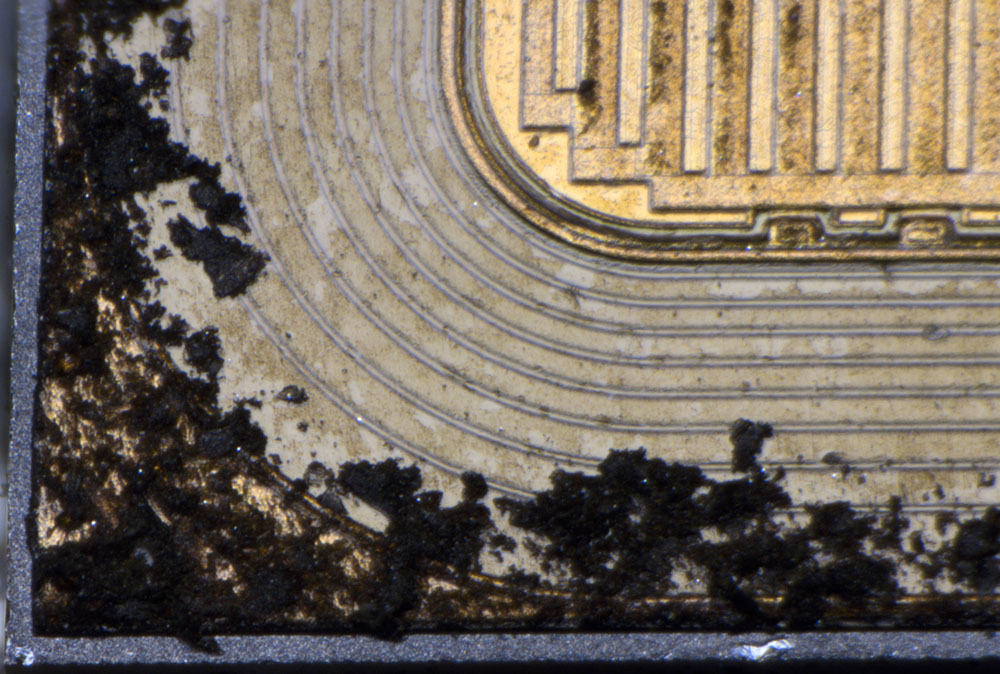

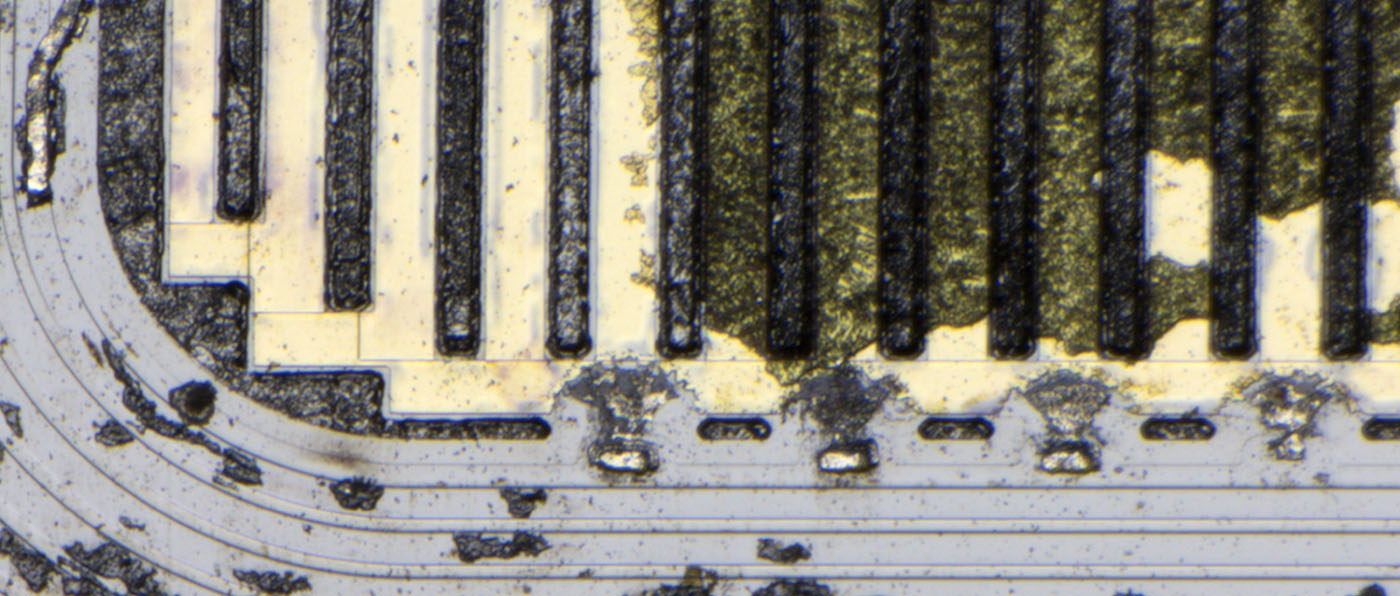

Das Gate-Potential wird über einen Rahmen, um den Umfang des aktiven Bereichs herumgeführt und kontaktiert an der oberen und der unteren Kante tiefer liegende Streifen, die in den aktiven Bereich führen.

Die Metallfläche, die das Drain-Potential leitet, ist über lange vertikale Durchbrüche mit den darunter liegenden Trench-MOSFET-Strukturen verbunden.

Die Schichten lassen sich nur schwer abtragen. Hier kann man aber erkennen, dass das Gate-Potential über die gelblichen Flächen in den MOSFET geführt wird. Von den seitlichen Kontakten aus wurde die Fläche bereits stark angegriffen.

Das Drain-Potential kontaktiert den MOSFET nicht nur über die vertikalen Streifen, sondern auch an den Rändern. Diese Maßnahme soll vermutlich dafür sorgen, dass das Potential um den aktiven Bereich herum an allen Stellen immer gleich hoch ist und sich keine lokalen Überhöhungen im elektrischen Feld einstellen.