Die Firma UnitedSiC forscht seit 1999 an Siliziumcarbid-Halbleitern. 2014 brachte UnitedSiC die ersten Produkte auf den Markt.

Der UF3C120040K4S ist eine sogenannte SiC Cascode, die eine Sperrspannung von 1200V darstellen kann und deren Widerstand im eingeschalteten Zustand 35mΩ beträgt. Die Ausgangskapazität ist typisch für einen SiC-Halbleiter verhältnismäßig gering (112pF/280pF).

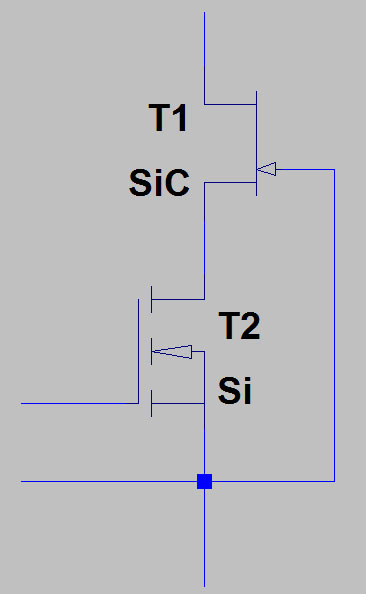

Eine SiC-Cascode besteht aus einem Siliziumcarbid-J-FET und einem Silizium-MOSFET. Der Grund für diese Verschaltung ist die Tatsache, dass sich J-FETs leichter herstellen lassen. Ein MOSFET benötigt sehr viel sauberere Strukturen, die sich mit Siliziumcarbid nicht so einfach umsetzen lassen wie mit Silzium. J-FETs sind allerdings selbstleitend. Beim Einsatz in Leistungselektroniken werden aber meistens eigensichere und damit selbstsperrende Schaltelemente benötigt. Die SiC-Cascode bietet das Schaltverhalten eines selbstsperrenden MOSFETs mit den positiven elektrischen Eigenschaften eines Siliziumcarbid-Transistors.

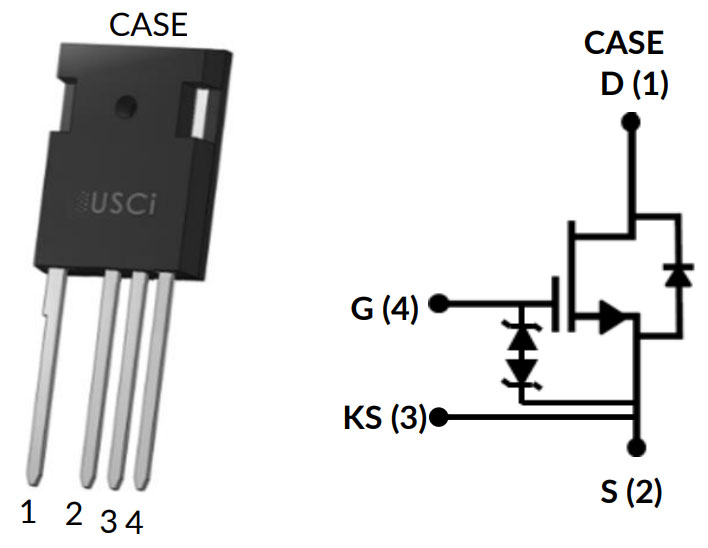

Das zusätzlich herausgeführte, zweite Source-Potential ermöglicht es das Gate-Source-Potential unabhängig vom Laststrom sauber einzustellen. Das TO-247-4L-Package bietet einen vergrößerten Abstand am Drain-Kontakt, was für eine hohe Spannungsfestigkeit sorgt.

Die Abbildung im Datenblatt vermischt die beiden Komponenten und stellt einen J-FET mit einer kleinen MOSFET-Gate-Elektrode dar. Tatsächlich handelt es sich um eine klassische Kaskodenverschaltung, bei der MOSFET und J-FET in Reihe geschaltet sind. Die Ansteuerung erreicht das Gate des MOSFETs. Das Gate des J-FETs ist an das Source-Potential des MOSFETs angeschlossen. Leitet der MOSFET, so beträgt die Gate-Source-Spannung des J-FETs 0V und er leitet ebenso. Sperrt der MOSFET, so verbleibt das Gate-Potential des J-FETs auf dem niedrigen Source-Potential des MOSFETs, während sich das Source-Potential des J-FETs anhebt. Das führt dazu, dass der J-FET sperrt.

Der J-FET muss auf die spezifizierten Spannungen und Ströme ausgelegt sein. Vor allem bei hohen Sperrspannungen sind Siliziumcarbid-Transistoren den Silizium-Transistoren überlegen. Der MOSFET muss dagegen nur den maximal zulässigen Strom tragen können, da der J-FET ihn von hohen Spannungen isoliert.

Die im Datenblatt abgebildete Freilaufdiode wird durch die Bodydiode des MOSFETs dargestellt. Wird diese leitend, so reduziert sich die Gate-Source-Spannung des J-FETs und die ganze Strecke wird wieder leitend.

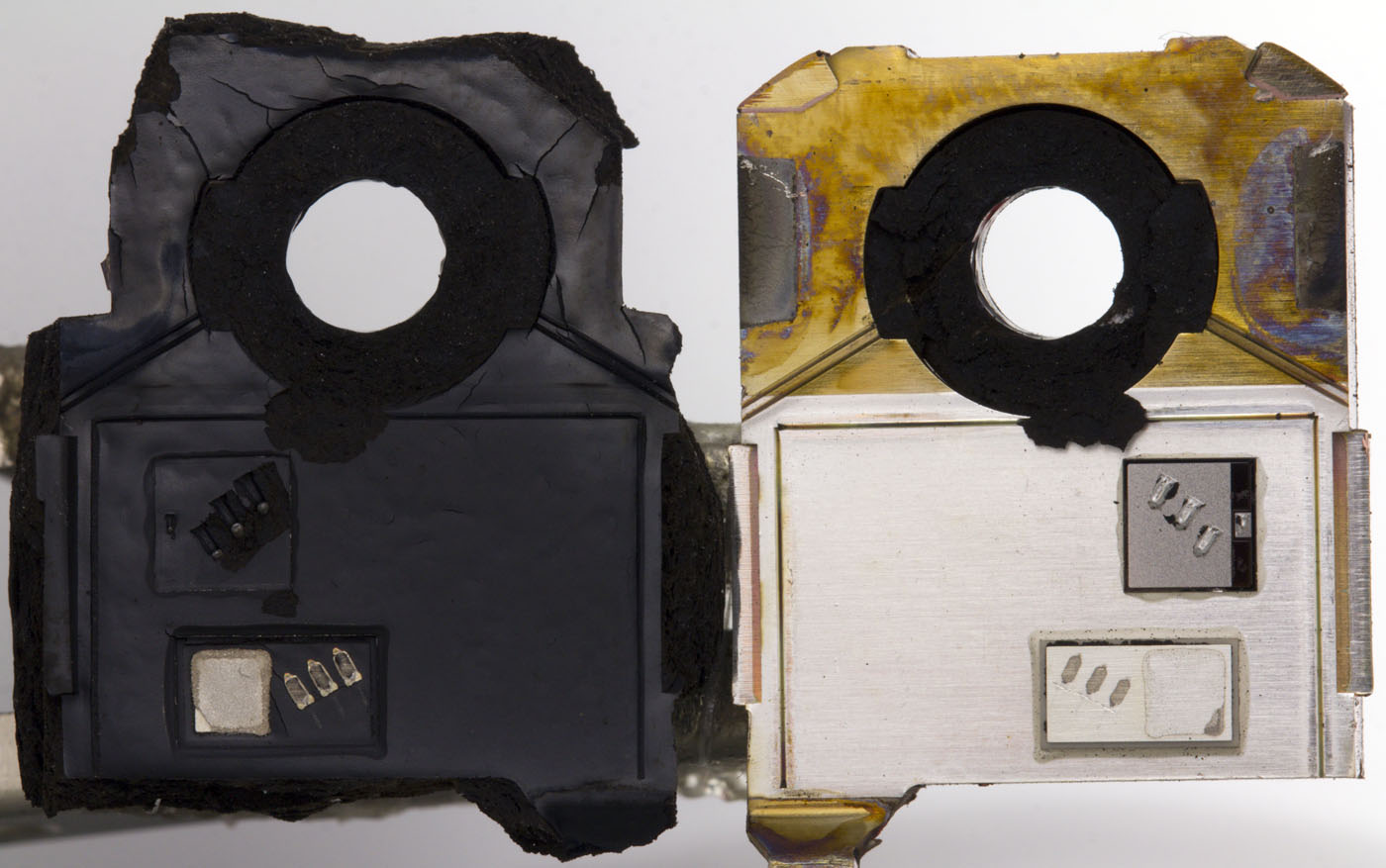

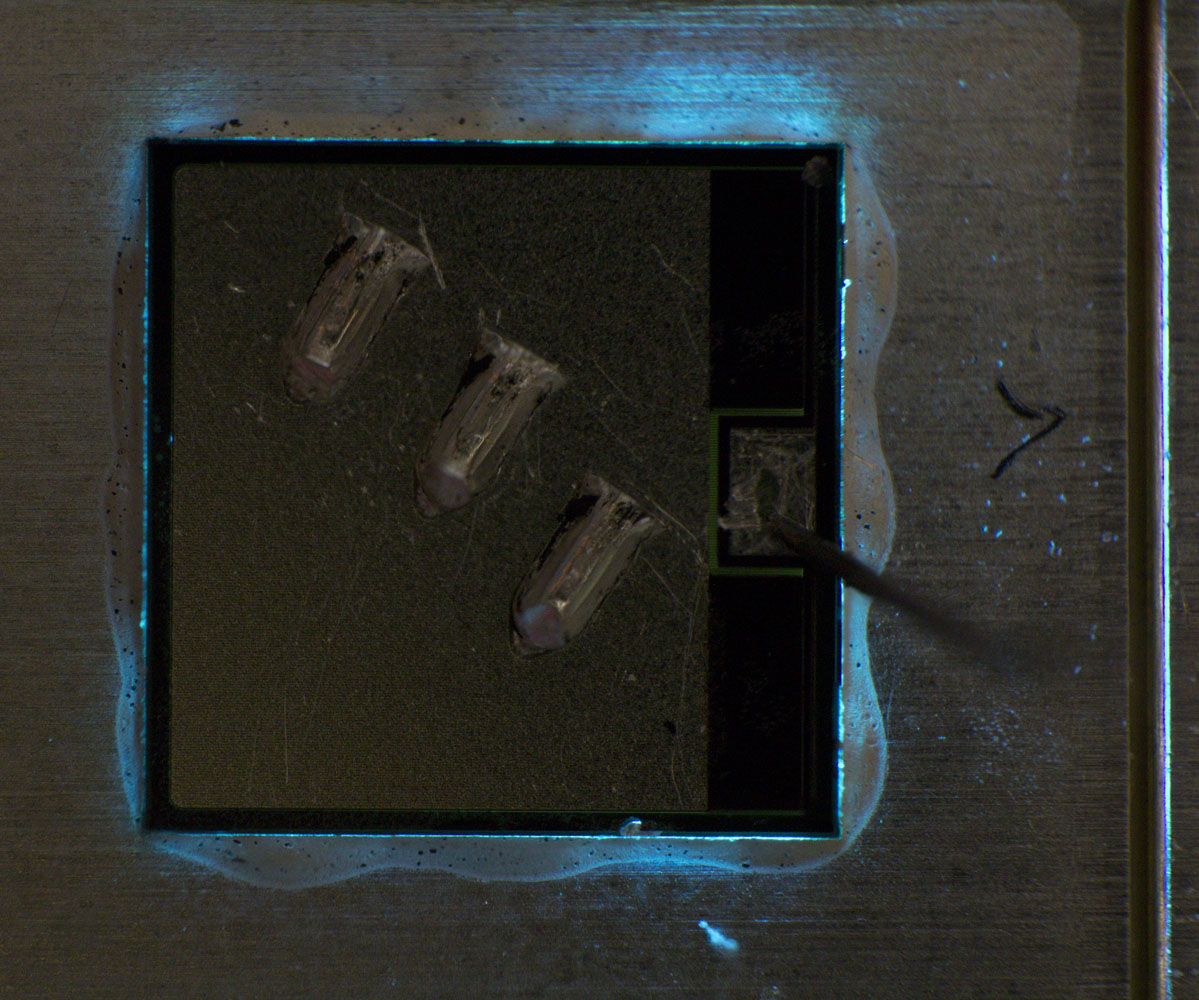

Auf der Kühlfahne des Packages befinden sich zwei Dies. Das obere Die enthält den Siliziumcarbid-J-FET, das untere Die befindet sich auf einer Isolationsschicht und enthält den Silizium-MOSFET. Der MOSFET hat sich von der Trägerplatte gelöst und befindet sich noch links im Mold-Material.

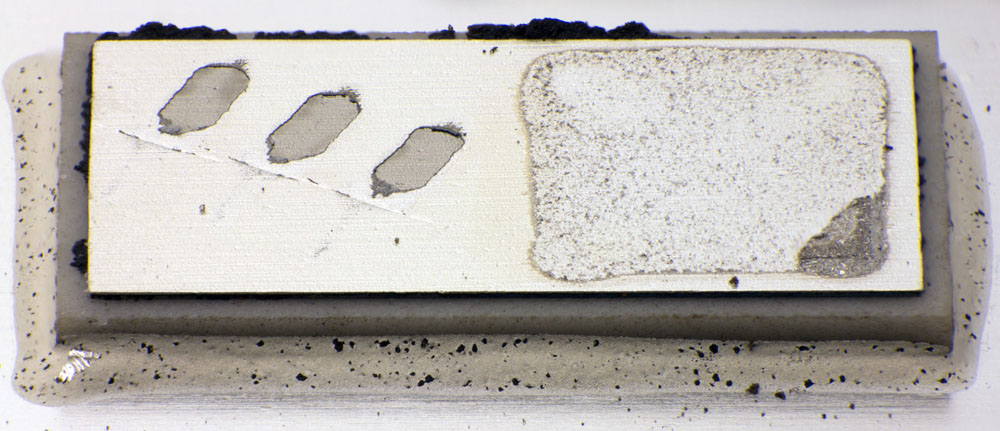

Die Isolation des MOSFETs realisiert ein Keramikplättchen, auf dem wiederum eine Metalllage aufgebracht ist.

Die Bonddrähte, die den Sourcekontakt des MOSFET elektrisch anbinden, sind im Verhältnis zum Die relativ groß und erschweren das Freilegen und Reinigen des Dies. An der oberen Kante ist der dünnere Bonddraht des zusätzlichen Source-Pins zu erkennen. Rechts erfolgt die Kontaktierung des Gate-Potentials.

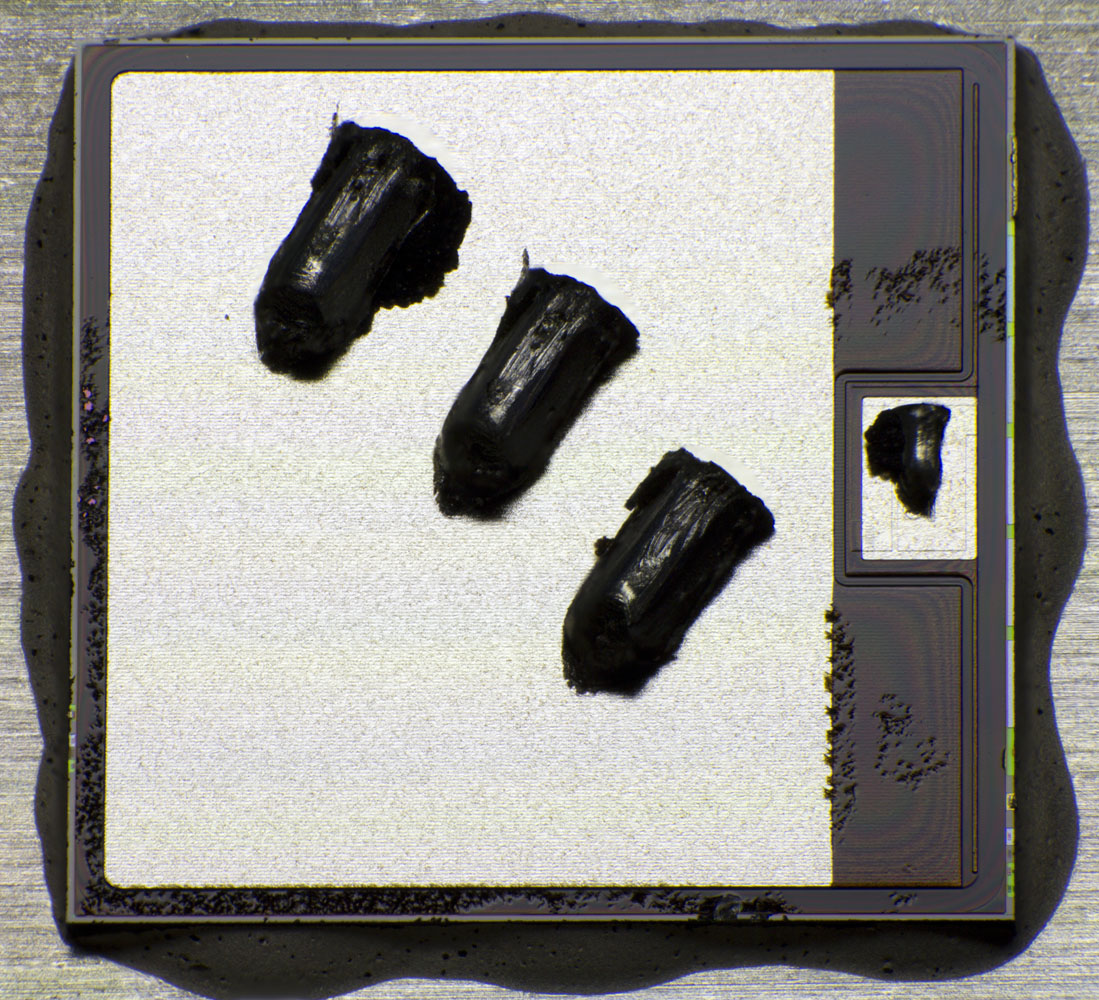

Vom MOSFET selbst ist auf Grund der massiven Metallisierung kaum etwas zu erkennen. Da der Transistor nur eine hohe Stromtragfähigkeit, keine hohe Sperrspannung bieten muss, ist an den Rändern kein erhöhter Abstand und keinerlei Feldsteuerung zu sehen.

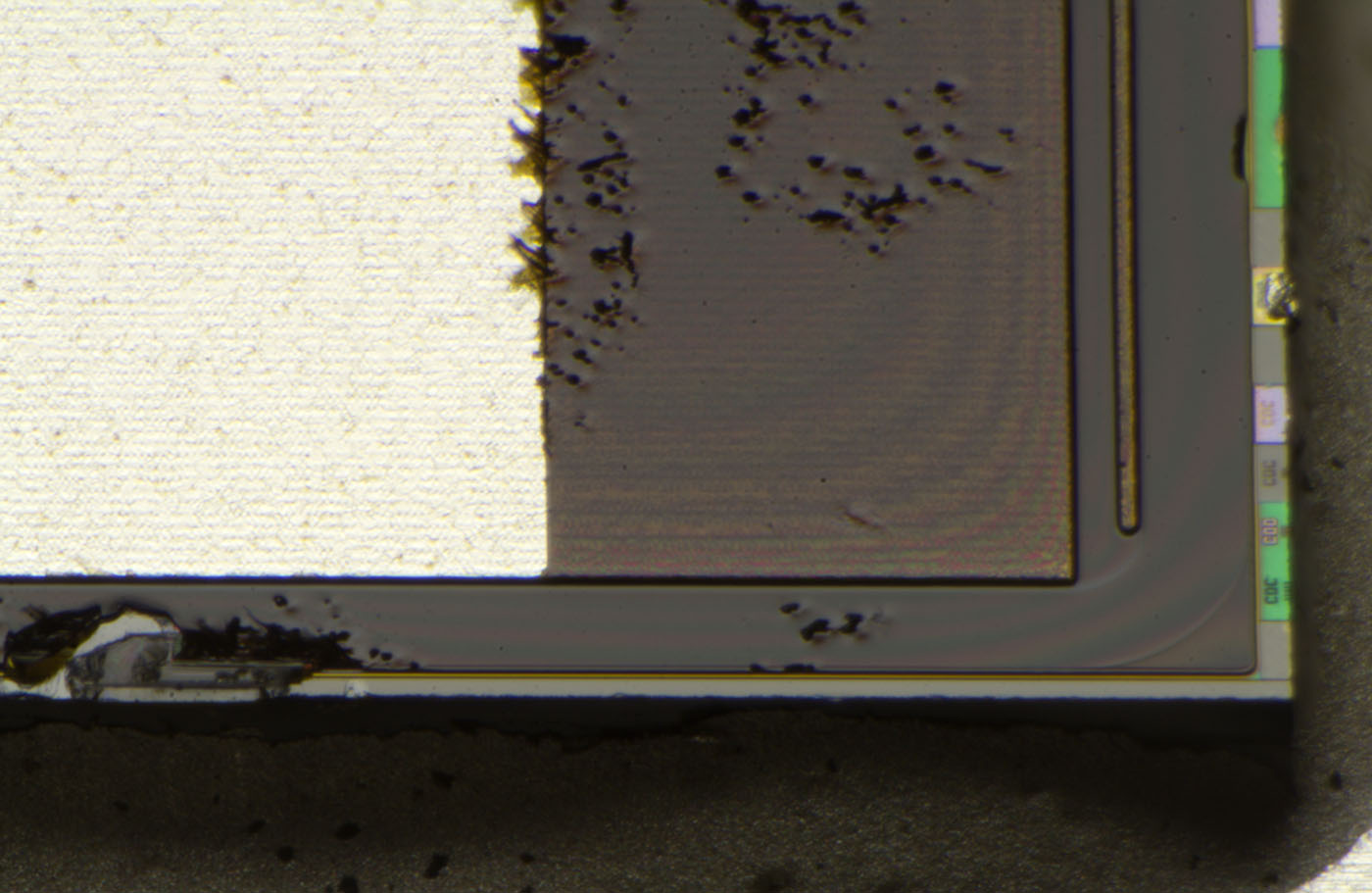

Der Siliziumcarbid-J-FET hat eine Kantenlänge von 3,1mm. Auch hier sind nicht allzu viele Details zu erkennen. Einen Großteil der Strukturen verdeckt die Metalllage, die den großen Source-Kontakt darstellt. An der rechten Kante befindet sich der Gate-Kontakt. Die Flächen, die nicht als Bondbereiche freigehalten wurden, sind mit einer Schutzschicht, vermutlich einer Polyimidschicht, überzogen.

An der rechten Kante befinden sich Maskenbezeichnungen.

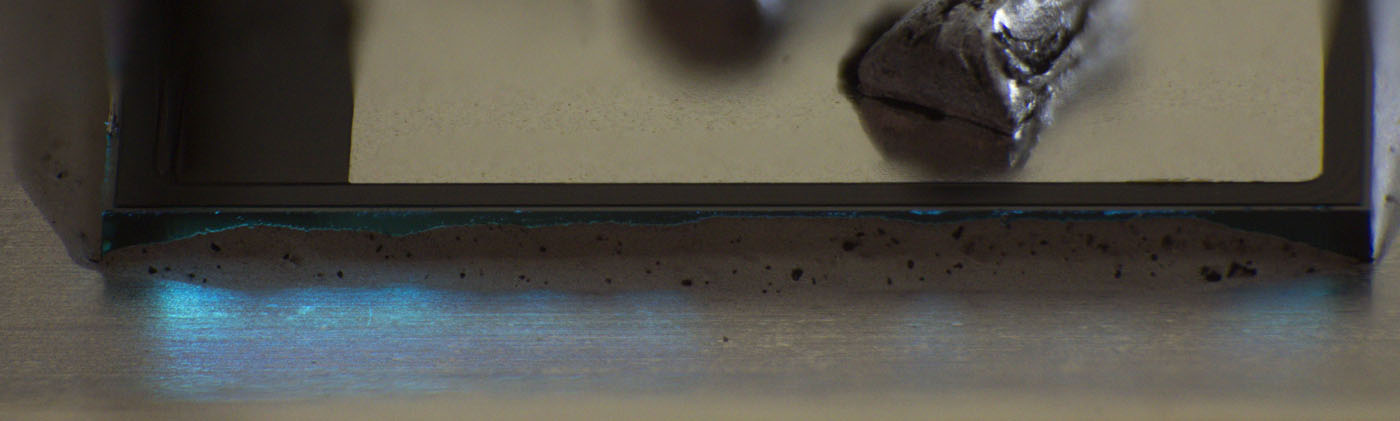

Die Randfläche mit den abgerundeten Ecken könnte eine Art Potentialsteuerung darstellen.

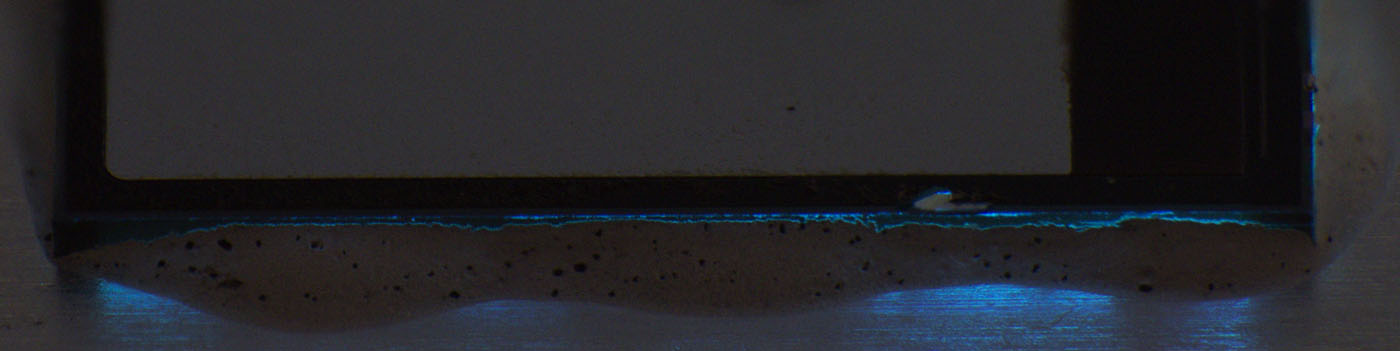

Die Flussspannung der pn-Grenzfläche innerhalb des JFETs liegt bei 3,5V. Während die Flussspannung eines Siliziumhalbleiters so niedrig ist, dass er nur im infraroten Bereich leuchten kann, ist bei Siliziumcarbid die Flusspannung hoch genug, dass ein Stromfluss über eine Sperrschicht ein blaues Leuchten erzeugt. Der Stromfluss beträgt hier 1A. Das generierte Licht strahlt seitlich aus dem Die heraus. Im normalen Betrieb liegt das Gate-Potential üblicherweise unter dem Source- und Drainpotential, weswegen der Leuchteffekt dort aubleibt.

Der Lichtstrom ist nicht allzu hoch, was vor allem zwei Gründe hat. Zum Einen ist der Bandübergang in Siliziumcarbid wie auch in Silizium ein indirekter Bandübergang. Das führt dazu, dass bei einer Rekombination eine Lichtausstrahlung weniger wahrscheinlich ist und somit die Umwandlung von elektrischer Energie in Licht weniger effizient abläuft. Dazu kommt, dass das Licht bis zum Rand des Dies einen relativ langen, verlustbehafteten Weg zurücklegen muss.