Das Bauteil und die Hintergrundinformationen stammen von einem Entwickler, der damals an diesem Projekt gearbeitet hat.

Ende der 80er Jahre benötigte die DDR dringend einen eigenen, hochauflösenden Digital-Analog-Wandler. Verfügbar war diesbezüglich nur der DAC4071 der keramischen Werke Hermsdorf, der zwar eine Auflösung von 16Bit bot, dessen Genauigkeit aber nicht über 14Bit hinaus ging. 16Bit-Digital-Analog-Wandler musste man teuer importieren.

Für 16Bit-Digital-Analog-Wandler gab es mehrere Anwendungsgebiete. So wollte man in der DDR eigene CD-Player entwickeln. Man hätte den dafür optimierten 16Bit-DAC TDA1541 von Philips in Lizenz fertigen können. Dabei wären allerdings pro verkauftes Gerät 5$ Lizenzgebühren fällig geworden. Das entspricht heute (2020) einem Wert von etwas mehr als 9€ und war indiskutabel. Ein großer Bedarf an 16Bit-Digital-Analog-Wandler bestand außerdem im Werkzeugmaschinenbau, wo dann meist teure Bauteile von Analog Devices beschafft wurden. Gleichzeitig eröffnete sich im militärischen Bereich mit dem amerikanischen SDI-Programm das Weltall als neues potentielles Kriegsgebiet. In diesem Zusammenhang benötigte man 16Bit-Digital-Analog-Wandler, um ein Fixsterntracking zu ermöglichen.

Mit diesem Hintergrund entwickelte man Ende der 80er Jahre im Halbleiterwerk Frankfurt Oder einen 16Bit-Digital-Analog-Wandler, der mit verschiedenen Spezifikationen als C536, als C5360 und als C5361 produziert worden wäre. Es handelt sich dabei um eine Weiterentwicklung des 12Bit-Digital-Analog-Wandler C565. Nachdem das Halbleiterwerk Frankfurt Oder 1990 geschlossen wurde, verblieb der C536 unvollendet.

Der TF536 ist ein Entwicklungsstand eines speziellen 16Bit-Digital-Analog-Wandlers, der die Basis der DAC-Familie gebildet hätte. Die ersten TF536 wurden im März 1989 produziert.

Der TF536 bietet eine Grundgenauigkeit von 13Bit und wäre so direkt als C536 eingesetzt worden. Im Bereich der CD-Player hätte er einfachere Digital-Analog-Wandler wie den MP7616 von Exar ersetzen können.

Um neben einer Auflösung von 16Bit auch eine Genauigkeit von 16Bit darstellen zu können, sollte eine digitale Korrektur der Kennlinie erfolgen. Dazu wurde ein Konzept entwickelt, das später in einen CMOS-Standardzellen-Baustein des Typs U1500 integriert werden sollte. Der als U5362 bezeichnete Korrekturprozessor hätte mit einem 2µm-CMOS-Prozess eine Fläche von 7,34mm x 8,78mm eingenommen.

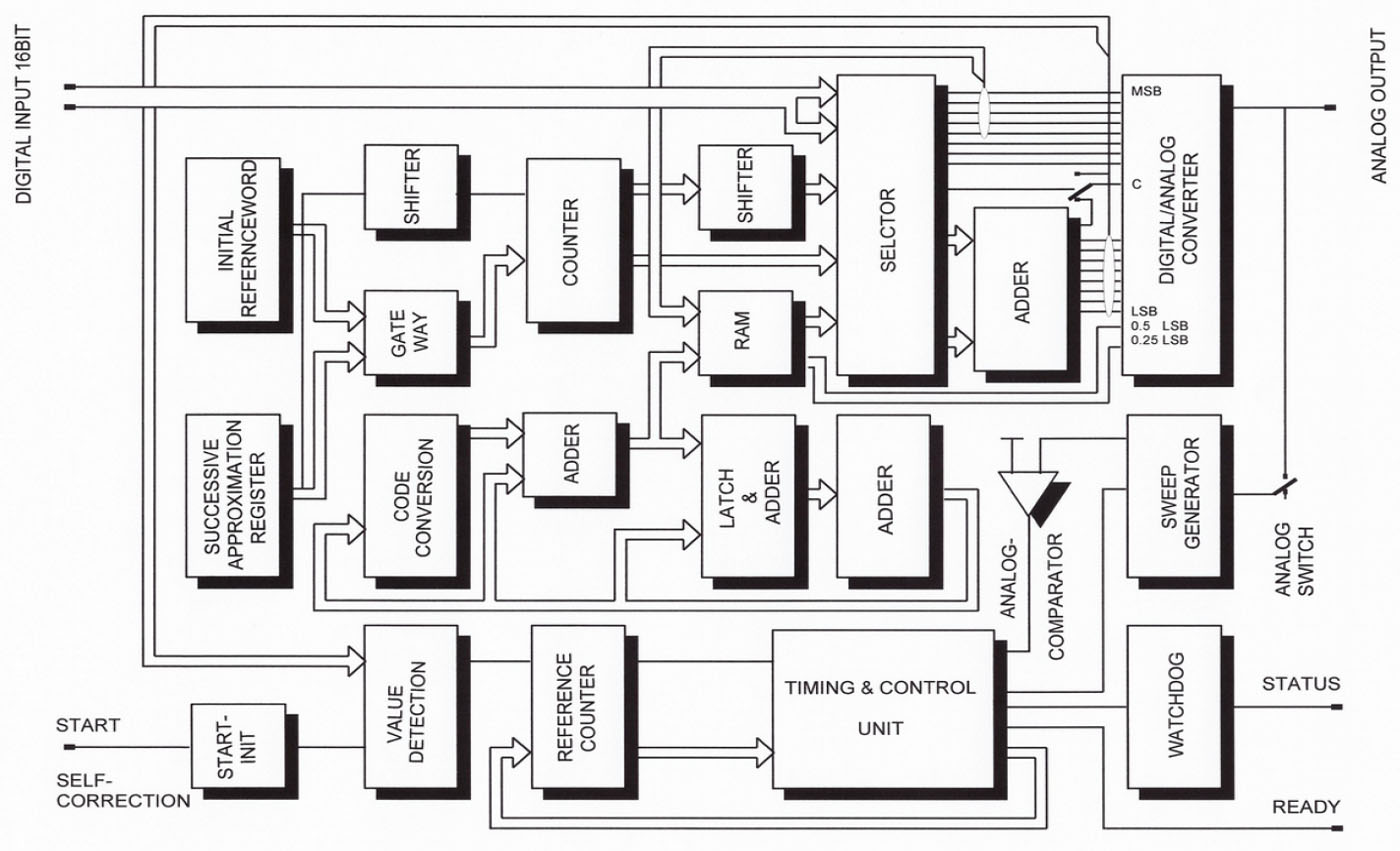

Um einen Digital-Analog-Wandler zu linearisieren, werden neben einer

Steuerungslogik und einem Speicher für Kalibrationsdaten oftmals ein oder zwei

zusätzliche Digital-Analog-Wandler integriert, was die Komplexität entsprechend

stark erhöht. Für den C5360 hat man ein

effizienteres Konzept gewählt. Es basiert auf einem Rampengenerator und einem

Komparator. Während des Abgleichs wird der Rampengenerator auf den Ausgang des

Digital-Analog-Wandlers geschaltet. Der Komparator überwacht wann

sich die beiden Ströme kompensieren.

Der Rampengenerator ist dabei keineswegs

so konstruiert, dass sein Wertebereich mit einer Genauigkeit von 16Bit linear

überstrichen wird. Eine derart hohe Genauigkeit ist allerdings auch nicht

notwendig, da hier mit kleinen Abschnitten von verschieden steilen Rampen

gearbeitet wird, die in diesem beschränkten Bereich äußerst linear sind.

Wird

der Komparator getriggert, erhöht die Logik den Wert des Digital-Analog-Wandlers

und wartet auf den nächsten Trigger. Gemessen wird die Zeit zwischen den

Triggerereignissen, was sich digital relativ einfach und genau umsetzen lässt.

Nach der ersten Referenzmessung kann im folgenden Durchlauf die Schrittweite des

Digital-Analog-Wandlers angepasst werden.

Der für dieses Konzept ideale Digital-Analog-Wandler bietet zwei Besonderheiten. Zum einen besitzt er ein zweites 9.Bit, genauer eine zusätzliche Stromsenke, die den gleichen Stromwert liefert wie das 9.Bit. Im Blockschaltbild ist dieser Eingang mit C für Carry-Bit bezeichnet. Das zusätzliche Bit ist notwendig, damit sich ein Korrekturbereich ergibt, der sowohl ausreichend positive als auch ausreichend negative Werte bietet. Zusätzlich weist der Digital-Analog-Wandler ein 17. und ein 18.Bit auf, die benötigt werden damit bei den Korrekturen keine störenden Rundungsfehler entstehen.

Die digitale Korrektur lässt sich relativ einfach umsetzen. Herausfordernd ist allerdings der Komparator, der ausreichend genau sein muss, um eine Auflösung von mehr als 16Bit darstellen zu können. Während das Konzept mit diskreten Bauteilen entwickelt wurde stand nur ein MAA725 (µA725) zur Verfügung, der bei einem bestmöglichen Schaltungsaufbau maximal das 15. Bit unterscheiden konnte.

Wie beschrieben wäre aus dem TF536 der C536 ohne digitale Korrektur hervorgegangen. Mit Korrekturlogik wäre der C5360 und der C5361 produziert worden. Der C5360 hätte sich bei der Inbetriebnahme einmal selbst abgeglichen, während der C5361 die Möglichkeit geboten hätte den Korrekturprozess von außen anzustoßen. Eine solche Triggermöglichkeit ist vor allem in Bereichen mit starken Temperaturschwankungen vorteilhaft, wo Temperaturdrifts die Genauigkeit des Digital-Analog-Wandlers merklich reduzieren.

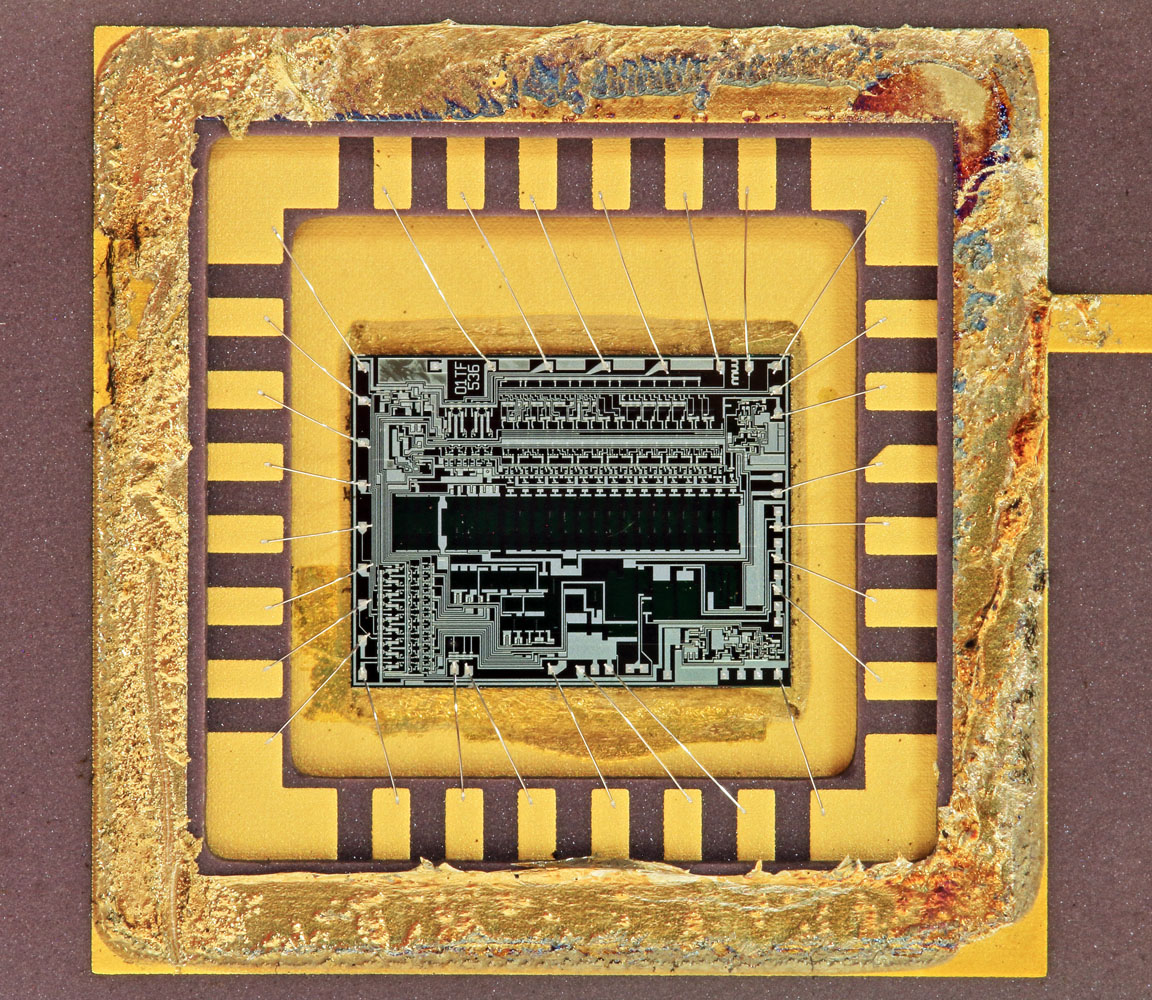

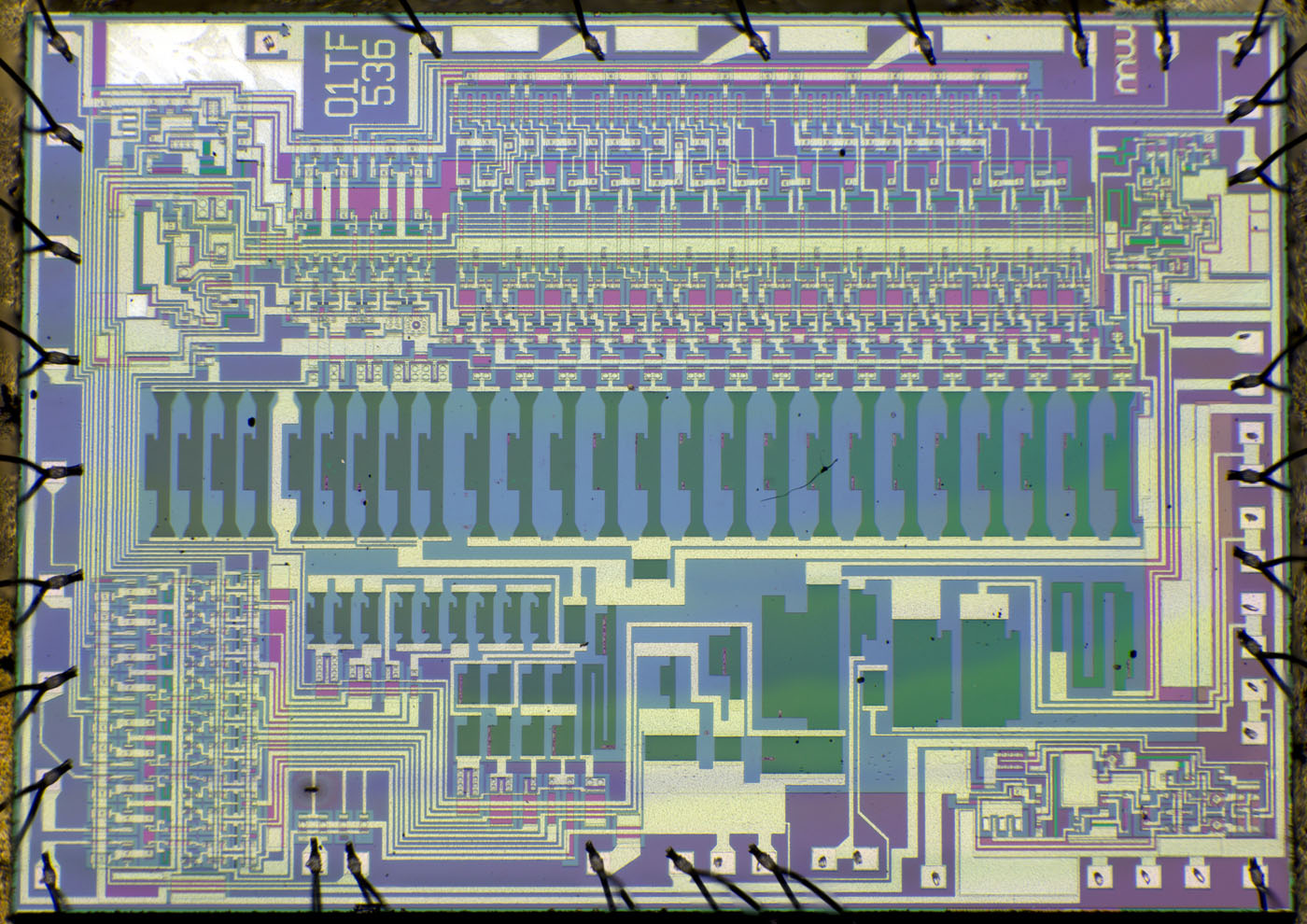

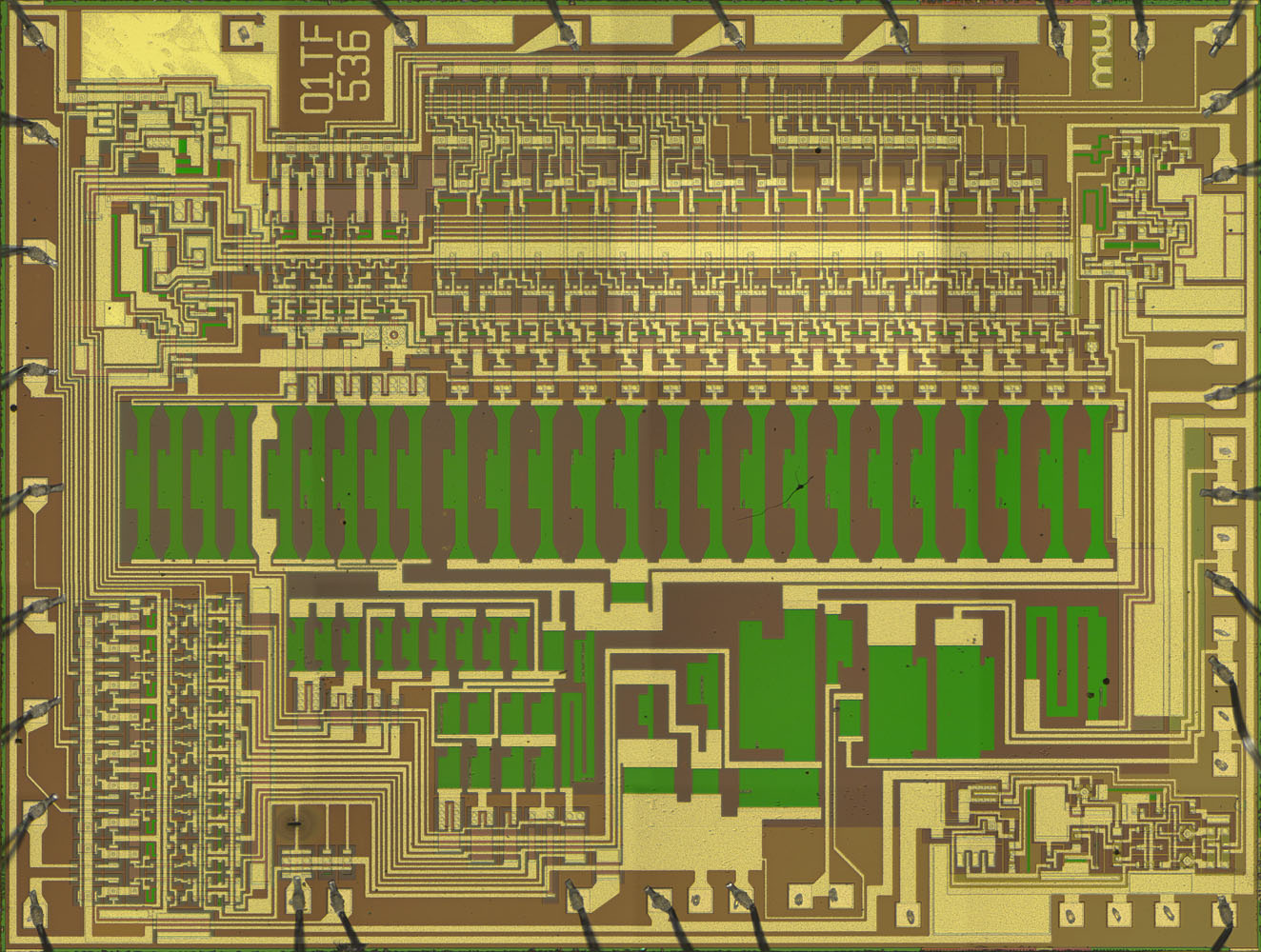

Das Die des TF536 ist mit 6,14mm x 4,65mm sehr groß. Bei einem 16Bit-D/A-Wandler sind die Qualitätsanforderungen an die Herstellungsprozesse außerdem sehr hoch. Die beiden Punkte können in Kombination zu einer nicht unbeträchtlichen Ausschussquote führen.

Das Die bietet 42 Bondpads, von denen 28 kontaktiert wurden. Wie es für einen Digital-Analog-Wandler zu erwarten war, befinden sich vielen abgeglichene Widerstände auf dem Die.

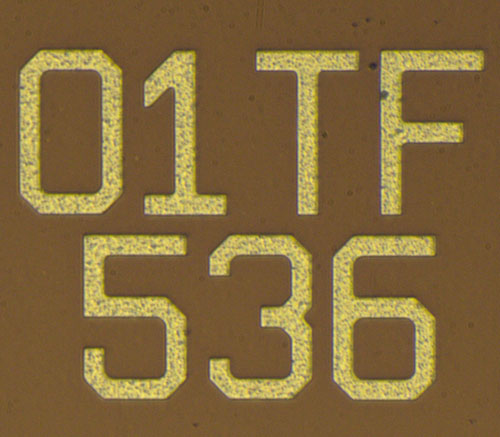

Die Bezeichnung des Digital-Analog-Wandlers lautet TF536. Die einleitenden Buchstaben TF waren zum Ende des HFO durchaus üblich. 01 dürfte für die erste Reivision des TF536 stehen.

Die Buchstaben mw sind die Initialen des Entwicklers.

An der Kante ist zu erkennen, dass hier im Gegensatz zum D220-Wafer bereits Teststrukturen in die Frässtraßen integriert wurden, was Siliziumfläche spart.

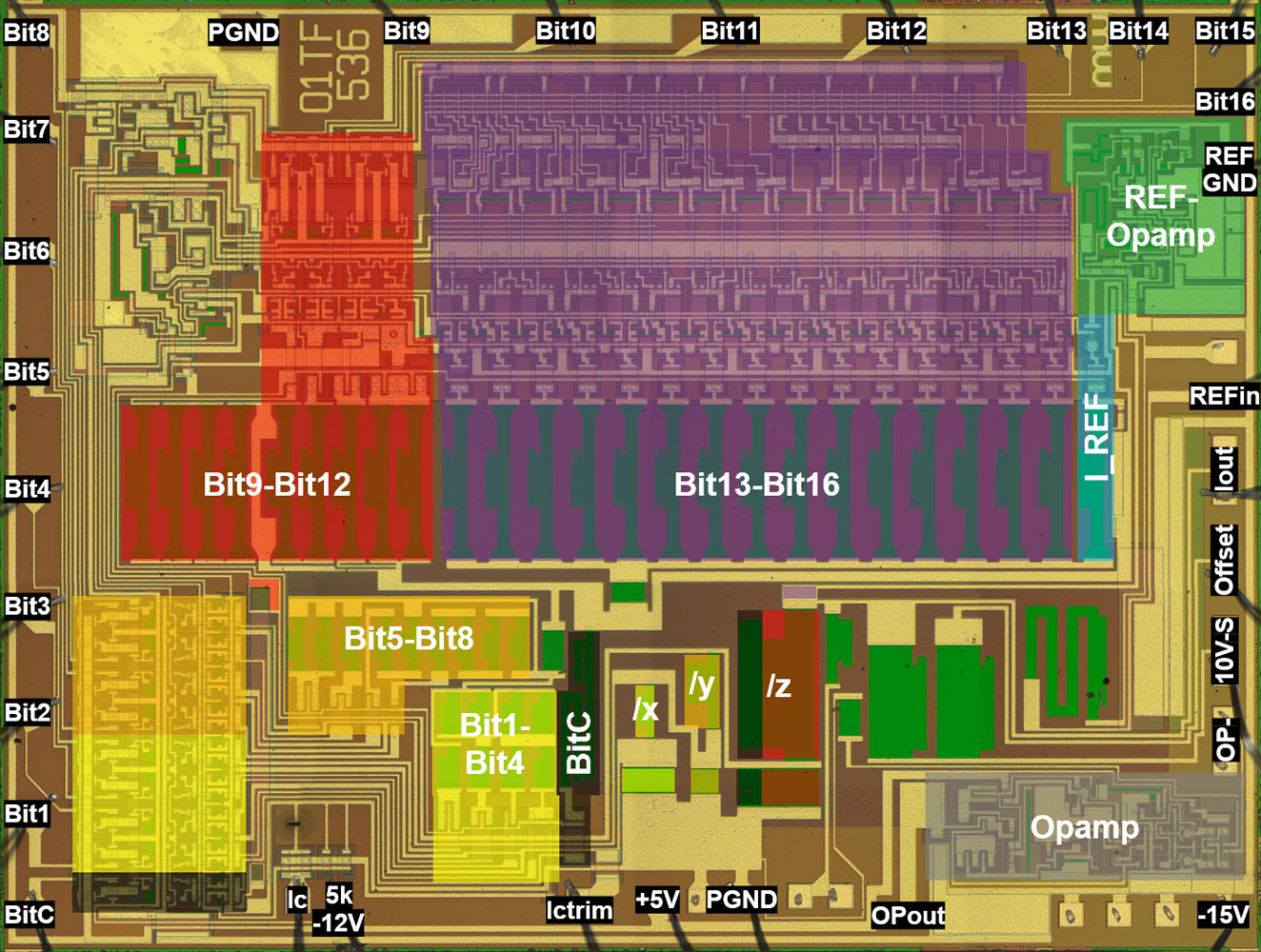

Die Pinbelegung des TF536 ist überliefert, wobei man viele Potentiale auch ohne

Bezeichnung zuordnen hätte können. Die digitalen Daten werden über

eine 16Bit breite Schnittstelle übertragen (LSB: Bit1). Zusätzlich befindet sich in

der unteren linken Ecke das Bit C. Es ist deutlich zu erkennen, dass die 16Bit

mit vier 4Bit breiten Blöcken dargestellt werden (lila, rot, orange, gelb). Das

Carry-Bit befindet sich neben dem gelben Bereich, sein Strom wird aber zum roten

Block addiert. Die Bits 17 und 18, die wünschenswert gewesen wären um

Rundungsfehler zu verhindern, sind auf diesem Die noch nicht vorhanden.

Unterhalb des lila Bereichs sind die drei Widerstandspaare

platziert, die die Ausgänge der unteren drei DAC-Blöcke passend herunterteilen,

bevor alle Ströme addiert und über Iout ausgegben werden.

Ictrim wird als

Testpin beschrieben. Es handelt sich dabei um das noch nicht heruntergeteilte

Potential des niederwertigsten DAC-Blocks (gelb). Die Bezeichnung Ictrim lässt

auf einen externen Abgleich schließen, ein Abgleich ist aber an dieser Stelle

weder notwendig noch sinnvoll. Wahrscheinlicher ist, dass der Pin genutzt wurde,

um die internen Widerstände des gelben DAC-Blocks abzugleichen. Da dessen Ströme

am stärksten heruntergeteilt werden, ist es sicherlich hilfreich während des

Abgleichs auf das sehr viel höhere Rohsignal zugreifen zu können.

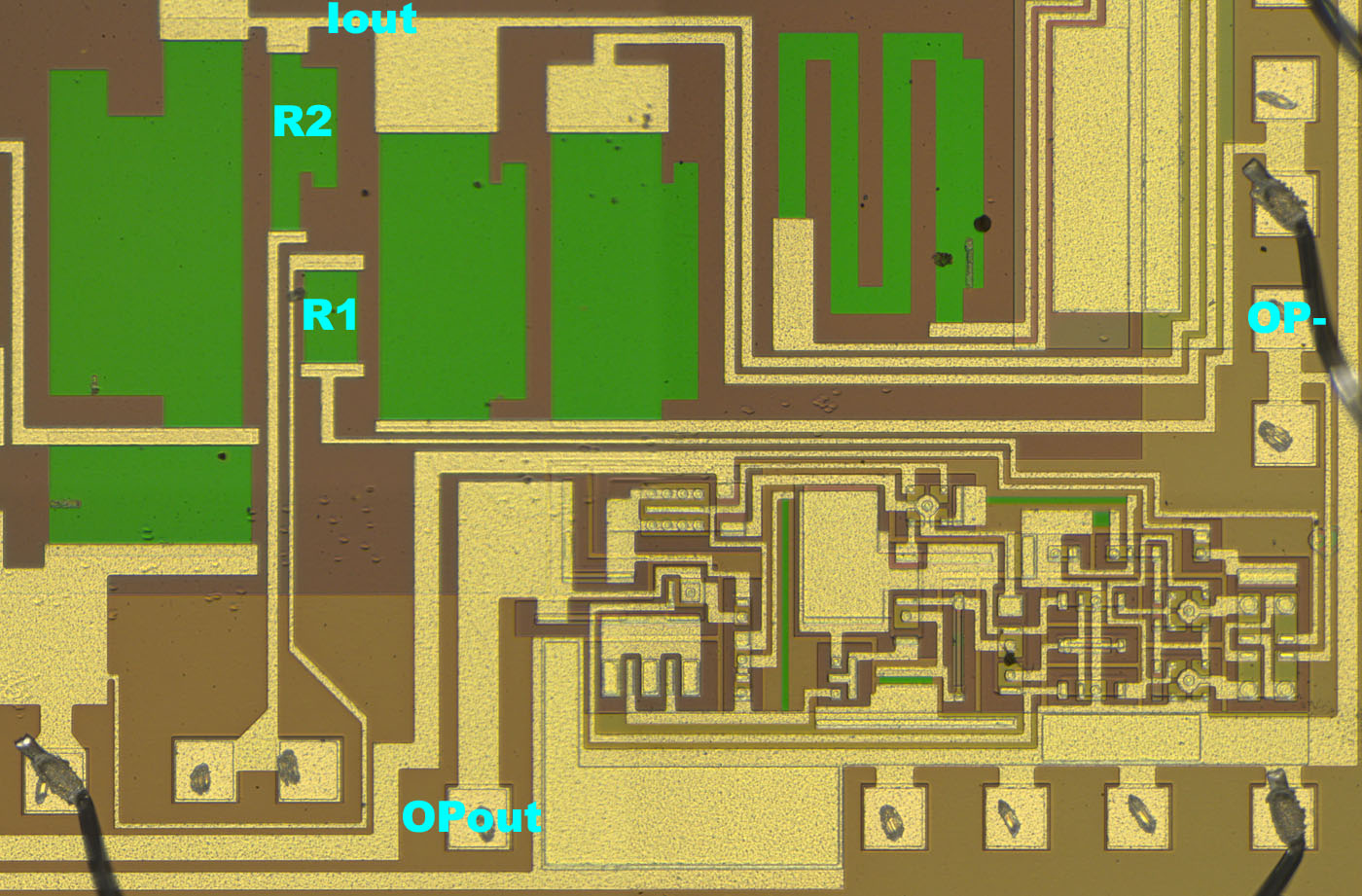

In der unteren rechten Ecke befindet sich ein Operationsverstärker. Ein Eingang und der Ausgang sind auf Bondpads geführt, die aber hier nicht kontaktiert wurden. Höchstwahrscheinlich sollte dieser Operationsverstärker später als Ausgangstreiber dienen. Oberhalb des Operationsverstärkers befinden sich zwei große Widerstände, die über die Bondpads 10V-S und Offset nach außen geführt werden. Wie bei vielen Digital-Analog-Wandlern können diese Widerstände, die dann auch abgeglichen werden, genutzt werden, um verschiedene Ausgangsspannungsbereiche zu wählen und den Offset zu definieren.

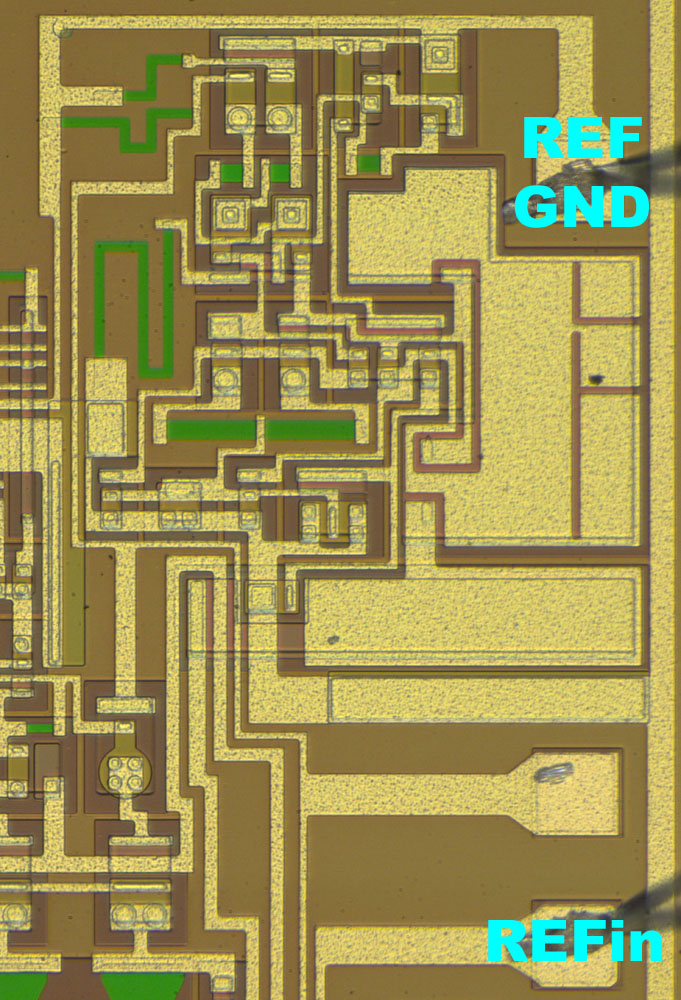

Versorgt wird der TF536 mit einer Referenzspannung, einem +5V- und einem

-15V-Potential. Auf die Integration einer Referenzspannungsquelle wurde

vermutlich auf

Grund der notwendigen Genauigkeit verzichtet. Es war vorgesehen die beste

Referenzsannungsquelle des HFO einzusetzen, die B581, einen Nachbau der AD581

mit einem Temperaturdrift von 30ppm/K. Neben dem PGND-Bezugspotential bietet der

Pin REFGND ein isoliertes Bezugspotential für die Referenzspannung. Der Pin 21

ist über einen 5kΩ-Widerstand mit dem -15V-Potential zu verbinden, so dass sich

dort -7V einstellen.

In der oberen rechten Ecke befindet sich der

Operationsverstärker, der das Referenzpotential entgegen nimmt und puffert

(grün). Im unteren Bereich ist ein schleifenförmiger, abgeglichener

Widerstand platziert, der sich elektrisch zwischen dem Referenzspannungsbondpad

und dem Eingang des Operationsverstärkers befindet. Die Erzeugung des

Referenzstroms erfolgt wie beim DAC80, so dass mit

diesem Widerstand die Höhe des Referenzstroms eingestellt werden kann. Unterhalb des

Operationsverstärkers ist die Stromsenke platziert, die den Referenzstrom

ausgibt (hellblau).

Der nicht markierte Block in der linken oberen Ecke findet sich auch im AD565 und im C565. Er enthält wahrscheinlich Hilfsschaltungen.

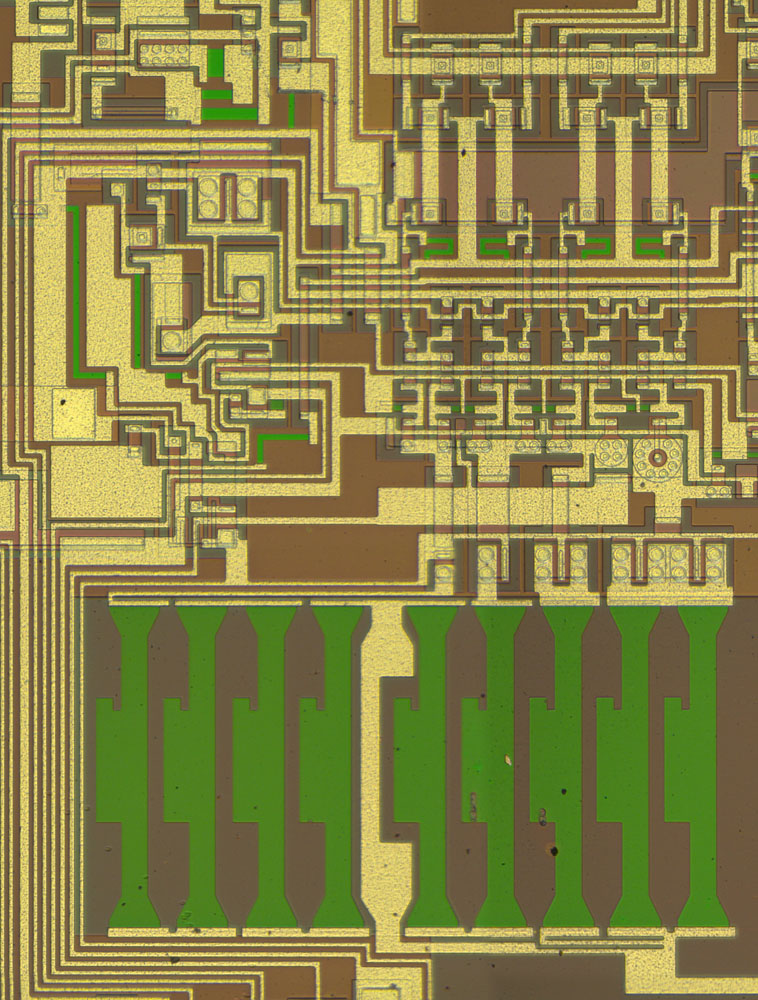

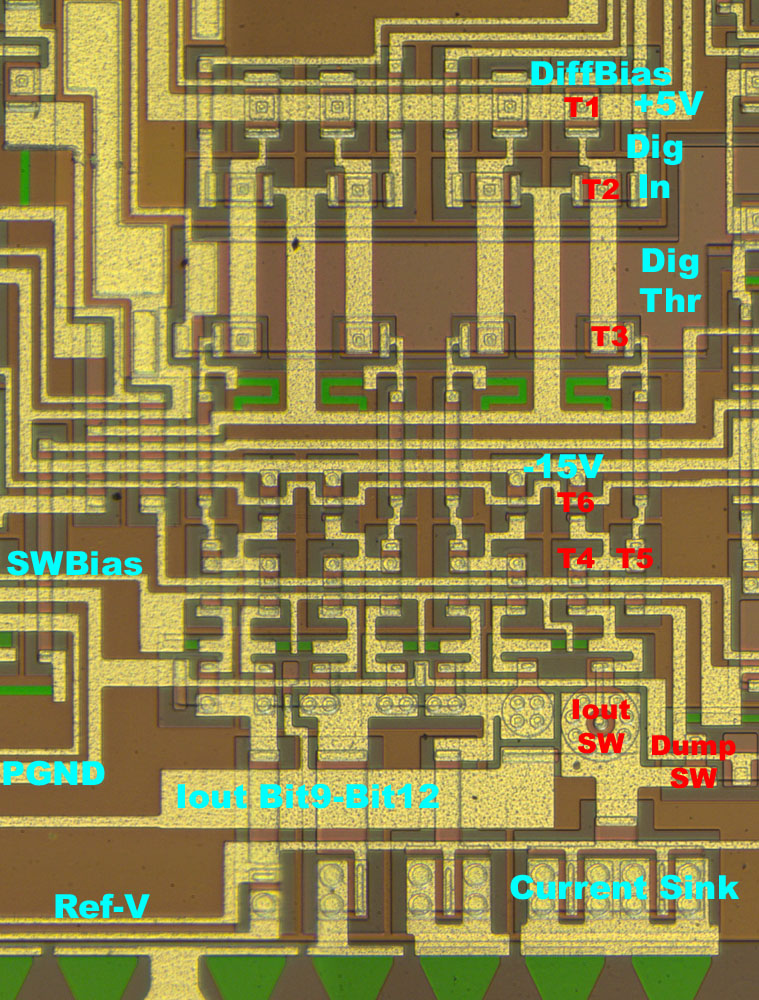

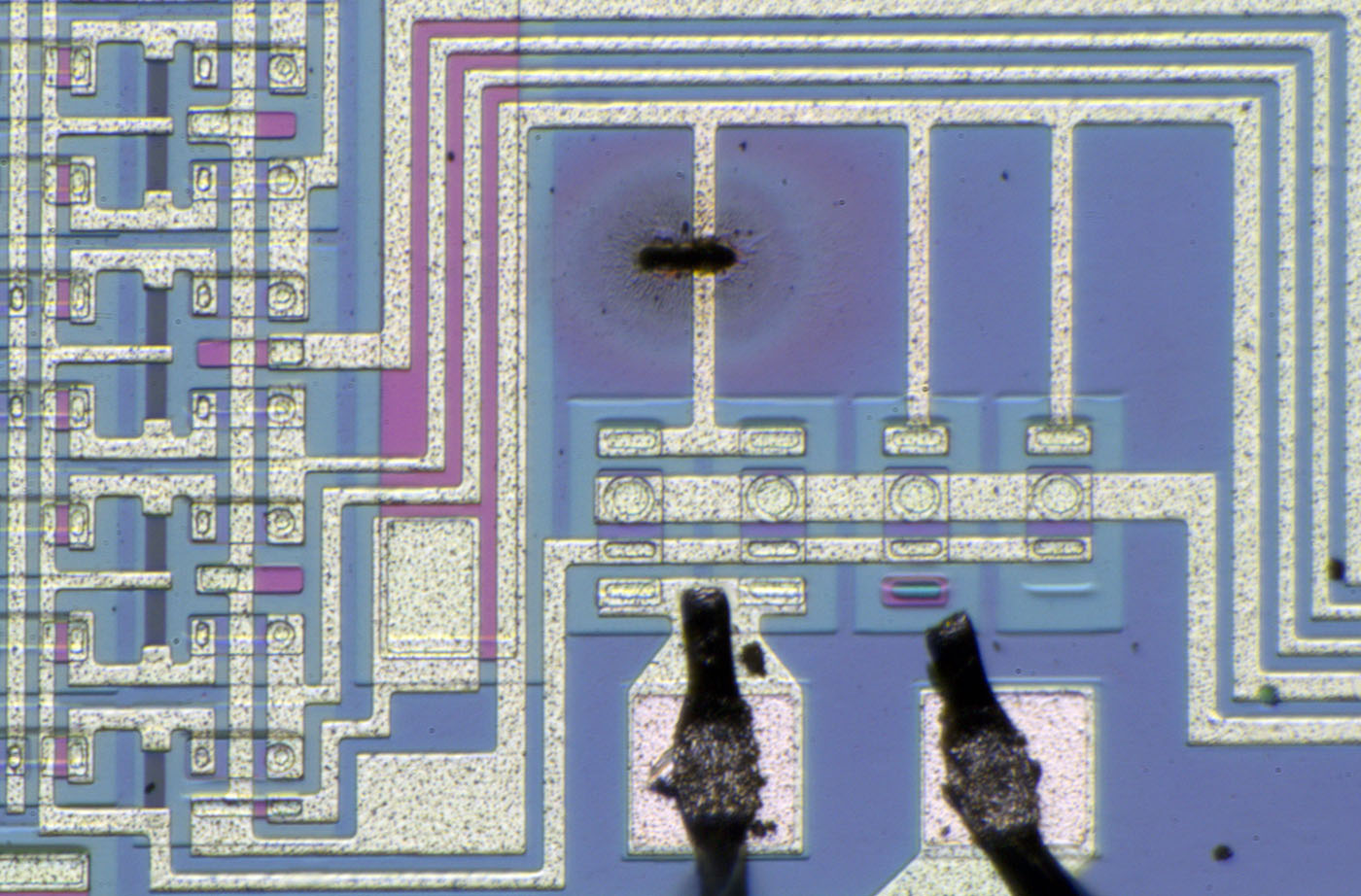

Die Erzeugung der unteren 12Bit erfolgt mit den gleichen Schaltungsteilen, die auch im 12Bit-Digital-Analog-Wandler C565 zum Einsatz kommen. Hier sind die Bits 9 bis 12 zu sehen. Im Vergleich zum C565 fehlt lediglich der Referenzstrompfad und die Schnittstelle zu den digitalen Eingangssignalen wurde etwas verlängert.

Auf die abgeglichenen Widerstände folgen die vier Transistoren der Stromsenken. Die bekannte Verdopplung der Emitterfläche garantiert eine gleichbleibende Stromdichte.

Über den Stromsenken befinden sich die zweimal vier Transistoren, die den Stromwert des jeweiligen Bits entweder zum Ausgang oder zum Massepotential leiten. Auch hier sind die Flächenverhältnisse an die Ströme angepasst. Der Arbeitspunkt der Stromschalter wird über das Potential SWBias bestimmt.

Die Transistoren T4 und T5 kontrollieren die Stromschalter. Der Transistor T6 erzeugt ein Bezugspotential für die Transistoren T4 und T5.

Die Leitung, die nach oben zum Transistor T3 führt, kontaktiert im

C565 direkt den jeweiligen digitalen Eingang. Im TF536

folgen zuerst noch die Transistoren T3, T2 und T1. Höchstwahrscheinlich handelt

es sich dabei um eine Möglichkeit den Schaltpunkt der digitalen Schnittstelle

einzustellen. Die Transistoren T2 und T3 bilden einen Differenzverstärker. Der

Transistor T2 nimmt an seiner Basis das digitale Eigangssignal entgegen. Der

Transistor T3 befindet sich in einer Fläche, die das Basispotential und damit

die Schaltschwelle darstellt. Der Transistor T1 definiert basierend auf dem

+5V-Potential den Arbeitspunkt des Differenzverstärkers.

Das Bondpad, das

extern über einen 5kΩ-Widerstand mit dem -15V-Potential zu verbinden ist, führt

zum Kollektor von T2. Vermutlich musste dieses Potential extern zugeführt

werden, damit die digitalen Signale die analogen Schaltungsteile möglichst wenig

stören.

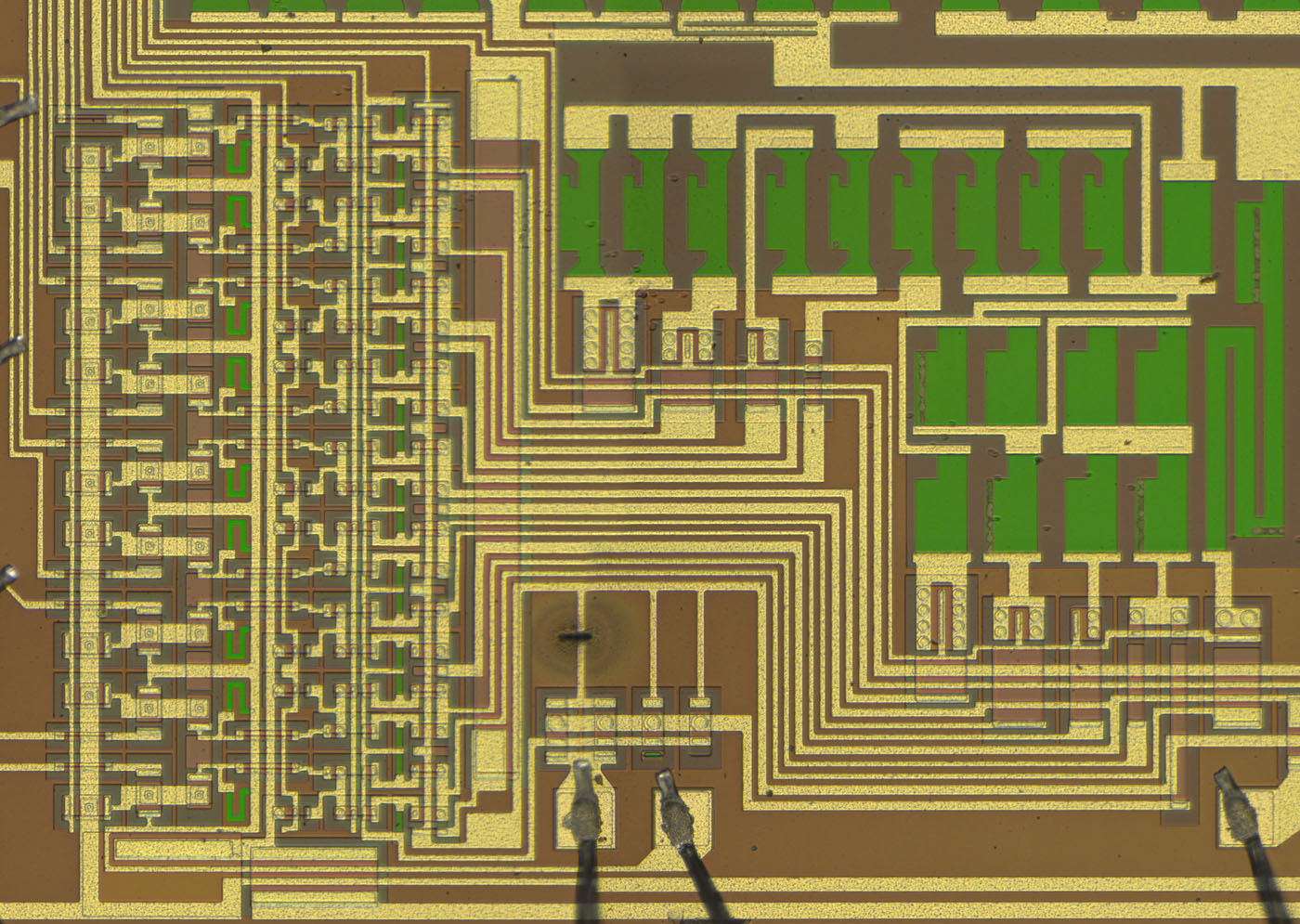

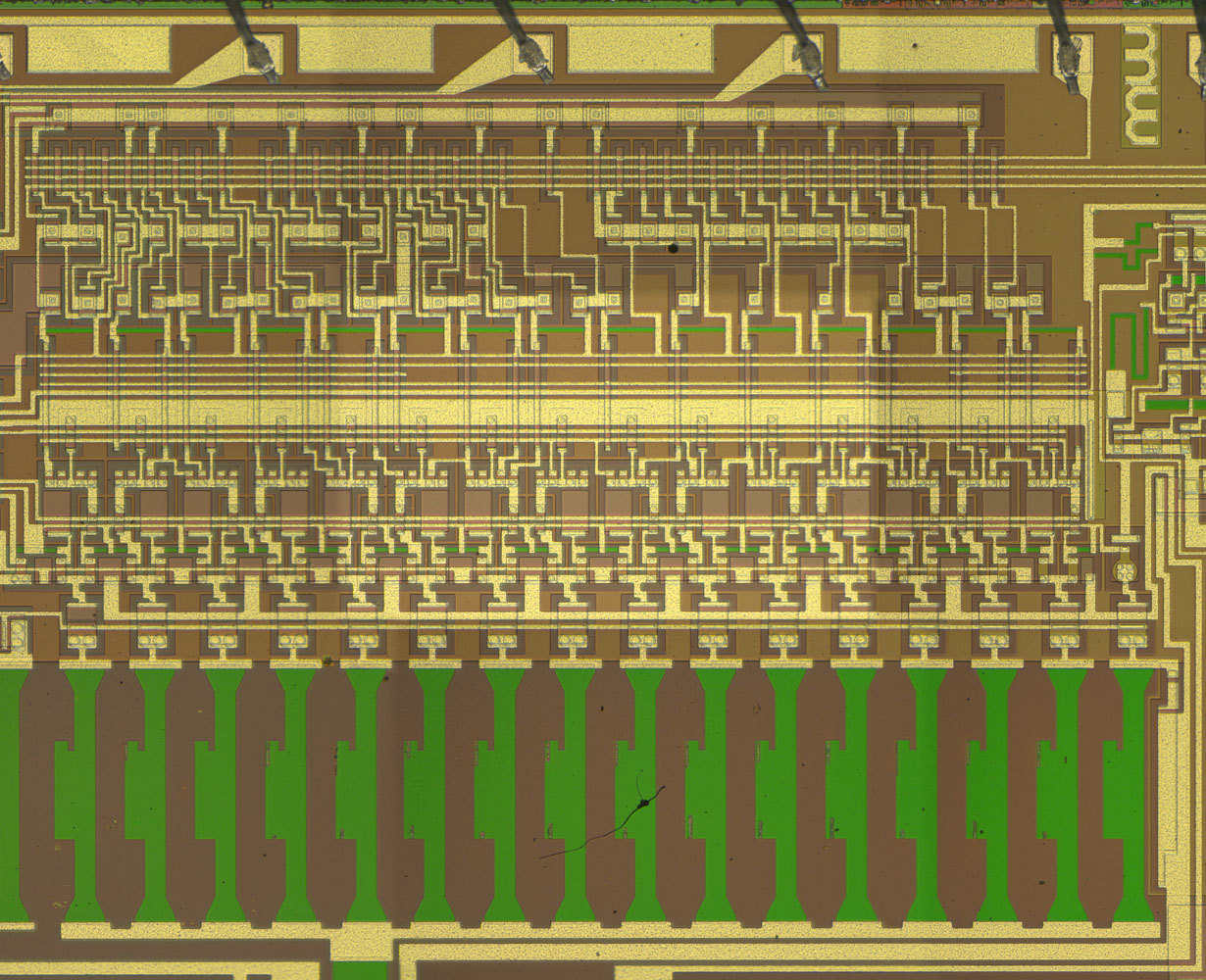

Die Bits 1-8 sind etwas anders angeordnet, aber zeigen grundsätzlich den gleichen Aufbau wie im C565. Auch die Formen der Widerstände sind gleich. Lediglich das Carry-Bit wurde an der unteren Kante hinzugefügt und die digitale Schnittstelle wurde um die oben beschriebene Einstellung der Schaltschwelle erweitert.

Hier ist zu sehen wie der Strom des Carry-Bits vom untersten Stromschalter über einen breiten braunen Streifen zur oberen Kante geführt und dort zum Strom der Bits 9-12 addiert wird.

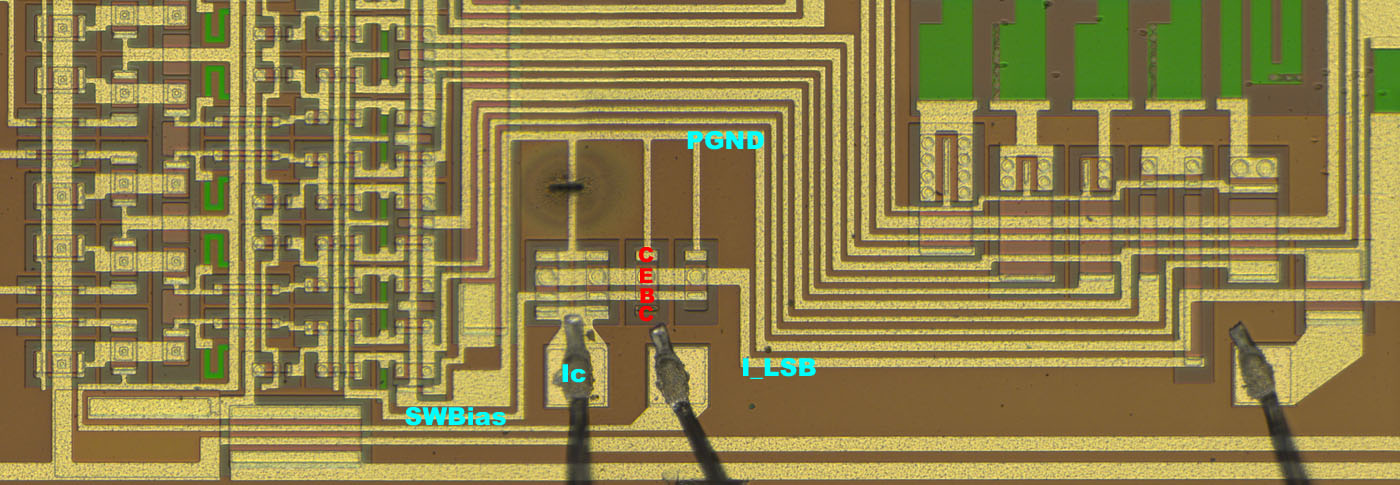

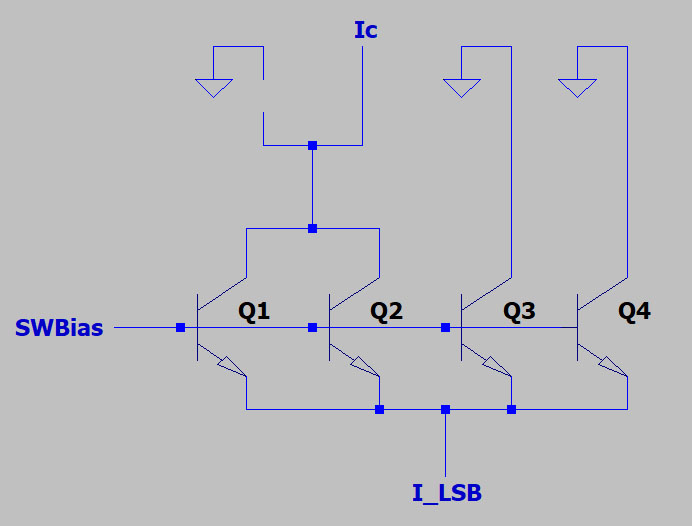

Der Pin Ic soll angeblich den Stromwert des Carry-Bits ausgeben und wäre mit dem DAC-Ausgang zu verbinden. Es zeigt sich allerdings, dass das nicht ganz richtig ist. Der Pin Ic ist an die Kollektoren von zwei parallel geschalteten Transistoren angebunden.

Die Emitter der vier nebeneinander platzierten Transistoren sind alle mit der aufgedoppelten Stromsenke des LSB verbunden. Im AD565 wurde bereits beschrieben, dass die doppelte Stromsenke beim LSB notwendig ist, um den gewünschten Stromwert erzeugen zu können. Gleichzeitig wird das Potential der zweiten LSB-Stromsenke für die Schaltlogik verwendet. Die Aufteilung auf vier Transistoren führt dazu, dass in jedem Kollektor ein Viertel des LSB-Stroms fließt. Es handelt sich allerdings nicht wirklich um den LSB-Stromwert, da dieser später noch einmal heruntergeteilt wird.

Der Hinweis, dass der Ic-Pin mit dem Ausgang des Digital-Analog-Wandlers verbunden werden muss, lässt vermuten, dass der zusätzliche Strom einen Offset kompensiert. Es ist durchaus denkbar, dass Ic den Strom bereitstellt, der durch Leckströme verloren geht.

Besonders interessant ist die Tatsache, dass an dieser Stelle die Metalllage nachträglich unterbrochen wurde. Es scheint allgemein so zu sein, dass man über das Design der Metalllage auswählen kann wie hoch der mutmaßliche Kompensationsstrom sein soll. Man bindet die Transistoren dazu entweder an das Massepotential oder an den Pin Ic an. Beim dritten Transistor ist der zweite Kollektoranschluss schon vorgehalten, wird aber nicht kontaktiert. Vermutlich wollte man sich während der Entwicklung den Aufwand einer Metalllagenänderung sparen und passte den Kompensationsstrom über eine Unterbrechung der Masseverbindung an den tatsächlichen Leckstrom an.

Die Genauigkeitsanforderungen sind bei den obersten vier Bits am höchsten. Selbst für eine Genauigkeit von 13Bit muss bei einem maximalen Ausgangsstrom von -1mA die Ungenauigkeit des MSB (-0,5mA) kleiner 61nA sein. Um diese Anforderungen umsetzen zu können, wurden die oberen vier Bits mit fünfzehn einzelnen Stromsenken aufgebaut.

Oberhalb der Eingangsbeschaltung für die digitalen Signale befindet sich bei diesem DAC-Block eine Matrix, die die binären Werte den jeweiligen Stromsenken zuweist. Die Schaltungsteile zur Einstellung der Schaltschwellen wurden entsprechend der Anzahl der Eingangssignale vervielfacht.

Die sechszehnte Stromsenke ist die Referenzstromsenke. Sie ist genauso groß aufgebaut wie die Stromsenken der obersten vier Bits, da an sie ähnliche Anforderungen gestellt werden.

Der Strom der Bits 13 bis 16 wird direkt zum Ausgang geführt. Alle anderen Bits durchlaufen eine teilweise mehrfache Teilung. Die Bits 1 bis 4 durchlaufen den Teiler /x und werden dann zu den Bits 5 bis 8 addiert. Die Summe der Bits 1 bis 8 durchläuft den Teiler /y und überlagert sich mit dem Strom der Bits 9 bis 12 und dem Strom des C-Bits. Zuletzt folgt der Teiler /z bevor das Signal mit dem Strom der Bits 13 bis 16 zum Ausgang geführt wird.

Ein Eingang des nicht verwendeten Operationsverstärkers ist über einen Widerstand an das Massepotential angebunden. Neben dem Ausgangspotential OPout befinden sich zwei ungenutzte Bondpads, die über einen Widerstand zum Ausgang des Digital-Analog-Wandlers führen. Der Schluss liegt nahe, dass der Operationsverstärker als Ausgangstreiber vorgesehen war. Dazu passen auch die integrierten Widerstände zur Einstellung des Spannungsbereichs.

Der Aufbau des Operationsverstärkers im Referenzspannungspfad erinnert sehr stark an den Operationsverstärker des C565 und damit an den ursprünglichen Operationsverstärker im AD565.